Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp204-e-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.3 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en530271          |

#### 3.3.1 KEY RESOURCES

- Section 2. "CPU" (DS70204)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

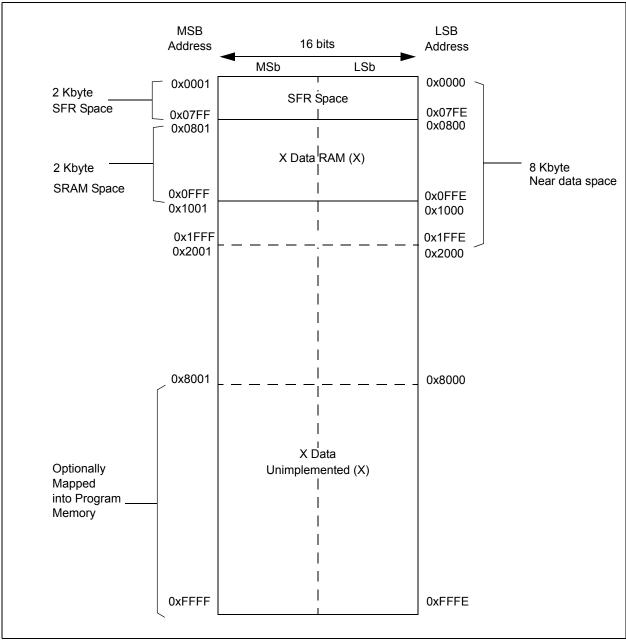

### FIGURE 4-3: DATA MEMORY MAP FOR PIC24HJ32GP202/204 AND PIC24HJ16GP304 DEVICES WITH 2 KB RAM

### 4.3 Program Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en530271          |

#### 4.3.1 KEY RESOURCES

- Section 4. "Program Memory" (DS70202)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### TABLE 4-23: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA.)                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

### 4.5.3 MOVE (MOV) INSTRUCTION

Move instructions provide a greater degree of addressing flexibility than the other instructions. In addition to the Addressing modes supported by most MCU instructions, MOV instructions also support Register Indirect with Register Offset Addressing mode. This is also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing mode specified in the instruction can differ |

|-------|---------------------------------------------------------------------------------------|

|       | for the source and the destination EA.                                                |

|       | However, the 4-bit Wb (Register Offset)                                               |

|       | field is shared by both source and                                                    |

|       | destination (but typically only used by                                               |

|       | one).                                                                                 |

In summary, move instructions support the following addressing modes:

- Register Direct

- Register Indirect

- · Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

| Note: | Not   | all   | instructions  | support      | all   | the  |

|-------|-------|-------|---------------|--------------|-------|------|

|       | addr  | essir | ng modes give | n above. I   | ndivi | dual |

|       | instr | uctio | ns may suppo  | ort differen | t sub | sets |

|       | of th | ese a | addressing mo | odes.        |       |      |

### 4.5.4 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

| R/W-0         | R-0                                                                                            | U-0               | U-0           | U-0              | U-0             | U-0             | U-0    |  |

|---------------|------------------------------------------------------------------------------------------------|-------------------|---------------|------------------|-----------------|-----------------|--------|--|

| ALTIVT        | DISI                                                                                           | —                 | _             | —                | —               | —               | _      |  |

| bit 15        |                                                                                                |                   |               |                  |                 |                 | bit 8  |  |

|               |                                                                                                |                   |               |                  |                 |                 |        |  |

| U-0           | U-0                                                                                            | U-0               | U-0           | U-0              | R/W-0           | R/W-0           | R/W-0  |  |

| —             | _                                                                                              | —                 |               | —                | INT2EP          | INT1EP          | INT0EP |  |

| bit 7         |                                                                                                |                   |               |                  |                 |                 | bit (  |  |

|               |                                                                                                |                   |               |                  |                 |                 |        |  |

| Legend:       |                                                                                                |                   |               |                  |                 |                 |        |  |

| R = Readabl   | e bit                                                                                          | W = Writable      | bit           | U = Unimple      | mented bit, rea | d as '0'        |        |  |

| -n = Value at | POR                                                                                            | '1' = Bit is set  |               | '0' = Bit is cle | eared           | x = Bit is unki | nown   |  |

|               |                                                                                                |                   |               |                  |                 |                 |        |  |

| bit 15        | ALTIVT: Enat                                                                                   | ole Alternate In  | terrupt Vecto | r Table bit      |                 |                 |        |  |

|               |                                                                                                | nate vector tabl  |               |                  |                 |                 |        |  |

|               |                                                                                                | dard (default) v  |               |                  |                 |                 |        |  |

| bit 14        |                                                                                                | struction Statu   |               |                  |                 |                 |        |  |

|               |                                                                                                | ruction is active | -             |                  |                 |                 |        |  |

| h:+ 40 0      |                                                                                                | ruction is not a  |               |                  |                 |                 |        |  |

| bit 13-3      | -                                                                                              | ted: Read as '    |               |                  |                 |                 |        |  |

| bit 2         |                                                                                                |                   | •             | t Polarity Selec | t bit           |                 |        |  |

|               |                                                                                                | on negative edg   |               |                  |                 |                 |        |  |

| bit 1         | •                                                                                              |                   |               | t Dolarity Soloo | + hit           |                 |        |  |

| DILI          | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge |                   |               |                  |                 |                 |        |  |

|               |                                                                                                | on positive edg   | •             |                  |                 |                 |        |  |

| bit 0         | •                                                                                              | 1 0               |               | t Polarity Selec | t bit           |                 |        |  |

|               |                                                                                                | •                 | •             |                  |                 |                 |        |  |

|               | 1 = Interrupt a                                                                                | on negative edg   | ne            |                  |                 |                 |        |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| U-0                                 | U-0                                     | U-0              | U-0 | U-0                                     | U-0 | U-0   | U-0   |

|-------------------------------------|-----------------------------------------|------------------|-----|-----------------------------------------|-----|-------|-------|

| _                                   | _                                       | —                | —   | —                                       |     | —     | —     |

| bit 15                              |                                         |                  |     |                                         |     |       | bit 8 |

|                                     |                                         |                  |     |                                         |     |       |       |

| U-0                                 | U-0                                     | U-0              | U-0 | U-0                                     | U-0 | R/W-0 | U-0   |

| —                                   | —                                       | _                | —   | —                                       |     | U1EIE | —     |

| bit 7                               |                                         |                  |     |                                         |     |       | bit 0 |

|                                     |                                         |                  |     |                                         |     |       |       |

| Legend:                             |                                         |                  |     |                                         |     |       |       |

| R = Readable bit W = Writable bit   |                                         |                  |     | U = Unimplemented bit, read as '0'      |     |       |       |

| -n = Value at F                     | POR                                     | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |       |       |

|                                     |                                         |                  |     |                                         |     |       |       |

| bit 15-2 Unimplemented: Read as '0' |                                         |                  |     |                                         |     |       |       |

| bit 1                               | U1EIE: UART1 Error Interrupt Enable bit |                  |     |                                         |     |       |       |

| 1 = Interrupt request enabled       |                                         |                  |     |                                         |     |       |       |

|                                     | 0 = Interrupt request not enabled       |                  |     |                                         |     |       |       |

### REGISTER 7-10: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

bit 0 Unimplemented: Read as '0'

#### TABLE 10-1:REMAPPABLE PERIPHERAL INPUTS<sup>(1)</sup>

| Input Name               | Function Name | Register | Configuration<br>Bits |

|--------------------------|---------------|----------|-----------------------|

| External Interrupt 1     | INT1          | RPINR0   | INT1R<4:0>            |

| External Interrupt 2     | INT2          | RPINR1   | INT2R<4:0>            |

| Timer 2 External Clock   | T2CK          | RPINR3   | T2CKR<4:0>            |

| Timer 3 External Clock   | T3CK          | RPINR3   | T3CKR<4:0>            |

| Input Capture 1          | IC1           | RPINR7   | IC1R<4:0>             |

| Input Capture 2          | IC2           | RPINR7   | IC2R<4:0>             |

| Input Capture 7          | IC7           | RPINR10  | IC7R<4:0>             |

| Input Capture 8          | IC8           | RPINR10  | IC8R<4:0>             |

| Output Compare Fault A   | OCFA          | RPINR11  | OCFAR<4:0>            |

| UART 1 Receive           | U1RX          | RPINR18  | U1RXR<4:0>            |

| UART 1 Clear To Send     | U1CTS         | RPINR18  | U1CTSR<4:0>           |

| SPI 1 Data Input         | SDI1          | RPINR20  | SDI1R<4:0>            |

| SPI 1 Clock Input        | SCK1IN        | RPINR20  | SCK1R<4:0>            |

| SPI 1 Slave Select Input | SS1IN         | RPINR21  | SS1R<4:0>             |

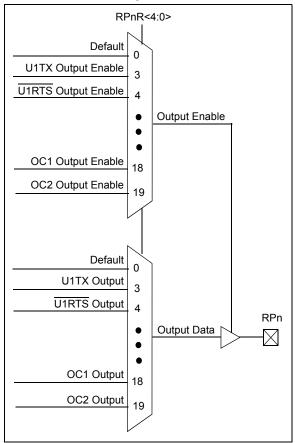

**FIGURE 10-3:**

**Note 1:** Unless otherwise noted, all inputs use the Schmitt input buffers.

### 10.6.2.2 Output Mapping

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 5-bit fields, with each set associated with one RPn pin (see Register 10-10 through Register 10-22). The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 10-2 and Figure 10-3).

The list of peripherals for output mapping also includes a null value of '00000' because of the mapping technique. This permits any given pin to remain unconnected from the output of any of the pin selectable peripherals.

### MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPn

### **10.9** Peripheral Pin Select Registers

The PIC24HJ32GP202/204 and PIC24HJ16GP304 devices implement 17 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (9)

- Output Remappable Peripheral Registers (8)

- Note: Input and Output Register values can only be changed if the IOLOCK bit (OSC-CON<6>) = 0. See Section 10.6.3.1 "Control Register Lock" for a specific command sequence.

| U-0          | U-0       | U-0                              | R/W-1                   | R/W-1                                   | R/W-1                                   | R/W-1              | R/W-1   |  |  |

|--------------|-----------|----------------------------------|-------------------------|-----------------------------------------|-----------------------------------------|--------------------|---------|--|--|

| 0-0          | 0-0       |                                  | 10/00-1                 | 10/00-1                                 | INT1R<4:0>                              |                    | 10/00-1 |  |  |

|              | _         |                                  |                         |                                         | 111111111111111111111111111111111111111 |                    | L : L : |  |  |

| bit 15       |           |                                  |                         |                                         |                                         |                    | bit 8   |  |  |

|              |           |                                  |                         |                                         |                                         |                    |         |  |  |

| U-0          | U-0       | U-0                              | U-0                     | U-0                                     | U-0                                     | U-0                | U-0     |  |  |

| —            | _         | —                                | —                       | _                                       | —                                       | —                  | —       |  |  |

| bit 7        |           |                                  |                         |                                         |                                         |                    | bit C   |  |  |

|              |           |                                  |                         |                                         |                                         |                    |         |  |  |

| Legend:      |           |                                  |                         |                                         |                                         |                    |         |  |  |

| R = Readab   | le bit    | W = Writable                     | bit                     | it U = Unimplemented bit, read as '0'   |                                         |                    |         |  |  |

| -n = Value a | t POR     | '1' = Bit is set                 | et '0' = Bit is cleared |                                         | eared                                   | x = Bit is unknown |         |  |  |

|              |           |                                  |                         |                                         |                                         |                    |         |  |  |

| bit 15-13    | Unimpleme | nted: Read as '                  | 0'                      |                                         |                                         |                    |         |  |  |

| bit 12-8     | -         | : Assign Externa                 |                         | (INTR1) to the                          | corresponding                           | RPn pin            |         |  |  |

|              |           | ut tied to Vss                   |                         | , , , , , , , , , , , , , , , , , , , , | 5                                       | r                  |         |  |  |

|              |           | ut tied to RP25                  |                         |                                         |                                         |                    |         |  |  |

|              | •         |                                  |                         |                                         |                                         |                    |         |  |  |

|              | •         |                                  |                         |                                         |                                         |                    |         |  |  |

|              | •         |                                  |                         |                                         |                                         |                    |         |  |  |

|              |           | ut tied to RP1<br>ut tied to RP0 |                         |                                         |                                         |                    |         |  |  |

### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| bit 7-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

#### REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0   |

|-------|

|       |

|       |

| bit 8 |

|       |

| R/W-1 |

|       |

| bit 0 |

|       |

|       |

|       |

| nown  |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

#### REGISTER 10-9: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0          | U-0                          | U-0              | U-0            | U-0              | U-0              | U-0             | U-0   |

|--------------|------------------------------|------------------|----------------|------------------|------------------|-----------------|-------|

| _            | —                            | —                | _              | —                | —                | —               | _     |

| bit 15       | ·                            |                  |                |                  |                  |                 | bit 8 |

|              |                              |                  |                |                  |                  |                 |       |

| U-0          | U-0                          | U-0              | R/W-1          | R/W-1            | R/W-1            | R/W-1           | R/W-1 |

| _            | —                            | —                |                |                  | SS1R<4:0>        |                 |       |

| bit 7        |                              |                  | •              |                  |                  |                 | bit 0 |

|              |                              |                  |                |                  |                  |                 |       |

| Legend:      |                              |                  |                |                  |                  |                 |       |

| R = Readab   | ole bit                      | W = Writable     | bit            | U = Unimpler     | nented bit, read | as '0'          |       |

| -n = Value a | at POR                       | '1' = Bit is set |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |                              |                  |                |                  |                  |                 |       |

| bit 15-5     | Unimplemen                   | ted: Read as '   | 0'             |                  |                  |                 |       |

| bit 4-0      | SS1R<4:0>: /                 | Assign SPI1 Sl   | ave Select Inp | out (SS1IN) to   | the correspondi  | ng RPn pin      |       |

|              | 11111 = Inpu<br>11001 = Inpu |                  |                |                  |                  |                 |       |

|              | •                            |                  |                |                  |                  |                 |       |

|              | •                            |                  |                |                  |                  |                 |       |

00001 = Input tied to RP1

00000 = Input tied to RP0

#### REGISTER 10-10: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP1R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

|        |     |     |       |       |           |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

| —      | —   | —   |       |       | RP0R<4:0> |       |       |

| bit 7  |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP1R<4:0>:** Peripheral Output Function is Assigned to RP1 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin (see Table 10-2 for peripheral function numbers)

| R/W-0         | R/W-0                                               | R/W-0                               | U-0           | U-0                | U-0             | U-0              | U-0   |  |  |  |

|---------------|-----------------------------------------------------|-------------------------------------|---------------|--------------------|-----------------|------------------|-------|--|--|--|

| FRMEN         | SPIFSD                                              | FRMPOL                              |               | —                  |                 | —                | —     |  |  |  |

| bit 15        | bit 15                                              |                                     |               |                    |                 |                  |       |  |  |  |

|               |                                                     |                                     |               |                    |                 |                  |       |  |  |  |

| U-0           | U-0                                                 | U-0                                 | U-0           | U-0                | U-0             | R/W-0            | U-0   |  |  |  |

| —             | _                                                   | —                                   | _             | —                  | —               | FRMDLY           | —     |  |  |  |

| bit 7         |                                                     |                                     |               |                    |                 |                  | bit 0 |  |  |  |

|               |                                                     |                                     |               |                    |                 |                  |       |  |  |  |

| Legend:       |                                                     |                                     |               |                    |                 |                  |       |  |  |  |

| R = Readable  | e bit                                               | W = Writable                        | bit           | U = Unimpler       | nented bit, rea | d as '0'         |       |  |  |  |

| -n = Value at | POR                                                 | '1' = Bit is set                    |               | '0' = Bit is cle   | ared            | x = Bit is unkno | own   |  |  |  |

|               |                                                     |                                     |               |                    |                 |                  |       |  |  |  |

| bit 15        |                                                     | med SPIx Supp                       |               |                    |                 |                  |       |  |  |  |

|               |                                                     | SPIx support en<br>SPIx support dis |               | in used as fram    | ne sync pulse i | nput/output)     |       |  |  |  |

| bit 14        |                                                     | ••                                  |               | ntral hit          |                 |                  |       |  |  |  |

| DIL 14        |                                                     | me Sync Pulse<br>nc pulse input (   |               |                    |                 |                  |       |  |  |  |

|               |                                                     | nc pulse input (                    | ,             |                    |                 |                  |       |  |  |  |

| bit 13        | ,                                                   | ame Sync Puls                       | ( )           |                    |                 |                  |       |  |  |  |

|               |                                                     | nc pulse is activ                   | -             |                    |                 |                  |       |  |  |  |

|               | 0 = Frame sy                                        | nc pulse is activ                   | ve-low        |                    |                 |                  |       |  |  |  |

| bit 12-2      | 12-2 Unimplemented: Read as '0'                     |                                     |               |                    |                 |                  |       |  |  |  |

| bit 1         | FRMDLY: Frame Sync Pulse Edge Select bit            |                                     |               |                    |                 |                  |       |  |  |  |

|               | 1 = Frame sync pulse coincides with first bit clock |                                     |               |                    |                 |                  |       |  |  |  |

|               | •                                                   | nc pulse preced                     |               |                    |                 |                  |       |  |  |  |

| bit 0         | Unimplemen                                          | ted: This bit m                     | ust not be se | t to '1' by the us | ser application |                  |       |  |  |  |

|               |                                                     |                                     |               |                    |                 |                  |       |  |  |  |

### REGISTER 15-3: SPIxCON2: SPIx CONTROL REGISTER 2

#### REGISTER 17-1: UxMODE: UARTx MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                      |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                              |

- **Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

NOTES:

#### TABLE 22-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| (unless o    | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |  |  |  |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Param<br>No. | Symbol Characteristics Min Ivo Max Units Comments                                                                                                                                                    |  |  |  |  |  |  |  |  |

|              | —     CEFC     External Filter Capacitor     4.7     10     —     μF     Capacitor must be low series resistance (< 5 ohms)                                                                          |  |  |  |  |  |  |  |  |

**Note 1:** Typical VCAP voltage = 2.5V when  $VDD \ge VDDMIN$ .

# TABLE 22-21:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

| AC CHA       | AC CHARACTERISTICS |                                                                               |                                  | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |    |                                                                                                         |  |  |

|--------------|--------------------|-------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------|-----|----|---------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol             | Characteristic                                                                | Min Typ <sup>(2)</sup> Max Units |                                                       |     |    | Conditions                                                                                              |  |  |

| SY10         | TMCL               | MCLR Pulse-Width (low) <sup>(1)</sup>                                         | 2                                | _                                                     | _   | μS | -40°C to +85°C                                                                                          |  |  |

| SY11         | TPWRT              | Power-up Timer Period <sup>(1)</sup>                                          |                                  | 2<br>4<br>16<br>32<br>64<br>128                       |     | ms | -40°C to +85°C<br>User programmable                                                                     |  |  |

| SY12         | TPOR               | Power-on Reset Delay <sup>(3)</sup>                                           | 3                                | 10                                                    | 30  | μS | -40°C to +85°C                                                                                          |  |  |

| SY13         | Tioz               | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset <sup>(1)</sup> | 0.68                             | 0.72                                                  | 1.2 | μS | —                                                                                                       |  |  |

| SY20         | Twdt1              | Watchdog Timer Time-out<br>Period <sup>(1)</sup>                              | _                                | _                                                     | _   | ms | See <b>Section 19.4 "Watchdog</b><br><b>Timer (WDT)</b> " and LPRC<br>specification F21a (Table 22-19). |  |  |

| SY30         | Tost               | Oscillator Start-up Time                                                      | _                                | 1024<br>Tosc                                          | _   | —  | Tosc = OSC1 period                                                                                      |  |  |

| SY35         | TFSCM              | Fail-Safe Clock Monitor<br>Delay <sup>(1)</sup>                               | _                                | 500                                                   | 900 | μS | -40°C to +85°C                                                                                          |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

3: These parameters are characterized by similarity, but are not tested in manufacturing.

#### TABLE 22-28: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARAG            | CTERISTICS                               |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |  |

| 15 MHz               | Table 22-29                              | —                                           | _                                                     | 0,1 | 0,1 | 0,1 |  |  |

| 9 MHz                | _                                        | Table 22-30                                 | —                                                     | 1   | 0,1 | 1   |  |  |

| 9 MHz                | —                                        | Table 22-31                                 | —                                                     | 0   | 0,1 | 1   |  |  |

| 15 MHz               | —                                        | —                                           | Table 22-32                                           | 1   | 0   | 0   |  |  |

| 11 MHz               | —                                        | —                                           | Table 22-33                                           | 1   | 1   | 0   |  |  |

| 15 MHz               | _                                        | _                                           | Table 22-34                                           | 0   | 1   | 0   |  |  |

| 11 MHz               | _                                        | _                                           | Table 22-35                                           | 0   | 0   | 0   |  |  |

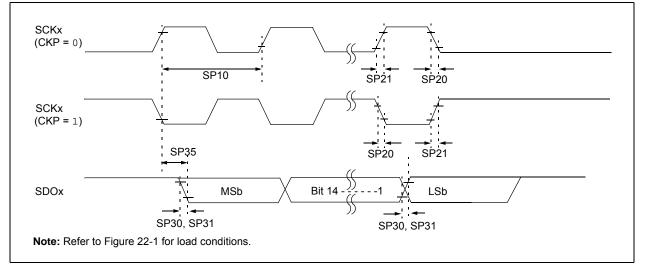

# FIGURE 22-9: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 0) TIMING CHARACTERISTICS

# TABLE 22-33:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       | AC CHARACTERISTICS    |                                                              |              | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |     |       |                                      |  |  |

|--------------|-----------------------|--------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------------------------|--|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                | Min          | Тур <sup>(2)</sup>                                                                                                                                                                                                                                                                   | Max | Units | Conditions                           |  |  |

| SP70         | TscP                  | Maximum SCK Input Frequency                                  | —            | _                                                                                                                                                                                                                                                                                    | 11  | MHz   | See Note 3                           |  |  |

| SP72         | TscF                  | SCKx Input Fall Time                                         | —            | _                                                                                                                                                                                                                                                                                    | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |  |

| SP73         | TscR                  | SCKx Input Rise Time                                         | —            |                                                                                                                                                                                                                                                                                      |     | ns    | See parameter DO31 and <b>Note 4</b> |  |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                   | _            | Ι                                                                                                                                                                                                                                                                                    | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                   | _            |                                                                                                                                                                                                                                                                                      | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —            | 6                                                                                                                                                                                                                                                                                    | 20  | ns    | —                                    |  |  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30           |                                                                                                                                                                                                                                                                                      | _   | ns    | —                                    |  |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30           | _                                                                                                                                                                                                                                                                                    | _   | ns    | —                                    |  |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30           | _                                                                                                                                                                                                                                                                                    | _   | ns    | —                                    |  |  |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120          | Ι                                                                                                                                                                                                                                                                                    | —   | ns    | —                                    |  |  |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup>        | 10           | —                                                                                                                                                                                                                                                                                    | 50  | ns    | —                                    |  |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40 | _                                                                                                                                                                                                                                                                                    |     | ns    | See Note 4                           |  |  |

| SP60         | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                     | —            | —                                                                                                                                                                                                                                                                                    | 50  | ns    | —                                    |  |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCK clock generated by the Master must not violate this specification.

**4:** Assumes 50 pF load on all SPIx pins.

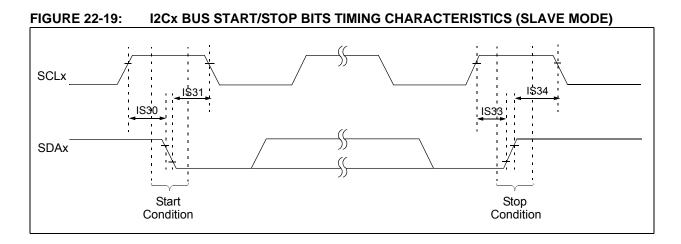

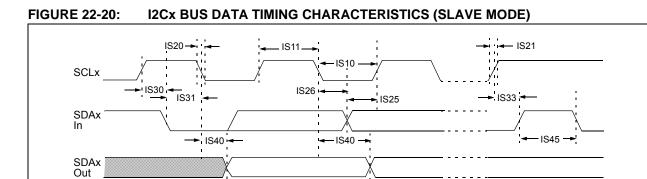

| AC CHA       | RACTER  | ISTICS                        |                           | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)                                                         |      |       |                        |  |  |

|--------------|---------|-------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------|--|--|

|              |         |                               |                           | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |       |                        |  |  |

| Param<br>No. | Symbol  | Characteristic <sup>(3)</sup> |                           | Min <sup>(1)</sup>                                                                                                               | Мах  | Units | Conditions             |  |  |

| IM10         | TLO:SCL | Clock Low Time                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  |      | μS    |                        |  |  |

|              |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  | _    | μS    | _                      |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                  | _    | μS    | _                      |  |  |

| IM11         | THI:SCL | Clock High Time               | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  |      | μS    | _                      |  |  |

|              |         | -                             | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  |      | μS    | _                      |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                  |      | μS    | —                      |  |  |

| IM20         | TF:SCL  | SDAx and SCLx                 | 100 kHz mode              |                                                                                                                                  | 300  | ns    | CB is specified to be  |  |  |

|              |         | Fall Time                     | 400 kHz mode              | 20 + 0.1 Св                                                                                                                      | 300  | ns    | from 10 to 400 pF      |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                | 100  | ns    |                        |  |  |

| IM21         | TR:SCL  | SDAx and SCLx                 | 100 kHz mode              | _                                                                                                                                | 1000 | ns    | CB is specified to be  |  |  |

|              |         | Rise Time                     | 400 kHz mode              | 20 + 0.1 Св                                                                                                                      | 300  | ns    | from 10 to 400 pF      |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                | 300  | ns    |                        |  |  |

| IM25         | TSU:DAT | Data Input                    | 100 kHz mode              | 250                                                                                                                              | —    | ns    | _                      |  |  |

|              |         | Setup Time                    | 400 kHz mode              | 100                                                                                                                              | _    | ns    |                        |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                               | _    | ns    | -                      |  |  |

| IM26         | THD:DAT | Data Input                    | 100 kHz mode              | 0                                                                                                                                | _    | μS    | _                      |  |  |

|              |         | Hold Time                     | 400 kHz mode              | 0                                                                                                                                | 0.9  | μS    |                        |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                              | _    | μS    |                        |  |  |

| IM30         | TSU:STA | Start Condition               | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  | _    | μS    | Only relevant for      |  |  |

|              |         | Setup Time                    | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  | _    | μS    | Repeated Start         |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                  | —    | μS    | condition              |  |  |

| IM31         | THD:STA | Start Condition               | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  | —    | μS    | After this period the  |  |  |

|              |         | Hold Time                     | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  | —    | μS    | first clock pulse is   |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                  | —    | μS    | generated              |  |  |

| IM33         | Tsu:sto | Stop Condition                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  | —    | μS    | _                      |  |  |

|              |         | Setup Time                    | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  | —    | μS    |                        |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                  | _    | μS    |                        |  |  |

| IM34         | THD:STO | Stop Condition                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  | _    | ns    | —                      |  |  |

|              |         | Hold Time                     | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                  | _    | ns    |                        |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                  | _    | ns    |                        |  |  |

| IM40         | TAA:SCL | Output Valid                  | 100 kHz mode              | _                                                                                                                                | 3500 | ns    | _                      |  |  |

|              |         | From Clock                    | 400 kHz mode              | —                                                                                                                                | 1000 | ns    | —                      |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                | 400  | ns    | —                      |  |  |

| IM45         | TBF:SDA | Bus Free Time                 | 100 kHz mode              | 4.7                                                                                                                              | —    | μs    | Time the bus must be   |  |  |

|              |         |                               | 400 kHz mode              | 1.3                                                                                                                              | —    | μs    | free before a new      |  |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                              | —    | μs    | transmission can start |  |  |

| IM50         | Св      | Bus Capacitive L              | oading                    | —                                                                                                                                | 400  | pF    | —                      |  |  |

| IM51         | TPGD    | Pulse Gobbler de              | lay                       | 65                                                                                                                               | 390  | ns    | See Note 4             |  |  |

#### TABLE 22-36: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

Note 1: BRG is the value of the I<sup>2</sup>C Baud Rate Generator. Refer to Section 19. "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70195) in the "dsPIC33F/PIC24H Family Reference Manual".

**2:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

3: These parameters are characterized by similarity, but are not tested in manufacturing.

**4:** Typical value for this parameter is 130 ns.

### TABLE 22-42: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                 |                                                                         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |         |       |                                      |  |

|--------------------|-----------------|-------------------------------------------------------------------------|-------------------------------------------------------|--------------------|---------|-------|--------------------------------------|--|

| Param<br>No.       | Symbol          | Characteristic                                                          | Min.                                                  | Typ <sup>(1)</sup> | Max.    | Units | Conditions                           |  |

|                    |                 | Cloc                                                                    | k Parame                                              | ters               |         |       |                                      |  |

| AD50               | TAD             | ADC Clock Period <sup>(1)</sup>                                         | 76                                                    | _                  | _       | ns    | —                                    |  |

| AD51               | tRC             | ADC Internal RC Oscillator<br>Period <sup>(1)</sup>                     | -                                                     | 250                | —       | ns    | _                                    |  |

|                    | Conversion Rate |                                                                         |                                                       |                    |         |       |                                      |  |

| AD55               | tCONV           | Conversion Time <sup>(1)</sup>                                          | _                                                     | 12 Tad             | _       | _     | —                                    |  |

| AD56               | FCNV            | Throughput Rate <sup>(1)</sup>                                          | —                                                     | —                  | 1.1     | Msps  | —                                    |  |

| AD57               | TSAMP           | Sample Time <sup>(1)</sup>                                              | 2.0 Tad                                               | —                  | —       | _     | —                                    |  |

|                    |                 | Timin                                                                   | g Param                                               | eters              |         |       |                                      |  |

| AD60               | tPCS            | Conversion Start from Sample<br>Trigger <sup>(1)</sup>                  | 2.0 Tad                                               |                    | 3.0 Tad |       | Auto-Convert Trigger<br>not selected |  |

| AD61               | tpss            | Sample Start from Setting<br>Sample (SAMP) bit <sup>(1)</sup>           | 2.0 Tad                                               | —                  | 3.0 Tad | _     | _                                    |  |

| AD62               | tcss            | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(1)</sup>      | —                                                     | 0.5 Tad            | —       | _     | —                                    |  |

| AD63               | tdpu            | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(1)</sup> | —                                                     | _                  | 20      | μS    | —                                    |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.