#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp204-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to  $\leq$  8 MHz for start-up with PLL enabled. This means that if the external oscillator frequency is outside this range, the application must start-up in FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

# 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL registers.

The bits in the registers that correspond to the A/D pins that are initialized by MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When the MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

# 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and the unused pins.

### 4.4.1 SOFTWARE STACK

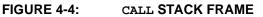

In addition to its use as a working register, the W15 register is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-4. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | concatenates the SRL register to the MSB |

|       | of the PC prior to the push.             |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. Similarly, the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word aligned.

When an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. For example, to cause a stack error trap when the stack grows beyond address 0x1000 in RAM, initialize the SPLIM with the value 0x0FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be lesser than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

## 4.4.2 DATA RAM PROTECTION FEATURE

The PIC24H product family supports Data RAM protection features that enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

## 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-23 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

## 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

## 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2 where:

Operand 1 is always a working register (that is, the addressing mode can only be register direct), which is referred to as Wb.

Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| REGISTER 7    | 7-5: IFS0: I                                                                                                                 | INTERRUPT                        | FLAG STAT        | US REGIST        | ER 0             |                 |                 |

|---------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|------------------|------------------|-----------------|-----------------|

| U-0           | U-0                                                                                                                          | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0           |

|               |                                                                                                                              | AD1IF                            | U1TXIF           | U1RXIF           | SPI1IF           | SPI1EIF         | T3IF            |

| bit 15        |                                                                                                                              |                                  |                  |                  |                  |                 | bit 8           |

|               |                                                                                                                              |                                  |                  |                  |                  |                 |                 |

| R/W-0<br>T2IF | R/W-0<br>OC2IF                                                                                                               | R/W-0<br>IC2IF                   | U-0              | R/W-0<br>T1IF    | R/W-0<br>OC1IF   | R/W-0<br>IC1IF  | R/W-0<br>INT0IF |

| bit 7         | UCZIF                                                                                                                        | ICZIF                            |                  |                  | OCTIF            |                 | bit C           |

|               |                                                                                                                              |                                  |                  |                  |                  |                 |                 |

| Legend:       | 1.11                                                                                                                         |                                  |                  |                  |                  | (0)             |                 |

| R = Readable  |                                                                                                                              | W = Writable                     |                  |                  | mented bit, read |                 |                 |

| -n = Value at | POR                                                                                                                          | '1' = Bit is set                 |                  | '0' = Bit is cle | ared             | x = Bit is unkn | own             |

| bit 15-4      | Unimplemen                                                                                                                   | ted: Read as '                   | 0'               |                  |                  |                 |                 |

| bit 13        | AD1IF: ADC1                                                                                                                  | Conversion C                     | complete Interi  | rupt Flag Statu  | s bit            |                 |                 |

|               | •                                                                                                                            | request has oc<br>request has no |                  |                  |                  |                 |                 |

| bit 12        | U1TXIF: UAR                                                                                                                  | RT1 Transmitte                   | r Interrupt Flag | g Status bit     |                  |                 |                 |

|               |                                                                                                                              | request has oc<br>request has no |                  |                  |                  |                 |                 |

| bit 11        | U1RXIF: UAF                                                                                                                  | RT1 Receiver I                   | nterrupt Flag S  | Status bit       |                  |                 |                 |

|               |                                                                                                                              | request has oc<br>request has no |                  |                  |                  |                 |                 |

| bit 10        | SPI1IF: SPI1                                                                                                                 | Event Interrup                   | t Flag Status b  | pit              |                  |                 |                 |

|               |                                                                                                                              | request has oc<br>request has no |                  |                  |                  |                 |                 |

| bit 9         | SPI1EIF: SPI                                                                                                                 | 1 Fault Interru                  | ot Flag Status   | bit              |                  |                 |                 |

|               |                                                                                                                              | request has oc<br>request has no |                  |                  |                  |                 |                 |

| bit 8         | -                                                                                                                            | Interrupt Flag                   |                  |                  |                  |                 |                 |

|               | 1 = Interrupt r                                                                                                              | request has oc<br>request has no | curred           |                  |                  |                 |                 |

| bit 7         | -                                                                                                                            | Interrupt Flag                   |                  |                  |                  |                 |                 |

|               |                                                                                                                              | request has oc                   |                  |                  |                  |                 |                 |

|               |                                                                                                                              | request has no                   |                  |                  |                  |                 |                 |

| bit 6         | -                                                                                                                            | ut Compare Ch                    |                  | upt Flag Status  | s bit            |                 |                 |

|               | •                                                                                                                            | request has oc<br>request has no |                  |                  |                  |                 |                 |

| bit 5         | <ul> <li>0 = Interrupt request has not occurred</li> <li>IC2IF: Input Capture Channel 2 Interrupt Flag Status bit</li> </ul> |                                  |                  |                  |                  |                 |                 |

|               |                                                                                                                              | request has oc<br>request has no |                  |                  |                  |                 |                 |

| bit 4         | Unimplemen                                                                                                                   | ted: Read as '                   | 0'               |                  |                  |                 |                 |

| bit 3         | T1IF: Timer1                                                                                                                 | Interrupt Flag                   | Status bit       |                  |                  |                 |                 |

|               | •                                                                                                                            | request has oc<br>request has no |                  |                  |                  |                 |                 |

| bit 2         | OC1IF: Output                                                                                                                | ut Compare Ch                    | annel 1 Interr   | upt Flag Status  | s bit            |                 |                 |

|               | 1 = Interrupt r<br>0 = Interrupt r                                                                                           | request has oc                   |                  |                  |                  |                 |                 |

# REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

## REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 1 | IC1IF: Input Capture Channel 1 | Interrupt Flag Status bit  |

|-------|--------------------------------|----------------------------|

|       | ion input oupture onumer i     | interrupt i lug otatao bit |

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

### INTOIF: External Interrupt 0 Flag Status bit

1 = Interrupt request has occurred

bit 0

0 = Interrupt request has not occurred

| U-0                 | U-0                                | U-0                                                       | U-0                                        | U-0              | U-0              | U-0                | U-0   |

|---------------------|------------------------------------|-----------------------------------------------------------|--------------------------------------------|------------------|------------------|--------------------|-------|

|                     | —                                  | _                                                         |                                            | —                | _                |                    |       |

| bit 15              |                                    |                                                           |                                            |                  |                  |                    | bit 8 |

| r                   |                                    |                                                           |                                            |                  |                  |                    |       |

| U-0                 | R/W-1                              | R/W-0                                                     | R/W-0                                      | U-0              | U-0              | U-0                | U-0   |

|                     |                                    | U1EIP<2:0>                                                |                                            |                  |                  |                    | —     |

| bit 7               |                                    |                                                           |                                            |                  |                  |                    | bit 0 |

| r                   |                                    |                                                           |                                            |                  |                  |                    |       |

| Legend:             |                                    |                                                           |                                            |                  |                  |                    |       |

| R = Readab          | le bit                             | W = Writable I                                            | oit                                        | U = Unimplen     | nented bit, read | as '0'             |       |

| -n = Value a        | t POR                              | '1' = Bit is set                                          |                                            | '0' = Bit is cle | ared             | x = Bit is unknown |       |

|                     |                                    |                                                           |                                            |                  |                  |                    |       |

|                     |                                    |                                                           |                                            |                  |                  |                    |       |

| bit 15-7            | Unimplemen                         | t <b>ed:</b> Read as 'd                                   | )'                                         |                  |                  |                    |       |

| bit 15-7<br>bit 6-4 | -                                  | t <b>ed:</b> Read as 'd<br>UART1 Error Ir                 |                                            | ity bits         |                  |                    |       |

|                     | U1EIP<2:0>:                        |                                                           | nterrupt Prior                             | •                |                  |                    |       |

|                     | U1EIP<2:0>:                        | UART1 Error Ir                                            | nterrupt Prior                             | •                |                  |                    |       |

|                     | U1EIP<2:0>:                        | UART1 Error Ir                                            | nterrupt Prior                             | •                |                  |                    |       |

|                     | U1EIP<2:0>:<br>111 = Interrup<br>• | UART1 Error Ir<br>ot is priority 7 (h                     | nterrupt Prior                             | •                |                  |                    |       |

|                     | U1EIP<2:0>:<br>111 = Interrup      | UART1 Error Ir<br>ot is priority 7 (h                     | nterrupt Prior<br>nighest priorit          | •                |                  |                    |       |

|                     | U1EIP<2:0>:<br>111 = Interrup      | UART1 Error Ir<br>ot is priority 7 (f<br>ot is priority 1 | nterrupt Prior<br>nighest priorit<br>abled | •                |                  |                    |       |

## REGISTER 7-18: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0             | U-0        | U-0              | U-0            | U-0              | U-0              | U-0                | R/W-0     |  |

|-----------------|------------|------------------|----------------|------------------|------------------|--------------------|-----------|--|

| —               | —          | —                |                | —                | —                |                    | PLLDIV<8> |  |

| bit 15          |            |                  |                |                  |                  |                    | bit 8     |  |

|                 |            |                  |                |                  |                  |                    |           |  |

| R/W-0           | R/W-0      | R/W-1            | R/W-1          | R/W-0            | R/W-0            | R/W-0              | R/W-0     |  |

|                 |            |                  | PLLDI          | V<7:0>           |                  |                    |           |  |

| bit 7           |            |                  |                |                  |                  |                    | bit 0     |  |

| Legend:         |            |                  |                |                  |                  |                    |           |  |

| R = Readable    | bit        | W = Writable I   | oit            | U = Unimpler     | mented bit, read | as '0'             |           |  |

| -n = Value at F |            | '1' = Bit is set |                | '0' = Bit is cle |                  | x = Bit is unknown |           |  |

|                 |            |                  |                |                  |                  |                    |           |  |

| bit 15-9        | Unimplemer | nted: Read as '0 | )'             |                  |                  |                    |           |  |

| bit 8-0         | PLLDIV<8:0 | >: PLL Feedbac   | k Divisor bits | (also denoted    | as 'M', PLL mult | tiplier)           |           |  |

|                 | 111111111  |                  |                |                  |                  | . ,                |           |  |

|                 | •          |                  |                |                  |                  |                    |           |  |

|                 | •          |                  |                |                  |                  |                    |           |  |

|                 | •          |                  |                |                  |                  |                    |           |  |

|                 | 000110000  | = 50 (default)   |                |                  |                  |                    |           |  |

|                 | •          |                  |                |                  |                  |                    |           |  |

|                 | •          |                  |                |                  |                  |                    |           |  |

|                 | •          |                  |                |                  |                  |                    |           |  |

|                 | 000000010  | = 4              |                |                  |                  |                    |           |  |

|                 | 00000001   |                  |                |                  |                  |                    |           |  |

|                 | 000000000  | = 2              |                |                  |                  |                    |           |  |

|                 |            |                  |                |                  |                  |                    |           |  |

# REGISTER 8-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

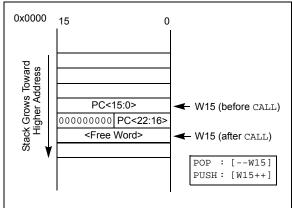

## FIGURE 18-3: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

# 18.3 ADC Helpful Tips

- 1. The SMPI<3:0> (AD1CON2<5:2>) control bits:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated if enabled.

- b) When the CSCNA bit (AD1CON2<10>) is set to '1', determines when the ADC analog scan channel list defined in the AD1CSSL/AD1CSSH registers starts over from the beginning.

- c) On devices without a DMA peripheral, determines when ADC result buffer pointer to ADC1BUF0-ADC1BUFF, gets reset back to the beginning at ADC1BUF0.

- On devices without a DMA module, the ADC has 2 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF regardless of which analog inputs are being used subject to the SMPI<3:0> bits (AD1CON2<5:2>) and the condition described in 1c above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- On devices with a DMA module, the ADC module has only 1 ADC result buffer, (i.e., ADC1BUF0), per ADC peripheral and the ADC conversion result must be read either by the CPU or DMA controller before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this

behavior because the CPU code execution is faster than the ADC. As a result, in manual sample mode, particularly where the users code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. On devices with two ADC modules, the ADCxPCFG registers for both ADC modules must be set to a logic '1' to configure a target I/O pin as a digital I/O pin. Failure to do so means that any alternate digital input function will always see only a logic '0' as the digital input buffer is held in Disable mode.

## 18.4 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en530271

### 18.4.1 KEY RESOURCES

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

### REGISTER 18-5: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

```

bit 4-0 CH0SA<4:0>: Channel 0 Positive Input Select for Sample A bits

PIC24HJ32GP204 and PIC24HJ16GP304 devices only:

01100 = Channel 0 positive input is AN12

.

.

00010 = Channel 0 positive input is AN2

00001 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN0

PIC24HJ32GP202 devices only:

01100 = Channel 0 positive input is AN12

.

.

01000 = Reserved

00111 = Reserved

00110 = Reserved

00110 = Reserved

.

.

00010 = Channel 0 positive input is AN2

00010 = Channel 0 positive input is AN1

00010 = Channel 0 positive input is AN1

```

#### 19.4 Watchdog Timer (WDT)

For PIC24HJ32GP202/204 and PIC24HJ16GP304 devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 19.4.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler than can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allows the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- · On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (Sleep or Idle mode is entered)

- · When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### WDT BLOCK DIAGRAM All Device Resets Transition to New Clock Source Exit Sleep or Idle Mode PWRSAV Instruction CLRWDT Instruction Watchdog Timer Sleep/Idle WDTPOST<3:0> WDTPRE SWDTEN WDT Wake-up FWDTEN 1 RS Prescaler Postscaler WDT LPRC Clock (divide by N1) (divide by N2) 0 Reset WDT Window Select WINDIS CLRWDT Instruction

### **FIGURE 19-2:**

#### SLEEP AND IDLE MODES 19.4.2

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3.2>) will need to be cleared in software after the device wakes up.

#### 19.4.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

If the WINDIS bit (FWDT<6>) is cleared, Note: the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before this window, a WDT Reset occurs.

# TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|------------------------------|---------------|----------------|--------------------------|

| 66                 | TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd        | 1             | 2              | None                     |

| 67                 | TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| 68                 | TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| 69                 | ULNK                 | ULNK   |                 | Unlink Frame Pointer         | 1             | 1              | None                     |

| 70                 | XOR                  | XOR    | f               | f = f .XOR. WREG             | 1             | 1              | N,Z                      |

|                    |                      | XOR    | f,WREG          | WREG = f .XOR. WREG          | 1             | 1              | N,Z                      |

|                    |                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd          | 1             | 1              | N,Z                      |

|                    |                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws             | 1             | 1              | N,Z                      |

|                    |                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5           | 1             | 1              | N,Z                      |

| 71                 | ZE                   | ZE     | Ws,Wnd          | Wnd = Zero-extend Ws         | 1             | 1              | C,Z,N                    |

# 22.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of PIC24HJ32GP202/204 and PIC24HJ16GP304 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24HJ32GP202/204 and PIC24HJ16GP304 family are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias40°C                                                      | C to +125°C  |

|-----------------------------------------------------------------------------------------|--------------|

| -65°C                                                                                   | C to +160°C  |

| -0.2 Voltage on VDD with respect to Vss                                                 | 3V to +4.0V  |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup> 0.3V to ( | Vdd + 0.3V)  |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(4)</sup> C     | ).3V to 3.6V |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(4)}$            | 3V to +5.6V  |

| Maximum current out of Vss pin                                                          | 300 mA       |

| Maximum current into VDD pin <sup>(2)</sup>                                             | 250 mA       |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                           | 8 mA         |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                           | 15 mA        |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                           | 25 mA        |

| Maximum current sunk by all ports                                                       | 200 mA       |

| Maximum current sourced by all ports <sup>(2)</sup>                                     | 200 mA       |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 22-2).

- 3: Exceptions are CLKOUT, which is able to sink/source 25 mA, and the VREF+, VREF-, SCLx, SDAx, PGECx and PGEDx pins, which are able to sink/source 12 mA.

- 4: Refer to the "Pin Diagrams" section for 5V tolerant pins.

| DC CHARACTERISTICS |        |                                         | (unless | •                  | se stated<br>rature - | )<br>∙40°C ≤ ` | <b>3.0V to 3.6V</b><br>TA $\leq$ +85°C for Industrial<br>TA $\leq$ +125°C for Extended                    |

|--------------------|--------|-----------------------------------------|---------|--------------------|-----------------------|----------------|-----------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                          | Min     | Typ <sup>(1)</sup> | Max                   | Units          | Conditions                                                                                                |

|                    | lı∟    | Input Leakage Current <sup>(2,3)</sup>  |         |                    |                       |                |                                                                                                           |

| DI50               |        | I/O Pins 5V Tolerant <sup>(4)</sup>     | —       | —                  | ±2                    | μA             | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                                             |

| DI51               |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | _       | _                  | ±1                    | μA             | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance,<br>-40°C \le TA \le +85°C                              |

| DI51a              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | _       | _                  | ±2                    | μΑ             | Shared with external reference pins, $-40^{\circ}C \le TA \le +85^{\circ}C$                               |

| DI51b              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | _       | _                  | ±3.5                  | μΑ             | $Vss \le VPIN \le VDD$ , Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                    |

| DI51c              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | _       | _                  | ±8                    | μA             | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$            |

| DI55               |        | MCLR                                    | _       | —                  | ±2                    | μA             | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                  |

| DI56               |        | OSC1                                    | _       | -                  | ±2                    | μA             | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$ |

## TABLE 22-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: See the "Pin Diagrams" section for a list of digital-only and analog pins.

- **5:** VIL source < (Vss 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5V or devices with USB, "D+" and "D-" VIH source > (VUSB + 0.3). Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

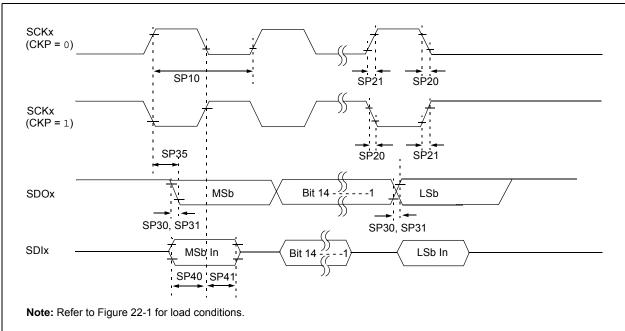

# FIGURE 22-12: SPIx MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 22-31:SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHA       | RACTERIST             | (unless o                                     | Operatin<br>otherwise<br>otemperat | <b>stated)</b><br>ture -40 | °C ≤ Ta ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |                                       |

|--------------|-----------------------|-----------------------------------------------|------------------------------------|----------------------------|-----------|-----------------------------------------------------------------|---------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                 | Min                                | Тур <sup>(2)</sup>         | Max       | Units                                                           | Conditions                            |

| SP10         | TscP                  | Maximum SCK Frequency                         | _                                  | —                          | 9         | MHz                                                             | -40°C to +125°C and see <b>Note 3</b> |

| SP20         | TscF                  | SCKx Output Fall Time                         | _                                  | —                          | _         | ns                                                              | See parameter DO32 and <b>Note 4</b>  |

| SP21         | TscR                  | SCKx Output Rise Time                         | _                                  | —                          | _         | ns                                                              | See parameter DO31 and <b>Note 4</b>  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                    | _                                  | —                          | _         | ns                                                              | See parameter DO32 and <b>Note 4</b>  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                    | _                                  | —                          | _         | ns                                                              | See parameter DO31 and <b>Note 4</b>  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge     | _                                  | 6                          | 20        | ns                                                              | _                                     |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                 | —                          | _         | ns                                                              | _                                     |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                 | —                          |           | ns                                                              | _                                     |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30                                 | —                          |           | ns                                                              | —                                     |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

# **Revision C (December 2008)**

This revision includes minor typographical and formatting changes throughout the data sheet text.

The major changes are referenced by their respective section in the following table.

### TABLE 25-2: MAJOR SECTION UPDATES

| Section Name                                                              | Update Description                                                                                                                                |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Microcontrollers"                            | Updated all pin diagrams to denote the pin voltage tolerance (see " <b>Pin Diagrams</b> ").                                                       |

| Section 2.0 "Guidelines for Getting Started with 16-bit Microcontrollers" | Added new section to the data sheet that provides guidelines on getting started with 16-bit microcontrollers.                                     |

| Section 10.0 "I/O Ports"                                                  | Updated 5V tolerant status for I/O pin RB4 from Yes to No (see Table 10-1).                                                                       |

| Section 22.0 "Electrical<br>Characteristics"                              | Removed the maximum value for parameter DC12 (RAM Data Retention Voltage) in Table 22-4.                                                          |

|                                                                           | Updated typical values for Operating Current (IDD) and added Note 3 in Table 22-5.                                                                |

|                                                                           | Updated typical and maximum values for Idle Current (IIDLE): Core OFF Clock ON Base Current and added Note 3 in Table 22-6.                       |

|                                                                           | Updated typical and maximum values for Power Down Current (IPD) and added Note 5 in Table 22-7.                                                   |

|                                                                           | Updated typical and maximum values for Doze Current (IDOZE) and added Note 2 in Table 22-8.                                                       |

|                                                                           | Added Note 3 to Table 22-12.                                                                                                                      |

|                                                                           | Updated minimum value for Internal Voltage Regulator Specifications in Table 22-13.                                                               |

|                                                                           | Added parameter OS42 (GM) and Notes 4, 5, and 6 to Table 22-16.                                                                                   |

|                                                                           | Added Notes 2 and 3 to Table 22-17.                                                                                                               |

|                                                                           | Added Note 2 to Table 22-20.                                                                                                                      |

|                                                                           | Added Note 2 to Table 22-21.                                                                                                                      |

|                                                                           | Added Note 2 to Table 22-22.                                                                                                                      |

|                                                                           | Added Note 1 to Table 22-23.                                                                                                                      |

|                                                                           | Added Note 1 to Table 22-24.                                                                                                                      |

|                                                                           | Added Note 3 to Table 22-32.                                                                                                                      |

|                                                                           | Added Note 2 to Table 22-33.                                                                                                                      |

|                                                                           | Updated typical value for parameter AD08 (ADC in operation) and added Notes 2 and 3 in Table 22-34.                                               |

|                                                                           | Updated minimum, typical, and maximum values for parameters AD23a, AD24a, AD30a, AD32a, AD32a, and AD34a, and added Notes 2 and 3 in Table 22-35. |

|                                                                           | Updated minimum, typical, and maximum values for parameters AD23b, AD24b, AD30b, AD32b, AD32b, and AD34b, and added Notes 2 and 3 in Table 22-36. |

# Revision D (June 2009)

This revision includes minor typographical and formatting changes throughout the data sheet text.

Global changes include:

- Changed all instances of OSCI to OSC1 and OSCO to OSC2

- Changed all instances of PGCx/EMUCx and PGDx/EMUDx (where x = 1, 2, or 3) to PGECx and PGEDx

Changed all instances of VDDCORE and VDDCORE/VCAP to VCAP/VDDCORE

All other major changes are referenced by their respective section in the following table.

### TABLE 25-3: MAJOR SECTION UPDATES

| Section Name                                                         | Update Description                                                                                                                                         |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Microcontrollers"                       | Added Note 2 to the 28-Pin QFN-S and 44-Pin QFN pin diagrams, which references pin connections to Vss.                                                     |

| Section 8.0 "Oscillator Configuration"                               | Updated the Oscillator System Diagram (see Figure 8-1).                                                                                                    |

|                                                                      | Added Note 1 to the Oscillator Tuning (OSCTUN) register (see Register 8-4).                                                                                |

| Section 10.0 "I/O Ports"                                             | Removed Table 10-1 and added reference to pin diagrams for I/O pin availability and functionality.                                                         |

| Section 15.0 "Serial Peripheral Interface (SPI)"                     | Added Note 2 to the SPIx Control Register 1 (see Register 15-2).                                                                                           |

| Section 17.0 "Universal Asynchronous<br>Receiver Transmitter (UART)" | Updated the UTXINV bit settings in the UxSTA register and added Note 1 (see Register 17-2).                                                                |

| Section 22.0 "Electrical Characteristics"                            | Updated the Min value for parameter DC12 (RAM Retention Voltage)<br>and added Note 4 to the DC Temperature and Voltage Specifications<br>(see Table 22-4). |

|                                                                      | Updated the Min value for parameter DI35 (see Table 22-20).                                                                                                |

|                                                                      | Updated AD08 and added reference to Note 2 for parameters AD05a, AD06a, and AD08a (see Table 22-34).                                                       |

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE:                  | Technical Publications Manager<br>Reader Response                                        | Total Pages Sent            |  |

|-----------------------------|------------------------------------------------------------------------------------------|-----------------------------|--|

| From                        | n: Name                                                                                  |                             |  |

|                             | Company                                                                                  |                             |  |

|                             | Address                                                                                  |                             |  |

|                             | City / State / ZIP / Country                                                             |                             |  |

|                             | Telephone: ()                                                                            | FAX: ()                     |  |

| Application (optional):     |                                                                                          |                             |  |

| Would you like a reply? Y N |                                                                                          |                             |  |

| Devi                        | ce: PIC24HJ32GP202/204 and PIC24HJ16GP304                                                | Literature Number: DS70289J |  |

| Questions:                  |                                                                                          |                             |  |

| 1.                          | 1. What are the best features of this document?                                          |                             |  |

| 2                           | . How does this document meet your hardware and software development needs?              |                             |  |

| ۲.                          |                                                                                          |                             |  |

| -                           |                                                                                          |                             |  |

| 3.                          | Do you find the organization of this document easy to follow? If not, why?               |                             |  |

| -                           |                                                                                          |                             |  |

| 4.                          | What additions to the document do you think would enhance the structure and subject?     |                             |  |

| -                           |                                                                                          |                             |  |

| 5.                          | What deletions from the document could be made without affecting the overall usefulness? |                             |  |

| -                           |                                                                                          |                             |  |

| 6.                          | Is there any incorrect or misleading information (what and where)?                       |                             |  |

|                             |                                                                                          |                             |  |

| 7.                          | How would you improve this document?                                                     |                             |  |

|                             |                                                                                          |                             |  |

|                             |                                                                                          |                             |  |

NOTES:

### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007-2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

### ISBN: 978-1-62076-440-4

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.