Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp204t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# DS70289J-page 30

#### TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR PIC24HJ32GP202

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|--------|-------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  |        | _     | —       | CN7IE   | CN6IE   | CN5IE   | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE   | 0000          |

| CNEN2       | 0062        | _       | CN30IE  | CN29IE  | _       | CN27IE  |        | _     | CN24IE  | CN23IE  | CN22IE  | CN21IE  |        |        |        | _      | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE |        | _     | _       | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE | CN3PUE | CN2PUE | CN1PUE | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | CN30PUE | CN29PUE | _       | CN27PUE | _      |       | CN24PUE | CN23PUE | CN22PUE | CN21PUE | _      | _      | _      | _      | CN16PUE | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR PIC24HJ32GP204 AND PIC24HJ16GP304

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE   | CN8IE   | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | —       | CN30IE  | CN29IE  | CN28IE  | CN27IE  | CN26IE  | CN25IE  | CN24IE  | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE  | CN8PUE  | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | CN30PUE | CN29PUE | CN28PUE | CN27PUE | CN26PUE | CN25PUE | CN24PUE | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

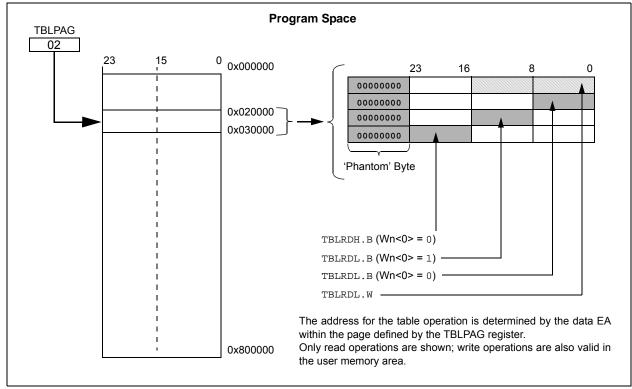

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method to read or write the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only methods to read or write the upper 8 bits of a program space word as data.

The PC is incremented by 2 for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16 bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word sized (16-bit) data to and from program space. Both function as either byte or word operations.

• TBLRDL (Table Read Low): In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

• TBLRDH (Table Read High): In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, as in the TBLRDL instruction. Note that the data will always be '0' when the upper 'Phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

# FIGURE 4-6: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

#### REGISTER 7-8: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 1 | IC1IE: Input Capture Channel 1 Interrupt Enable bit |

|-------|-----------------------------------------------------|

|-------|-----------------------------------------------------|

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- INTOIE: External Interrupt 0 Enable bit

- 1 = Interrupt request enabled

bit 0

0 = Interrupt request not enabled

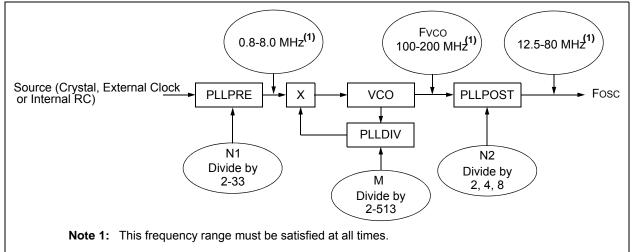

For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by:

# EQUATION 8-2: Fosc CALCULATION

$$FOSC = FIN \cdot \left(\frac{M}{N1 \cdot N2}\right)$$

For example, when a 10 MHz crystal is being used, with "XT with PLL" being the selected oscillator mode.

• If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz.

- If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 x 32 = 160 MHz, which is within the 100 MHz to 200 MHz range, which is needed.

- If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

EQUATION 8-3: XT WITH PLL MODE EXAMPLE

$$F_{CY} = \frac{F_{OSC}}{2} = \frac{1}{2} \cdot \left(\frac{10000000 \cdot 32}{2 \cdot 2}\right) = 40 \text{ MIPS}$$

## FIGURE 8-2: PIC24HJ32GP202/204 AND PIC24HJ16GP304 PLL BLOCK DIAGRAM

#### TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                  | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See Note |

|--------------------------------------------------|-------------------|-------------|------------|----------|

| Fast RC Oscillator with Divide-by-N<br>(FRCDIVN) | Internal          | xx          | 111        | 1, 2     |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)  | Internal          | XX          | 110        | 1        |

| Low-Power RC Oscillator (LPRC)                   | Internal          | XX          | 101        | 1        |

| Secondary (Timer1) Oscillator (SOSC)             | Secondary         | XX          | 100        | 1        |

| Primary Oscillator (HS) with PLL<br>(HSPLL)      | Primary           | 10          | 011        | _        |

| Primary Oscillator (XT) with PLL<br>(XTPLL)      | Primary           | 01          | 011        | -        |

| Primary Oscillator (EC) with PLL<br>(ECPLL)      | Primary           | 00          | 011        | 1        |

| Primary Oscillator (HS)                          | Primary           | 10          | 010        | _        |

| Primary Oscillator (XT)                          | Primary           | 01          | 010        | _        |

| Primary Oscillator (EC)                          | Primary           | 00          | 010        | 1        |

| Fast RC Oscillator with PLL (FRCPLL)             | Internal          | xx          | 001        | 1        |

| Fast RC Oscillator (FRC)                         | Internal          | xx          | 000        | 1        |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

## 8.4 Clock Switching Operation

Applications are free to switch among any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects of this flexibility, devices have a safeguard lock built into the switch process.

| Note: | Primary Oscillator mode has three different |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | submodes (XT, HS and EC), which are         |  |  |  |  |  |  |  |  |  |

|       | determined by the POSCMD<1:0>               |  |  |  |  |  |  |  |  |  |

|       | Configuration bits. While an application    |  |  |  |  |  |  |  |  |  |

|       | can switch to and from Primary Oscillator   |  |  |  |  |  |  |  |  |  |

|       | mode in software, it cannot switch among    |  |  |  |  |  |  |  |  |  |

|       | the different primary submodes without      |  |  |  |  |  |  |  |  |  |

|       | reprogramming the device.                   |  |  |  |  |  |  |  |  |  |

#### 8.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 19.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

#### 8.4.2 OSCILLATOR SWITCHING SEQUENCE

Performing a clock switch requires the following basic sequence:

- Read the COSC bits (OSCCON<14:12>) to determine the current oscillator source, if desired.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

1. The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If both of them are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the status bits, LOCK (OSCCON<5>) and CF (OSCCON<3>) are cleared.

- 3. The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator has to be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRC-PLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

# 8.5 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

## 10.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Pin Diagrams"** section for the available pins and their functionality.

# 10.3 Configuring Analog Port Pins

The AD1PCFG and TRIS registers control the operation of the Analog-to-Digital (A/D) port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The AD1PCFGL register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORT register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

# 10.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP. Examples are shown in Example 10-1 and Example 10-2. This also applies to PORT bit operations, such as BSET PORTB, # RB0, which are single cycle read-modify-write. All PORT bit operations, such as MOV PORTB, W0 or BSET PORTB, # RBx, read the pin and *not* the latch.

# 10.5 Input Change Notification

The input change notification function of the I/O ports allows the PIC24HJ32GP202/204 and PIC24HJ16GP304 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 31 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a change-of-state.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on change notification pins should always be disabled when the port pin is configured as a digital output.

#### EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> as inputs |

|------|------------|-----------------------------------|

| MOV  | W0, TRISBB | ; and PORTB<7:0> as outputs       |

| NOP  |            | ; Delay 1 cycle                   |

| btss | PORTB, #13 | ; Next Instruction                |

#### EXAMPLE 10-2: PORT BIT OPERATIONS

| PORTB,  | #RB1                                | ;Set                                      | PORTB <rb1></rb1>                                                            | high                                                                                                                                               |

|---------|-------------------------------------|-------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| PORTB,  | #RB6                                | ;Set                                      | PORTB <rb6></rb6>                                                            | high                                                                                                                                               |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

| PORTB,  | #RB1                                | ;Set                                      | PORTB <rb1></rb1>                                                            | high                                                                                                                                               |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

| PORTB,  | #RB6                                | ;Set                                      | PORTB <rb6></rb6>                                                            | high                                                                                                                                               |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

| LATB, 1 | LATB1                               | ;Set                                      | PORTB <rb1></rb1>                                                            | high                                                                                                                                               |

| LATB, 1 | latb6                               | ;Set                                      | PORTB <rb6></rb6>                                                            | high                                                                                                                                               |

|         | PORTB,<br>PORTB,<br>PORTB,<br>LATB, | PORTB, #RB6<br>PORTB, #RB1<br>PORTB, #RB6 | PORTB, #RB6 ;Set<br>PORTB, #RB1 ;Set<br>PORTB, #RB6 ;Set<br>LATB, LATB1 ;Set | <pre>PORTE, #RB6 ;Set PORTB<rb6> PORTE, #RB1 ;Set PORTB<rb1> PORTE, #RB6 ;Set PORTB<rb6> LATE, LATB1 ;Set PORTB<rb1></rb1></rb6></rb1></rb6></pre> |

| U-0          | U-0       | U-0                              | R/W-1   | R/W-1                                   | R/W-1                                   | R/W-1              | R/W-1   |  |

|--------------|-----------|----------------------------------|---------|-----------------------------------------|-----------------------------------------|--------------------|---------|--|

| 0-0          | 0-0       |                                  | 10/00-1 | 10/00-1                                 | INT1R<4:0>                              |                    | 10/00-1 |  |

|              | _         |                                  |         |                                         | 111111111111111111111111111111111111111 |                    | L : L : |  |

| bit 15       |           |                                  |         |                                         |                                         |                    | bit 8   |  |

|              |           |                                  |         |                                         |                                         |                    |         |  |

| U-0          | U-0       | U-0                              | U-0     | U-0                                     | U-0                                     | U-0                | U-0     |  |

| —            | _         | —                                | —       | _                                       | —                                       | —                  | —       |  |

| bit 7        |           |                                  |         |                                         |                                         |                    | bit C   |  |

|              |           |                                  |         |                                         |                                         |                    |         |  |

| Legend:      |           |                                  |         |                                         |                                         |                    |         |  |

| R = Readab   | le bit    | W = Writable                     | bit     | U = Unimple                             | mented bit, read                        | d as '0'           |         |  |

| -n = Value a | t POR     | '1' = Bit is set                 |         | '0' = Bit is cle                        | eared                                   | x = Bit is unknown |         |  |

|              |           |                                  |         |                                         |                                         |                    |         |  |

| bit 15-13    | Unimpleme | nted: Read as '                  | 0'      |                                         |                                         |                    |         |  |

| bit 12-8     | -         | : Assign Externa                 |         | (INTR1) to the                          | corresponding                           | RPn pin            |         |  |

|              |           | ut tied to Vss                   |         | , , , , , , , , , , , , , , , , , , , , | 5                                       | r                  |         |  |

|              |           | ut tied to RP25                  |         |                                         |                                         |                    |         |  |

|              | •         |                                  |         |                                         |                                         |                    |         |  |

|              | •         |                                  |         |                                         |                                         |                    |         |  |

|              | •         |                                  |         |                                         |                                         |                    |         |  |

|              |           | ut tied to RP1<br>ut tied to RP0 |         |                                         |                                         |                    |         |  |

#### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| bit 7-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

#### REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0   |

|-------|

|       |

|       |

| bit 8 |

|       |

| R/W-1 |

|       |

| bit 0 |

|       |

|       |

|       |

| nown  |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

#### REGISTER 10-15: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

|        | —   | _   |       |       | RP11R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

|        |     |     |       |       |            |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

| —       | — — — RP10R<4:0> |         |  |       |  |  |  |  |  |

|---------|------------------|---------|--|-------|--|--|--|--|--|

| bit 7   |                  | · · · · |  | bit 0 |  |  |  |  |  |

|         |                  |         |  |       |  |  |  |  |  |

| Legend: |                  |         |  |       |  |  |  |  |  |

|         | ••               |         |  |       |  |  |  |  |  |

| J                                 |                              |                        |                                    |  |  |  |  |

|-----------------------------------|------------------------------|------------------------|------------------------------------|--|--|--|--|

| R = Readable bit W = Writable bit |                              | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR                 | alue at POR '1' = Bit is set |                        | x = Bit is unknown                 |  |  |  |  |

#### bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-16: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0          | U-0        | U-0                            | R/W-0 | R/W-0            | R/W-0           | R/W-0            | R/W-0   |

|--------------|------------|--------------------------------|-------|------------------|-----------------|------------------|---------|

| _            | _          | —                              |       |                  | RP13R<4:0>      | >                |         |

| bit 15       | ·          |                                |       |                  |                 |                  | bit 8   |

|              |            |                                |       |                  |                 |                  |         |

| U-0          | U-0        | U-0                            | R/W-0 | R/W-0            | R/W-0           | R/W-0            | R/W-0   |

| _            | —          | —                              |       |                  | RP12R<4:0>      | >                |         |

| bit 7        |            |                                |       |                  |                 |                  | bit 0   |

|              |            |                                |       |                  |                 |                  |         |

| Legend:      |            |                                |       |                  |                 |                  |         |

| R = Readab   | le bit     | W = Writable I                 | oit   | U = Unimpler     | nented bit, rea | d as '0'         |         |

| -n = Value a | t POR      | '1' = Bit is set               |       | '0' = Bit is cle | ared            | x = Bit is unkr  | nown    |

|              |            |                                |       |                  |                 |                  |         |

| bit 15-13    | Unimplemen | ted: Read as 'd                | )'    |                  |                 |                  |         |

| bit 12-8     |            | : Peripheral Ounction numbers) | -     | n is Assigned to | RP13 Output     | Pin (see Table 1 | 0-2 for |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP12R<4:0>:** Peripheral Output Function is Assigned to RP12 Output Pin (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-19: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0  | U-0  | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|------|------|------------|-------|-------|-------|-------|--|--|

| —      | —    | —    | RP19R<4:0> |       |       |       |       |  |  |

| bit 15 |      |      |            |       |       |       | bit 8 |  |  |

|        |      |      |            |       |       |       |       |  |  |

| 11_0   | 11_0 | 11.0 |            |       |       |       |       |  |  |

| 0-0   | 0-0 | 0-0 | 10/00-0 | 10.00-0 | 10/00-0    | 10/00-0 | 10/00-0 |

|-------|-----|-----|---------|---------|------------|---------|---------|

| —     | —   | —   |         |         | RP18R<4:0> |         |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

|       |     |     |         |         |            |         |         |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP19R<4:0>:** Peripheral Output Function is Assigned to RP19 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP18R<4:0>:** Peripheral Output Function is Assigned to RP18 Output Pin (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-20: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10

| U-0                                |     |                |                                         |                                    |           |       |       |  |

|------------------------------------|-----|----------------|-----------------------------------------|------------------------------------|-----------|-------|-------|--|

|                                    | U-0 | U-0            | R/W-0                                   | R/W-0                              | R/W-0     | R/W-0 | R/W-0 |  |

| —                                  |     | —              |                                         |                                    | RP21R<4:0 | >     |       |  |

| bit 15                             |     |                |                                         |                                    |           |       | bit 8 |  |

| U-0                                | U-0 | U-0            | R/W-0                                   | R/W-0                              | R/W-0     | R/W-0 | R/W-0 |  |

|                                    | _   |                |                                         |                                    | RP20R<4:0 | >     |       |  |

| bit 7                              |     | ·              |                                         |                                    |           |       | bit 0 |  |

| Legend:                            |     |                |                                         |                                    |           |       |       |  |

| R = Readable b                     | oit | W = Writable I | oit                                     | U = Unimplemented bit, read as '0' |           |       |       |  |

| -n = Value at POR '1' = Bit is set |     |                | '0' = Bit is cleared x = Bit is unknown |                                    |           | nown  |       |  |

bit 12-8 **RP21R<4:0>:** Peripheral Output Function is Assigned to RP21 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP20R<4:0>:** Peripheral Output Function is Assigned to RP20 Output Pin (see Table 10-2 for peripheral function numbers)

NOTES:

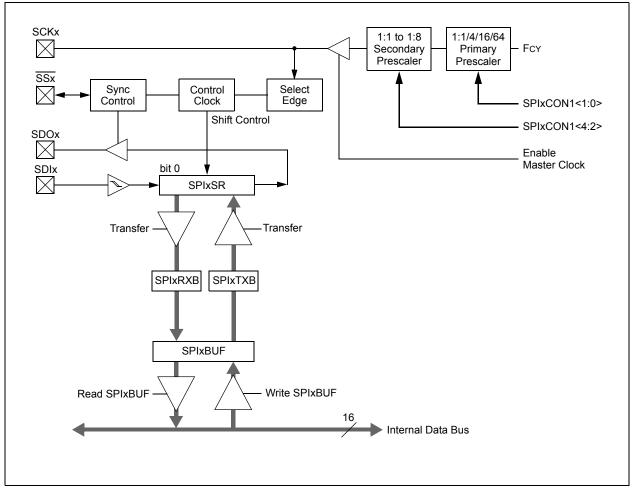

# 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 18. Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters (ADCs), and so on. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of these four pins:

- · SDIx (serial data input)

- · SDOx (serial data output)

- SCKx (shift clock input or output)

- SSx (active-low slave select)

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

#### FIGURE 15-1: SPI MODULE BLOCK DIAGRAM

# 16.2 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|--|--|

|       | the product page using the link above,  |  |  |  |  |  |  |  |  |  |

|       | enter this URL in your browser:         |  |  |  |  |  |  |  |  |  |

|       | http://www.microchip.com/wwwproducts/   |  |  |  |  |  |  |  |  |  |

|       | Devices.aspx?dDocName=en530271          |  |  |  |  |  |  |  |  |  |

#### 16.2.1 KEY RESOURCES

- Section 13. "Inter-Integrated Circuit™ (I2C™)" (DS70195)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 16.3 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

- · I2CxRSR is the shift register used for shifting data

- I2CxRCV is the receive buffer and the register to which data bytes are written, or from which data bytes are read

- I2CxTRN is the transmit register to which bytes are written during a transmit operation

- The I2CxADD register holds the slave address

- A status bit, ADD10, indicates 10-bit Address mode

- I2CxBRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV, and an interrupt pulse is generated.

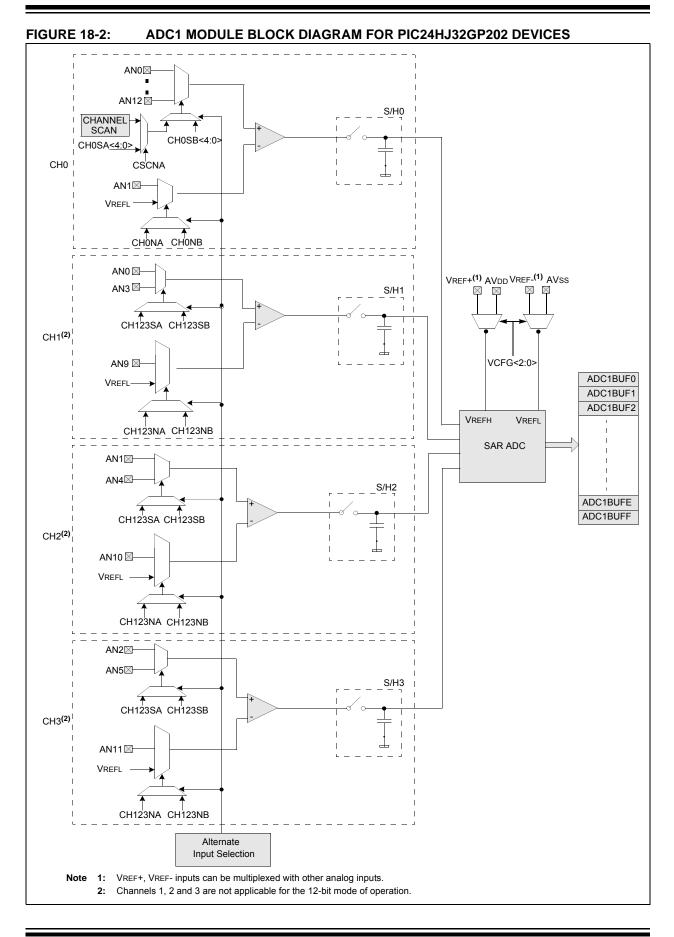

#### REGISTER 18-5: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

```

bit 4-0 CH0SA<4:0>: Channel 0 Positive Input Select for Sample A bits

PIC24HJ32GP204 and PIC24HJ16GP304 devices only:

01100 = Channel 0 positive input is AN12

.

.

00010 = Channel 0 positive input is AN2

00001 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN0

PIC24HJ32GP202 devices only:

01100 = Channel 0 positive input is AN12

.

.

01000 = Reserved

00111 = Reserved

00110 = Reserved

00110 = Reserved

.

.

00010 = Channel 0 positive input is AN2

00010 = Channel 0 positive input is AN1

00010 = Channel 0 positive input is AN1

```

NOTES:

#### TABLE 22-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| (unless o    | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                 |     |     |     |       |          |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|-------|----------|--|--|--|--|

| Param<br>No. | Symbol                                                                                                                                                                                               | Characteristics | Min | Тур | Max | Units | Comments |  |  |  |  |

|              | —     CEFC     External Filter Capacitor     4.7     10     —     μF     Capacitor must be low series resistance (< 5 ohms)                                                                          |                 |     |     |     |       |          |  |  |  |  |

**Note 1:** Typical VCAP voltage = 2.5V when  $VDD \ge VDDMIN$ .

## 22.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC24HJ32GP202/204 and PIC24HJ16GP304 AC characteristics and timing parameters.

#### TABLE 22-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)    |

|--------------------|-----------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |

|                    | $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended                        |

|                    | Operating voltage VDD range as described in Table 22-1.                     |

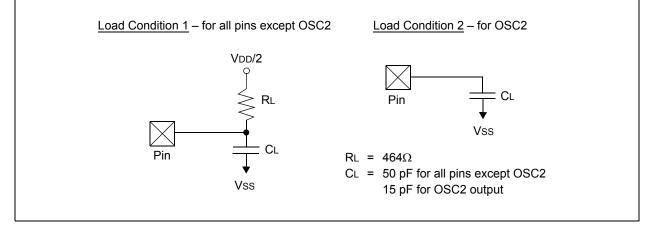

#### FIGURE 22-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 22-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Тур | Max | Units | Conditions                                                         |

|--------------|--------|-----------------------|-----|-----|-----|-------|--------------------------------------------------------------------|

| DO50         | Cosc2  | OSC2/SOSC2 pin        | _   | _   | 15  |       | In XT and HS modes when<br>external clock is used to drive<br>OSC1 |

| DO56         | Cio    | All I/O pins and OSC2 | —   | —   | 50  | pF    | EC mode                                                            |

| DO58         | Св     | SCLx, SDAx            |     | —   | 400 | pF    | In I <sup>2</sup> C™ mode                                          |

| TADLL        | ABLE 25-12. SPIX MODULE SLAVE MODE (CRE = 0) HIMING REQUIREMENTS |                                                              |     |     |     |       |            |  |  |

|--------------|------------------------------------------------------------------|--------------------------------------------------------------|-----|-----|-----|-------|------------|--|--|

| CHARA        | AC<br>CTERISTICS                                                 | Standard Operating Conditions<br>Operating temperature -40°C |     |     |     |       |            |  |  |

| Param<br>No. | Symbol                                                           | Characteristic <sup>(1)</sup>                                | Min | Тур | Max | Units | Conditions |  |  |

| HSP35        | TscH2doV,<br>TscL2doV                                            | SDOx Data Output Valid after<br>SCKx Edge                    |     | _   | 35  | ns    | _          |  |  |

| HSP40        | TdiV2scH,<br>TdiV2scL                                            | Setup Time of SDIx Data Input to SCKx Edge                   | 25  | —   | —   | ns    | _          |  |  |

| HSP41        | TscH2diL,<br>TscL2diL                                            | Hold Time of SDIx Data Input to SCKx Edge                    | 25  | —   | —   | ns    | _          |  |  |

| HSP51        | TssH2doZ                                                         | SSx ↑ to SDOx Output<br>High-Impedance                       | 15  | _   | 55  | ns    | See Note 2 |  |  |

# TABLE 23-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

**2:** Assumes 50 pF load on all SPIx pins.

#### TABLE 23-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC<br>CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |  |

|-----------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|--|

| Param<br>No.          | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |  |  |

| HSP35                 | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               | _   |     | 35  | ns    | —          |  |  |

| HSP40                 | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 25  | _   |     | ns    | _          |  |  |

| HSP41                 | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                               | 25  |     |     | ns    |            |  |  |

| HSP51                 | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                                                                                                  | 15  | _   | 55  | ns    | See Note 2 |  |  |

| HSP60                 | TssL2doV              | <u>SDO</u> x Data Output Valid after<br>SSx Edge                                                                                                        | —   |     | 55  | ns    |            |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Assumes 50 pF load on all SPIx pins.

#### TABLE 23-14: INTERNAL RC ACCURACY

| AC CH        | ARACTERISTICS                      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for Extended |     |     |       |                                        |                |  |

|--------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|----------------------------------------|----------------|--|

| Param<br>No. | Characteristic                     | Min                                                                                                                                             | Тур | Max | Units | Condit                                 | ions           |  |

|              | LPRC @ 32.768 kHz <sup>(1,2)</sup> |                                                                                                                                                 |     |     |       |                                        |                |  |

| HF21         | LPRC                               | -70                                                                                                                                             | _   | +70 | %     | $-40^\circ C \le T A \le +150^\circ C$ | VDD = 3.0-3.6V |  |

**Note 1:** Change of LPRC frequency as VDD changes.

2: LPRC accuracy impacts the Watchdog Timer Time-out Period (TWDT1). See Section 19.4 "Watchdog Timer (WDT)" for more information.

| Section Name                                               | Update Description                                                                                                                                          |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Section 22.0 "Electrical Characteristics"                  | Added 28-pin SSOP Thermal Packaging Characteristics (see Table 22-3).                                                                                       |  |

|                                                            | Removed Note 4 from the DC Temperature and Voltage Specifications (see Table 22-4).                                                                         |  |

|                                                            | Updated the maximum value for parameter DI19 and added parameters DI28, DI29, DI60a, DI60b, and DI60c to the I/O Pin Input Specifications (see Table 22-9). |  |

|                                                            | Updated Note 3 in the PLL Clock Timing Specifications (see Table 22-17).                                                                                    |  |

|                                                            | Removed Note 2 from the AC Characteristics: Internal RC Accuracy (see Table 22-18).                                                                         |  |

|                                                            | Updated the characteristic description for parameter DI35 in the I/O Timing Requirements (see Table 22-20).                                                 |  |

|                                                            | Updated <i>all</i> SPI specifications (see Table 22-28 through Table 22-35 and Figure 22-10 through Figure 22-16).                                          |  |

|                                                            | Added Note 4 to the 12-bit ADC Module Specifications (see Table 22-39).                                                                                     |  |

|                                                            | Added Note 4 to the 10-bit ADC Module Specifications (see Table 22-40).                                                                                     |  |

| Section 23.0 "High Temperature Electrical Characteristics" | Updated all ambient temperature end range values to +150°C throughout the chapter.                                                                          |  |

|                                                            | Updated the storage temperature end range to +160°C.                                                                                                        |  |

|                                                            | Updated the maximum junction temperature from +145°C to +155°C.                                                                                             |  |

|                                                            | Updated Note 1 in the PLL Clock Timing Specifications (see Table 23-10).                                                                                    |  |

|                                                            | Added Note 3 to the 12-bit Mode ADC Module Specifications (see Table 23-17).                                                                                |  |

|                                                            | Added Note 3 to the 10-bit Mode ADC Module Specifications (see Table 23-18).                                                                                |  |

| Section 24.0 "Packaging Information"                       | Added the 28-Lead SSOP package information (see Section 24.1<br>"Package Marking Information" and Section 24.2 "Package Details").                          |  |

| "Product Identification System"                            | Added the "SS" definition for the SSOP package.                                                                                                             |  |

# TABLE A-2: MAJOR SECTION UPDATES (CONTINUED)

# Revision H (July 2011)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

## TABLE A-3: MAJOR SECTION UPDATES

| Section Name                              | Update Description                                                                                                                 |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Section 19.0 "Special Features"           | Added Note 3 to the Connections for the On-chip Voltage Regulator diagram (see Figure 19-1).                                       |

| Section 22.0 "Electrical Characteristics" | Removed Note 3 and parameter DC10 (VCORE) from the DC Temperature and Voltage Specifications (see Table 22-4).                     |

|                                           | Updated the Characteristics definition and Conditions for parameter BO10 in the Electrical Characteristics: BOR (see Table 22-11). |

|                                           | Added Note 1 to the Internal Voltage Regulator Specifications (see Table 22-13).                                                   |

# Revision J (July 2012)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

#### TABLE A-4: MAJOR SECTION UPDATES

| Section Name                                               | Update Description                                                                                                      |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Section 22.0 "Electrical Characteristics"                  | Added Note 1 to the Operating MIPS vs. Voltage (see Table 22-1).                                                        |

|                                                            | Updated the notes in the following tables:                                                                              |

|                                                            | Operating Current (IDD) (see Table 22-5)                                                                                |

|                                                            | Idle Current (IIDLE) (see Table 22-6)                                                                                   |

|                                                            | Power-Down Current (IPD) (see Table 22-7)                                                                               |

|                                                            | Doze Current (IDOZE) (see Table 22-8)                                                                                   |

|                                                            | Updated the conditions for Program Memory parameters D136b, D137b, and D138b (TA = $+150^{\circ}$ C) (see Table 22-12). |

| Section 23.0 "High Temperature Electrical Characteristics" | Removed Table 23-8: DC Characteristics: Program Memory.                                                                 |

| Section 24.0 "DC and AC Device<br>Characteristics Graphs"  | Added new chapter.                                                                                                      |