Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

|                            |                                                                             |

| Product Status             | Active                                                                      |

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 50MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                                |

| Number of I/O              | 38                                                                          |

| Program Memory Size        | 16KB (16K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 512 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 68-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 68-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3244lti-130t |

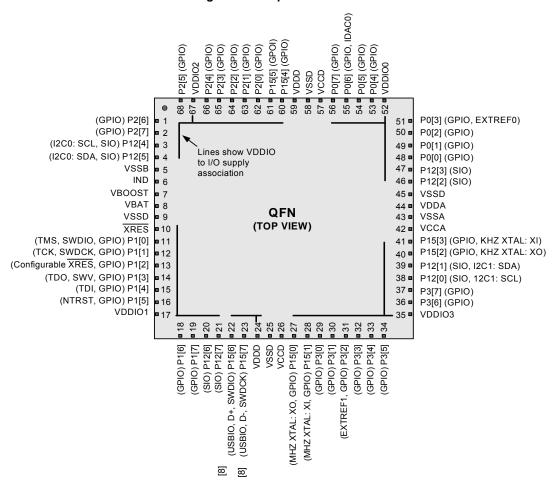

Figure 2-5. 68-pin QFN Part Pinout<sup>[7]</sup>

The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices.

Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

**Digital Input Path** Naming Convention PRT[x]CTL 'x' = Port Number PRT[x]DBL\_SYNC\_IN 'y' = Pin Number PRT[x]PS Digital System Input PICU[x]INTTYPE[y] Input Buffer Disable PICU[x]INTSTAT Interrupt Pin Interrupt Signal Logic PICU[x]INTSTAT **Digital Output Path** PRT[x]SLW PRT[x]SYNC\_OUT Vddio Vddio PRT[x]DR In Digital System Output PRT[x]BYP PRT[x]DM2 Drive Slew Logic PIN PRT[x]DM1 Cntl PRT[x]DM0 Bidirectional Control PRT[x]BIE OE Analog Capsense Global Control CAPS[x]CFG1 Switches PRT[x]AG Analog Global PRT[x]AMUX Analog Mux  $\sim$ LCD Display Data PRT[x]LCD\_COM\_SEG Logic & MUX PRT[x]LCD\_EN LCD Bias Bus

Figure 6-9. GPIO Block Diagram

#### 6.4.5 Pin Interrupts

All GPIO and SIO pins are able to generate interrupts to the system. All eight pins in each port interface to their own Port Interrupt Control Unit (PICU) and associated interrupt vector. Each pin of the port is independently configurable to detect rising edge, falling edge, both edge interrupts, or to not generate an interrupt.

Depending on the configured mode for each pin, each time an interrupt event occurs on a pin, its corresponding status bit of the interrupt status register is set to "1" and an interrupt request is sent to the interrupt controller. Each PICU has its own interrupt vector in the interrupt controller and the pin status register providing easy determination of the interrupt source down to the pin level.

Port pin interrupts remain active in all sleep modes allowing the PSoC device to wake from an externally generated interrupt.

While level sensitive interrupts are not directly supported; Universal Digital Blocks (UDB) provide this functionality to the system when needed.

#### 6.4.6 Input Buffer Mode

GPIO and SIO input buffers can be configured at the port level for the default CMOS input thresholds or the optional LVTTL input thresholds. All input buffers incorporate Schmitt triggers for input hysteresis. Additionally, individual pin input buffers can be disabled in any drive mode.

#### 6.4.7 I/O Power Supplies

Up to four I/O pin power supplies are provided depending on the device and package. Each I/O supply must be less than or equal to the voltage on the chip's analog (VDDA) pin. This feature allows users to provide different I/O voltage levels for different pins on the device. Refer to the specific device package pinout to determine VDDIO capability for a given port and pin.

The SIO port pins support an additional regulated high output capability, as described in Adjustable Output Level.

#### 6.4.8 Analog Connections

These connections apply only to GPIO pins. All GPIO pins may be used as analog inputs or outputs. The analog voltage present on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs. Each GPIO may connect to one of the analog global busses or to one of the analog mux buses to connect any pin to any internal analog resource such as ADC or comparators. In addition, one select pin provides direct connection to the high current DAC.

#### 6.4.9 CapSense

This section applies only to GPIO pins. All GPIO pins may be used to create CapSense buttons and sliders. See the "CapSense" section on page 61 for more information.

#### 6.4.10 LCD Segment Drive

This section applies only to GPIO pins. All GPIO pins may be used to generate Segment and Common drive signals for direct glass drive of LCD glass. See the "LCD Direct Drive" section on page 60 for details.

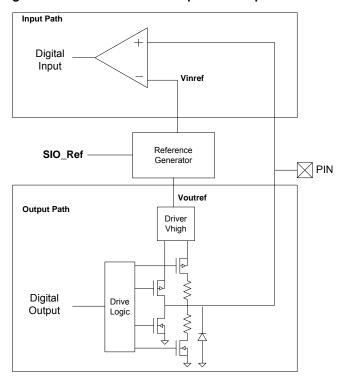

#### 6.4.11 Adjustable Output Level

This section applies only to SIO pins. SIO port pins support the ability to provide a regulated high output level for interface to external signals that are lower in voltage than the SIO's respective VDDIO. SIO pins are individually configurable to output either the standard VDDIO level or the regulated output, which is based on an internally generated reference. Typically the voltage DAC (VDAC) is used to generate the reference (see Figure 6-13). The "DAC" section on page 61 has more details on VDAC use and reference routing to the SIO pins. Resistive pull-up and pull-down drive modes are not available with SIO in regulated output mode.

#### 6.4.12 Adjustable Input Level

This section applies only to SIO pins. SIO pins by default support the standard CMOS and LVTTL input levels but also support a differential mode with programmable levels. SIO pins are grouped into pairs. Each pair shares a reference generator block which, is used to set the digital input buffer reference level for interface to external signals that differ in voltage from VDDIO. The reference sets the pins voltage threshold for a high logic level (see Figure 6-13). Available input thresholds are:

- 0.5 × VDDIO

- 0.4 × VDDIO

- 0.5 × VREF

- VREF

Typically the voltage DAC (VDAC) generates the  $V_{REF}$  reference. The "DAC" section on page 61 has more details on VDAC use and reference routing to the SIO pins.

Figure 6-13. SIO Reference for Input and Output

#### 7.1.4 Designing with PSoC Creator

#### 7.1.4.1 More Than a Typical IDE

A successful design tool allows for the rapid development and deployment of both simple and complex designs. It reduces or eliminates any learning curve. It makes the integration of a new design into the production stream straightforward.

PSoC Creator is that design tool.

PSoC Creator is a full featured Integrated Development Environment (IDE) for hardware and software design. It is optimized specifically for PSoC devices and combines a modern, powerful software development platform with a sophisticated graphical design tool. This unique combination of tools makes PSoC Creator the most flexible embedded design platform available.

Graphical design entry simplifies the task of configuring a particular part. You can select the required functionality from an extensive catalog of components and place it in your design. All components are parameterized and have an editor dialog that allows you to tailor functionality to your needs.

PSoC Creator automatically configures clocks and routes the I/O to the selected pins and then generates APIs to give the application complete control over the hardware. Changing the PSoC device configuration is as simple as adding a new component, setting its parameters, and rebuilding the project.

At any stage of development you are free to change the hardware configuration and even the target processor. To retarget your application (hardware and software) to new devices, even from 8- to 32-bit families, just select the new device and rebuild.

You also have the ability to change the C compiler and evaluate an alternative. Components are designed for portability and are validated against all devices, from all families, and against all supported tool chains. Switching compilers is as easy as editing the from the project options and rebuilding the application with no errors from the generated APIs or boot code.

#### 7.1.4.2 Component Catalog

The component catalog is a repository of reusable design elements that select device functionality and customize your PSoC device. It is populated with an impressive selection of content; from simple primitives such as logic gates and device registers, through the digital timers, counters and PWMs, plus

analog components such as ADC and DAC, and communication protocols, such as  $I^2C$ , and USB. See Example Peripherals on page 45 for more details about available peripherals. All content is fully characterized and carefully documented in datasheets with code examples, AC/DC specifications, and user code ready APIs.

#### 7.1.4.3 Design Reuse

The symbol editor gives you the ability to develop reusable components that can significantly reduce future design time. Just draw a symbol and associate that symbol with your proven design. PSoC Creator allows for the placement of the new symbol anywhere in the component catalog along with the content provided by Cypress. You can then reuse your content as many times as you want, and in any number of projects, without ever having to revisit the details of the implementation.

#### 7.1.4.4 Software Development

Anchoring the tool is a modern, highly customizable user interface. It includes project management and integrated editors for C and assembler source code, as well the design entry tools.

Project build control leverages compiler technology from top commercial vendors such as ARM<sup>®</sup> Limited, Keil™, and CodeSourcery (GNU). Free versions of Keil C51 and GNU C Compiler (GCC) for ARM, with no restrictions on code size or end product distribution, are included with the tool distribution. Upgrading to more optimizing compilers is a snap with support for the professional Keil C51 product and ARM RealView™ compiler.

#### 7.1.4.5 Nonintrusive Debugging

With JTAG (4-wire) and SWD (2-wire) debug connectivity available on all devices, the PSoC Creator debugger offers full control over the target device with minimum intrusion. Breakpoints and code execution commands are all readily available from toolbar buttons and an impressive lineup of windows—register, locals, watch, call stack, memory and peripherals—make for an unparalleled level of visibility into the system.

PSoC Creator contains all the tools necessary to complete a design, and then to maintain and extend that design for years to come. All steps of the design flow are carefully integrated and optimized for ease-of-use and to maximize productivity.

Document Number: 001-56955 Rev. \*Y Page 46 of 128

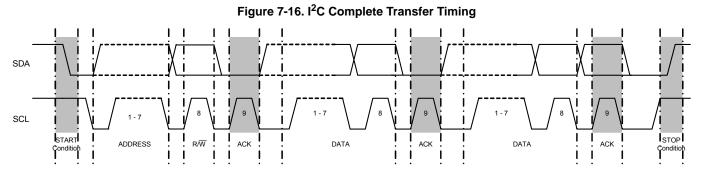

#### 7.7 I<sup>2</sup>C

PSoC includes a single fixed-function I<sup>2</sup>C peripheral. Additional I<sup>2</sup>C interfaces can be instantiated using Universal Digital Blocks (UDBs) in PSoC Creator, as required.

The I<sup>2</sup>C peripheral provides a synchronous two-wire interface designed to interface the PSoC device with a two-wire I<sup>2</sup>C serial communication bus. It is compatible<sup>[13]</sup> with I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I2C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O may be implemented with GPIO or SIO in open-drain modes.

To eliminate the need for excessive CPU intervention and overhead, I<sup>2</sup>C specific support is provided for status detection and generation of framing bits. I<sup>2</sup>C operates as a slave, a master, or multimaster (Slave and Master)[14]. In slave mode, the unit always listens for a start condition to begin sending or receiving data. Master mode supplies the ability to generate the Start and Stop conditions and initiate transactions. Multimaster mode provides clock synchronization and arbitration to allow multiple masters on the same bus. If Master mode is enabled and Slave mode is not enabled, the block does not generate interrupts on externally generated Start conditions. I<sup>2</sup>C interfaces through the DSI routing and allows direct connections to any GPIO or SIO pins.

I<sup>2</sup>C provides hardware address detect of a 7-bit address without CPU intervention. Additionally the device can wake from low-power modes on a 7-bit hardware address match. If wakeup functionality is required, I2C pin connections are limited to one of two specific pairs of SIO pins. See descriptions of SCL and SDA pins in Pin Descriptions on page 12.

I<sup>2</sup>C features include:

- Slave and Master, Transmitter, and Receiver operation

- Byte processing for low CPU overhead

- Interrupt or polling CPU interface

- Support for bus speeds up to 1 Mbps

- 7 or 10-bit addressing (10-bit addressing requires firmware support)

- SMBus operation (through firmware support SMBus supported in hardware in UDBs)

- 7-bit hardware address compare

- Wake from low-power modes on address match

- Glitch filtering (active and alternate-active modes only)

Data transfers follow the format shown in Figure 7-16. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master.

7.7.1 External Electrical Connections

As Figure 7-17 shows, the I<sup>2</sup>C bus requires external pull-up resistors (R<sub>P</sub>). These resistors are primarily determined by the supply voltage, bus speed, and bus capacitance. For detailed

information on how to calculate the optimum pull-up resistor value for your design, we recommend using the UM10204 I2C-bus specification and user manual Rev 6, or newer, available from the NXP website at www.nxp.com.

#### Notes

Document Number: 001-56955 Rev. \*Y

<sup>13.</sup> The I<sup>2</sup>C peripheral is non-compliant with the NXP I2C specification in the following areas: analog glitch filter, I/O VOL/IOL, I/O hysteresis. The I<sup>2</sup>C Block has a digital glitch filter (not available in sleep mode). The Fast-mode minimum fall-time specification can be met by setting the I/Os to slow speed mode. See the I/O Electrical Specifications in "Inputs and Outputs" section on page 76 for details.

<sup>14.</sup> Fixed-block I<sup>2</sup>C does not support undefined bus conditions, nor does it support Repeated Start in Slave mode. These conditions should be avoided, or the UDB-based I<sup>2</sup>C component should be used instead.

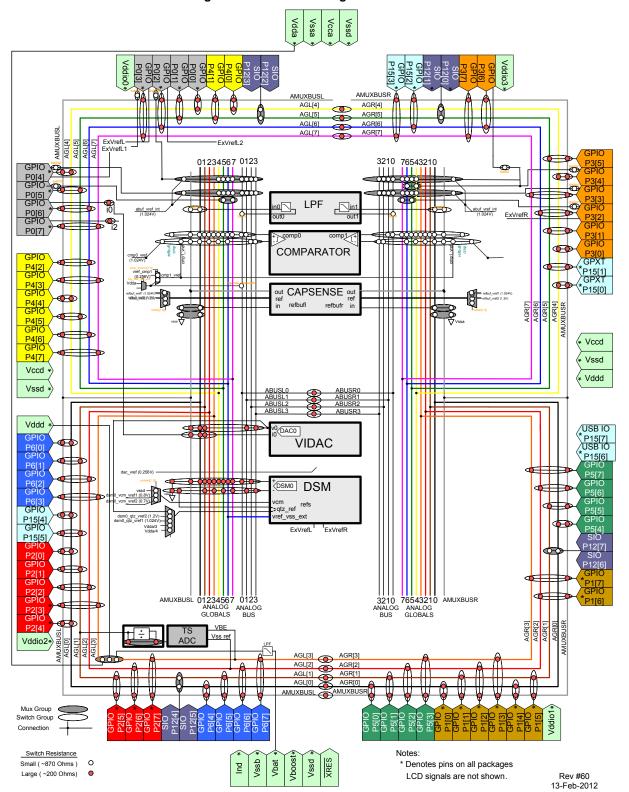

#### 8.1 Analog Routing

The CY8C32 family of devices has a flexible analog routing architecture that provides the capability to connect GPIOs and different analog blocks, and also route signals between different analog blocks. One of the strong points of this flexible routing architecture is that it allows dynamic routing of input and output connections to the different analog blocks.

For information on how to make pin selections for optimal analog routing, refer to the application note, AN58304 - PSoC® 3 and PSoC® 5 - Pin Selection for Analog Designs.

#### 8.1.1 Features

- Flexible, configurable analog routing architecture

- 16 analog globals (AG) and two analog mux buses (AMUXBUS) to connect GPIOs and the analog blocks

- Each GPIO is connected to one analog global and one analog mux bus

- Eight analog local buses (abus) to route signals between the different analog blocks

- Multiplexers and switches for input and output selection of the analog blocks

#### 8.1.2 Functional Description

Analog globals (AGs) and analog mux buses (AMUXBUS) provide analog connectivity between GPIOs and the various analog blocks. There are 16 AGs in the CY8C32 family. The analog routing architecture is divided into four quadrants as shown in Figure 8-2. Each quadrant has four analog globals (AGL[0..3], AGL[4..7], AGR[0..3], AGR[4..7]). Each GPIO is connected to the corresponding AG through an analog switch. The analog mux bus is a shared routing resource that connects to every GPIO through an analog switch. There are two AMUXBUS routes in CY8C32, one in the left half (AMUXBUSL) and one in the right half (AMUXBUSR), as shown in Figure 8-2.

Document Number: 001-56955 Rev. \*Y Page 56 of 128

Figure 8-2. CY8C32 Analog Interconnect

To preserve detail of this figure, this figure is best viewed with a PDF display program or printed on a 11" × 17" paper.

#### Programming, Debug Interfaces, Resources

PSoC devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware. Three interfaces are available: JTAG, SWD, and SWV. JTAG and SWD support all programming and debug features of the device. JTAG also supports standard JTAG scan chains for board level test and chaining multiple JTAG devices to a single JTAG connection.

For more information on PSoC 3 Programming, refer to the PSoC<sup>®</sup> 3 Device Programming Specifications.

Complete Debug on Chip (DoC) functionality enables full device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator IDE software provides fully integrated programming and debug support for PSoC devices. The low cost MiniProg3 programmer and debugger is designed to provide full programming and debug support of PSoC devices in conjunction with the PSoC Creator IDE. PSoC JTAG, SWD, and SWV interfaces are fully compatible with industry standard third party tools.

All DOC circuits are disabled by default and can only be enabled in firmware. If not enabled, the only way to reenable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables DOC. Disabling DOC features, robust flash protection, and hiding custom analog and digital functionality inside the PSoC device provide a level of security not possible with multichip application solutions. Additionally, all device interfaces can be permanently disabled (Device Security) for applications concerned about phishing attacks due to a maliciously reprogrammed device. Permanently

disabling interfaces is not recommended in most applications because you cannot access the device later. Because all programming, debug, and test interfaces are disabled when Device Security is enabled, PSoCs with Device Security enabled may not be returned for failure analysis.

Table 9-1. Debug Configurations

| Debug and Trace Configuration | GPIO Pins Used |

|-------------------------------|----------------|

| All debug and trace disabled  | 0              |

| JTAG                          | 4 or 5         |

| SWD                           | 2              |

| SWV                           | 1              |

| SWD + SWV                     | 3              |

#### 9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG interface is used for programming the flash memory, debugging, I/O scan chains, and JTAG device chaining.

PSoC 3 has certain timing requirements to be met for entering programming mode through the JTAG interface. Due to these timing requirements, not all standard JTAG programmers, or standard JTAG file formats such as SVF or STAPL, can support PSoC 3 programming. The list of programmers that support PSoC 3 programming is available at

http://www.cypress.com/go/programming.

The JTAG clock frequency can be up to 14 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit transfers, or 1/5 of the CPU clock frequency for 32-bit transfers. By default, the JTAG pins are enabled on new devices but the JTAG interface can be disabled, allowing these pins to be used as GPIO instead.

Document Number: 001-56955 Rev. \*Y Page 62 of 128

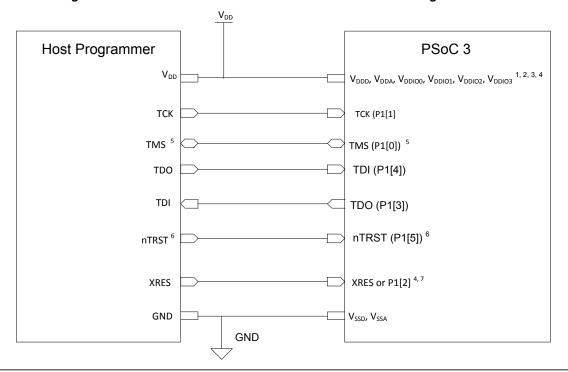

Figure 9-1. JTAG Interface Connections between PSoC 3 and Programmer

- The voltage levels of Host Programmer and the PSoC 3 voltage domains involved in Programming should be same. The Port 1 JTAG pins, XRES pin (XRES\_N or P1[2]) are powered by V<sub>DDIO1</sub>. So, V<sub>DDIO1</sub> of PSoC 3 should be at same voltage level as host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDIO2</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer.

- Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

- <sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- <sup>4</sup> For JTAG Programming, Device reset can also be done without connecting to the XRES pin or Power cycle mode by using the TMS,TCK,TDI, TDO pins of PSoC 3, and writing to a specific register. But this requires that the DPS setting in NVL is not equal to "Debug Ports Disabled".

- <sup>5</sup> By default, PSoC 3 is configured for 4-wire JTAG mode unless user changes the DPS setting. So the TMS pin is unidirectional. But if the DPS setting is changed to non-JTAG mode, the TMS pin in JTAG is bi-directional as the SWD Protocol has to be used for acquiring the PSoC 3 device initially. After switching from SWD to JTAG mode, the TMS pin will be uni-directional. In such a case, unidirectional buffer should not be used on TMS line.

- <sup>3</sup> nTRST JTAG pin (P1[5]) cannot be used to reset the JTAG TAP controlller during first time programming of PSoC 3 as the default setting is 4-wire JTAG (nTRST disabled). Use the TMS, TCK pins to do a reset of JTAG TAP controller.

- If XRES pin is used by host, P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48-pin devices, but use dedicated XRES pin for rest of devices.

Document Number: 001-56955 Rev. \*Y Page 63 of 128

#### 11.2 Device Level Specifications

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

#### 11.2.1 Device Level Specifications

#### Table 11-2. DC Specifications

| Parameter                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Conditions                                                                                             |            | Min  | Typ <sup>[22]</sup> | Max                                    | Units |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------|------|---------------------|----------------------------------------|-------|

| $V_{DDA}$                           | Analog supply voltage and input to analog core regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Analog core regulato                                                                                   | r enabled  | 1.8  | _                   | 5.5                                    | V     |

| $V_{DDA}$                           | Analog supply voltage, analog regulator bypassed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Analog core regulato                                                                                   | r disabled | 1.71 | 1.8                 | 1.89                                   | V     |

| $V_{\mathrm{DDD}}$                  | Digital supply voltage relative to V <sub>SSD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital core regulator                                                                                 | enabled    | 1.8  | -                   | V <sub>DDA</sub> <sup>[18]</sup>       | V     |

| עטט ע                               | Digital supply voltage relative to vggD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Digital core regulator                                                                                 | Chabica    | -    | -                   | V <sub>DDA</sub> + 0.1 <sup>[24]</sup> | V     |

| $V_{DDD}$                           | Digital supply voltage, digital regulator bypassed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Digital core regulator                                                                                 | disabled   | 1.71 | 1.8                 | 1.89                                   | ٧     |

| V <sub>DDIO</sub> [19]              | I/O supply voltage relative to V <sub>SSIO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |            | 1.71 | -                   | V <sub>DDA</sub> <sup>[18]</sup>       | V     |

| ▼DDIO <sup>3</sup>                  | The supply voltage relative to VSSIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                        |            | ı    | 1                   | V <sub>DDA</sub> + 0.1 <sup>[24]</sup> |       |

| V <sub>CCA</sub>                    | Direct analog core voltage input (Analog regulator bypass)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Analog core regulato                                                                                   | r disabled | 1.71 | 1.8                 | 1.89                                   | ٧     |

| V <sub>CCD</sub>                    | Direct digital core voltage input (Digital regulator bypass)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Digital core regulator                                                                                 | disabled   | 1.71 | 1.8                 | 1.89                                   | V     |

|                                     | Active Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                        |            |      |                     |                                        |       |

|                                     | Only IMO and CPU clock enabled. CPU executing simple loop from instruction buffer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Function $F_{CPU} = 6 \text{ MHz}^{[23]}$ $T = 25 ^{\circ}\text{C}$ $T = 85 ^{\circ}\text{C}$          |            | 1    | 1.2                 | 2.9                                    |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                        | ı          | 1.2  | 3.1                 |                                        |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                        | ı          | 4.9  | 7.7                 |                                        |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | \/ -27\/ 55\/:                                                                                         |            | _    | 1.3                 | 2.9                                    |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $V_{DDX} = 2.7 \text{ V} - 5.5 \text{ V},$ $F_{CRIJ} = 3 \text{ MHz}^{[23]}$ $T = 25 ^{\circ}\text{C}$ | _          | 1.6  | 3.2                 |                                        |       |

|                                     | V <sub>DDX</sub> = 2.7 V – 5.5 V;<br>$V_{CPU} = 3 \text{ MHz}^{[23]}$<br>$T = 85 ^{\circ}\text{C}$<br>$T = -40 ^{\circ}\text{C}$<br>$T = 25 ^{\circ}\text{C}$<br>$T = 85 ^{\circ}\text{C}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                                                                                                      | 4.8        | 7.5  |                     |                                        |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | \/ -0.7\/ F.F.\/:                                                                                      | T = -40 °C | _    | 2.1                 | 3.7                                    |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                        |            | -    | 2.3                 | 3.9                                    |       |

| I <sub>DD</sub> <sup>[20, 21]</sup> | $V_{DDX} = 2.7 \text{ V} - 5.5 \text{ V};$ $F_{CPU} = 3 \text{ MHz}^{[23]}$ $T = 25 ^{\circ}\text{C}$ $T = 85 ^{\circ}\text{C}$ $T = 40 ^{\circ}\text{C}$ $T = 25 ^{\circ}\text{C}$ $T = 25 ^{\circ}\text{C}$ $T = 85 ^{\circ}\text{C}$ | -                                                                                                      | 5.6        | 8.5  | mA                  |                                        |       |

|                                     | IMO enabled, bus clock and CPU clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{DDX} = 2.7 \text{ V} - 5.5 \text{ V};$                                                             |            | _    | 3.5                 | 5.2                                    | ША    |

|                                     | enabled. CPU executing program from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | F <sub>CPU</sub> = 12 MHz <sup>[23]</sup>                                                              | T = 25 °C  | _    | 3.8                 | 5.5                                    |       |

|                                     | flash.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                        | T = 85 °C  | _    | 7.1                 | 9.8                                    |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $V_{DDX} = 2.7 \text{ V} - 5.5 \text{ V};$                                                             | T = -40 °C | _    | 6.3                 | 8.1                                    |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $F_{CPU} = 24 \text{ MHz}^{[23]}$                                                                      | T = 25 °C  | _    | 6.6                 | 8.3                                    |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                        | T = 85 °C  | _    | 10                  | 13                                     |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $V_{DDX} = 2.7 \text{ V} - 5.5 \text{ V}; T = -40 ^{\circ}$                                            | T = -40 °C | _    | 11.5                | 13.5                                   |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $F_{CPU} = 48 \text{ MHz}^{[23]}$                                                                      | T = 25 °C  | -    | 12                  | 14                                     |       |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                        | T = 85 °C  | -    | 15.5                | 18.5                                   |       |

- 18. The power supplies can be brought up in any sequence however once stable  $V_{DDA}$  must be greater than or equal to all other supplies. 19. The  $V_{DDIO}$  supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin  $\leq V_{DDIO} \leq V_{DDA}$ . 20. Total current for all power domains: digital ( $I_{DDD}$ ), analog ( $I_{DDA}$ ), and I/Os ( $I_{DDIO0, 1, 2, 3}$ ). Boost not included. All I/Os floating.

- 22. V<sub>DDX</sub> = 3.3 V.

23. Based on device characterizations (Not production tested).

- 24. Guaranteed by design, not production tested.

<sup>21.</sup> The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find the CPU current at the frequency of interest and add peripheral currents for your particular system from the device datasheet and component datasheets.

#### 11.3.3 Inductive Boost Regulator

Unless otherwise specified, operating conditions are:  $V_{BAT}$  = 0.5 V–3.6 V,  $V_{OUT}$  = 1.8 V–5.0 V,  $I_{OUT}$  = 0 mA–50 mA,  $L_{BOOST}$  = 4.7  $\mu$ H–22  $\mu$ H,  $C_{BOOST}$  = 22  $\mu$ F || 3 × 1.0  $\mu$ F || 3 × 0.1  $\mu$ F,  $C_{BAT}$  = 22  $\mu$ F,  $I_F$  = 1.0 A. Unless otherwise specified, all charts and graphs show typical values.

Table 11-6. Inductive Boost Regulator DC Specifications

| Parameter           | Description                            | Cond                          | ditions                                                               | Min  | Тур  | Max  | Units |

|---------------------|----------------------------------------|-------------------------------|-----------------------------------------------------------------------|------|------|------|-------|

| V <sub>OUT</sub>    | Boost output voltage <sup>[31]</sup>   | vsel = 1.8 V in regist        | ter BOOST_CR0                                                         | 1.71 | 1.8  | 1.89 | V     |

|                     |                                        | vsel = 1.9 V in regist        | ter BOOST_CR0                                                         | 1.81 | 1.90 | 2.00 | V     |

|                     |                                        | vsel = 2.0 V in regist        | ter BOOST_CR0                                                         | 1.90 | 2.00 | 2.10 | V     |

|                     |                                        | vsel = 2.4 V in regist        | ter BOOST_CR0                                                         | 2.16 | 2.40 | 2.64 | V     |

|                     |                                        | vsel = 2.7 V in regist        | ter BOOST_CR0                                                         | 2.43 | 2.70 | 2.97 | V     |

|                     |                                        | vsel = 3.0 V in regist        | ter BOOST_CR0                                                         | 2.70 | 3.00 | 3.30 | V     |

|                     |                                        | vsel = 3.3 V in regist        | ter BOOST_CR0                                                         | 2.97 | 3.30 | 3.63 | V     |

|                     |                                        | vsel = 3.6 V in regist        | ter BOOST_CR0                                                         | 3.24 | 3.60 | 3.96 | V     |

|                     |                                        | vsel = 5.0 V in regist        | ter BOOST_CR0                                                         | 4.50 | 5.00 | 5.50 | V     |

| $V_{BAT}$           | Input voltage to boost <sup>[32]</sup> |                               | vsel = 1.8 V–2.0 V,<br>T <sub>A</sub> = 0 °C–70 °C                    | 0.5  | _    | 0.8  | V     |

|                     |                                        | I <sub>OUT</sub> = 0 mA–15 mA | vsel = 1.8 V–5.0 V <sup>[33]</sup> ,<br>T <sub>A</sub> = –10 °C–85 °C | 1.6  | _    | 3.6  | V     |

|                     |                                        | I <sub>OUT</sub> = 0 mA–25 mA | vsel = 1.8 V–2.7 V,<br>T <sub>A</sub> = –10 °C–85 °C                  | 0.8  | -    | 1.6  | V     |

|                     |                                        | I <sub>OUT</sub> = 0 mA–50 mA | vsel = 1.8 V-3.3 V <sup>[33]</sup> ,<br>T <sub>A</sub> = -40 °C-85 °C | 1.8  | _    | 2.5  | V     |

|                     |                                        |                               | vsel = 1.8 V-3.3 V <sup>[33]</sup> ,<br>T <sub>A</sub> = -10 °C-85 °C | 1.3  | -    | 2.5  | V     |

|                     |                                        |                               | vsel = 2.5 V-5.0 V <sup>[33]</sup> ,<br>T <sub>A</sub> = -10 °C-85 °C | 2.5  | _    | 3.6  | V     |

| I <sub>OUT</sub>    | Output current                         | T <sub>A</sub> = 0 °C-70 °C   | V <sub>BAT</sub> = 0.5 V–0.8 V                                        | 0    | _    | 5    | mA    |

|                     |                                        | T <sub>A</sub> = -10 °C-85 °C | V <sub>BAT</sub> = 1.6 V–3.6 V                                        | 0    | _    | 15   | mA    |

|                     |                                        |                               | V <sub>BAT</sub> = 0.8 V–1.6 V                                        | 0    | _    | 25   | mA    |

|                     |                                        |                               | $V_{BAT} = 1.3 \text{ V} - 2.5 \text{ V}$                             | 0    | _    | 50   | mA    |

|                     |                                        |                               | $V_{BAT} = 2.5 \text{ V} - 3.6 \text{ V}$                             | 0    | _    | 50   | mA    |

|                     |                                        | T <sub>A</sub> = -40 °C-85 °C |                                                                       | 0    | _    | 50   | mA    |

|                     | la direta a a a la arraga at           | 1A40 C-65 C                   | VBAT - 1.0 V-2.5 V                                                    |      | _    |      |       |

| I <sub>LPK</sub>    | Inductor peak current                  |                               |                                                                       |      |      | 700  | mA    |

| $I_Q$               | Quiescent current                      | Boost active mode             |                                                                       | -    | 250  | _    | μA    |

|                     |                                        | Boost sleep mode, I           | <sub>OUT</sub> < 1 μA                                                 | _    | 25   | _    | μA    |

| Reg <sub>LOAD</sub> | Load regulation                        |                               |                                                                       | -    | _    | 10   | %     |

| Reg <sub>LINE</sub> | Line regulation                        |                               |                                                                       | -    | -    | 10   | %     |

<sup>31.</sup> Listed vsel options are characterized. Additional vsel options are valid and guaranteed by design.

32. The boost will start at all valid V<sub>BAT</sub> conditions including down to V<sub>BAT</sub> = 0.5 V.

33. If V<sub>BAT</sub> is greater than or equal to V<sub>OUT</sub> boost setting, then V<sub>OUT</sub> will be less than V<sub>BAT</sub> due to resistive losses in the boost circuit.

#### 11.4 Inputs and Outputs

Specifications are valid for  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$  and  $T_{J} \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values.

When the power supplies ramp up, there are low-impedance connections between each GPIO pin and its  $V_{DDIO}$  supply. This causes the pin voltages to track  $V_{DDIO}$  until both  $V_{DDIO}$  and  $V_{DDA}$  reach the IPOR voltage, which can be as high as 1.45 V. At that point, the low-impedance connections no longer exist and the pins change to their normal NVL settings.

#### 11.4.1 GPIO

#### Table 11-9. GPIO DC Specifications

| Parameter       | Description                                                                                         | Conditions                                             | Min                     | Тур | Max                     | Units |

|-----------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------|-----|-------------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                                                        | CMOS Input, PRT[x]CTL = 0                              | $0.7 \times V_{DDIO}$   | _   | -                       | V     |

| V <sub>IL</sub> | Input voltage low threshold                                                                         | CMOS Input, PRT[x]CTL = 0                              | _                       | -   | $0.3 \times V_{DDIO}$   | V     |

| V <sub>IH</sub> | Input voltage high threshold                                                                        | LVTTL Input, PRT[×]CTL = 1, V <sub>DDIO</sub> < 2.7 V  | 0.7 × V <sub>DDIO</sub> | _   | _                       | V     |

| V <sub>IH</sub> | Input voltage high threshold                                                                        | LVTTL Input, PRT[×]CTL = 1, V <sub>DDIO</sub> ≥ 2.7V   | 2.0                     | _   | _                       | V     |

| V <sub>IL</sub> | Input voltage low threshold                                                                         | LVTTL Input, PRT[×]CTL = 1, V <sub>DDIO</sub> < 2.7 V  | _                       | Ī   | 0.3 × V <sub>DDIO</sub> | V     |

| V <sub>IL</sub> | Input voltage low threshold                                                                         | LVTTL Input, PRT[×]CTL = 1, V <sub>DDIO</sub> ≥ 2.7V   | _                       | _   | 0.8                     | V     |

| V <sub>OH</sub> | Output voltage high                                                                                 | I <sub>OH</sub> = 4 mA at 3.3 V <sub>DDIO</sub>        | V <sub>DDIO</sub> – 0.6 | _   | _                       | V     |

|                 |                                                                                                     | I <sub>OH</sub> = 1 mA at 1.8 V <sub>DDIO</sub>        | V <sub>DDIO</sub> – 0.5 | -   | _                       | V     |

| V <sub>OL</sub> | Output voltage low                                                                                  | $I_{OL}$ = 8 mA at 3.3 $V_{DDIO}$                      | _                       | _   | 0.6                     | V     |

|                 |                                                                                                     | I <sub>OL</sub> = 4 mA at 1.8 V <sub>DDIO</sub>        | _                       | _   | 0.6                     | V     |

|                 |                                                                                                     | I <sub>OL</sub> = 3 mA at 3.3 V <sub>DDIO</sub>        | _                       | -   | 0.4                     | V     |

| Rpullup         | Pull-up resistor                                                                                    |                                                        | 3.5                     | 5.6 | 8.5                     | kΩ    |

| Rpulldown       | Pull-down resistor                                                                                  |                                                        | 3.5                     | 5.6 | 8.5                     | kΩ    |

| I <sub>IL</sub> | Input leakage current (absolute value)[36]]                                                         | 25 °C, V <sub>DDIO</sub> = 3.0 V                       | _                       | -   | 2                       | nA    |

| C <sub>IN</sub> | Input capacitance <sup>[36]</sup>                                                                   | GPIOs not shared with opamp outputs, MHz ECO or kHzECO | _                       | 4   | 7                       | pF    |

|                 |                                                                                                     | GPIOs shared with MHz<br>ECO or kHzECO <sup>[37]</sup> | _                       | 5   | 7                       | pF    |

|                 |                                                                                                     | GPIOs shared with opamp outputs                        | _                       | _   | 18                      | pF    |

| V <sub>H</sub>  | Input voltage hysteresis (Schmitt-Trigger)[36]                                                      |                                                        | _                       | 40  | -                       | mV    |

| Idiode          | Current through protection diode to $V_{\mbox{\scriptsize DDIO}}$ and $V_{\mbox{\scriptsize SSIO}}$ |                                                        | _                       | -   | 100                     | μΑ    |

| Rglobal         | Resistance pin to analog global bus                                                                 | 25 °C, V <sub>DDIO</sub> = 3.0 V                       | _                       | 320 | _                       | Ω     |

| Rmux            | Resistance pin to analog mux bus                                                                    | 25 °C, V <sub>DDIO</sub> = 3.0 V                       | _                       | 220 | -                       | Ω     |

<sup>36.</sup> Based on device characterization (Not production tested).

<sup>37.</sup> For information on designing with PSoC oscillators, refer to the application note, AN54439 - PSoC® 3 and PSoC 5 External Oscillator.

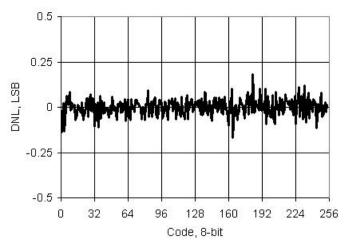

Figure 11-28. IDAC DNL vs Input Code, Range = 255  $\mu$ A, Source Mode

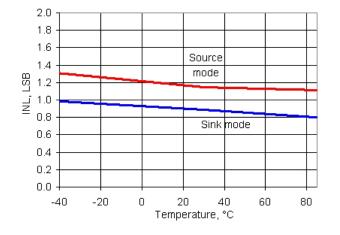

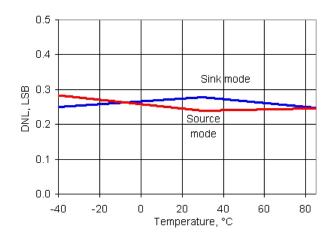

Figure 11-30. IDAC INL vs Temperature, Range = 255  $\mu$ A, High speed mode

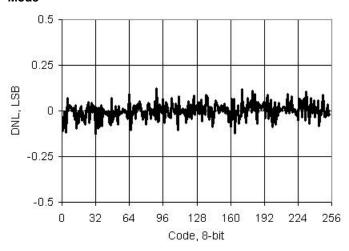

Figure 11-29. IDAC DNL vs Input Code, Range = 255  $\mu$ A, Sink Mode

Figure 11-31. IDAC DNL vs Temperature, Range = 255  $\mu$ A, High speed mode

#### 11.5.6 Voltage Digital to Analog Converter (VDAC)

See the VDAC component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

Table 11-28. VDAC DC Specifications

| Parameter        | Description                               | Conditions                        | Min | Тур  | Max  | Units     |

|------------------|-------------------------------------------|-----------------------------------|-----|------|------|-----------|

|                  | Resolution                                |                                   | -   | 8    | -    | bits      |

| INL1             | Integral nonlinearity                     | 1 V scale                         | -   | ±2.1 | ±2.5 | LSB       |

| INL4             | Integral nonlinearity <sup>[52]</sup>     | 4 V scale                         | -   | ±2.1 | ±2.5 | LSB       |

| DNL1             | Differential nonlinearity                 | 1 V scale                         | -   | ±0.3 | ±1   | LSB       |

| DNL4             | Differential nonlinearity <sup>[52]</sup> | 4 V scale                         | _   | ±0.3 | ±1   | LSB       |

| Rout             | Output resistance                         | 1 V scale                         | -   | 4    | -    | kΩ        |

|                  |                                           | 4 V scale                         | -   | 16   | -    | kΩ        |

| V <sub>OUT</sub> | Output voltage range, code = 255          | 1 V scale                         | -   | 1.02 | -    | V         |

|                  |                                           | 4 V scale, V <sub>DDA</sub> = 5 V | -   | 4.08 | -    | V         |

|                  | Monotonicity                              |                                   | _   | _    | Yes  | _         |

| V <sub>OS</sub>  | Zero scale error                          |                                   | _   | 0    | ±0.9 | LSB       |

| Eg               | Gain error                                | 1 V scale                         | -   | _    | ±2.5 | %         |

|                  |                                           | 4 V scale                         | _   | _    | ±2.5 | %         |

| TC_Eg            | Temperature coefficient, gain error       | 1 V scale                         | _   | _    | 0.03 | %FSR/°C   |

|                  |                                           | 4 V scale                         | -   | -    | 0.03 | %FSR / °C |

| I <sub>DD</sub>  | Operating current                         | Low speed mode                    | -   | -    | 100  | μA        |

|                  |                                           | High speed mode                   | _   | _    | 500  | μA        |

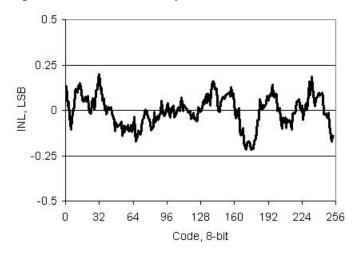

Figure 11-40. VDAC INL vs Input Code, 1 V Mode

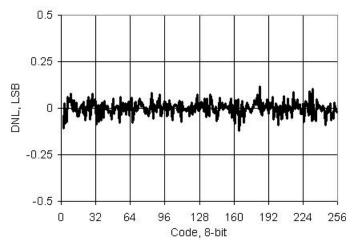

Figure 11-41. VDAC DNL vs Input Code, 1 V Mode

#### Note

52. Based on device characterization (Not production tested).

#### 11.7.2 EEPROM

#### Table 11-47. EEPROM DC Specifications

| Parameter | Description               | Conditions | Min  | Тур | Max | Units |

|-----------|---------------------------|------------|------|-----|-----|-------|

|           | Erase and program voltage |            | 1.71 | -   | 5.5 | V     |

#### Table 11-48. EEPROM AC Specifications

| Parameter          | Description                                                                 | Conditions                                                               | Min | Тур | Max | Units |

|--------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>WRITE</sub> | Single row erase/write cycle time                                           |                                                                          | -   | 10  | 20  | ms    |

|                    | EEPROM data retention time, retention period measured from last erase cycle | Average ambient temp, T <sub>A</sub> ≤ 25 °C, 1M erase/program cycles    | 20  | _   | _   | years |

|                    |                                                                             | Average ambient temp, T <sub>A</sub> ≤ 55 °C, 100 K erase/program cycles | 20  | _   | -   |       |

|                    |                                                                             | Average ambient temp. $T_A \le 85$ °C, 10 K erase/program cycles         | 10  | _   | _   |       |

#### 11.7.3 Nonvolatile Latches (NVL))

### Table 11-49. NVL DC Specifications

| Parameter | Description               | Conditions           | Min  | Тур | Max | Units |

|-----------|---------------------------|----------------------|------|-----|-----|-------|

|           | Erase and program voltage | V <sub>DDD</sub> pin | 1.71 | 1   | 5.5 | V     |

#### Table 11-50. NVL AC Specifications

| Parameter | Description             | Conditions                                   | Min | Тур | Max | Units                       |

|-----------|-------------------------|----------------------------------------------|-----|-----|-----|-----------------------------|

|           | NVL endurance           | Programmed at 25 °C                          | 1K  | _   | _   | program/<br>erase<br>cycles |

|           |                         | Programmed at 0 °C to 70 °C                  | 100 | -   | _   | program/<br>erase<br>cycles |

|           | NVL data retention time | Average ambient temp. T <sub>A</sub> ≤ 55 °C | 20  | -   | -   | years                       |

|           |                         | Average ambient temp. T <sub>A</sub> ≤ 85 °C | 10  | _   | _   | years                       |

#### 11.7.4 SRAM

#### Table 11-51. SRAM DC Specifications

| Parameter  | Description            | Conditions | Min | Тур | Max | Units |

|------------|------------------------|------------|-----|-----|-----|-------|

| $V_{SRAM}$ | SRAM retention voltage |            | 1.2 | _   | _   | V     |

### Table 11-52. SRAM AC Specifications

| Parameter         | Description              | Conditions | Min | Тур | Max   | Units |

|-------------------|--------------------------|------------|-----|-----|-------|-------|

| F <sub>SRAM</sub> | SRAM operating frequency |            | DC  | -   | 50.01 | MHz   |

Document Number: 001-56955 Rev. \*Y Page 100 of 128

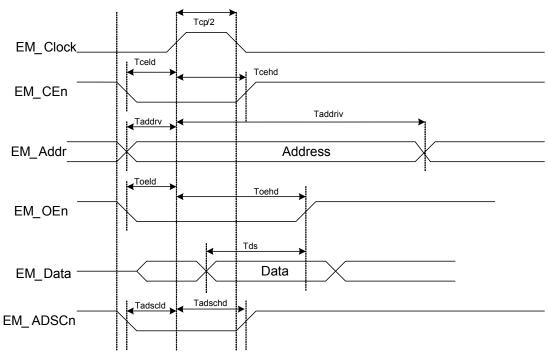

Figure 11-55. Synchronous Read Cycle Timing

Table 11-55. Synchronous Read Cycle Specifications

| Parameter | Description                       | Conditions                  | Min     | Тур | Max | Units |

|-----------|-----------------------------------|-----------------------------|---------|-----|-----|-------|

| Т         | EMIF clock period <sup>[62]</sup> | $V_{DDA} \ge 3.3 \text{ V}$ | 30.3    | _   | _   | ns    |

| Tcp/2     | EM_Clock pulse high               |                             | T/2     | _   | _   | ns    |

| Tceld     | EM_CEn low to EM_Clock high       |                             | 5       | _   | _   | ns    |

| Tcehd     | EM_Clock high to EM_CEn high      |                             | T/2 - 5 | _   | _   | ns    |

| Taddrv    | EM_Addr valid to EM_Clock high    |                             | 5       | _   | _   | ns    |

| Taddriv   | EM_Clock high to EM_Addr invalid  |                             | T/2 - 5 | _   | _   | ns    |

| Toeld     | EM_OEn low to EM_Clock high       |                             | 5       | _   | _   | ns    |

| Toehd     | EM_Clock high to EM_OEn high      |                             | Т       | _   | _   | ns    |

| Tds       | Data valid before EM_OEn high     |                             | T + 15  | _   | _   | ns    |

| Tadscld   | EM_ADSCn low to EM_Clock high     |                             | 5       | _   | _   | ns    |

| Tadschd   | EM_Clock high to EM_ADSCn high    |                             | T/2 - 5 | _   | _   | ns    |

#### 11.8.5 SWD Interface

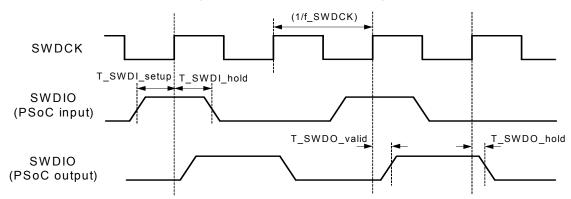

#### Figure 11-58. SWD Interface Timing

Table 11-63. SWD Interface AC Specifications<sup>[67]</sup>

| Parameter    | Description                         | Conditions                                                                      | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|---------------------------------------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3 \text{ V} \leq \text{V}_{DDD} \leq 5 \text{ V}$                            | -   | -   | 14 <sup>[68]</sup>  | MHz   |

|              |                                     | 1.71 V ≤ V <sub>DDD</sub> < 3.3 V                                               | _   | _   | 7 <sup>[68]</sup>   | MHz   |