#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 512 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 48-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3244pvi-133 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 3:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes and code examples covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 3 are:

- AN54181: Getting Started With PSoC 3

- AN61290: Hardware Design Considerations

- AN57821: Mixed Signal Circuit Board Layout

- AN58304: Pin Selection for Analog Designs

- AN81623: Digital Design Best Practices

- AN73854: Introduction To Bootloaders

using the PSoC Creator IDE C compiler

- Development Kits:

- CY8CKIT-030 is designed for analog performance, for developing high-precision analog, low-power, and low-voltage applications.

- CY8CKIT-001 provides a common development platform for any one of the PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP families of devices.

- The MiniProg3 device provides an interface for flash programming and debug.

- Technical Reference Manuals (TRM)

- Architecture TRM

- Registers TRM

- Programming Specification

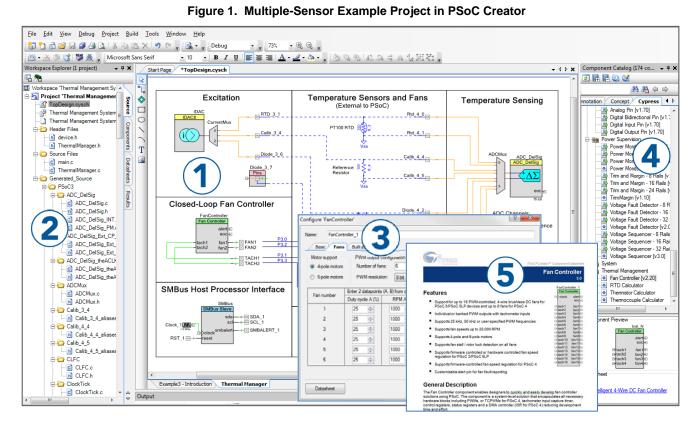

# PSoC Creator

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100 pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can:

1. Drag and drop component icons to build your hardware system design in the main design workspace

2. Codesign your application firmware with the PSoC hardware,

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- 5. Review component datasheets

# Document Number: 001-56955 Rev. \*Y

This enables the device to be powered directly from a single battery or solar cell. In addition, you can use the boost converter to generate other voltages required by the device, such as a 3.3-V supply for LCD glass drive. The boost's output is available on the V<sub>BOOST</sub> pin, allowing other devices in the application to be powered from the PSoC.

PSoC supports a wide range of low-power modes. These include a 200-nA hibernate mode with RAM retention and a  $1-\mu$ A sleep mode with RTC. In the second mode the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC.

Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low-power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 1.2 mA when the CPU is running at 6 MHz, or 0.8 mA running at 3 MHz.

The details of the PSoC power modes are covered in the "Power System" section on page 31 of this datasheet.

PSoC uses JTAG (4-wire) or SWD (2-wire) interfaces for programming, debug, and test. The 1-wire SWV may also be used for "printf" style debugging. By combining SWD and SWV, you can implement a full debugging interface with just three pins. Using these standard interfaces enables you to debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. PSoC supports on-chip break points and 4-KB instruction and data race memory for debug. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 62 of this datasheet.

## 2. Pinouts

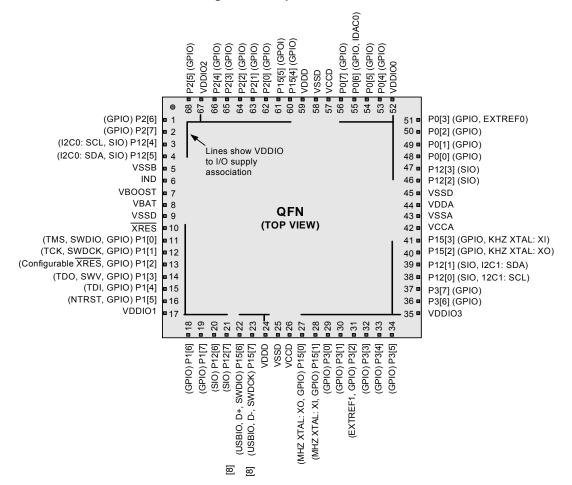

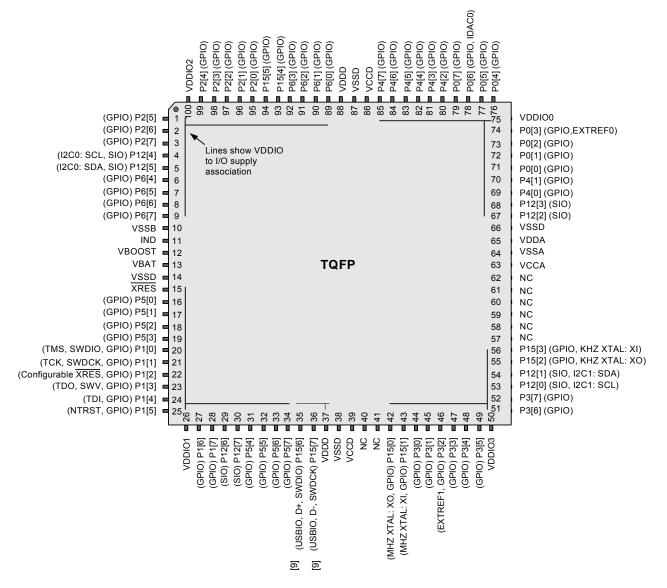

Each VDDIO pin powers a specific set of I/O pins. (The USBIOs are powered from VDDD.) Using the VDDIO pins, a single PSoC can support multiple voltage levels, reducing the need for off-chip level shifters. The black lines drawn on the pinout diagrams in Figure 2-3 through Figure 2-6, as well as Table 2-1, show the pins that are powered by each VDDIO.

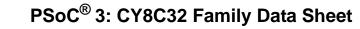

Each VDDIO may source up to 100 mA total to its associated I/O pins, as shown in Figure 2-1.

## Figure 2-1. VDDIO Current Limit

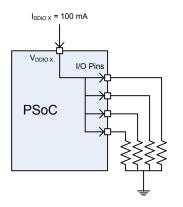

Conversely, for the 100-pin and 68-pin devices, the set of I/O pins associated with any VDDIO may sink up to 100 mA total, as shown in Figure 2-2.

#### Figure 2-2. I/O Pins Current Limit

For the 48-pin devices, the set of I/O pins associated with VDDIO0 plus VDDIO2 may sink up to 100 mA total. The set of I/O pins associated with VDDIO1 plus VDDIO3 may sink up to a total of 100 mA.

Figure 2-5. 68-pin QFN Part Pinout<sup>[7]</sup>

Notes

The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices.

Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

### Figure 2-6. 100-pin TQFP Part Pinout

#### Table 2-1. VDDIO and Port Pin Associations

| VDDIO  | Port Pins                            |

|--------|--------------------------------------|

| VDDIO0 | P0[7:0], P4[7:0], P12[3:2]           |

| VDDIO1 | P1[7:0], P5[7:0], P12[7:6]           |

| VDDIO2 | P2[7:0], P6[7:0], P12[5:4], P15[5:4] |

| VDDIO3 | P3[7:0], P12[1:0], P15[3:0]          |

| VDDD   | P15[7:6] (USB D+, D-)                |

Note 9. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

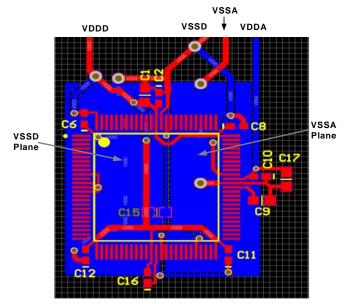

## Figure 2-8. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

# 3. Pin Descriptions

### IDAC0

Low resistance output pin for high current DAC (IDAC).

#### Extref0, Extref1

External reference input to the analog system.

### GPIO

General purpose I/O pin provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense.

#### 12C0: SCL, 12C1: SCL

$I^2C$  SCL line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SCL if wake from sleep is not required.

#### 12C0: SDA, 12C1: SDA

$\rm I^2C$  SDA line providing wake from sleep on an address match. Any I/O pin can be used for  $\rm I^2C$  SDA if wake from sleep is not required.

#### Ind

Inductor connection to boost pump.

#### kHz XTAL: Xo, kHz XTAL: Xi

32.768-kHz crystal oscillator pin.

#### MHz XTAL: Xo, MHz XTAL: Xi

4- to 25- MHz crystal oscillator pin.

## nTRST

Optional JTAG test reset programming and debug port connection to reset the JTAG connection.

### SIO

Special I/O provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

#### SWDCK

Serial wire debug clock programming and debug port connection.

## SWDIO

Serial wire debug input and output programming and debug port connection.

## SWV.

Single wire viewer debug output.

## тск

JTAG test clock programming and debug port connection.

## TDI

JTAG test data in programming and debug port connection.

## TDO

JTAG test data out programming and debug port connection.

## TMS

JTAG test mode select programming and debug port connection.

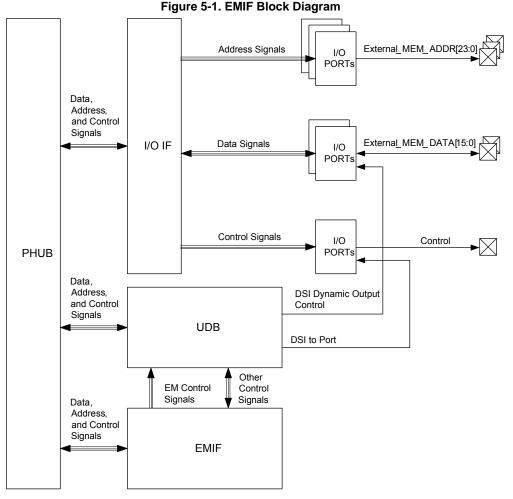

## 5.6 External Memory Interface

CY8C32 provides an external memory interface (EMIF) for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles. Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C32 supports only one type of external memory device at a time.

External memory can be accessed via the 8051 xdata space; up to 24 address bits can be used. See "xdata Space" section on page 28. The memory can be 8 or 16 bits wide.

## 5.7 Memory Map

The CY8C32 8051 memory map is very similar to the MCS-51 memory map.

#### 5.7.1 Code Space

The CY8C32 8051 code space is 64 KB. Only main flash exists in this space. See the "Flash Program Memory" section on page 24.

### 5.7.2 Internal Data Space

The CY8C32 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in Static RAM on page 24) and a 128-byte space for Special Function Registers (SFRs). See Figure 5-2. The lowest 32 bytes are used for 4 banks of registers R0-R7. The next 16 bytes are bit-addressable.

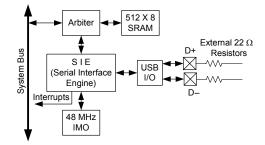

## 7.5 USB

PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 37.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Three memory modes

- Manual Memory Management with No DMA Access

- Manual Memory Management with Manual DMA Access

Automatic Memory Management with Automatic DMA Access

- Internal 3.3 V regulator for transceiver

- Internal 48 MHz main oscillator mode that auto locks to USB bus clock, requiring no external crystal for USB (USB equipped parts only)

- Interrupts on bus and each endpoint event, with device wakeup

- USB Reset, Suspend, and Resume operations

- Bus powered and self powered modes

#### Figure 7-14. USB

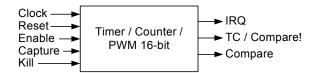

## 7.6 Timers, Counters, and PWMs

The Timer/Counter/PWM peripheral is a 16-bit dedicated peripheral providing three of the most common embedded peripheral features. As almost all embedded systems use some combination of timers, counters, and PWMs. Four of them have been included on this PSoC device family. Additional and more advanced functionality timers, counters, and PWMs can also be instantiated in Universal Digital Blocks (UDBs) as required. PSoC Creator allows you to choose the timer, counter, and PWM features that they require. The tool set utilizes the most optimal resources available.

The Timer/Counter/PWM peripheral can select from multiple clock sources, with input and output signals connected through the DSI routing. DSI routing allows input and output connections to any device pin and any internal digital signal accessible through the DSI. Each of the four instances has a compare output, terminal count output (optional complementary compare output), and programmable interrupt request line. The Timer/Counter/PWMs are configurable as free running, one shot, or Enable input controlled. The peripheral has timer reset and capture inputs, and a kill input for control of the comparator outputs. The peripheral supports full 16-bit capture.

Timer/Counter/PWM features include:

- 16-bit Timer/Counter/PWM (down count only)

- Selectable clock source

- PWM comparator (configurable for LT, LTE, EQ, GTE, GT)

- Period reload on start, reset, and terminal count

- Interrupt on terminal count, compare true, or capture

- Dynamic counter reads

- Timer capture mode

- Count while enable signal is asserted mode

- Free run mode

- One Shot mode (stop at end of period)

- Complementary PWM outputs with deadband

- PWM output kill

#### Figure 7-15. Timer/Counter/PWM

## 9. Programming, Debug Interfaces, Resources

PSoC devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware. Three interfaces are available: JTAG, SWD, and SWV. JTAG and SWD support all programming and debug features of the device. JTAG also supports standard JTAG scan chains for board level test and chaining multiple JTAG devices to a single JTAG connection.

For more information on PSoC 3 Programming, refer to the PSoC<sup>®</sup> 3 Device Programming Specifications.

Complete Debug on Chip (DoC) functionality enables full device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator IDE software provides fully integrated programming and debug support for PSoC devices. The low cost MiniProg3 programmer and debugger is designed to provide full programming and debug support of PSoC devices in conjunction with the PSoC Creator IDE. PSoC JTAG, SWD, and SWV interfaces are fully compatible with industry standard third party tools.

All DOC circuits are disabled by default and can only be enabled in firmware. If not enabled, the only way to reenable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables DOC. Disabling DOC features, robust flash protection, and hiding custom analog and digital functionality inside the PSoC device provide a level of security not possible with multichip application solutions. Additionally, all device interfaces can be permanently disabled (Device Security) for applications concerned about phishing attacks due to a maliciously reprogrammed device. Permanently disabling interfaces is not recommended in most applications because you cannot access the device later. Because all programming, debug, and test interfaces are disabled when Device Security is enabled, PSoCs with Device Security enabled may not be returned for failure analysis.

#### Table 9-1. Debug Configurations

| Debug and Trace Configuration | GPIO Pins Used |

|-------------------------------|----------------|

| All debug and trace disabled  | 0              |

| JTAG                          | 4 or 5         |

| SWD                           | 2              |

| SWV                           | 1              |

| SWD + SWV                     | 3              |

## 9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG interface is used for programming the flash memory, debugging, I/O scan chains, and JTAG device chaining.

PSoC 3 has certain timing requirements to be met for entering programming mode through the JTAG interface. Due to these timing requirements, not all standard JTAG programmers, or standard JTAG file formats such as SVF or STAPL, can support PSoC 3 programming. The list of programmers that support PSoC 3 programming is available at

http://www.cypress.com/go/programming.

The JTAG clock frequency can be up to 14 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit transfers, or 1/5 of the CPU clock frequency for 32-bit transfers. By default, the JTAG pins are enabled on new devices but the JTAG interface can be disabled, allowing these pins to be used as GPIO instead.

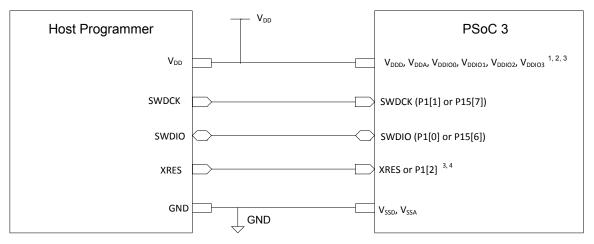

## 9.2 Serial Wire Debug Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D– pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8  $\mu$ s (key window) after reset, that pin pair

(JTAG or USB) receives a predetermined acquire sequence of 1s and 0s. If the NVL latches are set for SWD (see Section 5.5), this sequence need not be applied to the JTAG pin pair. The acquire sequence must always be applied to the USB pin pair.

SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

## Figure 9-2. SWD Interface Connections between PSoC 3 and Programmer

<sup>1</sup> The voltage levels of the Host Programmer and the PSoC 3 voltage domains involved in Programming should be the same. XRES pin (XRES\_N or P1[2]) is powered by V<sub>DDI01</sub>. The USB SWD pins are powered by V<sub>DDD</sub>. So for Programming using the USB SWD pins with XRES pin, the V<sub>DDD</sub>, V<sub>DDI01</sub> of PSoC 3 should be at the same voltage level as Host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDI01</sub>. So V<sub>DDI01</sub> of PSoC 3 should be at same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDI01</sub>. So V<sub>DDI01</sub> of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDI02</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programming. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI01</sub>, Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDI02</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer.

<sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

- <sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- <sup>4</sup> P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48pin devices, but use dedicated XRES pin for rest of devices.

## 9.3 Debug Features

Using the JTAG or SWD interface, the CY8C32 supports the following debug features:

- Halt and single-step the CPU

- View and change CPU and peripheral registers, and RAM addresses

- Eight program address breakpoints

- One memory access breakpoint—break on reading or writing any memory address and data value

- Break on a sequence of breakpoints (non recursive)

- Debugging at the full speed of the CPU

- Compatible with PSoC Creator and MiniProg3 programmer and debugger

- Standard JTAG programming and debugging interfaces make CY8C32 compatible with other popular third-party tools (for example, ARM / Keil)

### 9.4 Trace Features

The CY8C32 supports the following trace features when using JTAG or SWD:

- Trace the 8051 program counter (PC), accumulator register (ACC), and one SFR / 8051 core RAM register

- Trace depth up to 1000 instructions if all registers are traced, or 2000 instructions if only the PC is traced (on devices that include trace memory)

- Program address trigger to start tracing

- Trace windowing, that is, only trace when the PC is within a given range

- Two modes for handling trace buffer full: continuous (overwriting the oldest trace data) or break when trace buffer is full

#### 9.5 Single Wire Viewer Interface

The SWV interface is closely associated with SWD but can also be used independently. SWV data is output on the JTAG interface's TDO pin. If using SWV, you must configure the device for SWD, not JTAG. SWV is not supported with the JTAG interface.

SWV is ideal for application debug where it is helpful for the firmware to output data similar to 'printf' debugging on PCs. The SWV is ideal for data monitoring, because it requires only a single pin and can output data in standard UART format or Manchester encoded format. For example, it can be used to tune a PID control loop in which the output and graphing of the three error terms greatly simplifies coefficient tuning.

The following features are supported in SWV:

- 32 virtual channels, each 32 bits long

- Simple, efficient packing and serializing protocol

- Supports standard UART format (N81)

## 9.6 Programming Features

The JTAG and SWD interfaces provide full programming support. The entire device can be erased, programmed, and verified. You can increase flash protection levels to protect firmware IP. Flash protection can only be reset after a full device erase. Individual flash blocks can be erased, programmed, and verified, if block security settings permit.

#### 9.7 Device Security

PSoC 3 offers an advanced security feature called device security, which permanently disables all test, programming, and debug ports, protecting your application from external access. The device security is activated by programming a 32-bit key (0×50536F43) to a Write Once Latch (WOL).

The Write Once Latch is a type of nonvolatile latch (NVL). The cell itself is an NVL with additional logic wrapped around it. Each WOL device contains four bytes (32 bits) of data. The wrapper outputs a '1' if a super-majority (28 of 32) of its bits match a pre-determined pattern (0×50536F43); it outputs a '0' if this majority is not reached. When the output is 1, the Write Once NV latch locks the part out of Debug and Test modes; it also permanently gates off the ability to erase or alter the contents of the latch. Matching all bits is intentionally not required, so that single (or few) bit failures do not deassert the WOL output. The state of the NVL bits after wafer processing is truly random with no tendency toward 1 or 0.

The WOL only locks the part after the correct 32-bit key (0×50536F43) is loaded into the NVL's volatile memory, programmed into the NVL's nonvolatile cells, and the part is reset. The output of the WOL is only sampled on reset and used to disable the access. This precaution prevents anyone from reading, erasing, or altering the contents of the internal memory.

The user can write the key into the WOL to lock out external access only if no flash protection is set (see "Flash Security" on page 24). However, after setting the values in the WOL, a user still has access to the part until it is reset. Therefore, a user can write the key into the WOL, program the flash protection data, and then reset the part to lock it.

If the device is protected with a WOL setting, Cypress cannot perform failure analysis and, therefore, cannot accept RMAs from customers. The WOL can be read out via SWD port to electrically identify protected parts. The user can write the key in WOL to lock out external access only if no flash protection is set. For more information on how to take full advantage of the security features in PSoC see the PSoC 3 TRM.

#### Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress datasheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

## **11.2 Device Level Specifications**

Specifications are valid for –40  $^{\circ}C \le T_A \le 85 ~^{\circ}C$  and  $T_J \le 100 ~^{\circ}C$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.2.1 Device Level Specifications

## Table 11-2. DC Specifications

| Parameter                           | Description                                                  | Conditions                                                                            |                               | Min  | Typ <sup>[22]</sup> | Max                                    | Units |

|-------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------|------|---------------------|----------------------------------------|-------|

| V <sub>DDA</sub>                    | Analog supply voltage and input to analog core regulator     | Analog core regulato                                                                  | Analog core regulator enabled |      | _                   | 5.5                                    | V     |

| V <sub>DDA</sub>                    | Analog supply voltage, analog regulator bypassed             | Analog core regulato                                                                  | r disabled                    | 1.71 | 1.8                 | 1.89                                   | V     |

| V <sub>DDD</sub>                    | Digital supply voltage relative to V <sub>SSD</sub>          | Digital core regulator                                                                | enabled                       | 1.8  | -                   | V <sub>DDA</sub> <sup>[18]</sup>       | V     |

| • DDD                               |                                                              | Digital core regulator enabled                                                        |                               | 1    | -                   | V <sub>DDA</sub> + 0.1 <sup>[24]</sup> | v     |

| V <sub>DDD</sub>                    | Digital supply voltage, digital regulator<br>bypassed        | Digital core regulator                                                                | disabled                      | 1.71 | 1.8                 | 1.89                                   | V     |

| V <sub>DDIO</sub> <sup>[19]</sup>   | I/O supply voltage relative to V <sub>SSIO</sub>             |                                                                                       |                               | 1.71 | -                   | V <sub>DDA</sub> <sup>[18]</sup>       | V     |

|                                     |                                                              |                                                                                       |                               | -    | -                   | V <sub>DDA</sub> + 0.1 <sup>[24]</sup> |       |

| V <sub>CCA</sub>                    | Direct analog core voltage input (Analog regulator bypass)   | Analog core regulato                                                                  | r disabled                    | 1.71 | 1.8                 | 1.89                                   | V     |

| V <sub>CCD</sub>                    | Direct digital core voltage input (Digital regulator bypass) | Digital core regulator                                                                | disabled                      | 1.71 | 1.8                 | 1.89                                   | V     |

|                                     | Active Mode                                                  |                                                                                       |                               |      |                     |                                        |       |

|                                     | Only IMO and CPU clock enabled. CPU                          | V <sub>DDX</sub> = $2.7 V - 5.5 V$ ;<br>V <sub>DDX</sub> = $6 MHz^{[23]}$ T = $25 °C$ | T = -40 °C                    | -    | 1.2                 | 2.9                                    |       |

|                                     | executing simple loop from instruction buffer.               |                                                                                       |                               | -    | 1.2                 | 3.1                                    |       |

|                                     |                                                              |                                                                                       | T = 85 °C                     | -    | 4.9                 | 7.7                                    |       |

|                                     |                                                              | $V_{PDV} = 2.7 V - 5.5 V$                                                             | -                             | 1.3  | 2.9                 |                                        |       |

|                                     |                                                              | V <sub>DDX</sub> = 2.7 V – 5.5 V;<br>F <sub>CPU</sub> = 3 MHz <sup>[23]</sup>         | T = 25 °C                     | -    | 1.6                 | 3.2                                    |       |

|                                     |                                                              |                                                                                       | T = 85 °C                     | _    | 4.8                 | 7.5                                    |       |

|                                     |                                                              |                                                                                       | T = -40 °C                    | -    | 2.1                 | 3.7                                    |       |

|                                     |                                                              | V <sub>DDX</sub> = 2.7 V – 5.5 V;<br>F <sub>CPU</sub> = 6 MHz                         | T = 25 °C                     | -    | 2.3                 | 3.9                                    |       |

| I <sub>DD</sub> <sup>[20, 21]</sup> |                                                              |                                                                                       | T = 85 °C                     | _    | 5.6                 | 8.5                                    | mA    |

|                                     | IMO enabled, bus clock and CPU clock                         | $V_{DDX} = 2.7 V - 5.5 V;$                                                            | T = -40 °C                    | -    | 3.5                 | 5.2                                    |       |

|                                     | enabled. CPU executing program from                          | $F_{CPU} = 12 \text{ MHz}^{[23]}$                                                     | T = 25 °C                     | -    | 3.8                 | 5.5                                    |       |

|                                     | flash.                                                       |                                                                                       | T = 85 °C                     | -    | 7.1                 | 9.8                                    |       |

|                                     |                                                              | $V_{DDX} = 2.7 V - 5.5 V;$                                                            | T = -40 °C                    | -    | 6.3                 | 8.1                                    |       |

|                                     |                                                              | $F_{CPU}^{DDM} = 24 \text{ MHz}^{[23]}$                                               | T = 25 °C                     | _    | 6.6                 | 8.3                                    |       |

|                                     |                                                              |                                                                                       | T = 85 °C                     | -    | 10                  | 13                                     |       |

|                                     |                                                              | $V_{DDX} = 2.7 V - 5.5 V;$                                                            | T = -40 °C                    | _    | 11.5                | 13.5                                   |       |

|                                     |                                                              | $F_{CPU} = 48 \text{ MHz}^{[23]}$                                                     | T = 25 °C                     | -    | 12                  | 14                                     |       |

|                                     |                                                              |                                                                                       | T = 85 °C                     | _    | 15.5                | 18.5                                   |       |

#### Notes

18. The power supplies can be brought up in any sequence however once stable  $V_{DDA}$  must be greater than or equal to all other supplies. 19. The  $V_{DDIO}$  supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin  $\leq V_{DDIO} \leq V_{DDA}$ . 20. Total current for all power domains: digital ( $I_{DDD}$ ), analog ( $I_{DDA}$ ), and I/Os ( $I_{DDIO0, 1, 2, 3}$ ). Boost not included. All I/Os floating.

21. The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find the CPU current at the frequency of interest and add peripheral currents for your particular system from the device datasheet and component datasheets.

22.  $V_{DDX}$  = 3.3 V. 23. Based on device characterizations (Not production tested).

24. Guaranteed by design, not production tested.

## Table 11-2. DC Specifications (continued)

| Parameter | Description                                                                                                                        | Conditions                                                                        |            | Min | Typ <sup>[22]</sup> | Max | Units    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------|-----|---------------------|-----|----------|

|           | Sleep Mode <sup>[25]</sup>                                                                                                         |                                                                                   |            |     |                     |     |          |

|           | CPU = OFF                                                                                                                          | V <sub>DD</sub> = V <sub>DDIO</sub> =                                             | T = -40 °C | -   | 1.1                 | 2.3 | μA       |

|           | RTC = ON (= ECO32K ON, in low-power                                                                                                | 4.5 V - 5.5 V                                                                     | T = 25 °C  | _   | 1.1                 | 2.2 |          |

|           | mode)<br>Sleep timer = ON (= ILO ON at 1 kHz) <sup>[26]</sup>                                                                      |                                                                                   | T = 85 °C  | _   | 15                  | 30  |          |

|           | WDT = OFF                                                                                                                          | V <sub>DD</sub> = V <sub>DDIO</sub> =                                             | T = -40 °C | _   | 1                   | 2.2 |          |

|           | I <sup>2</sup> C Wake = OFF<br>Comparator = OFF                                                                                    | 2.7 V – 3.6 V                                                                     | T = 25 °C  | _   | 1                   | 2.1 |          |

|           | POR = ON                                                                                                                           |                                                                                   | T = 85 °C  | _   | 12                  | 28  |          |

|           | Boost = OFF                                                                                                                        | V <sub>DD</sub> = V <sub>DDO</sub> =                                              | T = 25 °C  | _   | 2.2                 | 4.2 |          |

|           | SIO pins in single ended input, unregulated output mode                                                                            | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>1.71 V – 1.95 V <sup>[27]</sup>          |            |     |                     |     |          |

|           | Comparator = ON                                                                                                                    | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>2.7 V – 3.6 V <sup>[28]</sup>            | T = 25 °C  | —   | 2.2                 | 2.7 |          |

|           | CPU = OFF<br>RTC = OFF                                                                                                             | $2.7 V - 3.6 V^{[20]}$                                                            |            |     |                     |     |          |

|           | Sleep timer = OFF                                                                                                                  |                                                                                   |            |     |                     |     |          |

|           | WDT = OFF                                                                                                                          |                                                                                   |            |     |                     |     |          |

|           | I <sup>2</sup> C Wake = OFF<br>POR = ON                                                                                            |                                                                                   |            |     |                     |     |          |

|           | Boost = OFF                                                                                                                        |                                                                                   |            |     |                     |     |          |

|           | SIO pins in single ended input, unregulated                                                                                        |                                                                                   |            |     |                     |     |          |

|           | output mode                                                                                                                        |                                                                                   | T 05 00    |     |                     |     |          |

|           | I <sup>2</sup> C Wake = ON<br>CPU = OFF                                                                                            | $V_{DD} = V_{DDIO} =$<br>2.7 V - 3.6 V <sup>[28]</sup>                            | T = 25 °C  | -   | 2.2                 | 2.8 |          |

|           | RTC = OFF                                                                                                                          | 2.7 4 0.0 4                                                                       |            |     |                     |     |          |

|           | Sleep timer = OFF                                                                                                                  |                                                                                   |            |     |                     |     |          |

|           | WDT = OFF<br>Comparator = OFF                                                                                                      |                                                                                   |            |     |                     |     |          |

|           | POR = ON                                                                                                                           |                                                                                   |            |     |                     |     |          |

|           | Boost = OFF                                                                                                                        |                                                                                   |            |     |                     |     |          |

|           | SIO pins in single ended input, unregulated                                                                                        |                                                                                   |            |     |                     |     |          |

|           | output mode<br>Hibernate Mode <sup>[25]</sup>                                                                                      |                                                                                   |            |     |                     |     |          |

|           | Hibernate mode current                                                                                                             | V <sub>DD</sub> = V <sub>DDIO</sub> =                                             | T = -40 °C | _   | 0.2                 | 1.5 | μA       |

|           | All regulators and oscillators off                                                                                                 | 4.5 V - 5.5 V                                                                     | T = 25 °C  | _   | 0.5                 | 1.5 | - ·      |

|           | SRAM retention<br>GPIO interrupts are active                                                                                       |                                                                                   | T = 85 °C  | _   | 4.1                 | 5.3 |          |

|           | Boost = OFF                                                                                                                        | V <sub>DD</sub> = V <sub>DDIO</sub> =                                             | T = -40 °C | _   | 0.2                 | 1.5 |          |

|           |                                                                                                                                    | 2.7 V – 3.6 V                                                                     | T = 25 °C  | _   | 0.2                 | 1.5 |          |

|           | output<br>mode                                                                                                                     |                                                                                   | T = 85 °C  | _   | 3.2                 | 4.2 |          |

|           |                                                                                                                                    | Vpp = Vppio =                                                                     | T = -40 °C | _   | 0.2                 | 1.5 |          |

|           |                                                                                                                                    | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>1.71 V – 1.95 V <sup>[27]</sup>          | T = 25 °C  | _   | 0.3                 | 1.5 |          |

|           |                                                                                                                                    |                                                                                   | T = 85 °C  | _   | 3.3                 | 4.3 |          |

|           |                                                                                                                                    |                                                                                   | 1          |     |                     | 0.0 |          |

|           | Analog current consumption while device is                                                                                         | V <sub>DDA</sub> ≤ 3.6 V                                                          |            | _   | 0.3                 | 0.6 | mA       |

| DDAR      | Analog current consumption while device is reset <sup>[29]</sup>                                                                   | DDA                                                                               |            | -   | 0.3                 | 3.3 | mA<br>mA |

| DDAR      | Analog current consumption while device is reset <sup>[29]</sup> Digital current consumption while device is reset <sup>[29]</sup> | $V_{DDA} \le 3.6 \text{ V}$ $V_{DDA} > 3.6 \text{ V}$ $V_{DDD} \le 3.6 \text{ V}$ |            | -   |                     |     |          |

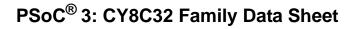

V<sub>DDD</sub> = 3.3 V, 25 pF Load

Table 11-16. USB Driver AC Specifications

| Parameter | Description                     | Conditions                                                                          | Min | Тур | Max  | Units |

|-----------|---------------------------------|-------------------------------------------------------------------------------------|-----|-----|------|-------|

| Tr        | Transition rise time            |                                                                                     | -   | -   | 20   | ns    |

| Tf        | Transition fall time            |                                                                                     | -   | -   | 20   | ns    |

| TR        | Rise/fall time matching         | V <sub>USB_5</sub> , V <sub>USB_3.3</sub> , see USB DC<br>Specifications on page 98 | 90% | -   | 111% |       |

| Vcrs      | Output signal crossover voltage |                                                                                     | 1.3 | -   | 2    | V     |

## 11.4.4 XRES

## Table 11-17. XRES DC Specifications

| Parameter       | Description                                                   | Conditions | Min                   | Тур | Max               | Units |

|-----------------|---------------------------------------------------------------|------------|-----------------------|-----|-------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  |            | $0.7 \times V_{DDIO}$ | _   | _                 | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   |            | -                     | -   | 0.3 ×             | V     |

|                 |                                                               |            |                       |     | V <sub>DDIO</sub> |       |

| Rpullup         | Pull-up resistor                                              |            | 3.5                   | 5.6 | 8.5               | kΩ    |

| C <sub>IN</sub> | Input capacitance <sup>[43]</sup>                             |            | _                     | 3   | -                 | pF    |

| V <sub>H</sub>  | Input voltage hysteresis<br>(Schmitt-Trigger) <sup>[43]</sup> |            | -                     | 100 | _                 | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |            | -                     | _   | 100               | μA    |

## Table 11-18. XRES AC Specifications

| Parameter          | Description       | Conditions | Min | Тур | Max | Units |

|--------------------|-------------------|------------|-----|-----|-----|-------|

| T <sub>RESET</sub> | Reset pulse width |            | 1   | -   | -   | μs    |

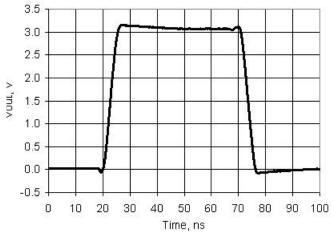

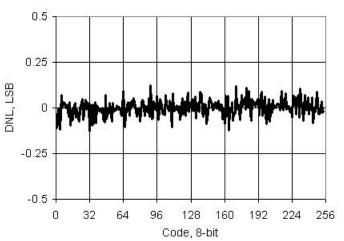

Figure 11-28. IDAC DNL vs Input Code, Range = 255  $\mu\text{A},$  Source Mode

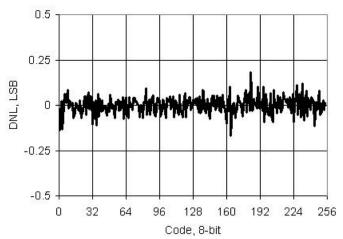

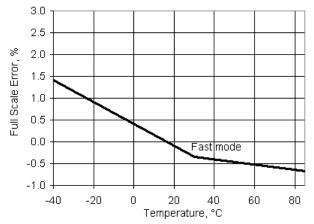

Figure 11-30. IDAC INL vs Temperature, Range = 255  $\mu A,$  High speed mode

Figure 11-29. IDAC DNL vs Input Code, Range = 255  $\mu A,$  Sink Mode

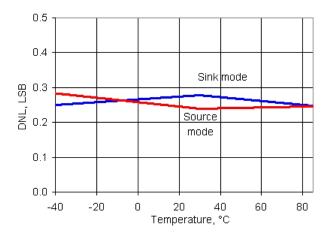

Figure 11-31. IDAC DNL vs Temperature, Range = 255  $\mu\text{A},$  High speed mode

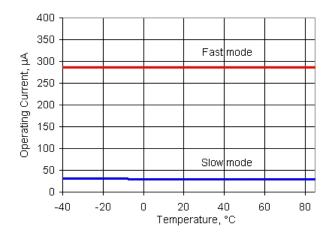

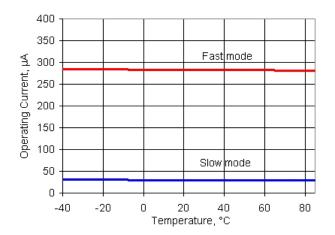

Figure 11-34. IDAC Operating Current vs Temperature, Range =  $255 \mu$ A, Code = 0, Source Mode

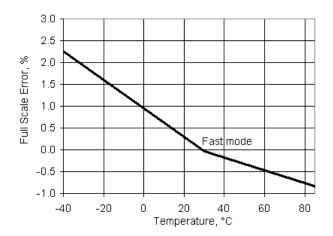

Figure 11-33. IDAC Full Scale Error vs Temperature, Range =  $255 \mu$ A, Sink Mode

Figure 11-35. IDAC Operating Current vs Temperature, Range = 255  $\mu$ A, Code = 0, Sink Mode

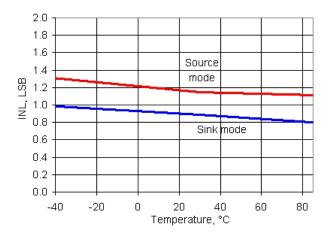

## 11.5.6 Voltage Digital to Analog Converter (VDAC)

See the VDAC component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

## Table 11-28. VDAC DC Specifications

| Parameter        | Description                               | Conditions                        | Min | Тур  | Max  | Units   |

|------------------|-------------------------------------------|-----------------------------------|-----|------|------|---------|

|                  | Resolution                                |                                   | -   | 8    | -    | bits    |

| INL1             | Integral nonlinearity                     | 1 V scale                         | -   | ±2.1 | ±2.5 | LSB     |

| INL4             | Integral nonlinearity <sup>[52]</sup>     | 4 V scale                         | -   | ±2.1 | ±2.5 | LSB     |

| DNL1             | Differential nonlinearity                 | 1 V scale                         | -   | ±0.3 | ±1   | LSB     |

| DNL4             | Differential nonlinearity <sup>[52]</sup> | 4 V scale                         | -   | ±0.3 | ±1   | LSB     |

| Rout             | Output resistance                         | 1 V scale                         | -   | 4    | -    | kΩ      |

|                  |                                           | 4 V scale                         | -   | 16   | -    | kΩ      |

| V <sub>OUT</sub> | Output voltage range, code = 255          | 1 V scale                         | -   | 1.02 | -    | V       |

|                  |                                           | 4 V scale, V <sub>DDA</sub> = 5 V | -   | 4.08 | -    | V       |

|                  | Monotonicity                              |                                   | -   | -    | Yes  | -       |

| V <sub>OS</sub>  | Zero scale error                          |                                   | -   | 0    | ±0.9 | LSB     |

| Eg               | Gain error                                | 1 V scale                         | -   | -    | ±2.5 | %       |

|                  |                                           | 4 V scale                         | -   | -    | ±2.5 | %       |

| TC_Eg            | Temperature coefficient, gain error       | 1 V scale                         | -   | -    | 0.03 | %FSR/°C |

|                  |                                           | 4 V scale                         | -   | -    | 0.03 | %FSR/°C |

| I <sub>DD</sub>  | Operating current                         | Low speed mode                    | -   | -    | 100  | μA      |

|                  |                                           | High speed mode                   | -   | -    | 500  | μA      |

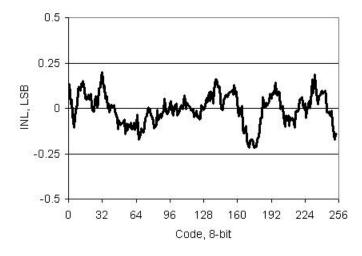

## Figure 11-40. VDAC INL vs Input Code, 1 V Mode

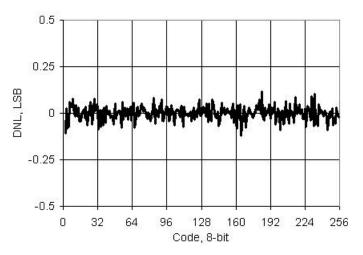

## Figure 11-41. VDAC DNL vs Input Code, 1 V Mode

Note 52. Based on device characterization (Not production tested).

## 11.5.7 Temperature Sensor

## Table 11-30. Temperature Sensor Specifications

| Parameter | Description          | Conditions              | Min | Тур | Max | Units |

|-----------|----------------------|-------------------------|-----|-----|-----|-------|

|           | Temp sensor accuracy | Range: –40 °C to +85 °C | -   | ±5  | _   | °C    |

11.5.8 LCD Direct Drive

## Table 11-31. LCD Direct Drive DC Specifications

| Parameter           | Description                                                                         | Conditions                                                                                                                                                                                 | Min | Тур                    | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|------|-------|

| Icc                 | LCD system operating current                                                        | Device sleep mode with wakeup at 400-Hz rate to refresh LCDs, bus clock = 3 MHz, $V_{DDIO} = V_{DDA} = 3 V$ , 4 commons, 16 segments, 1/4 duty cycle, 50 Hz frame rate, no glass connected | -   | 38                     | -    | μΑ    |

| I <sub>CC_SEG</sub> | Current per segment driver                                                          | Strong drive mode                                                                                                                                                                          | -   | 260                    | -    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $V_{DDA} \geq 3~V$ and $V_{DDA} \geq V_{BIAS}$                                                                                                                                             | 2   | -                      | 5    | V     |

|                     | LCD bias step size                                                                  | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                | -   | 9.1 × V <sub>DDA</sub> | -    | mV    |

|                     | LCD capacitance per<br>segment/common driver                                        | Drivers may be combined                                                                                                                                                                    | _   | 500                    | 5000 | pF    |

|                     | Long term segment offset                                                            |                                                                                                                                                                                            | -   | -                      | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver)                                            | V <sub>DDIO</sub> = 5.5V, strong drive mode                                                                                                                                                | 355 | -                      | 710  | μA    |

## Table 11-32. LCD Direct Drive AC Specifications

| Parameter        | Description    | Conditions | Min | Тур | Max | Units |

|------------------|----------------|------------|-----|-----|-----|-------|

| f <sub>LCD</sub> | LCD frame rate |            | 10  | 50  | 150 | Hz    |

# 13. Packaging

## Table 13-1. Package Characteristics

| Parameter       | Description                          | Conditions | Min | Тур   | Max | Units   |

|-----------------|--------------------------------------|------------|-----|-------|-----|---------|

| T <sub>A</sub>  | Operating ambient temperature        |            | -40 | 25.00 | 85  | °C      |

| TJ              | Operating junction temperature       |            | -40 | _     | 100 | °C      |

| T <sub>JA</sub> | Package $\theta_{JA}$ (48-pin SSOP)  |            | -   | 49    | -   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (48-pin QFN)   |            | -   | 14    | _   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (68-pin QFN)   |            | -   | 15    | -   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (100-pin TQFP) |            | -   | 34    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (48-pin SSOP)  |            | -   | 24    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (48-pin QFN)   |            | -   | 15    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (68-pin QFN)   |            | -   | 13    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (100-pin TQFP) |            | -   | 10    | -   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (72-pin CSP)   |            | -   | 18    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (72-pin CSP)   |            | _   | 0.13  | _   | °C/Watt |

## Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at Peak<br>Temperature |

|--------------|-----------------------------|-------------------------------------|

| 48-pin SSOP  | 260 °C                      | 30 seconds                          |

| 48-pin QFN   | 260 °C                      | 30 seconds                          |

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

| 72-pin CSP   | 260 °C                      | 30 seconds                          |

## Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 3 |

| 48-pin QFN   | MSL 3 |

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

| 72-pin CSP   | MSL 1 |

| Revision | nt Number:<br>ECN | Submission | Orig. of | Description of Change                                                                                                                                    |

|----------|-------------------|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                   | Date       | Change   |                                                                                                                                                          |

| *C       | 2903576           | 04/01/10   | MKEA     | Updated Vb pin in PCB Schematic.                                                                                                                         |

|          |                   |            |          | Updated Tstartup parameter in AC Specifications table.                                                                                                   |

|          |                   |            |          | Added Load regulation and Line regulation parameters to Inductive Boost                                                                                  |

|          |                   |            |          | Regulator DC Specifications table.                                                                                                                       |

|          |                   |            |          | Updated I <sub>CC</sub> parameter in LCD Direct Drive DC Specs table.<br>In page 1, updated internal oscillator range under Prescision programmable      |

|          |                   |            |          | clocking to start from 3 MHz.                                                                                                                            |

|          |                   |            |          | Updated I <sub>OUT</sub> parameter in LCD Direct Drive DC Specs table.                                                                                   |

|          |                   |            |          | Updated Table 6-2 and Table 6-3.                                                                                                                         |

|          |                   |            |          | Added bullets on CapSense in page 1; added CapSense column in Section 12                                                                                 |

|          |                   |            |          | Removed some references to footnote [1].                                                                                                                 |

|          |                   |            |          | Changed INC_Rn cycles from 3 to 2 (Table 4-1).                                                                                                           |

|          |                   |            |          | Added footnote in PLL AC Specification table.                                                                                                            |

|          |                   |            |          | Added PLL intermediate frequency row with footnote in PLL AC Specs table.                                                                                |

|          |                   |            |          | Added UDBs subsection under 11.6 Digital Peripherals.                                                                                                    |

|          |                   |            |          | Updated Figure 2-6 (PCB Layout).                                                                                                                         |

|          |                   |            |          | Updated Pin Descriptions section and modified Figures 6-6, 6-8, 6-9.                                                                                     |

|          |                   |            |          | Updated LVD in Tables 6-2 and 6-3; modified Low-power modes bullet in page 1                                                                             |

|          |                   |            |          | Added note to Figures 2-5 and 6-2; Updated Figure 6-2 to add capacitors for $V_{DDA}$                                                                    |

|          |                   |            |          | and V <sub>DDD</sub> pins.                                                                                                                               |

|          |                   |            |          | Updated boost converter section (6.2.2).                                                                                                                 |

|          |                   |            |          | Updated Tstartup values in Table 11-3.<br>Removed IPOR rows from Table 11-53. Updated 6.3.1.1, Power Voltage Level                                       |

|          |                   |            |          | Monitors.                                                                                                                                                |

|          |                   |            |          | Updated section 5.2 and Table 11-2 to correct suggestion of execution from flash                                                                         |

|          |                   |            |          | Updated IMO max frequency in Figure 6-1, Table 11-63, and Table 11-64.                                                                                   |

|          |                   |            |          | Updated $V_{\text{REF}}$ specs in Table 11-19.                                                                                                           |

|          |                   |            |          | Updated IDAC uncompensated gain error in Table 11-23.                                                                                                    |

|          |                   |            |          | Updated Delay from Interrupt signal input to ISR code execution from ISR code                                                                            |

|          |                   |            |          | in Table-71. Removed other line in table.                                                                                                                |

|          |                   |            |          | Added sentence to last paragraph of section 6.1.1.3.                                                                                                     |

|          |                   |            |          | Updated Tresp, high and low-power modes, in Table 11-22.                                                                                                 |

|          |                   |            |          | Updated f_TCK values in Table 11-58 and f_SWDCK values in Table 11-59.                                                                                   |

|          |                   |            |          | Updated SNR condition in Table 11-18.                                                                                                                    |

|          |                   |            |          | Updated sleep wakeup time in Table 6-3 and Tsleep in Table 11-3.                                                                                         |

|          |                   |            |          | Added 1.71 V $\leq$ V <sub>DDD</sub> $\leq$ 3.3 V, SWD over USBIO pins value to Table 11-59.                                                             |

|          |                   |            |          | Removed mention of hibernate reset (HRES) from page 1 features, Table 6-3,                                                                               |

|          |                   |            |          | Section 6.2.1.4, Section 6.3, and Section 6.3.1.1. Change PPOR/PRES to TBDs                                                                              |

|          |                   |            |          | in Section 6.3.1.1, Section 6.4.1.6 (changed PPOR to reset), Table 11-3 (changed PPOR to PRES), Table 11-53 (changed title, values TBD), and Table 11-54 |

|          |                   |            |          | (changed PPOR_TR to PRES_TR).                                                                                                                            |

|          |                   |            |          | Added sentence saying that LVD circuits can generate a reset to Section 6.3.1.1                                                                          |

|          |                   |            |          | Changed $I_{DD}$ values on page 1, page 5, and Table 11-2.                                                                                               |

|          |                   |            |          | Changed resume time value in Section 6.2.1.3.                                                                                                            |

|          |                   |            |          | Changed ESD HBM value in Table 11-1.                                                                                                                     |

|          |                   |            |          | Changed sample rate row in Table 11-18.                                                                                                                  |

|          |                   |            |          | Removed $V_{DDA}$ = 1.65 V rows and changed BWag value in Table 11-20.                                                                                   |

|          |                   |            |          | Changed Vioff values and changed CMRR value in Table 11-21.                                                                                              |

|          |                   |            |          | Changed INL max value in Table 11-25.                                                                                                                    |

|          |                   |            |          | Changed occurrences of "Block" to "Row" and deleted the "ECC not included"                                                                               |

|          |                   |            |          | footnote in Table 11-41.                                                                                                                                 |

|          |                   |            |          | Changed max response time value in Tables 11-54 and 11-56.                                                                                               |

|          |                   |            |          | Change the Startup time in Table 11-64.                                                                                                                  |

|          |                   |            |          | Added condition to intermediate frequency row in Table 11-70.                                                                                            |

|          |                   |            |          | Added row to Table 11-54.                                                                                                                                |

|          |                   |            |          | Added brown out note to Section 11.8.1.                                                                                                                  |

# 18. Sales, Solutions, and Legal Information

## Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

## Products

| Automotive               | cypress.com/go/automotive |

|--------------------------|---------------------------|

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

| Memory                   | cypress.com/go/memory     |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

## **PSoC<sup>®</sup> Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Community | Forums | Blogs | Video | Training

Technical Support cypress.com/go/support

© Cypress Semiconductor Corporation, 2009-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and ober countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software in binary code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.