#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3245lti-139 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1. Architectural Overview             | 4  |

|---------------------------------------|----|

| 2. Pinouts                            | 6  |

| 3. Pin Descriptions                   | 12 |

| 4. CPU                                | 13 |

| 4.1 8051 CPU                          | 13 |

| 4.2 Addressing Modes                  |    |

| 4.3 Instruction Set                   |    |

| 4.4 DMA and PHUB                      |    |

| 4.5 Interrupt Controller              | 20 |

| 5. Memory                             | 24 |

| 5.1 Static RAM                        | 24 |

| 5.2 Flash Program Memory              | 24 |

| 5.3 Flash Security                    |    |

| 5.4 EEPROM                            |    |

| 5.5 Nonvolatile Latches (NVLs)        |    |

| 5.6 External Memory Interface         |    |

| 5.7 Memory Map                        |    |

| 6. System Integration                 |    |

| 6.1 Clocking System                   |    |

| 6.2 Power System                      |    |

| 6.3 Reset                             |    |

| 6.4 I/O System and Routing            |    |

| 7. Digital Subsystem                  |    |

| 7.1 Example Peripherals               |    |

| 7.2 Universal Digital Block           |    |

| 7.3 UDB Array Description             |    |

| 7.4 DSI Routing Interface Description |    |

| 7.5 USB                               |    |

| 7.6 Timers, Counters, and PWMs        |    |

| 7.7 l <sup>2</sup> C                  |    |

| 8. Analog Subsystem                   |    |

| 8.1 Analog Routing                    |    |

| 8.2 Delta-sigma ADC                   |    |

| 8.3 Comparators                       |    |

| 8.4 LCD Direct Drive<br>8.5 CapSense  |    |

| 8.6 Temp Sensor                       |    |

| 8.7 DAC                               |    |

|                                       | 01 |

| 9. Programming, Debug Interfaces, Resources      |     |

|--------------------------------------------------|-----|

| 9.1 JTAG Interface                               |     |

| 9.2 Serial Wire Debug Interface                  |     |

| 9.3 Debug Features<br>9.4 Trace Features         |     |

| 9.5 Single Wire Viewer Interface                 |     |

| 9.6 Programming Features                         |     |

| 9.7 Device Security                              |     |

| 9.8 CSP Package Bootloader                       |     |

| 10. Development Support                          | 66  |

| 10.1 Documentation                               |     |

| 10.2 Online                                      |     |

| 10.3 Tools                                       |     |

| 11. Electrical Specifications                    |     |

| 11.1 Absolute Maximum Ratings                    |     |

| 11.2 Device Level Specifications                 |     |

| 11.3 Power Regulators<br>11.4 Inputs and Outputs |     |

| 11.5 Analog Peripherals                          |     |

| 11.6 Digital Peripherals                         |     |

| 11.7 Memory                                      |     |

| 11.8 PSoC System Resources                       |     |

| 11.9 Clocking                                    | 107 |

| 12. Ordering Information                         |     |

| 12.1 Part Numbering Conventions                  |     |

| 13. Packaging                                    | 113 |

| 14. Acronyms                                     | 117 |

| 15. Reference Documents                          | 118 |

| 16. Document Conventions                         | 119 |

| 16.1 Units of Measure                            | 119 |

| 17. Revision History                             | 120 |

| 18. Sales, Solutions, and Legal Information      | 128 |

| Worldwide Sales and Design Support               |     |

| Products                                         |     |

| PSoC® Solutions                                  |     |

| Cypress Developer Community                      |     |

| Technical Support                                | 128 |

# 5. Memory

# 5.1 Static RAM

CY8C32 Static RAM (SRAM) is used for temporary data storage. Up to 8 KB of SRAM is provided and can be accessed by the 8051 or the DMA controller. See Memory Map on page 26. Simultaneous access of SRAM by the 8051 and the DMA controller is possible if different 4-KB blocks are accessed.

# 5.2 Flash Program Memory

Flash memory in PSoC devices provides nonvolatile storage for user firmware, user configuration data, bulk data storage, and optional ECC data. The main flash memory area contains up to 64 KB of user program space.

Up to an additional 8 KB of flash space is available for Error Correcting Codes (ECC). If ECC is not used this space can store device configuration data and bulk user data. User code may not be run out of the ECC flash memory section. ECC can correct one bit error and detect two bit errors per 8 bytes of firmware memory; an interrupt can be generated when an error is detected.

The CPU reads instructions located in flash through a cache controller. This improves instruction execution rate and reduces system power consumption by requiring less frequent flash access. The cache has 8 lines at 64 bytes per line for a total of 512 bytes. It is fully associative, automatically controls flash power, and can be enabled or disabled. If ECC is enabled, the cache controller also performs error checking and correction, and interrupt generation.

Flash programming is performed through a special interface and preempts code execution out of flash. The flash programming interface performs flash erasing, programming and setting code protection levels. Flash in-system serial programming (ISSP), typically used for production programming, is possible through both the SWD and JTAG interfaces. In-system programming, typically used for bootloaders, is also possible using serial interfaces such as I<sup>2</sup>C, USB, UART, and SPI, or any communications protocol.

# 5.3 Flash Security

All PSoC devices include a flexible flash-protection model that prevents access and visibility to on-chip flash memory. This prevents duplication or reverse engineering of proprietary code. Flash memory is organized in blocks, where each block contains 256 bytes of program or data and 32 bytes of ECC or configuration data. A total of up to 256 blocks is provided on 64-KB flash devices.

The device offers the ability to assign one of four protection levels to each row of flash. Table 5-1 lists the protection modes available. Flash protection levels can only be changed by performing a complete flash erase. The Full Protection and Field Upgrade settings disable external access (through a debugging tool such as PSoC Creator, for example). If your application requires code update through a boot loader, then use the Field Upgrade setting. Use the Unprotected setting only when no security is needed in your application. The PSoC device also offers an advanced security feature called Device Security which permanently disables all test, programming, and debug ports, protecting your application from external access (see the "Device Security" section on page 65). For more information about how to take full advantage of the security features in PSoC, see the PSoC 3 TRM.

#### Table 5-1. Flash Protection

| Protection<br>Setting | Allowed                                              | Not Allowed                              |

|-----------------------|------------------------------------------------------|------------------------------------------|

| Unprotected           | External read and write<br>+ internal read and write | -                                        |

| Factory<br>Upgrade    | External write + internal read and write             | External read                            |

| Field Upgrade         | Internal read and write                              | External read and write                  |

| Full Protection       | Internal read                                        | External read and write + internal write |

#### Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress datasheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# 5.4 EEPROM

PSoC EEPROM memory is a byte-addressable nonvolatile memory. The CY8C32 has up to 2 KB of EEPROM memory to store user data. Reads from EEPROM are random access at the byte level. Reads are done directly; writes are done by sending write commands to an EEPROM programming interface. CPU code execution can continue from flash during EEPROM writes. EEPROM is erasable and writeable at the row level. The EEPROM is divided into 128 rows of 16 bytes each. The factory default values of all EEPROM bytes are 0.

Because the EEPROM is mapped to the 8051 xdata space, the CPU cannot execute out of EEPROM. There is no ECC hardware associated with EEPROM. If ECC is required it must be handled in firmware.

It can take as much as 20 milliseconds to write to EEPROM or flash. During this time the device should not be reset, or unexpected changes may be made to portions of EEPROM or flash. Reset sources (see Section 6.3.1) include XRES pin, software reset, and watchdog; care should be taken to make sure that these are not inadvertently activated. In addition, the low voltage detect circuits should be configured to generate an interrupt instead of a reset.

# 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2.

Table 5-2.

Device Configuration NVL Register Map

| Register Address | 7       | 6         | 5                            | 4 | 3            | 2         | 1     | 0        |

|------------------|---------|-----------|------------------------------|---|--------------|-----------|-------|----------|

| 0x00             | PRT3RE  | DM[1:0]   | PRT2RDM[1:0] PRT1RDM[1:0] PR |   | PRT2RDM[1:0] |           | PRT0  | RDM[1:0] |

| 0x01             | PRT12R  | DM[1:0]   | PRT6RDM[1:0] PRT5RDM[1:0]    |   | PRT4         | RDM[1:0]  |       |          |

| 0x02             | XRESMEN | DBGEN     |                              |   | PRT18        | 5RDM[1:0] |       |          |

| 0x03             |         | DIG_PHS_I | DLY[3:0] ECCEN DPS[          |   | DLY[3:0]     |           | [1:0] |          |

The details for individual fields and their factory default settings are shown in Table 5-3:.

#### Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                                        | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     | Controls reset drive mode of the corresponding IO port.<br>See "Reset Configuration" on page 44. All pins of the<br>port are set to the same mode. | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as an external reset. See "Pin Descriptions" on page 12, XRES description.                         | 0 (default for 68-pin 72-pin, and 100-pin parts) - GPIO<br>1 (default for 48-pin parts) - external reset                      |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                                       | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| DPS[1:0]         |                                                                                                                                                    | 00b - 5-wire JTAG<br>01b (default) - 4-wire JTAG<br>10b - SWD<br>11b - debug ports disabled                                   |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 24.                   | 0 - ECC disabled<br>1 (default) - ECC enabled                                                                                 |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                                             | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase / write cycles is limited – see "Nonvolatile Latches (NVL))" on page 100.

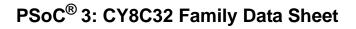

#### Figure 6-10. SIO Input/Output Block Diagram

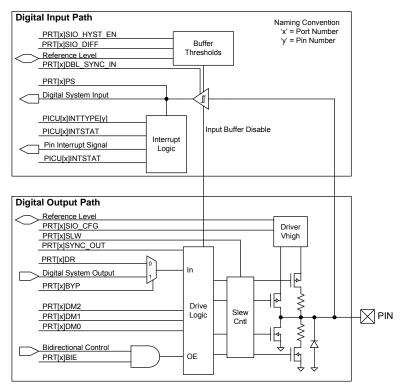

Figure 6-11. USBIO Block Diagram

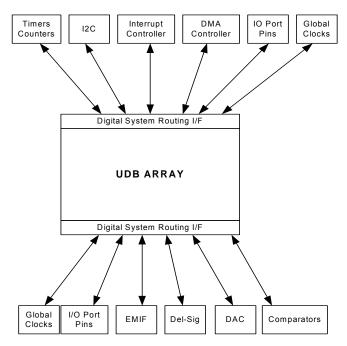

# Figure 7-9. Digital System Interconnect

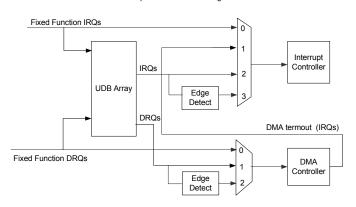

Interrupt and DMA routing is very flexible in the CY8C32 programmable architecture. In addition to the numerous fixed function peripherals that can generate interrupt requests, any data signal in the UDB array routing can also be used to generate a request. A single peripheral may generate multiple independent interrupt requests simplifying system and firmware design. Figure 7-10 shows the structure of the IDMUX (Interrupt/DMA Multiplexer).

#### Figure 7-10. Interrupt and DMA Processing in the IDMUX

Interrupt and DMA Processing in IDMUX

# 7.4.1 I/O Port Routing

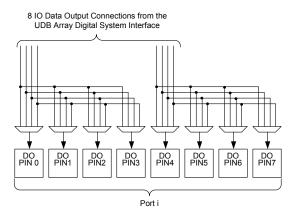

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

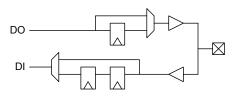

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In

conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

#### Figure 7-11. I/O Pin Synchronization Routing

#### Figure 7-12. I/O Pin Output Connectivity

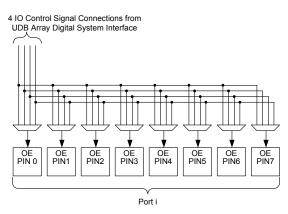

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

# Figure 7-13. I/O Pin Output Enable Connectivity

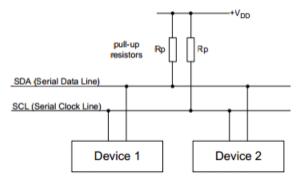

#### Figure 7-17. Connection of Devices to the I<sup>2</sup>C Bus

For most designs, the default values in Table 7-2 will provide excellent performance without any calculations. The default values were chosen to use standard resistor values between the minimum and maximum limits. The values in Table 7-2 work for designs with 1.8 V to 5.0V V<sub>DD</sub>, less than 200-pF bus capacitance (C<sub>B</sub>), up to 25  $\mu$ A of total input leakage (I<sub>IL</sub>), up to 0.4 V output voltage level (V<sub>OL</sub>), and a max V<sub>IH</sub> of 0.7 \* V<sub>DD</sub>. Standard Mode and Fast Mode can use either GPIO or SIO PSoC pins. Fast Mode Plus requires use of SIO pins to meet the V<sub>OL</sub> spec at 20 mA. Calculation of custom pull-up resistor values is required; if your design does not meet the default assumptions, you use series resistor value for low power consumption.

Table 7-2. Recommended default Pull-up Resistor Values

|                          | R <sub>P</sub> | Units |

|--------------------------|----------------|-------|

| Standard Mode – 100 kbps | 4.7 k, 5%      | Ω     |

| Fast Mode – 400 kbps     | 1.74 k, 1%     | Ω     |

| Fast Mode Plus – 1 Mbps  | 620, 5%        | Ω     |

Calculation of the ideal pull-up resistor value involves finding a value between the limits set by three equations detailed in the NXP  $I^2C$  specification. These equations are:

#### Equation 1:

$$R_{PMIN} = (V_{DD}(max) - V_{OL}(max))/(I_{OL}(min))$$

Equation 2:

$$R_{PMAX} = T_R(max)/0.8473 \times C_R(max)$$

#### **Equation 3:**

$R_{PMAX} = V_{DD}(min) - V_{IH}(min) + V_{NH}(min) / I_{IH}(max)$

Equation parameters:

$V_{DD}$  = Nominal supply voltage for I<sup>2</sup>C bus

$V_{OL}$  = Maximum output low voltage of bus devices.

$I_{OL}$  = Low-level output current from I<sup>2</sup>C specification

$T_R$  = Rise Time of bus from I<sup>2</sup>C specification

C<sub>B</sub> = Capacitance of each bus line including pins and PCB traces

V<sub>IH</sub> = Minimum high-level input voltage of all bus devices

$V_{\text{NH}}$  = Minimum high-level input noise margin from  $\text{I}^2\text{C}$  specification

I<sub>IH</sub> = Total input leakage current of all devices on the bus

The supply voltage (V<sub>DD</sub>) limits the minimum pull-up resistor value due to bus devices maximum low output voltage (V<sub>DL</sub>) specifications. Lower pull-up resistance increases current through the pins and can, therefore, exceed the spec conditions of V<sub>OL</sub>. Equation 1 is derived using Ohm's law to determine the minimum resistance that will still meet the V<sub>OL</sub> specification at 3 mA for standard and fast modes, and 20 mA for fast mode plus at the given V<sub>DD</sub>.

Equation 2 determines the maximum pull-up resistance due to bus capacitance. Total bus capacitance is comprised of all pin, wire, and trace capacitance on the bus. The higher the bus capacitance, the lower the pull-up resistance required to meet the specified bus speeds rise time due to RC delays. Choosing a pull-up resistance higher than allowed can result in failing timing requirements resulting in communication errors. Most designs with five or less  $I^2C$  devices and up to 20 centimeters of bus trace length have less than 100 pF of bus capacitance.

A secondary effect that limits the maximum pull-up resistor value is total bus leakage calculated in Equation 3. The primary source of leakage is I/O pins connected to the bus. If leakage is too high, the pull-ups will have difficulty maintaining an acceptable  $V_{IH}$  level causing communication errors. Most designs with five or less I<sup>2</sup>C devices on the bus have less than 10 µA of total leakage current.

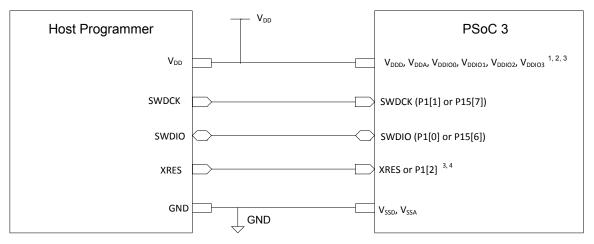

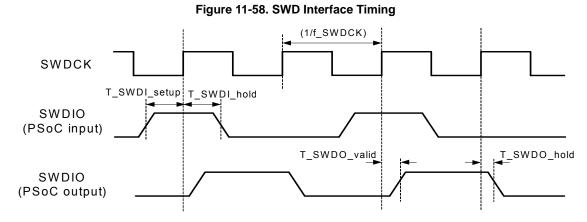

# 9.2 Serial Wire Debug Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D– pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8  $\mu$ s (key window) after reset, that pin pair

(JTAG or USB) receives a predetermined acquire sequence of 1s and 0s. If the NVL latches are set for SWD (see Section 5.5), this sequence need not be applied to the JTAG pin pair. The acquire sequence must always be applied to the USB pin pair.

SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

## Figure 9-2. SWD Interface Connections between PSoC 3 and Programmer

<sup>1</sup> The voltage levels of the Host Programmer and the PSoC 3 voltage domains involved in Programming should be the same. XRES pin (XRES\_N or P1[2]) is powered by V<sub>DDI01</sub>. The USB SWD pins are powered by V<sub>DDD</sub>. So for Programming using the USB SWD pins with XRES pin, the V<sub>DDD</sub>, V<sub>DDI01</sub> of PSoC 3 should be at the same voltage level as Host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDI01</sub>. So V<sub>DDI01</sub> of PSoC 3 should be at same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDI01</sub>. So V<sub>DDI01</sub> of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDI02</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programming. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI01</sub>, Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDI02</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer.

<sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

- <sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- <sup>4</sup> P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48pin devices, but use dedicated XRES pin for rest of devices.

| Table 11-7. | Recommended External Components for Boost Circuit |

|-------------|---------------------------------------------------|

|             |                                                   |

| Parameter          | Description                                                                                      | Conditions     | Min  | Тур  | Max  | Units |

|--------------------|--------------------------------------------------------------------------------------------------|----------------|------|------|------|-------|

| L <sub>BOOST</sub> | Boost inductor                                                                                   | 4.7 μH nominal | 3.7  | 4.7  | 5.7  | μH    |

|                    |                                                                                                  | 10 μH nominal  | 8.0  | 10.0 | 12.0 | μH    |

|                    |                                                                                                  | 22 μH nominal  | 17.0 | 22.0 | 27.0 | μH    |

| C <sub>BOOST</sub> | Total capacitance sum of V <sub>DDD</sub> , V <sub>DDA</sub> , V <sub>DDIO</sub> <sup>[34]</sup> |                | 17.0 | 26.0 | 31.0 | μF    |

| C <sub>BAT</sub>   | Battery filter capacitor                                                                         |                | 17.0 | 22.0 | 27.0 | μF    |

| I <sub>F</sub>     | Schottky diode average forward current                                                           |                | 1.0  | _    | -    | A     |

| V <sub>R</sub>     | Schottky reverse voltage                                                                         |                | 20.0 | -    | -    | V     |

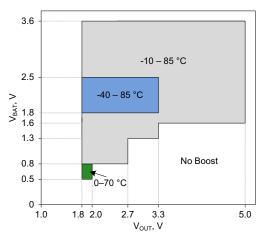

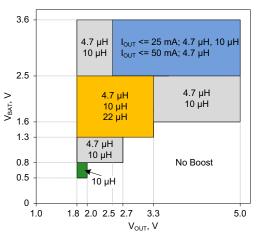

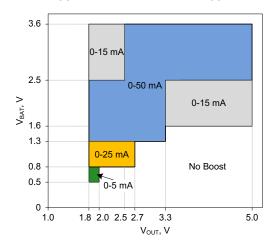

# Figure 11-8. T<sub>A</sub> range over $V_{BAT}$ and $V_{OUT}$

Figure 11-10.  $L_{BOOST}$  values over  $V_{BAT}$  and  $V_{OUT}$

# Figure 11-9. $I_{OUT}$ range over $V_{BAT}$ and $V_{OUT}$

#### Note

34. Based on device characterization (Not production tested).

# 11.4 Inputs and Outputs

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values.

When the power supplies ramp up, there are low-impedance connections between each GPIO pin and its  $V_{DDIO}$  supply. This causes the pin voltages to track  $V_{DDIO}$  until both  $V_{DDIO}$  and  $V_{DDA}$  reach the IPOR voltage, which can be as high as 1.45 V. At that point, the low-impedance connections no longer exist and the pins change to their normal NVL settings.

#### 11.4.1 GPIO

# Table 11-9. GPIO DC Specifications

| Parameter       | Description                                                   | Conditions                                                   | Min                     | Тур | Max                     | Units |

|-----------------|---------------------------------------------------------------|--------------------------------------------------------------|-------------------------|-----|-------------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  | CMOS Input, PRT[×]CTL = 0                                    | $0.7 \times V_{DDIO}$   | _   | _                       | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | CMOS Input, PRT[×]CTL = 0                                    | -                       | -   | $0.3 \times V_{DDIO}$   | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[×]CTL =<br>1, V <sub>DDIO</sub> < 2.7 V     | 0.7 × V <sub>DDIO</sub> | _   | -                       | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[×]CTL =<br>1, V <sub>DDIO</sub> ≥ 2.7V      | 2.0                     | _   | -                       | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | LVTTL Input, PRT[×]CTL =<br>1, V <sub>DDIO</sub> < 2.7 V     | -                       | -   | 0.3 × V <sub>DDIO</sub> | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | LVTTL Input, PRT[×]CTL =<br>1, V <sub>DDIO</sub> ≥ 2.7V      | -                       | -   | 0.8                     | V     |

| V <sub>OH</sub> | Output voltage high                                           | I <sub>OH</sub> = 4 mA at 3.3 V <sub>DDIO</sub>              | $V_{DDIO} - 0.6$        | -   | -                       | V     |

|                 |                                                               | I <sub>OH</sub> = 1 mA at 1.8 V <sub>DDIO</sub>              | $V_{DDIO} - 0.5$        | —   | -                       | V     |

| V <sub>OL</sub> | Output voltage low                                            | I <sub>OL</sub> = 8 mA at 3.3 V <sub>DDIO</sub>              | -                       | _   | 0.6                     | V     |

|                 |                                                               | I <sub>OL</sub> = 4 mA at 1.8 V <sub>DDIO</sub>              | -                       | _   | 0.6                     | V     |

|                 |                                                               | I <sub>OL</sub> = 3 mA at 3.3 V <sub>DDIO</sub>              | -                       | _   | 0.4                     | V     |

| Rpullup         | Pull-up resistor                                              |                                                              | 3.5                     | 5.6 | 8.5                     | kΩ    |

| Rpulldown       | Pull-down resistor                                            |                                                              | 3.5                     | 5.6 | 8.5                     | kΩ    |

| I <sub>IL</sub> | Input leakage current (absolute value) <sup>[36]]</sup>       | 25 °C, V <sub>DDIO</sub> = 3.0 V                             | -                       | -   | 2                       | nA    |

| C <sub>IN</sub> | Input capacitance <sup>[36]</sup>                             | GPIOs not shared with<br>opamp outputs, MHz ECO or<br>kHzECO | -                       | 4   | 7                       | pF    |

|                 |                                                               | GPIOs shared with MHz<br>ECO or kHzECO <sup>[37]</sup>       | -                       | 5   | 7                       | pF    |

|                 |                                                               | GPIOs shared with opamp outputs                              | -                       | _   | 18                      | pF    |

| V <sub>H</sub>  | Input voltage hysteresis (Schmitt-Trigger) <sup>[36]</sup>    |                                                              | -                       | 40  | -                       | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |                                                              | -                       | -   | 100                     | μA    |

| Rglobal         | Resistance pin to analog global bus                           | 25 °C, V <sub>DDIO</sub> = 3.0 V                             | _                       | 320 | -                       | Ω     |

| Rmux            | Resistance pin to analog mux bus                              | 25 °C, V <sub>DDIO</sub> = 3.0 V                             | _                       | 220 | _                       | Ω     |

Notes

36. Based on device characterization (Not production tested).

<sup>37.</sup> For information on designing with PSoC oscillators, refer to the application note, AN54439 - PSoC® 3 and PSoC 5 External Oscillator.

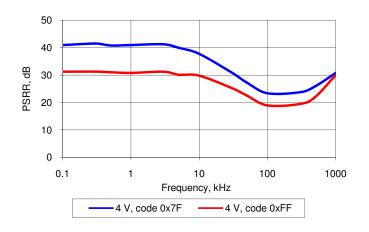

# Table 11-29. VDAC AC Specifications t

| Parameter        | Description                            | Conditions                                                      | Min | Тур  | Max  | Units     |

|------------------|----------------------------------------|-----------------------------------------------------------------|-----|------|------|-----------|

| F <sub>DAC</sub> | Update rate                            | 1 V scale                                                       | -   | -    | 1000 | ksps      |

|                  |                                        | 4 V scale                                                       | -   | -    | 250  | ksps      |

| TsettleP         | Settling time to 0.1%, step 25% to 75% | 1 V scale, Cload = 15 pF                                        | -   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                        | -   | 0.8  | 3.2  | μs        |

| TsettleN         | Settling time to 0.1%, step 75% to 25% | 1 V scale, Cload = 15 pF                                        | -   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                        | -   | 0.7  | 3    | μs        |

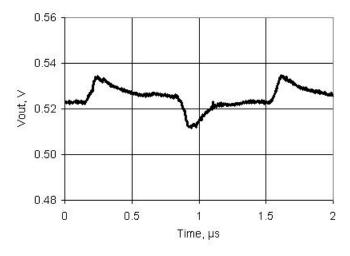

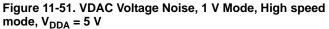

|                  | Voltage noise                          | Range = 1 V, High speed mode,<br>V <sub>DDA</sub> = 5 V, 10 kHz | -   | 750  | -    | nV/sqrtHz |

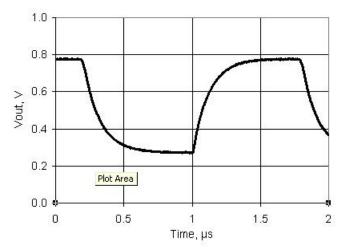

# Figure 11-48. VDAC Step Response, Codes 0x40 - 0xC0, 1 V Mode, High speed mode, $V_{DDA} = 5 V$

Figure 11-49. VDAC Glitch Response, Codes 0x7F - 0x80, 1 V Mode, High speed mode,  $V_{\text{DDA}}$  = 5 V

# 11.6.6 USB

#### Table 11-43. USB DC Specifications

| Parameter            | Description                                         | Conditions                                                                                          | Min  | Тур | Max  | Units |

|----------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|------|-------|

| V <sub>USB_5</sub>   | Device supply (V <sub>DDD</sub> ) for USB operation | USB configured, USB regulator<br>enabled                                                            | 4.35 | -   | 5.25 | V     |

| V <sub>USB_3.3</sub> |                                                     | USB configured, USB regulator bypassed                                                              | 3.15 | -   | 3.6  | V     |

| V <sub>USB_3</sub>   |                                                     | USB configured, USB regulator bypassed <sup>[54]</sup>                                              | 2.85 | -   | 3.6  | V     |

| IUSB_Configured      | Device supply current in device active              | V <sub>DDD</sub> = 5 V, F <sub>CPU</sub> = 1.5 MHz                                                  | -    | 10  | -    | mA    |

|                      | mode, bus clock and IMO = 24 MHz                    | V <sub>DDD</sub> = 3.3 V, F <sub>CPU</sub> = 1.5 MHz                                                | _    | 8   | -    | mA    |

| IUSB_Suspended       | Device supply current in device sleep mode          | V <sub>DDD</sub> = 5 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal   | -    | 0.5 | -    | mA    |

|                      |                                                     | V <sub>DDD</sub> = 5 V, disconnected from<br>USB host                                               | -    | 0.3 | -    | mA    |

|                      |                                                     | V <sub>DDD</sub> = 3.3 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal | _    | 0.5 | -    | mA    |

|                      |                                                     | V <sub>DDD</sub> = 3.3 V, disconnected from<br>USB host                                             | _    | 0.3 | -    | mA    |

# 11.6.7 Universal Digital Blocks (UDBs)

PSoC Creator provides a library of pre-built and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. See the component datasheets in PSoC Creator for full AC/DC specifications, APIs, and example code.

#### Table 11-44. UDB AC Specifications

| Parameter              | Description                                                              | Conditions                                       | Min | Тур | Max   | Units |

|------------------------|--------------------------------------------------------------------------|--------------------------------------------------|-----|-----|-------|-------|

| Datapath Per           | formance                                                                 |                                                  | •   | •   |       |       |

| F <sub>MAX_TIMER</sub> | Maximum frequency of 16-bit timer in a UDB pair                          |                                                  | -   | -   | 50.01 | MHz   |

| F <sub>MAX_ADDER</sub> | Maximum frequency of 16-bit adder in a UDB pair                          |                                                  | -   | -   | 50.01 | MHz   |

| F <sub>MAX_CRC</sub>   | Maximum frequency of 16-bit<br>CRC/PRS in a UDB pair                     |                                                  | -   | -   | 50.01 | MHz   |

| PLD Perform            | ance                                                                     |                                                  |     |     |       |       |

| F <sub>MAX_PLD</sub>   | Maximum frequency of a two-pass<br>PLD function in a UDB pair            |                                                  | -   | -   | 50.01 | MHz   |

| Clock to Outp          | but Performance                                                          |                                                  | •   | •   |       |       |

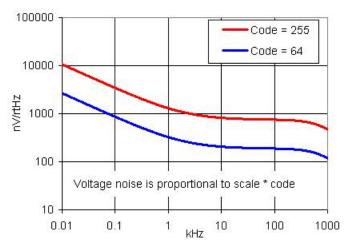

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-52 on page 99. | 25 °C, $V_{DDD} \ge 2.7 V$                       | -   | 20  | 25    | ns    |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-52 on page 99. | Worst-case placement, routing, and pin selection | -   | -   | 55    | ns    |

Note 54. Rise/fall time matching (TR) not guaranteed, see USB Driver AC Specifications on page 83.

# Figure 11-52. Clock to Output Performance

# 11.7 Memory

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

#### 11.7.1 Flash

#### Table 11-45. Flash DC Specifications

| Parameter | Description               | Conditions           | Min  | Тур | Max | Units |

|-----------|---------------------------|----------------------|------|-----|-----|-------|

|           | Erase and program voltage | V <sub>DDD</sub> pin | 1.71 | _   | 5.5 | V     |

#### Table 11-46. Flash AC Specifications

| Parameter          | Description                                                                | Conditions                                                           | Min | Тур | Max | Units   |

|--------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|---------|

| T <sub>WRITE</sub> | Row write time (erase + program)                                           |                                                                      | -   | 15  | 20  | ms      |

| T <sub>ERASE</sub> | Row erase time                                                             |                                                                      | -   | 10  | 13  | ms      |

|                    | Row program time                                                           |                                                                      | -   | 5   | 7   | ms      |

| T <sub>BULK</sub>  | Bulk erase time (16 KB to 64 KB)                                           |                                                                      | -   | -   | 35  | ms      |

|                    | Sector erase time (8 KB to 16 KB)                                          |                                                                      | -   | -   | 15  | ms      |

| T <sub>PROG</sub>  | Total device programming time                                              | No overhead <sup>[55]</sup>                                          | -   | 1.5 | 2   | seconds |

|                    | Flash data retention time, retention period measured from last erase cycle | Average ambient temp.<br>$T_A \le 55$ °C, 100 K erase/program cycles | 20  | -   | -   | years   |

|                    |                                                                            | Average ambient temp.<br>$T_A \le 85$ °C, 10 K erase/program cycles  | 10  | -   | _   |         |

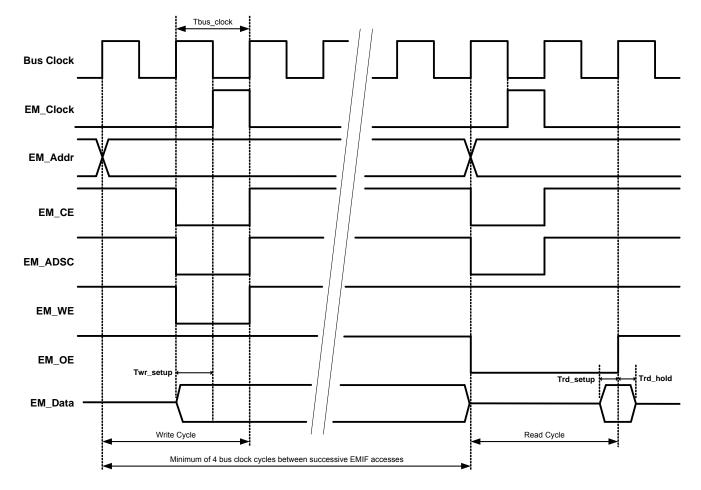

Figure 11-54. Synchronous Write and Read Cycle Timing, No Wait States

| Table 11-54. S | Synchronous | Write and Rea | ad Timing | Specifications <sup>[59]</sup> |

|----------------|-------------|---------------|-----------|--------------------------------|

|----------------|-------------|---------------|-----------|--------------------------------|

| Parameter  | Description                                                    | Conditions | Min             | Тур | Max | Units |

|------------|----------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[60]</sup>                            |            | -               | -   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[61]</sup>                               |            | 30.3            | -   | -   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge<br>of EM_Clock          |            | Tbus_clock – 10 | -   | -   | ns    |

| Trd_setup  | Time that EM_data must be valid before<br>rising edge of EM_OE |            | 5               | -   | -   | ns    |

| Trd_hold   | Time that EM_data must be valid after<br>rising edge of EM_OE  |            | 5               | _   | _   | ns    |

Notes

- 59. Based on device characterization (Not production tested).

60. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 76.

61. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

# 11.8 PSoC System Resources

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

#### 11.8.1 POR with Brown Out

For brown out detect in regulated mode,  $V_{DDD}$  and  $V_{DDA}$  must be  $\geq$  2.0 V. Brown out detect is not available in externally regulated mode.

#### Table 11-57. Precise Low-Voltage Reset (PRES) with Brown Out DC Specifications

| Parameter | Description          | Conditions   | Min  | Тур | Max  | Units |

|-----------|----------------------|--------------|------|-----|------|-------|

| PRESR     | Rising trip voltage  | Factory trim | 1.64 | -   | 1.68 | V     |

| PRESF     | Falling trip voltage |              | 1.62 | -   | 1.66 | V     |

#### Table 11-58. Power-on Reset (POR) with Brown Out AC Specifications

| Parameter | Description                                   | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------------------------------|------------|-----|-----|-----|-------|

| PRES_TR   | Response time                                 |            | -   | _   | 0.5 | μs    |

|           | V <sub>DDD</sub> /V <sub>DDA</sub> droop rate | Sleep mode | -   | 5   | -   | V/sec |

#### 11.8.2 Voltage Monitors

# Table 11-59. Voltage Monitors DC Specifications

| Parameter | Description              | Conditions | Min  | Тур  | Max  | Units |

|-----------|--------------------------|------------|------|------|------|-------|

| LVI       | Trip voltage             |            |      |      |      |       |

|           | LVI_A/D_SEL[3:0] = 0000b |            | 1.68 | 1.73 | 1.77 | V     |

|           | LVI_A/D_SEL[3:0] = 0001b |            | 1.89 | 1.95 | 2.01 | V     |

|           | LVI_A/D_SEL[3:0] = 0010b |            | 2.14 | 2.20 | 2.27 | V     |

|           | LVI_A/D_SEL[3:0] = 0011b |            | 2.38 | 2.45 | 2.53 | V     |

|           | LVI_A/D_SEL[3:0] = 0100b |            | 2.62 | 2.71 | 2.79 | V     |

|           | LVI_A/D_SEL[3:0] = 0101b |            | 2.87 | 2.95 | 3.04 | V     |

|           | LVI_A/D_SEL[3:0] = 0110b |            | 3.11 | 3.21 | 3.31 | V     |

|           | LVI_A/D_SEL[3:0] = 0111b |            | 3.35 | 3.46 | 3.56 | V     |

|           | LVI_A/D_SEL[3:0] = 1000b |            | 3.59 | 3.70 | 3.81 | V     |

|           | LVI_A/D_SEL[3:0] = 1001b |            | 3.84 | 3.95 | 4.07 | V     |

|           | LVI_A/D_SEL[3:0] = 1010b |            | 4.08 | 4.20 | 4.33 | V     |

|           | LVI_A/D_SEL[3:0] = 1011b |            | 4.32 | 4.45 | 4.59 | V     |

|           | LVI_A/D_SEL[3:0] = 1100b |            | 4.56 | 4.70 | 4.84 | V     |

|           | LVI_A/D_SEL[3:0] = 1101b |            | 4.83 | 4.98 | 5.13 | V     |

|           | LVI_A/D_SEL[3:0] = 1110b |            | 5.05 | 5.21 | 5.37 | V     |

|           | LVI_A/D_SEL[3:0] = 1111b |            | 5.30 | 5.47 | 5.63 | V     |

| HVI       | Trip voltage             |            | 5.57 | 5.75 | 5.92 | V     |

## Table 11-60. Voltage Monitors AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max | Units |

|-----------|-------------------------------|------------|-----|-----|-----|-------|

|           | Response time <sup>[64]</sup> |            | -   | -   | 1   | μs    |

#### 11.8.5 SWD Interface

# Table 11-63. SWD Interface AC Specifications<sup>[67]</sup>

| Parameter    | Description                         | Conditions                                                                         | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|------------------------------------------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3 \text{ V} \leq \text{V}_{DDD} \leq 5 \text{ V}$                               | -   | -   | 14 <sup>[68]</sup>  | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{\text{DDD}} < 3.3 \text{ V}$                         | -   | -   | 7 <sup>[68]</sup>   | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{\text{DDD}} < 3.3 \text{ V},$<br>SWD over USBIO pins | -   | _   | 5.5 <sup>[68]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK max                                                                  | T/4 | -   | -                   |       |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK max                                                                  | T/4 | -   | -                   |       |

| T_SWDO_valid | SWDCK high to SWDIO output          | T = 1/f_SWDCK max                                                                  | _   | _   | 2T/5                |       |

#### 11.8.6 SWV Interface

# Table 11-64. SWV Interface AC Specifications<sup>[30]</sup>

| Parameter | Description           | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------|------------|-----|-----|-----|-------|

|           | SWV mode SWV bit rate |            | _   | —   | 33  | Mbit  |

# 11.9 Clocking

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

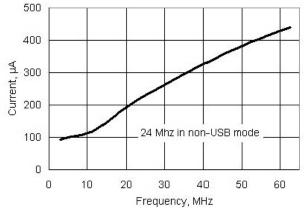

11.9.1 Internal Main Oscillator

# Table 11-65. IMO DC Specifications

| Parameter | Description           | Conditions                         | Min | Тур | Max | Units |

|-----------|-----------------------|------------------------------------|-----|-----|-----|-------|

|           | Supply current        |                                    |     |     |     |       |

|           | 24 MHz – USB mode     | With oscillator locking to USB bus | -   | -   | 500 | μA    |

|           | 24 MHz – non USB mode |                                    | -   | -   | 300 | μA    |

|           | 12 MHz                |                                    | -   | -   | 200 | μA    |

|           | 6 MHz                 |                                    | -   | -   | 180 | μA    |

|           | 3 MHz                 |                                    | _   | _   | 150 | μΑ    |

Notes

67. Based on device characterization (Not production tested). 68. f\_SWDCK must also be no more than 1/3 CPU clock frequency.

# Figure 11-59. IMO Current vs. Frequency

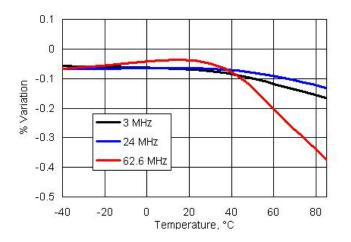

# Table 11-66. IMO AC Specifications

| Parameter        | Description                                 | Conditions                                   | Min   | Тур | Max  | Units |  |

|------------------|---------------------------------------------|----------------------------------------------|-------|-----|------|-------|--|

|                  | IMO frequency stability (with factory trim) |                                              |       |     |      |       |  |

| F <sub>IMO</sub> | 24 MHz – Non USB mode                       |                                              | -4    | _   | 4    | %     |  |

|                  | 24 MHz – USB mode                           | With oscillator locking to USB bus           | -0.25 | -   | 0.25 | %     |  |

|                  | 12 MHz                                      |                                              | -3    | -   | 3    | %     |  |

|                  | 6 MHz                                       |                                              | -2    | _   | 2    | %     |  |

|                  | 3 MHz                                       |                                              | -2    | -   | 2    | %     |  |

|                  | Startup time <sup>[69]</sup>                | From enable (during normal system operation) | -     | -   | 13   | μs    |  |

|                  | Jitter (peak to peak) <sup>[69]</sup>       |                                              |       |     |      |       |  |

| Јр-р             | F = 24 MHz                                  |                                              | _     | 0.9 | _    | ns    |  |

|                  | F = 3 MHz                                   |                                              | _     | 1.6 | _    | ns    |  |

| Jperiod          | Jitter (long term) <sup>[69]</sup>          |                                              |       |     |      |       |  |

|                  | F = 24 MHz                                  |                                              | _     | 0.9 | -    | ns    |  |

|                  | F = 3 MHz                                   |                                              | _     | 12  | -    | ns    |  |

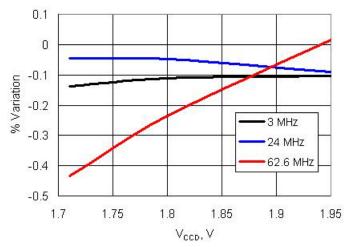

#### Figure 11-60. IMO Frequency Variation vs. Temperature

# Figure 11-61. IMO Frequency Variation vs. V<sub>CC</sub>

#### Note

69. Based on device characterization (Not production tested).

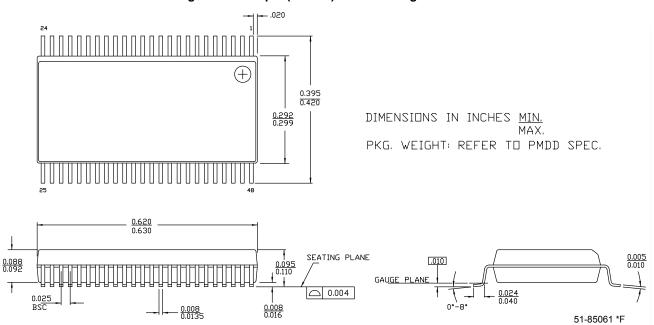

Figure 13-1. 48-pin (300 mil) SSOP Package Outline

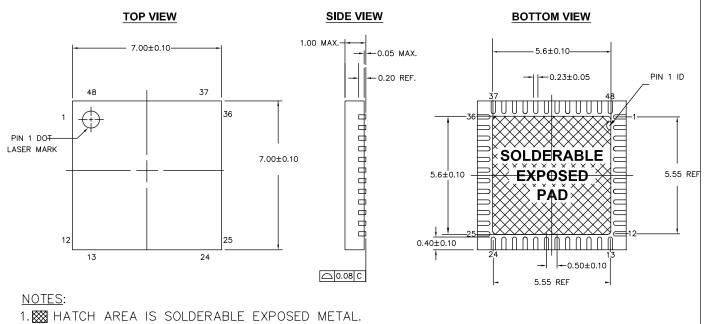

Figure 13-2. 48-pin QFN Package Outline

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT: REFER TO PMDD SPEC.

- 4. ALL DIMENSIONS ARE IN MM [MIN/MAX]

- 5. PACKAGE CODE

| PART # | DESCRIPTION |  |  |

|--------|-------------|--|--|

| LT48D  | LEAD FREE   |  |  |

001-45616 \*E

# **16. Document Conventions**

# 16.1 Units of Measure

# Table 16-1. Units of Measure

| Symbol | Unit of Measure        |  |  |  |

|--------|------------------------|--|--|--|

| °C     | degrees Celsius        |  |  |  |

| dB     | decibels               |  |  |  |

| fF     | femtofarads            |  |  |  |

| Hz     | hertz                  |  |  |  |

| KB     | 1024 bytes             |  |  |  |

| kbps   | kilobits per second    |  |  |  |

| Khr    | kilohours              |  |  |  |

| kHz    | kilohertz              |  |  |  |

| kΩ     | kilohms                |  |  |  |

| ksps   | kilosamples per second |  |  |  |

| LSB    | least significant bit  |  |  |  |

| Mbps   | megabits per second    |  |  |  |

| MHz    | megahertz              |  |  |  |

| MΩ     | megaohms               |  |  |  |

| Msps   | megasamples per second |  |  |  |

| μA     | microamperes           |  |  |  |

| Symbol | Unit of Measure      |  |  |

|--------|----------------------|--|--|

| μF     | microfarads          |  |  |

| μH     | microhenrys          |  |  |

| μs     | microseconds         |  |  |

| μV     | microvolts           |  |  |

| μW     | microwatts           |  |  |

| mA     | milliamperes         |  |  |

| ms     | milliseconds         |  |  |

| mV     | millivolts           |  |  |

| nA     | nanoamperes          |  |  |

| ns     | nanoseconds          |  |  |

| nV     | nanovolts            |  |  |

| Ω      | ohms                 |  |  |

| pF     | picofarads           |  |  |

| ppm    | parts per million    |  |  |

| ps     | picoseconds          |  |  |

| s      | seconds              |  |  |

| sps    | samples per second   |  |  |

| sqrtHz | square root of hertz |  |  |

| V      | volts                |  |  |

#### Table 16-1. Units of Measure (continued)

| Revision | nt Number:<br>ECN | Submission | Orig. of | Description of Change                                                                                                                                    |

|----------|-------------------|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                   | Date       | Change   |                                                                                                                                                          |

| *C       | 2903576           | 04/01/10   | MKEA     | Updated Vb pin in PCB Schematic.                                                                                                                         |

|          |                   |            |          | Updated Tstartup parameter in AC Specifications table.                                                                                                   |

|          |                   |            |          | Added Load regulation and Line regulation parameters to Inductive Boost                                                                                  |

|          |                   |            |          | Regulator DC Specifications table.                                                                                                                       |

|          |                   |            |          | Updated I <sub>CC</sub> parameter in LCD Direct Drive DC Specs table.<br>In page 1, updated internal oscillator range under Prescision programmable      |

|          |                   |            |          | clocking to start from 3 MHz.                                                                                                                            |

|          |                   |            |          | Updated I <sub>OUT</sub> parameter in LCD Direct Drive DC Specs table.                                                                                   |

|          |                   |            |          | Updated Table 6-2 and Table 6-3.                                                                                                                         |

|          |                   |            |          | Added bullets on CapSense in page 1; added CapSense column in Section 12                                                                                 |

|          |                   |            |          | Removed some references to footnote [1].                                                                                                                 |

|          |                   |            |          | Changed INC_Rn cycles from 3 to 2 (Table 4-1).                                                                                                           |

|          |                   |            |          | Added footnote in PLL AC Specification table.                                                                                                            |

|          |                   |            |          | Added PLL intermediate frequency row with footnote in PLL AC Specs table.                                                                                |

|          |                   |            |          | Added UDBs subsection under 11.6 Digital Peripherals.                                                                                                    |

|          |                   |            |          | Updated Figure 2-6 (PCB Layout).                                                                                                                         |

|          |                   |            |          | Updated Pin Descriptions section and modified Figures 6-6, 6-8, 6-9.                                                                                     |

|          |                   |            |          | Updated LVD in Tables 6-2 and 6-3; modified Low-power modes bullet in page 1                                                                             |

|          |                   |            |          | Added note to Figures 2-5 and 6-2; Updated Figure 6-2 to add capacitors for $V_{DDA}$                                                                    |

|          |                   |            |          | and V <sub>DDD</sub> pins.                                                                                                                               |

|          |                   |            |          | Updated boost converter section (6.2.2).                                                                                                                 |

|          |                   |            |          | Updated Tstartup values in Table 11-3.<br>Removed IPOR rows from Table 11-53. Updated 6.3.1.1, Power Voltage Level                                       |

|          |                   |            |          | Monitors.                                                                                                                                                |

|          |                   |            |          | Updated section 5.2 and Table 11-2 to correct suggestion of execution from flash                                                                         |

|          |                   |            |          | Updated IMO max frequency in Figure 6-1, Table 11-63, and Table 11-64.                                                                                   |

|          |                   |            |          | Updated $V_{\text{REF}}$ specs in Table 11-19.                                                                                                           |

|          |                   |            |          | Updated IDAC uncompensated gain error in Table 11-23.                                                                                                    |

|          |                   |            |          | Updated Delay from Interrupt signal input to ISR code execution from ISR code                                                                            |

|          |                   |            |          | in Table-71. Removed other line in table.                                                                                                                |

|          |                   |            |          | Added sentence to last paragraph of section 6.1.1.3.                                                                                                     |

|          |                   |            |          | Updated Tresp, high and low-power modes, in Table 11-22.                                                                                                 |

|          |                   |            |          | Updated f_TCK values in Table 11-58 and f_SWDCK values in Table 11-59.                                                                                   |

|          |                   |            |          | Updated SNR condition in Table 11-18.                                                                                                                    |

|          |                   |            |          | Updated sleep wakeup time in Table 6-3 and Tsleep in Table 11-3.                                                                                         |

|          |                   |            |          | Added 1.71 V $\leq$ V <sub>DDD</sub> $\leq$ 3.3 V, SWD over USBIO pins value to Table 11-59.                                                             |

|          |                   |            |          | Removed mention of hibernate reset (HRES) from page 1 features, Table 6-3,                                                                               |

|          |                   |            |          | Section 6.2.1.4, Section 6.3, and Section 6.3.1.1. Change PPOR/PRES to TBDs                                                                              |

|          |                   |            |          | in Section 6.3.1.1, Section 6.4.1.6 (changed PPOR to reset), Table 11-3 (changed PPOR to PRES), Table 11-53 (changed title, values TBD), and Table 11-54 |

|          |                   |            |          | (changed PPOR_TR to PRES_TR).                                                                                                                            |

|          |                   |            |          | Added sentence saying that LVD circuits can generate a reset to Section 6.3.1.1                                                                          |

|          |                   |            |          | Changed $I_{DD}$ values on page 1, page 5, and Table 11-2.                                                                                               |

|          |                   |            |          | Changed resume time value in Section 6.2.1.3.                                                                                                            |

|          |                   |            |          | Changed ESD HBM value in Table 11-1.                                                                                                                     |

|          |                   |            |          | Changed sample rate row in Table 11-18.                                                                                                                  |

|          |                   |            |          | Removed $V_{DDA}$ = 1.65 V rows and changed BWag value in Table 11-20.                                                                                   |

|          |                   |            |          | Changed Vioff values and changed CMRR value in Table 11-21.                                                                                              |

|          |                   |            |          | Changed INL max value in Table 11-25.                                                                                                                    |

|          |                   |            |          | Changed occurrences of "Block" to "Row" and deleted the "ECC not included"                                                                               |

|          |                   |            |          | footnote in Table 11-41.                                                                                                                                 |

|          |                   |            |          | Changed max response time value in Tables 11-54 and 11-56.                                                                                               |

|          |                   |            |          | Change the Startup time in Table 11-64.                                                                                                                  |

|          |                   |            |          | Added condition to intermediate frequency row in Table 11-70.                                                                                            |

|          |                   |            |          | Added row to Table 11-54.                                                                                                                                |

|          |                   |            |          | Added brown out note to Section 11.8.1.                                                                                                                  |

| Description Title: PSoC <sup>®</sup> 3: CY8C32 Family Data Sheet Programmable System-on-Chip (PSoC <sup>®</sup> ) (continued) Document Number: 001-56955 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision                                                                                                                                                 | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *D                                                                                                                                                       | 2938381 | 05/27/10           | MKEA               | Replaced $V_{DDIO}$ with $V_{DDD}$ in USBIO diagram and specification tables, added text<br>in USBIO section of Electrical Specifications.<br>Added Table 13-2 (Package MSL)<br>Modified Tstorag condition and changed max spec to 100<br>Added bullet (Pass) under ALU (section 7.2.2.2)<br>Added figures for kHzECO and MHzECO in the External Oscillator section<br>Updated Figure 6-1(Clocking Subsystem diagram)<br>Removed CPUCLK_DIV in table 5-2, Deleted Clock Divider SFR subsection<br>Updated PSoC Creator Framework image<br>Updated SIO DC Specifications (V <sub>IH</sub> and V <sub>IL</sub> parameters)<br>Updated bullets in Clocking System and Clocking Distribution sections<br>Updated Figure 8-2<br>Updated Table 11-10<br>Updated PCB Layout and Schematic, updated as per MTRB review comments<br>Updated Table 6-3 (power changed to current)<br>In 32kHZ EC DC Specifications table, changed I <sub>CC</sub> Max to 0.25<br>In IMO DC Specifications table, updated Supply Current values<br>Updated GPIO DC Specs table<br>Modified to support a maximum 50MHz CPU speed |

| *E                                                                                                                                                       | 2958674 | 06/22/10           | SHEA               | Minor ECN to post datasheet to external website                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| *F                                                                                                                                                       | 2989685 | 08/04/10           | MKEA               | Added USBIO 22 ohm DP and DM resistors to Simplified Block Diagram<br>Added to Table 6-6 a footnote and references to same.<br>Added sentences to the resistive pull-up and pull-down description bullets.<br>Added sentence to Section 6.4.11, Adjustable Output Level.<br>Updated section 5.5 External Memory Interface<br>Updated Table 11-73 JTAG Interface AC Specifications<br>Updated Table 11-74 SWD Interface AC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *G                                                                                                                                                       | 3078568 | 11/04/10           | MKEA               | Updated "Current Digital-to-analog Converter (IDAC)" on page 87<br>Updated "Voltage Digital to Analog Converter (VDAC)" on page 92<br>Updated Table 11-2, "DC Specifications," on page 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |