#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                               |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3245lti-144 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 3:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes and code examples covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 3 are:

- AN54181: Getting Started With PSoC 3

- AN61290: Hardware Design Considerations

- AN57821: Mixed Signal Circuit Board Layout

- AN58304: Pin Selection for Analog Designs

- AN81623: Digital Design Best Practices

- AN73854: Introduction To Bootloaders

using the PSoC Creator IDE C compiler

- Development Kits:

- CY8CKIT-030 is designed for analog performance, for developing high-precision analog, low-power, and low-voltage applications.

- CY8CKIT-001 provides a common development platform for any one of the PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP families of devices.

- The MiniProg3 device provides an interface for flash programming and debug.

- Technical Reference Manuals (TRM)

- Architecture TRM

- Registers TRM

- Programming Specification

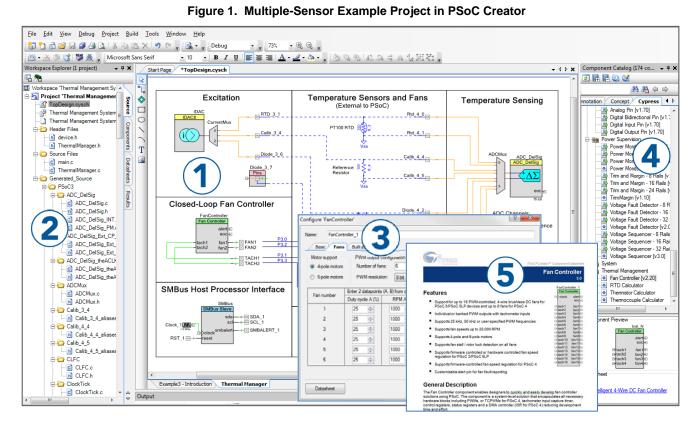

## PSoC Creator

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100 pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can:

1. Drag and drop component icons to build your hardware system design in the main design workspace

2. Codesign your application firmware with the PSoC hardware,

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- 5. Review component datasheets

# Document Number: 001-56955 Rev. \*Y

Table 2-2 shows the pinout for the 72-pin CSP package. Since there are four  $V_{DDIO}$  pins, the set of I/O pins associated with any  $V_{DDIO}$  may sink up to 100 mA total, same as for the 100-pin and 68-pin devices.

| Table 2-2. | COD | Dinout |

|------------|-----|--------|

| Table Z-Z. | LOP | Pinout |

| Ball | Name   | Ball               | Name   | Ball | Name   |

|------|--------|--------------------|--------|------|--------|

| G6   | P2[5]  | F1                 | VDDD   | A5   | VDDA   |

| E5   | P2[6]  | E1                 | VSSD   | A6   | VSSD   |

| F5   | P2[7]  | E2                 | VCCD   | B6   | P12[2] |

| J7   | P12[4] | C1                 | P15[0] | C6   | P12[3] |

| H6   | P12[5] | C2                 | P15[1] | A7   | P0[0]  |

| J6   | VSSB   | D2                 | P3[0]  | B7   | P0[1]  |

| J5   | Ind    | D3                 | P3[1]  | B5   | P0[2]  |

| H5   | VBOOST | D4                 | P3[2]  | C5   | P0[3]  |

| J4   | VBAT   | D5                 | P3[3]  | A8   | VIO0   |

| H4   | VSSD   | B4                 | P3[4]  | D6   | P0[4]  |

| J3   | XRES_N | B3                 | P3[5]  | D7   | P0[5]  |

| H3   | P1[0]  | A1                 | VIO3   | C7   | P0[6]  |

| G3   | P1[1]  | B2                 | P3[6]  | C8   | P0[7]  |

| H2   | P1[2]  | A2                 | P3[7]  | E8   | VCCD   |

| J2   | P1[3]  | C3                 | P12[0] | F8   | VSSD   |

| G4   | P1[4]  | C4                 | P12[1] | G8   | VDDD   |

| G5   | P1[5]  | E3                 | P15[2] | E7   | P15[4] |

| J1   | VIO1   | E4                 | P15[3] | F7   | P15[5] |

| F4   | P1[6]  | B1 <sup>[10]</sup> | NC     | G7   | P2[0]  |

| F3   | P1[7]  | B8 <sup>[10]</sup> | NC     | H7   | P2[1]  |

| H1   | P12[6] | D1 <sup>[10]</sup> | NC     | H8   | P2[2]  |

| G1   | P12[7] | D8 <sup>[10]</sup> | NC     | F6   | P2[3]  |

| G2   | P15[6] | A3                 | VCCA   | E6   | P2[4]  |

| F2   | P15[7] | A4                 | VSSA   | J8   | VIO2   |

Figure 2-7 and Figure 2-8 show an example schematic and an example PCB layout, for the 100-pin TQFP part, for optimal analog performance on a two layer board.

- The two pins labeled VDDD must be connected together.

- The two pins labeled VCCD must be connected together, with capacitance added, as shown in Figure 2-7 and Power System on page 31. The trace between the two VCCD pins should be as short as possible.

- The two pins labeled VSSD must be connected together.

For information on circuit board layout issues for mixed signals, refer to the application note AN57821 - Mixed Signal Circuit Board Layout Considerations for PSoC® 3 and PSoC 5.

## 4.3 Instruction Set

The 8051 instruction set is highly optimized for 8-bit handling and Boolean operations. The types of instructions supported include:

- Arithmetic instructions

- Logical instructions

- Data transfer instructions

- Boolean instructions

- Program branching instructions

#### Table 4-1. Arithmetic Instructions

#### 4.3.1 Instruction Set Summary

#### 4.3.1.1 Arithmetic Instructions

Arithmetic instructions support the direct, indirect, register, immediate constant, and register-specific instructions. Arithmetic modes are used for addition, subtraction, multiplication, division, increment, and decrement operations. Table 4-1 lists the different arithmetic instructions.

| Mnemonic       | Description                                          | Bytes | Cycles |

|----------------|------------------------------------------------------|-------|--------|

| ADD A,Rn       | Add register to accumulator                          | 1     | 1      |

| ADD A,Direct   | Add direct byte to accumulator                       | 2     | 2      |

| ADD A,@Ri      | Add indirect RAM to accumulator                      | 1     | 2      |

| ADD A,#data    | Add immediate data to accumulator                    | 2     | 2      |

| ADDC A,Rn      | Add register to accumulator with carry               | 1     | 1      |

| ADDC A, Direct | Add direct byte to accumulator with carry            | 2     | 2      |

| ADDC A,@Ri     | Add indirect RAM to accumulator with carry           | 1     | 2      |

| ADDC A,#data   | Add immediate data to accumulator with carry         | 2     | 2      |

| SUBB A,Rn      | Subtract register from accumulator with borrow       | 1     | 1      |

| SUBB A,Direct  | Subtract direct byte from accumulator with borrow    | 2     | 2      |

| SUBB A,@Ri     | Subtract indirect RAM from accumulator with borrow   | 1     | 2      |

| SUBB A,#data   | Subtract immediate data from accumulator with borrow | 2     | 2      |

| INC A          | Increment accumulator                                | 1     | 1      |

| INC Rn         | Increment register                                   | 1     | 2      |

| INC Direct     | Increment direct byte                                | 2     | 3      |

| INC @Ri        | Increment indirect RAM                               | 1     | 3      |

| DEC A          | Decrement accumulator                                | 1     | 1      |

| DEC Rn         | Decrement register                                   | 1     | 2      |

| DEC Direct     | Decrement direct byte                                | 2     | 3      |

| DEC @Ri        | Decrement indirect RAM                               | 1     | 3      |

| INC DPTR       | Increment data pointer                               | 1     | 1      |

| MUL            | Multiply accumulator and B                           | 1     | 2      |

| DIV            | Divide accumulator by B                              | 1     | 6      |

| DAA            | Decimal adjust accumulator                           | 1     | 3      |

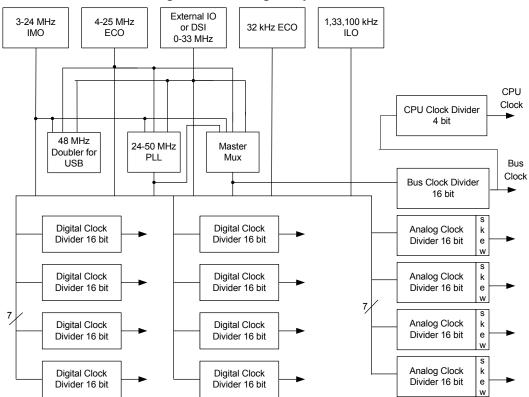

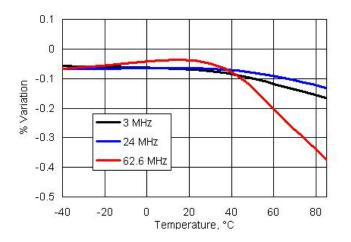

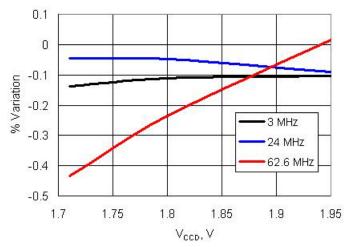

#### Table 6-1. Oscillator Summary

| Source  | Fmin   | Tolerance at Fmin                | Fmax    | Tolerance at Fmax | Startup Time                            |

|---------|--------|----------------------------------|---------|-------------------|-----------------------------------------|

| IMO     | 3 MHz  | ±2% over voltage and temperature | 24 MHz  | ±4%               | 13-µs max                               |

| MHzECO  | 4 MHz  | Crystal dependent                | 25 MHz  | Crystal dependent | 5 ms typ, max is<br>crystal dependent   |

| DSI     | 0 MHz  | Input dependent                  | 33 MHz  | Input dependent   | Input dependent                         |

| PLL     | 24 MHz | Input dependent                  | 50 MHz  | Input dependent   | 250 µs max                              |

| Doubler | 48 MHz | Input dependent                  | 48 MHz  | Input dependent   | 1 µs max                                |

| ILO     | 1 kHz  | -50%, +100%                      | 100 kHz | -55%, +100%       | 15 ms max in lowest power mode          |

| kHzECO  | 32 kHz | Crystal dependent                | 32 kHz  | Crystal dependent | 500 ms typ, max is<br>crystal dependent |

Figure 6-1. Clocking Subsystem

The term **device reset** indicates that the processor as well as analog and digital peripherals and registers are reset.

A reset status register shows some of the resets or power voltage monitoring interrupts. The program may examine this register to detect and report certain exception conditions. This register is cleared after a power-on reset. For details see the Technical Reference Manual.

#### 6.3.1 Reset Sources

- 6.3.1.1 Power Voltage Level Monitors

- IPOR Initial Power-on Reset

At initial power on, IPOR monitors the power voltages VDDD, VDDA, VCCD, and VCCA. The trip level is not precise. It is set to approximately 1 volt, which is below the lowest specified operating voltage but high enough for the internal circuits to be reset and to hold their reset state. The monitor generates a reset pulse that is at least 150 ns wide. It may be much wider if one or more of the voltages ramps up slowly.

After boot, the IPOR circuit is disabled and voltage supervision is handed off to the precise low-voltage reset (PRES) circuit.

PRES – Precise Low Voltage Reset

This circuit monitors the outputs of the analog and digital internal regulators after power up. The regulator outputs are compared to a precise reference voltage. The response to a PRES trip is identical to an IPOR reset.

In normal operating mode, the program cannot disable the digital PRES circuit. The analog regulator can be disabled, which also disables the analog portion of the PRES. The PRES circuit is disabled automatically during sleep and hibernate modes, with one exception: During sleep mode the regulators are periodically activated (buzzed) to provide supervisory services and to reduce wakeup time. At these times the PRES circuit is also buzzed to allow periodic voltage monitoring.

ALVI, DLVI, AHVI – Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

Interrupt circuits are available to detect when VDDA and VDDD go outside a voltage range. For AHVI, VDDA is compared to a fixed trip level. For ALVI and DLVI, VDDA and VDDD are compared to trip levels that are programmable, as listed in Table 6-5. ALVI and DLVI can also be configured to generate a device reset instead of an interrupt.

Table 6-5. Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

| Interrupt | Supply | Normal Voltage<br>Range | Available Trip Settings                 |

|-----------|--------|-------------------------|-----------------------------------------|

| DLVI      | VDDD   | 1.71 V – 5.5 V          | 1.70 V – 5.45 V in 250<br>mV increments |

| ALVI      | VDDA   | 1.71 V – 5.5 V          | 1.70 V – 5.45 V in 250<br>mV increments |

| AHVI      | VDDA   | 1.71 V – 5.5 V          | 5.75 V                                  |

The monitors are disabled until after IPOR. During sleep mode these circuits are periodically activated (buzzed). If an interrupt occurs during buzzing then the system first enters its wake up sequence. The interrupt is then recognized and may be serviced. The buzz frequency is adjustable, and should be set to be less than the minimum time that any voltage is expected to be out of range. For details on how to adjust the buzz frequency, see the TRM.

#### 6.3.1.2 Other Reset Sources

XRES – External Reset

PSoC 3 has either a single GPIO pin that is configured as an external reset or a dedicated XRES pin. Either the dedicated XRES pin or the GPIO pin, if configured, holds the part in reset while held active (low). The response to an XRES is the same as to an IPOR reset.

After XRES has been deasserted, at least 10  $\mu s$  must elapse before it can be reasserted.

The external reset is active low. It includes an internal pull-up resistor. XRES is active during sleep and hibernate modes.

SRES – Software Reset

A reset can be commanded under program control by setting a bit in the software reset register. This is done either directly by the program or indirectly by DMA access. The response to a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

WRES – Watchdog Timer Reset

The watchdog reset detects when the software program is no longer being executed correctly. To indicate to the watchdog timer that it is running correctly, the program must periodically reset the timer. If the timer is not reset before a user-specified amount of time, then a reset is generated.

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power-on reset event.

## 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and Special I/O (SIO) provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- Duser programmable port reset state

- Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

The USBIO pins (P15[7] and P15[6]), when enabled for I/O mode, have limited drive mode control. The drive mode is set using the PRT15.DM0[7, 6] register. A resistive pull option is also available at the USBIO pins, which can be enabled using the PRT15.DM1[7, 6] register. When enabled for USB mode, the drive mode control has no impact on the configuration of the USB pins. Unlike the GPIO and SIO configurations, the port wide configuration registers do not configure the USB drive mode bits. Table 6-7 shows the drive mode configuration for the USBIO pins.

| PRT15.DM1[7,6]<br>Pull up enable | PRT15.DM0[7,6]<br>Drive Mode enable | PRT15.DR[7,6] = 1 | PRT15.DR[7,6] = 0 | Description                   |

|----------------------------------|-------------------------------------|-------------------|-------------------|-------------------------------|

| 0                                | 0                                   | High Z            | Strong Low        | Open Drain, Strong Low        |

| 0                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

| 1                                | 0                                   | Res High (5k)     | Strong Low        | Resistive Pull Up, Strong Low |

| 1                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

## Table 6-7. USBIO Drive Modes (P15[7] and P15[6])

#### High Impedance Analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

High Impedance Digital

The input buffer is enabled for digital signal input. This is the standard high impedance (HiZ) state recommended for digital inputs.

Resistive pull-up or resistive pull-down

Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

Open Drain, Drives High and Open Drain, Drives Low

Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the  $I^2C$  bus signal lines.

Strong Drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

Resistive pull-up and pull-down

Similar to the resistive pull-up and resistive pull-down modes except the pin is always in series with a resistor. The high data state is pull-up while the low data state is pull-down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

#### 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

#### 6.4.3 Bidirectional Mode

High-speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRT×DM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

## 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRT×SLW registers.

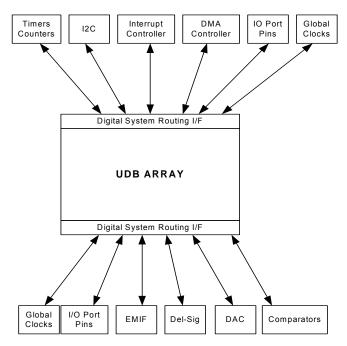

## Figure 7-9. Digital System Interconnect

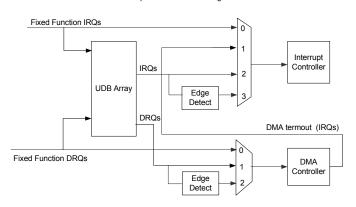

Interrupt and DMA routing is very flexible in the CY8C32 programmable architecture. In addition to the numerous fixed function peripherals that can generate interrupt requests, any data signal in the UDB array routing can also be used to generate a request. A single peripheral may generate multiple independent interrupt requests simplifying system and firmware design. Figure 7-10 shows the structure of the IDMUX (Interrupt/DMA Multiplexer).

#### Figure 7-10. Interrupt and DMA Processing in the IDMUX

Interrupt and DMA Processing in IDMUX

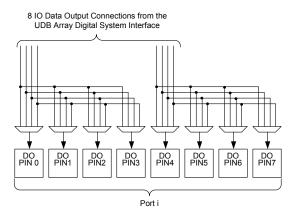

## 7.4.1 I/O Port Routing

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

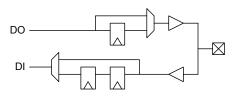

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In

conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

#### Figure 7-11. I/O Pin Synchronization Routing

#### Figure 7-12. I/O Pin Output Connectivity

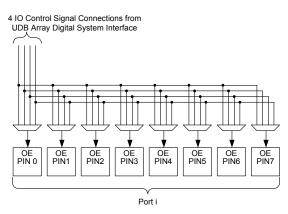

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

## Figure 7-13. I/O Pin Output Enable Connectivity

More information on output formats is provided in the Technical Reference Manual.

#### 8.2.3 Start of Conversion Input

The SoC signal is used to start an ADC conversion. A digital clock or UDB output can be used to drive this input. It can be used when the sampling period must be longer than the ADC conversion time or when the ADC must be synchronized to other hardware. This signal is optional and does not need to be connected if ADC is running in a continuous mode.

#### 8.2.4 End of Conversion Output

The EoC signal goes high at the end of each ADC conversion. This signal may be used to trigger either an interrupt or DMA request.

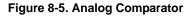

#### 8.3 Comparators

The CY8C32 family of devices contains two comparators in a device. Comparators have these features:

- Input offset factory trimmed to less than 5 mV

- Rail-to-rail common mode input range (VSSA to VDDA)

- Speed and power can be traded off by using one of three modes: fast, slow, or ultra low-power

- Comparator outputs can be routed to lookup tables to perform simple logic functions and then can also be routed to digital blocks

- The positive input of the comparators may be optionally passed through a low pass filter. Two filters are provided

- Comparator inputs can be connections to GPIO or DAC output

#### 8.3.1 Input and Output Interface

The positive and negative inputs to the comparators come from the analog global buses, the analog mux line, the analog local bus and precision reference through multiplexers. The output from each comparator could be routed to any of the two input LUTs. The output of that LUT is routed to the UDB Digital System Interface.

#### 9.3 Debug Features

Using the JTAG or SWD interface, the CY8C32 supports the following debug features:

- Halt and single-step the CPU

- View and change CPU and peripheral registers, and RAM addresses

- Eight program address breakpoints

- One memory access breakpoint—break on reading or writing any memory address and data value

- Break on a sequence of breakpoints (non recursive)

- Debugging at the full speed of the CPU

- Compatible with PSoC Creator and MiniProg3 programmer and debugger

- Standard JTAG programming and debugging interfaces make CY8C32 compatible with other popular third-party tools (for example, ARM / Keil)

#### 9.4 Trace Features

The CY8C32 supports the following trace features when using JTAG or SWD:

- Trace the 8051 program counter (PC), accumulator register (ACC), and one SFR / 8051 core RAM register

- Trace depth up to 1000 instructions if all registers are traced, or 2000 instructions if only the PC is traced (on devices that include trace memory)

- Program address trigger to start tracing

- Trace windowing, that is, only trace when the PC is within a given range

- Two modes for handling trace buffer full: continuous (overwriting the oldest trace data) or break when trace buffer is full

#### 9.5 Single Wire Viewer Interface

The SWV interface is closely associated with SWD but can also be used independently. SWV data is output on the JTAG interface's TDO pin. If using SWV, you must configure the device for SWD, not JTAG. SWV is not supported with the JTAG interface.

SWV is ideal for application debug where it is helpful for the firmware to output data similar to 'printf' debugging on PCs. The SWV is ideal for data monitoring, because it requires only a single pin and can output data in standard UART format or Manchester encoded format. For example, it can be used to tune a PID control loop in which the output and graphing of the three error terms greatly simplifies coefficient tuning.

The following features are supported in SWV:

- 32 virtual channels, each 32 bits long

- Simple, efficient packing and serializing protocol

- Supports standard UART format (N81)

## 9.6 Programming Features

The JTAG and SWD interfaces provide full programming support. The entire device can be erased, programmed, and verified. You can increase flash protection levels to protect firmware IP. Flash protection can only be reset after a full device erase. Individual flash blocks can be erased, programmed, and verified, if block security settings permit.

#### 9.7 Device Security

PSoC 3 offers an advanced security feature called device security, which permanently disables all test, programming, and debug ports, protecting your application from external access. The device security is activated by programming a 32-bit key (0×50536F43) to a Write Once Latch (WOL).

The Write Once Latch is a type of nonvolatile latch (NVL). The cell itself is an NVL with additional logic wrapped around it. Each WOL device contains four bytes (32 bits) of data. The wrapper outputs a '1' if a super-majority (28 of 32) of its bits match a pre-determined pattern (0×50536F43); it outputs a '0' if this majority is not reached. When the output is 1, the Write Once NV latch locks the part out of Debug and Test modes; it also permanently gates off the ability to erase or alter the contents of the latch. Matching all bits is intentionally not required, so that single (or few) bit failures do not deassert the WOL output. The state of the NVL bits after wafer processing is truly random with no tendency toward 1 or 0.

The WOL only locks the part after the correct 32-bit key (0×50536F43) is loaded into the NVL's volatile memory, programmed into the NVL's nonvolatile cells, and the part is reset. The output of the WOL is only sampled on reset and used to disable the access. This precaution prevents anyone from reading, erasing, or altering the contents of the internal memory.

The user can write the key into the WOL to lock out external access only if no flash protection is set (see "Flash Security" on page 24). However, after setting the values in the WOL, a user still has access to the part until it is reset. Therefore, a user can write the key into the WOL, program the flash protection data, and then reset the part to lock it.

If the device is protected with a WOL setting, Cypress cannot perform failure analysis and, therefore, cannot accept RMAs from customers. The WOL can be read out via SWD port to electrically identify protected parts. The user can write the key in WOL to lock out external access only if no flash protection is set. For more information on how to take full advantage of the security features in PSoC see the PSoC 3 TRM.

#### Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress datasheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# 11. Electrical Specifications

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. The unique flexibility of the PSoC UDBs and analog blocks enable many functions to be implemented in PSoC Creator components, see the component datasheets for full AC/DC specifications of individual functions. See the "Example Peripherals" section on page 45 for further explanation of PSoC Creator components.

## 11.1 Absolute Maximum Ratings

| Parameter                         | Description                                             | Conditions                                                                              | Min                   | Тур | Max                       | Units |

|-----------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------|-----|---------------------------|-------|

| V <sub>DDA</sub>                  | Analog supply voltage relative to V <sub>SSA</sub>      |                                                                                         | -0.5                  | _   | 6                         | V     |

| V <sub>DDD</sub>                  | Digital supply voltage relative to V <sub>SSD</sub>     |                                                                                         | -0.5                  | -   | 6                         | V     |

| V <sub>DDIO</sub>                 | I/O supply voltage relative to $V_{SSD}$                |                                                                                         | -0.5                  | -   | 6                         | V     |

| V <sub>CCA</sub>                  | Direct analog core voltage input                        |                                                                                         | -0.5                  | -   | 1.95                      | V     |

| V <sub>CCD</sub>                  | Direct digital core voltage input                       |                                                                                         | -0.5                  | I   | 1.95                      | V     |

| V <sub>SSA</sub>                  | Analog ground voltage                                   |                                                                                         | V <sub>SSD</sub> –0.5 | -   | V <sub>SSD</sub> +<br>0.5 | V     |

| V <sub>GPIO</sub> <sup>[16]</sup> | DC input voltage on GPIO                                | Includes signals sourced by $V_{\mbox{\scriptsize DDA}}$ and routed internal to the pin | V <sub>SSD</sub> –0.5 | -   | V <sub>DDIO</sub> + 0.5   | V     |

| V <sub>SIO</sub>                  | DC input voltage on SIO                                 | Output disabled                                                                         | V <sub>SSD</sub> –0.5 | -   | 7                         | V     |

|                                   |                                                         | Output enabled                                                                          | V <sub>SSD</sub> –0.5 | -   | 6                         | V     |

| V <sub>IND</sub>                  | Voltage at boost converter input                        |                                                                                         | 0.5                   | -   | 5.5                       | V     |

| V <sub>BAT</sub>                  | Boost converter supply                                  |                                                                                         | V <sub>SSD</sub> –0.5 | -   | 5.5                       | V     |

| I <sub>VDDIO</sub>                | Current per V <sub>DDIO</sub> supply pin                |                                                                                         | -                     | -   | 100                       | mA    |

| I <sub>GPIO</sub>                 | GPIO current                                            |                                                                                         | -30                   | -   | 41                        | mA    |

| I <sub>SIO</sub>                  | SIO current                                             |                                                                                         | -49                   | -   | 28                        | mA    |

| I <sub>USBIO</sub>                | USBIO current                                           |                                                                                         | -56                   | -   | 59                        | mA    |

| VEXTREF                           | ADC external reference inputs                           | Pins P0[3], P3[2]                                                                       | -                     | -   | 2                         | V     |

| LU                                | Latch up current <sup>[17]</sup>                        |                                                                                         | -140                  | I   | 140                       | mA    |

|                                   | Electrostatic discharge voltage,                        | V <sub>SSA</sub> tied to V <sub>SSD</sub>                                               | 2200                  | -   | -                         | V     |

| ESD <sub>HBM</sub>                | Human body model                                        | V <sub>SSA</sub> not tied to V <sub>SSD</sub>                                           | 750                   | I   | -                         | V     |

| ESD <sub>CDM</sub>                | Electrostatic discharge voltage,<br>Charge device model |                                                                                         | 500                   | -   | _                         | V     |

Notes

15. Usage above the absolute maximum conditions listed in Table 11-1 may cause permanent damage to the device. Exposure to Absolute Maximum conditions for extended periods of time may affect device reliability. The Maximum Storage Temperature is 150 °C in compliance with JEDEC Standard JESD22-A103, High Temperature Storage Life. When used below Absolute Maximum conditions but above normal operating conditions, the device may not operate to specification.

16. The V<sub>DDIO</sub> supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin ≤ V<sub>DDIO</sub> ≤ V<sub>DDA</sub>. 17. Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch-up Test.

## **11.2 Device Level Specifications**

Specifications are valid for –40  $^{\circ}C \le T_A \le 85 ~^{\circ}C$  and  $T_J \le 100 ~^{\circ}C$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.2.1 Device Level Specifications

## Table 11-2. DC Specifications

| Parameter                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Conditions                                             |                                | Min       | Typ <sup>[22]</sup> | Max                                                   | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------|-----------|---------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>DDA</sub>                    | Analog supply voltage and input to analog core regulator                                                                                                                                                                                                                                                                                                                                                                                                                         | Analog core regulato                                   | r enabled                      | 1.8       | _                   | 5.5                                                   | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| V <sub>DDA</sub>                    | Analog supply voltage, analog regulator bypassed                                                                                                                                                                                                                                                                                                                                                                                                                                 | Analog core regulato                                   | r disabled                     | 1.71      | 1.8                 | 1.89                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| V <sub>DDD</sub>                    | Digital supply voltage relative to V <sub>SSD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                              | Digital core regulator                                 | enabled                        | 1.8       | -                   | V <sub>DDA</sub> <sup>[18]</sup>                      | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| • DDD                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Digital core regulator                                 | Chabled                        | 1         | -                   | V <sub>DDA</sub> + 0.1 <sup>[24]</sup>                | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| V <sub>DDD</sub>                    | Digital supply voltage, digital regulator<br>bypassed                                                                                                                                                                                                                                                                                                                                                                                                                            | Digital core regulator                                 | disabled                       | 1.71      | 1.8                 | 1.89                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| V <sub>DDIO</sub> <sup>[19]</sup>   | I/O supply voltage relative to V <sub>SSIO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                        |                                | 1.71      | -                   | V <sub>DDA</sub> <sup>[18]</sup>                      | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        |                                | -         | -                   | V <sub>DDA</sub> + 0.1 <sup>[24]</sup>                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| V <sub>CCA</sub>                    | Direct analog core voltage input (Analog regulator bypass)                                                                                                                                                                                                                                                                                                                                                                                                                       | Analog core regulato                                   | r disabled                     | 1.71      | 1.8                 | 1.89                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| V <sub>CCD</sub>                    | Direct digital core voltage input (Digital regulator bypass)                                                                                                                                                                                                                                                                                                                                                                                                                     | Digital core regulator                                 | disabled                       | 1.71      | 1.8                 | 1.89                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                     | Active Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        |                                |           |                     |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     | Only IMO and CPU clock enabled. CPU executing simple loop from instruction buffer.                                                                                                                                                                                                                                                                                                                                                                                               | T = -271(55)(-7)                                       | T = -40 °C                     | -         | 1.2                 | 2.9                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $F_{CPU} = 6 \text{ MHz}^{[23]}$                       | T = 25 °C                      |           | 1.2                 |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | T = 85 °C                                              | -                              | 4.9       |                     |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $V_{PPV} = 27V - 55V$                                  | T = -40 °C                     | -         | 1.3                 |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $F_{CPU} = 3 \text{ MHz}^{[23]}$                       | T = 25 °C                      | -         | 1.6                 | -                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        | T = 85 °C                      | -         | 4.8                 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        | T = -40 °C                     | -         | 2.1                 |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $V_{DDX} = 2.7 V - 5.5 V;$<br>E <sub>ODV</sub> = 6 MHz | $V_{DDX} = 2.7 V - 5.5 V,$ T = | T = 25 °C | -                   | 2.3                                                   | 5.5         3       1.89 $V_{DDA}^{[18]}$ $V_{DDA} + 0.1^{[24]}$ 3       1.89 $V_{DDA} + 0.1^{[24]}$ 3       1.89 $V_{DDA} + 0.1^{[24]}$ 3       1.89         2       2.9         2       3.1         9       7.7         3       2.9         5       3.2         3       7.5         1       3.7         3       3.9         5       5.5         5       5.2         3       5.5         1       9.8         3       8.1         5       3.3.5         1       13.5         2       14 |  |

| I <sub>DD</sub> <sup>[20, 21]</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        | T = 85 °C                      | _         | 5.6                 | 8.5                                                   | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                     | IMO enabled, bus clock and CPU clock                                                                                                                                                                                                                                                                                                                                                                                                                                             | $V_{DDX} = 2.7 V - 5.5 V;$                             | T = -40 °C                     | -         | 3.5                 | 5.2                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     | enabled. CPU executing program from                                                                                                                                                                                                                                                                                                                                                                                                                                              | F <sub>CPU</sub> = 12 MHz <sup>[23]</sup>              | T = 25 °C                      | -         | 3.8                 | 5.5                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     | flash.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        | T = 85 °C                      | -         | 7.1                 | 9.8                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $V_{DDX} = 2.7 V - 5.5 V;$                             | T = -40 °C                     | -         | 6.3                 | 8.1                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $F_{CPU} = 24 \text{ MHz}^{[23]}$                      | T = 25 °C                      | _         | 6.6                 | 8.3                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        | T = 85 °C                      | -         | 10                  | 13                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $V_{DDX} = 2.7 V - 5.5 V;$                             | T = -40 °C                     | _         | 11.5                | 13.5                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | F <sub>CPU</sub> = 48 MHz <sup>[23]</sup>              | T = 25 °C                      | -         | 12                  | 14                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     | Only IMO and CPU clock enabled. CPU<br>executing simple loop from instruction<br>buffer. $V_{DDX} = 2.7 V - 5.5 V_F_{CPU} = 6 \text{ MHz}^{[23]}$ 1] $V_{DDX} = 2.7 V - 5.5 V_F_{CPU} = 3 \text{ MHz}^{[23]}$ $V_{DDX} = 2.7 V - 5.5 V_F_{CPU} = 3 \text{ MHz}^{[23]}$ 1]IMO enabled, bus clock and CPU clock<br>enabled. CPU executing program from<br>flash. $V_{DDX} = 2.7 V - 5.5 V_F_{CPU} = 6 \text{ MHz}^{-1}$ 1] $V_{DDX} = 2.7 V - 5.5 V_F_{CPU} = 12 \text{ MHz}^{-1}$ | T = 85 °C                                              | _                              | 15.5      | 18.5                |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

#### Notes

18. The power supplies can be brought up in any sequence however once stable  $V_{DDA}$  must be greater than or equal to all other supplies. 19. The  $V_{DDIO}$  supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin  $\leq V_{DDIO} \leq V_{DDA}$ . 20. Total current for all power domains: digital ( $I_{DDD}$ ), analog ( $I_{DDA}$ ), and I/Os ( $I_{DDIO0, 1, 2, 3}$ ). Boost not included. All I/Os floating.

21. The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find the CPU current at the frequency of interest and add peripheral currents for your particular system from the device datasheet and component datasheets.

22.  $V_{DDX}$  = 3.3 V. 23. Based on device characterizations (Not production tested).

24. Guaranteed by design, not production tested.

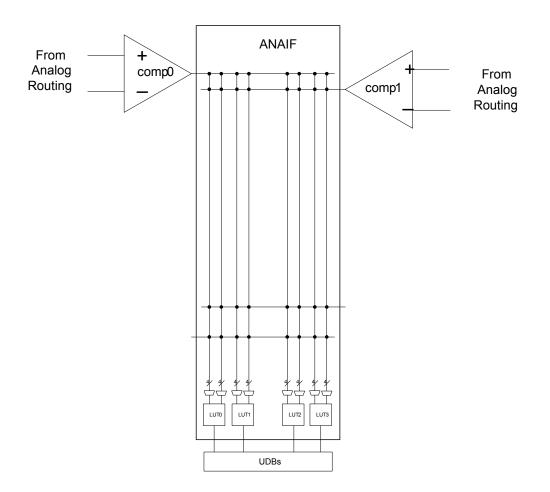

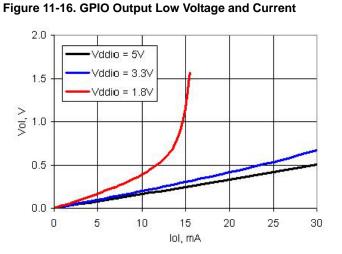

## Figure 11-15. GPIO Output High Voltage and Current

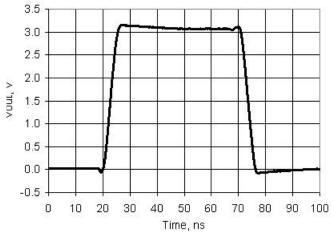

# Table 11-10. GPIO AC Specifications

| Parameter | Description                                                                             | Conditions                            | Min | Тур | Мах | Units |

|-----------|-----------------------------------------------------------------------------------------|---------------------------------------|-----|-----|-----|-------|

| TriseF    |                                                                                         | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | _   | -   | 6   | ns    |

| TfallF    | Fall time in Fast Strong Mode <sup>[38]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | _   | -   | 6   | ns    |

| TriseS    | Rise time in Slow Strong Mode <sup>[38]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

| TfallS    | Fall time in Slow Strong Mode <sup>[38]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

|           | GPIO output operating frequency                                                         |                                       |     |     |     |       |

|           | 2.7 V $\leq$ V <sub>DDIO</sub> $\leq$ 5.5 V, fast strong drive mode                     | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 33  | MHz   |

| Fgpioout  | $1.71 \text{ V} \leq \text{V}_{\text{DDIO}} < 2.7 \text{ V}$ , fast strong drive mode   | 90/10% V <sub>DDIO</sub> into 25 pF   | _   | -   | 20  | MHz   |

|           | $3.3 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , slow strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | _   | -   | 7   | MHz   |

|           | 1.71 V $\leq$ V <sub>DDIO</sub> < 3.3 V, slow strong drive mode                         | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 3.5 | MHz   |

| Fgpioin   | GPIO input operating frequency                                                          |                                       |     |     |     |       |

|           | 1.71 V <u>≤</u> V <sub>DDIO</sub> <u>≤</u> 5.5 V                                        | 90/10% V <sub>DDIO</sub>              | -   | -   | 33  | MHz   |

<sup>38.</sup> Based on device characterization (Not production tested).

V<sub>DDD</sub> = 3.3 V, 25 pF Load