Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-4-W-                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Details                    |                                                                             |

| Product Status             | Active                                                                      |

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 50MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 38                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 68-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 68-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3245lti-163t |

## More Information

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 3:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP

In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes and code examples covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 3 are:

□ AN54181: Getting Started With PSoC 3

□ AN61290: Hardware Design Considerations

□ AN57821: Mixed Signal Circuit Board Layout

□ AN58304: Pin Selection for Analog Designs

□ AN81623: Digital Design Best Practices

□ AN73854: Introduction To Bootloaders

## ■ Development Kits:

- CY8CKIT-030 is designed for analog performance, for developing high-precision analog, low-power, and low-voltage applications.

- CY8CKIT-001 provides a common development platform for any one of the PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP families of devices.

- □ The MiniProg3 device provides an interface for flash programming and debug.

- Technical Reference Manuals (TRM)

- Architecture TRM

- Registers TRM

- Programming Specification

## **PSoC Creator**

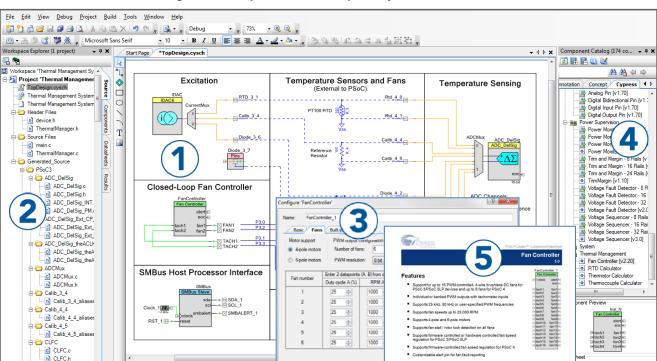

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100 pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can:

- Drag and drop component icons to build your hardware system design in the main design workspace

- Codesign your application firmware with the PSoC hardware, using the PSoC Creator IDE C compiler

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- 5. Review component datasheets

Datasheet

Figure 1. Multiple-Sensor Example Project in PSoC Creator

Output

ckTicl

ClockTick.c

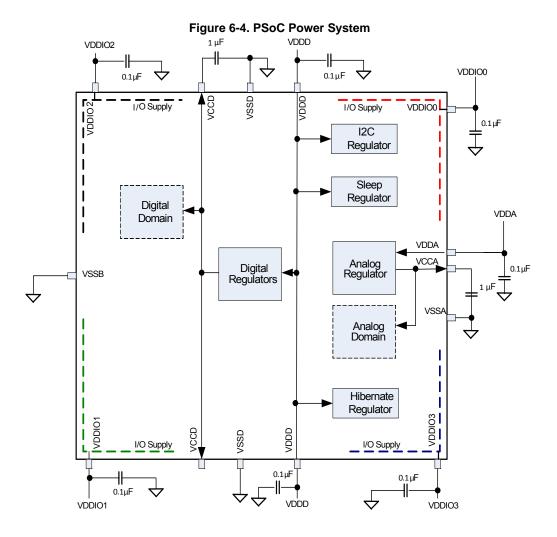

Figure 2-7. Example Schematic for 100-pin TQFP Part with Power Connections

**Note** The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-8 on page 12.

For more information on pad layout, refer to http://www.cypress.com/cad-resources/psoc-3-cad-libraries.

# 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2Table 4-2 on page 15 shows the list of logical instructions and their description.

Table 4-2. Logical Instructions

| Mnemonic |               | Description                           | Bytes | Cycles |

|----------|---------------|---------------------------------------|-------|--------|

| ANL      | A,Rn          | AND register to accumulator           | 1     | 1      |

| ANL      | A,Direct      | AND direct byte to accumulator        | 2     | 2      |

| ANL      | A,@Ri         | AND indirect RAM to accumulator       | 1     | 2      |

| ANL      | A,#data       | AND immediate data to accumulator     | 2     | 2      |

| ANL      | Direct, A     | AND accumulator to direct byte        | 2     | 3      |

| ANL      | Direct, #data | AND immediate data to direct byte     | 3     | 3      |

| ORL      | A,Rn          | OR register to accumulator            | 1     | 1      |

| ORL      | A,Direct      | OR direct byte to accumulator         | 2     | 2      |

| ORL      | A,@Ri         | OR indirect RAM to accumulator        | 1     | 2      |

| ORL      | A,#data       | OR immediate data to accumulator      | 2     | 2      |

| ORL      | Direct, A     | OR accumulator to direct byte         | 2     | 3      |

| ORL      | Direct, #data | OR immediate data to direct byte      | 3     | 3      |

| XRL      | A,Rn          | XOR register to accumulator           | 1     | 1      |

| XRL      | A,Direct      | XOR direct byte to accumulator        | 2     | 2      |

| XRL      | A,@Ri         | XOR indirect RAM to accumulator       | 1     | 2      |

| XRL      | A,#data       | XOR immediate data to accumulator     | 2     | 2      |

| XRL      | Direct, A     | XOR accumulator to direct byte        | 2     | 3      |

| XRL      | Direct, #data | XOR immediate data to direct byte     | 3     | 3      |

| CLR      | Α             | Clear accumulator                     | 1     | 1      |

| CPL      | Α             | Complement accumulator                | 1     | 1      |

| RL       | A             | Rotate accumulator left               | 1     | 1      |

| RLC      | Α             | Rotate accumulator left through carry | 1     | 1      |

| RR       | Α             | Rotate accumulator right              | 1     | 1      |

| RRC      | Α             | Rotate accumulator right though carry | 1     | 1      |

| SWAF     | PA            | Swap nibbles within accumulator       | 1     | 1      |

# PSoC® 3: CY8C32 Family Data Sheet

# 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2.

Table 5-2. Device Configuration NVL Register Map

| Register Address | 7       | 6         | 5                         | 4       | 3           | 2       | 1         | 0        |

|------------------|---------|-----------|---------------------------|---------|-------------|---------|-----------|----------|

| 0x00             | PRT3RI  | DM[1:0]   | PRT2R                     | DM[1:0] | PRT1R       | DM[1:0] | PRT0      | RDM[1:0] |

| 0x01             | PRT12R  | DM[1:0]   | PRT6RDM[1:0] PRT5RDM[1:0] |         | :0] PRT6RDM |         | PRT4      | RDM[1:0] |

| 0x02             | XRESMEN | DBGEN     |                           |         |             | PRT1    | 5RDM[1:0] |          |

| 0x03             |         | DIG_PHS_I | DLY[3:0]                  |         | ECCEN       | DPS     | [1:0]     |          |

The details for individual fields and their factory default settings are shown in Table 5-3:.

Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                                  | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     | Controls reset drive mode of the corresponding IO port. See "Reset Configuration" on page 44. All pins of the port are set to the same mode. | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as an external reset. See "Pin Descriptions" on page 12, XRES description.                   | 0 (default for 68-pin 72-pin, and 100-pin parts) - GPIO 1 (default for 48-pin parts) - external reset                         |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                                 | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| DPS[1:0]         | Controls the usage of various P1 pins as a debug port. See "Programming, Debug Interfaces, Resources" on page 62.                            | 00b - 5-wire JTAG<br>01b (default) - 4-wire JTAG<br>10b - SWD<br>11b - debug ports disabled                                   |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 24.             | 0 - ECC disabled<br>1 (default) - ECC enabled                                                                                 |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                                       | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase / write cycles is limited – see "Nonvolatile Latches (NVL))" on page 100.

Document Number: 001-56955 Rev. \*Y Page 25 of 128

## **Notes**

- The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-8 on page 12.

- It is good practice to check the datasheets for your bypass capacitors, specifically the working voltage and the DC bias specifications. With some capacitors, the actual capacitance can decrease considerably when the DC bias (VDDX or VCCX in Figure 6-4) is a significant percentage of the rated working voltage.

- You can power the device in internally regulated mode, where the voltage applied to the VDDx pins is as high as 5.5 V, and the internal regulators provide the core voltages. In this mode, do not apply power to the VCCx pins, and do not tie the VDDx pins to the VCCx pins.

- You can also power the device in externally regulated mode, that is, by directly powering the VCCD and VCCA pins. In this configuration, the VDDD pins should be shorted to the VCCD pins and the VDDA pin should be shorted to the VCCA pin. The allowed supply range in this configuration is 1.71 V to 1.89 V. After power up in this configuration, the internal regulators are on by default, and should be disabled to reduce power consumption.

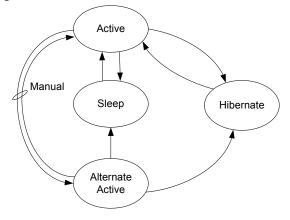

Figure 6-5. Power Mode Transitions

#### 6.2.1.1 Active Mode

Active mode is the primary operating mode of the device. When in active mode, the active configuration template bits control which available resources are enabled or disabled. When a resource is disabled, the digital clocks are gated, analog bias currents are disabled, and leakage currents are reduced as appropriate. User firmware can dynamically control subsystem power by setting and clearing bits in the active configuration template. The CPU can disable itself, in which case the CPU is automatically reenabled at the next wakeup event.

When a wakeup event occurs, the global mode is always returned to active, and the CPU is automatically enabled, regardless of its template settings. Active mode is the default global power mode upon boot.

#### 6.2.1.2 Alternate Active Mode

Alternate Active mode is very similar to Active mode. In alternate active mode, fewer subsystems are enabled, to reduce power consumption. One possible configuration is to turn off the CPU and flash, and run peripherals at full speed.

## 6.2.1.3 Sleep Mode

Sleep mode reduces power consumption when a resume time of 15  $\mu s$  is acceptable. The wake time is used to ensure that the regulator outputs are stable enough to directly enter active mode.

#### 6.2.1.4 Hibernate Mode

In hibernate mode nearly all of the internal functions are disabled. Internal voltages are reduced to the minimal level to keep vital systems alive. Configuration state is preserved in hibernate mode and SRAM memory is retained. GPIOs configured as digital outputs maintain their previous values and external GPIO pin interrupt settings are preserved. The device can only return from hibernate mode in response to an external I/O interrupt. The resume time from hibernate mode is less than 100 µs.

To achieve an extremely low current, the hibernate regulator has limited capacity. This limits the frequency of any signal present on the input pins - no GPIO should toggle at a rate greater than 10 kHz while in hibernate mode. If pins must be toggled at a high rate while in a low power mode, use sleep mode instead.

## 6.2.1.5 Wakeup Events

Wakeup events are configurable and can come from an interrupt or device reset. A wakeup event restores the system to active mode. Firmware enabled interrupt sources include internally generated interrupts, power supervisor, central timewheel, and I/O interrupts. Internal interrupt sources can come from a variety of peripherals, such as analog comparators and UDBs. The central timewheel provides periodic interrupts to allow the system to wake up, poll peripherals, or perform real-time functions. Reset event sources include the external reset I/O pin (XRES), WDT, and Precision Reset (PRES).

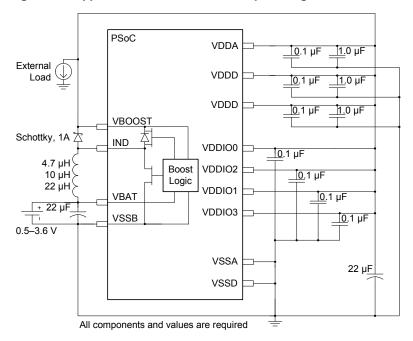

#### 6.2.2 Boost Converter

Applications that use a supply voltage of less than 1.71 V, such as solar panels or single cell battery supplies, may use the on-chip boost converter to generate a minimum of 1.8 V supply voltage. The boost converter may also be used in any system that requires a higher operating voltage than the supply provides such as driving 5.0 V LCD glass in a 3.3 V system. With the addition of an inductor, Schottky diode, and capacitors, it produces a selectable output voltage sourcing enough current to operate the PSoC and other on-board components.

The boost converter accepts an input voltage V<sub>BAT</sub> from 0.5 V to 3.6 V, and can start up with V<sub>BAT</sub> as low as 0.5 V. The converter provides a user configurable output voltage of 1.8 to 5.0 V (V<sub>OUT</sub>) in 100 mV increments. V<sub>BAT</sub> is typically less than V<sub>OUT</sub>; if V<sub>BAT</sub> is greater than or equal to V<sub>OUT</sub>, then V<sub>OUT</sub> will be slightly less than V<sub>BAT</sub> due to resistive losses in the boost converter. The block can deliver up to 50 mA (I<sub>BOOST</sub>) depending on configuration to both the PSoC device and external components. The sum of all current sinks in the design including the PSoC device, PSoC I/O pin loads, and external component loads must be less than the I<sub>BOOST</sub> specified maximum current.

Four pins are associated with the boost converter: VBAT, VSSB, VBOOST, and IND. The boosted output voltage is sensed at the VBOOST pin and must be connected directly to the chip's supply inputs, VDDA, VDDD, and VDDIO, if used to power the PSoC device.

The boost converter requires four components in addition to those required in a non-boost design, as shown in Figure 6-6 on page 35. A 22-µF capacitor (CBAT) is required close to the VBAT pin to provide local bulk storage of the battery voltage and provide regulator stability. A diode between the battery and VBAT pin should not be used for reverse polarity protection because the diodes forward voltage drop reduces the  $V_{\mbox{\footnotesize{BAT}}}$  voltage. Between the VBAT and IND pins, an inductor of 4.7 μH, 10 μH, or 22 µH is required. The inductor value can be optimized to increase the boost converter efficiency based on input voltage, output voltage, temperature, and current. Inductor size is determined by following the design guidance in this section and the electrical specifications. The inductor must be placed within 1 cm of the VBAT and IND pins and have a minimum saturation current of 750 mA. Between the IND and VBOOST pins, place a Schottky diode within 1 cm of the pins. This diode shall have a forward current rating of at least 1.0 A and a reverse voltage of at least 20 V. Connect a 22-µF bulk capacitor (CBOOST) close to VBOOST to provide regulator output stability. It is important to sum the total capacitance connected to the VBOOST pin and ensure the maximum CBOOST specification is not exceeded. All capacitors must be rated for a minimum of 10 V to minimize capacitive losses due to voltage de-rating.

Figure 6-6. Application of Boost Converter powering PSoC device

The boost converter may also generate a supply that is not used directly by the PSoC device. An example of this use case is boosting a 1.8 V supply to 4.0 V to drive a white LED. If the boost converter is not supplying the PSoC devices  $V_{DDA}$ ,  $V_{DDD}$ , and  $V_{DDIO}$  it must comply with the same design rules as supplying

the PSoC device, but with a change to the bulk capacitor requirements. A parallel arrangement 22  $\mu F$ , 1.0  $\mu F$ , and 0.1  $\mu F$  capacitors are all required on the Vout supply and must be placed within 1 cm of the VBOOST pin to ensure regulator stability.

External **PSoC** VDDA 🗀 Load VDDD 🗀 22 μF 1.0 μF 0.1 μI VDDD 🗀 VDDA, VDDD, and **VBOOST VDDIO** connections Schottky, 1A 💢 per section 6.2 IND VDDIO0 Power System. VDDIO2 ⊟ Boost 10 µH > Logic 22 µH VDDIO1 **VBAT** VDDIO3 VSSB 0.5-3.6 V **VSSA VSSD** All components and values are required

Figure 6-7. Application of Boost Converter not powering PSoC device

The switching frequency is set to 400 kHz using an oscillator integrated into the boost converter. The boost converter can be operated in two different modes: active and standby. Active mode is the normal mode of operation where the boost regulator

actively generates a regulated output voltage. In standby mode, most boost functions are disabled, thus reducing power consumption of the boost circuit. Only minimal power is provided, typically < 5  $\mu$ A to power the PSoC device in Sleep mode. The

boost typically draws 250  $\mu A$  in active mode and 25  $\mu A$  in standby mode. The boost operating modes must be used in conjunction with chip power modes to minimize total power consumption. Table 6-4 lists the boost power modes available in different chip power modes.

Table 6-4. Chip and Boost Power Modes Compatibility

| Chip Power Modes                     | Boost Power Modes                                                                                                                                                            |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip-active or alternate active mode | Boost must be operated in its active mode.                                                                                                                                   |

| Chip-sleep mode                      | Boost can be operated in either active or standby mode. In boost standby mode, the chip must wake up periodically for boost active-mode refresh.                             |

| Chip-hibernate mode                  | Boost can be operated in its active mode. However, it is recommended not to use the boost in chip hibernate mode due to the higher current consumption in boost active mode. |

## 6.2.2.1 Boost Firmware Requirements

To ensure boost inrush current is within specification at startup, the **Enable Fast IMO During Startup** value must be unchecked in the PSoC Creator IDE. The **Enable Fast IMO During Startup** option is found in PSoC Creator in the design wide resources (cydwr) file **System** tab. Un-checking this option configures the device to run at 12 MHz vs 48 MHz during startup while configuring the device. The slower clock speed results in reduced current draw through the boost circuit.

### 6.2.2.2 Boost Design Process

Correct operation of the boost converter requires specific component values determined for each designs unique operating conditions. The  $C_{BAT}$  capacitor, Inductor, Schottky diode, and  $C_{BOOST}$  capacitor components are required with the values specified in the electrical specifications, Table 11-7 on page 74. The only variable component value is the inductor  $L_{BOOST}$  which is primarily sized for correct operation of the boost across operating conditions and secondarily for efficiency. Additional operating region constraints exist for  $V_{OUT},\,V_{BAT},\,I_{OUT},\,$  and  $T_A.$

The following steps must be followed to determine boost converter operating parameters and  $L_{\text{BOOST}}$  value.

- Choose desired V<sub>BAT</sub>, V<sub>OUT</sub>, T<sub>A</sub>, and I<sub>OUT</sub> operating condition ranges for the application.

- Determine if V<sub>BAT</sub> and V<sub>OUT</sub> ranges fit the boost operating range based on the T<sub>A</sub> range over V<sub>BAT</sub> and V<sub>OUT</sub> chart, Figure 11-8 on page 74. If the operating ranges are not met, modify the operating conditions or use an external boost regulator.

- 3. Determine if the desired ambient temperature (T<sub>A</sub>) range fits the ambient temperature operating range based on the T<sub>A</sub> range over V<sub>BAT</sub> and V<sub>OUT</sub> chart, Figure 11-8 on page 74. If the temperature range is not met, modify the operating conditions and return to step 2, or use an external boost regulator.

- Determine if the desired output current (I<sub>OUT</sub>) range fits the output current operating range based on the I<sub>OUT</sub> range over V<sub>BAT</sub> and V<sub>OUT</sub> chart, Figure 11-9 on page 74. If the output

- current range is not met, modify the operating conditions and return to step 2, or use an external boost regulator.

- Find the allowed inductor values based on the L<sub>BOOST</sub> values over V<sub>BAT</sub> and V<sub>OUT</sub> chart, Figure 11-10 on page 74.

- 6. Based on the allowed inductor values, inductor dimensions, inductor cost, boost efficiency, and V<sub>RIPPLE</sub> choose the optimum inductor value for the system. Boost efficiency and V<sub>RIPPLE</sub> typical values are provided in the Efficiency vs V<sub>BAT</sub> and V<sub>RIPPLE</sub> vs V<sub>BAT</sub> charts, Figure 11-11 on page 75 through Figure 11-14 on page 75. In general, if high efficiency and low V<sub>RIPPLE</sub> are most important, then the highest allowed inductor value should be used. If low inductor cost or small inductor size are most important, then one of the smaller allowed inductor values should be used. If the allowed inductor(s) efficiency, V<sub>RIPPLE</sub>, cost or dimensions are not acceptable for the application than an external boost regulator should be used.

#### 6.3 Reset

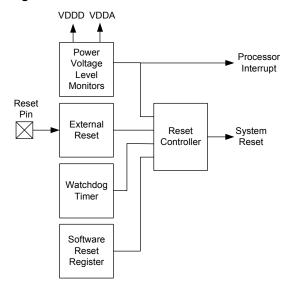

CY8C32 has multiple internal and external reset sources available. The reset sources are:

- Power source monitoring The analog and digital power voltages, VDDA, VDDD, VCCA, and VCCD are monitored in several different modes during power up, active mode, and sleep mode (buzzing). If any of the voltages goes outside predetermined ranges then a reset is generated. The monitors are programmable to generate an interrupt to the processor under certain conditions before reaching the reset thresholds.

- External The device <u>can</u> be reset fro<u>m</u> an external source by pulling the reset pin (XRES) low. The XRES pin includes an internal pull-up to VDDIO1. VDDD, VDDA, and VDDIO1 must all have voltage applied before the part comes out of reset.

- Watchdog timer A watchdog timer monitors the execution of instructions by the processor. If the watchdog timer is not reset by firmware within a certain period of time, the watchdog timer generates a reset.

- Software The device can be reset under program control.

Figure 6-8. Resets

## 6.4.5 Pin Interrupts

All GPIO and SIO pins are able to generate interrupts to the system. All eight pins in each port interface to their own Port Interrupt Control Unit (PICU) and associated interrupt vector. Each pin of the port is independently configurable to detect rising edge, falling edge, both edge interrupts, or to not generate an interrupt.

Depending on the configured mode for each pin, each time an interrupt event occurs on a pin, its corresponding status bit of the interrupt status register is set to "1" and an interrupt request is sent to the interrupt controller. Each PICU has its own interrupt vector in the interrupt controller and the pin status register providing easy determination of the interrupt source down to the pin level.

Port pin interrupts remain active in all sleep modes allowing the PSoC device to wake from an externally generated interrupt.

While level sensitive interrupts are not directly supported; Universal Digital Blocks (UDB) provide this functionality to the system when needed.

### 6.4.6 Input Buffer Mode

GPIO and SIO input buffers can be configured at the port level for the default CMOS input thresholds or the optional LVTTL input thresholds. All input buffers incorporate Schmitt triggers for input hysteresis. Additionally, individual pin input buffers can be disabled in any drive mode.

#### 6.4.7 I/O Power Supplies

Up to four I/O pin power supplies are provided depending on the device and package. Each I/O supply must be less than or equal to the voltage on the chip's analog (VDDA) pin. This feature allows users to provide different I/O voltage levels for different pins on the device. Refer to the specific device package pinout to determine VDDIO capability for a given port and pin.

The SIO port pins support an additional regulated high output capability, as described in Adjustable Output Level.

# 6.4.8 Analog Connections

These connections apply only to GPIO pins. All GPIO pins may be used as analog inputs or outputs. The analog voltage present on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs. Each GPIO may connect to one of the analog global busses or to one of the analog mux buses to connect any pin to any internal analog resource such as ADC or comparators. In addition, one select pin provides direct connection to the high current DAC.

#### 6.4.9 CapSense

This section applies only to GPIO pins. All GPIO pins may be used to create CapSense buttons and sliders. See the "CapSense" section on page 61 for more information.

#### 6.4.10 LCD Segment Drive

This section applies only to GPIO pins. All GPIO pins may be used to generate Segment and Common drive signals for direct glass drive of LCD glass. See the "LCD Direct Drive" section on page 60 for details.

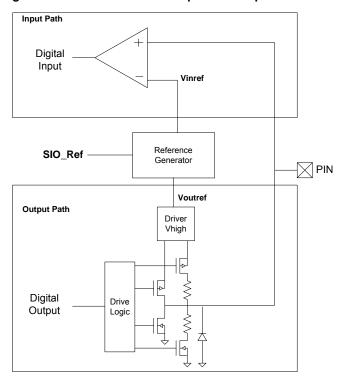

#### 6.4.11 Adjustable Output Level

This section applies only to SIO pins. SIO port pins support the ability to provide a regulated high output level for interface to external signals that are lower in voltage than the SIO's respective VDDIO. SIO pins are individually configurable to output either the standard VDDIO level or the regulated output, which is based on an internally generated reference. Typically the voltage DAC (VDAC) is used to generate the reference (see Figure 6-13). The "DAC" section on page 61 has more details on VDAC use and reference routing to the SIO pins. Resistive pull-up and pull-down drive modes are not available with SIO in regulated output mode.

## 6.4.12 Adjustable Input Level

This section applies only to SIO pins. SIO pins by default support the standard CMOS and LVTTL input levels but also support a differential mode with programmable levels. SIO pins are grouped into pairs. Each pair shares a reference generator block which, is used to set the digital input buffer reference level for interface to external signals that differ in voltage from VDDIO. The reference sets the pins voltage threshold for a high logic level (see Figure 6-13). Available input thresholds are:

- 0.5 × VDDIO

- 0.4 × VDDIO

- 0.5 × VREF

- VREF

Typically the voltage DAC (VDAC) generates the  $V_{REF}$  reference. The "DAC" section on page 61 has more details on VDAC use and reference routing to the SIO pins.

Figure 6-13. SIO Reference for Input and Output

# 7. Digital Subsystem

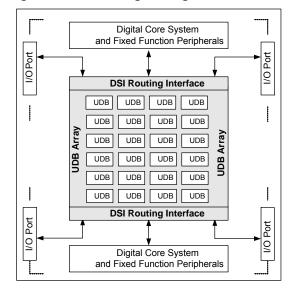

The digital programmable system creates application specific combinations of both standard and advanced digital peripherals and custom logic functions. These peripherals and logic are then interconnected to each other and to any pin on the device, providing a high level of design flexibility and IP security.

The features of the digital programmable system are outlined here to provide an overview of capabilities and architecture. You do not need to interact directly with the programmable digital system at the hardware and register level. PSoC Creator provides a high level schematic capture graphical interface to automatically place and route resources similar to PLDs.

The main components of the digital programmable system are:

- Universal Digital Blocks (UDB) These form the core functionality of the digital programmable system. UDBs are a collection of uncommitted logic (PLD) and structural logic (Datapath) optimized to create all common embedded peripherals and customized functionality that are application or design specific.

- Universal Digital Block Array UDB blocks are arrayed within a matrix of programmable interconnect. The UDB array structure is homogeneous and allows for flexible mapping of digital functions onto the array. The array supports extensive and flexible routing interconnects between UDBs and the Digital System Interconnect.

- Digital System Interconnect (DSI) Digital signals from Universal Digital Blocks (UDBs), fixed function peripherals, I/O pins, interrupts, DMA, and other system core signals are attached to the Digital System Interconnect to implement full featured device connectivity. The DSI allows any digital function to any pin or other feature routability when used with the Universal Digital Block Array.

Figure 7-1. CY8C32 Digital Programmable Architecture

## 7.1 Example Peripherals

The flexibility of the CY8C32 family's Universal Digital Blocks (UDBs) and Analog Blocks allow the user to create a wide range of components (peripherals). The most common peripherals were built and characterized by Cypress and are shown in the PSoC Creator component catalog, however, users may also create their own custom components using PSoC Creator. Using PSoC Creator, users may also create their own components for reuse within their organization, for example sensor interfaces, proprietary algorithms, and display interfaces.

The number of components available through PSoC Creator is too numerous to list in the datasheet, and the list is always growing. An example of a component available for use in CY8C32 family, but, not explicitly called out in this datasheet is the UART component.

## 7.1.1 Example Digital Components

The following is a sample of the digital components available in PSoC Creator for the CY8C32 family. The exact amount of hardware resources (UDBs, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Communications

- □ I<sup>2</sup>C

- UART

- SPI

- Functions

- EMIF

- PWMs

- □ Timers

- Counters

- Logic

- □ NOT

- □ OR □ XOR

- □ AND

## 7.1.2 Example Analog Components

The following is a sample of the analog components available in PSoC Creator for the CY8C32 family. The exact amount of hardware resources (routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- ADC

- Delta-sigma

- DACs

- Current

- Voltage

- □ PWM

- Comparators

#### 7.1.3 Example System Function Components

The following is a sample of the system function components available in PSoC Creator for the CY8C32 family. The exact amount of hardware resources (UDBs, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- CapSense

- LCD Drive

- LCD Control

# PSoC® 3: CY8C32 Family Data Sheet

## 7.7 I<sup>2</sup>C

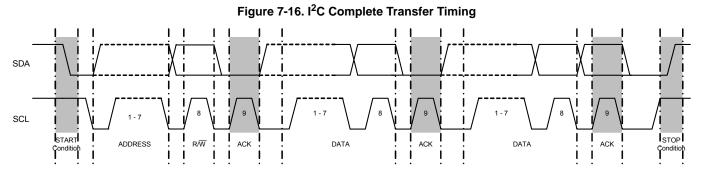

PSoC includes a single fixed-function I<sup>2</sup>C peripheral. Additional I<sup>2</sup>C interfaces can be instantiated using Universal Digital Blocks (UDBs) in PSoC Creator, as required.

The I<sup>2</sup>C peripheral provides a synchronous two-wire interface designed to interface the PSoC device with a two-wire I<sup>2</sup>C serial communication bus. It is compatible<sup>[13]</sup> with I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I2C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O may be implemented with GPIO or SIO in open-drain modes.

To eliminate the need for excessive CPU intervention and overhead, I<sup>2</sup>C specific support is provided for status detection and generation of framing bits. I<sup>2</sup>C operates as a slave, a master, or multimaster (Slave and Master)[14]. In slave mode, the unit always listens for a start condition to begin sending or receiving data. Master mode supplies the ability to generate the Start and Stop conditions and initiate transactions. Multimaster mode provides clock synchronization and arbitration to allow multiple masters on the same bus. If Master mode is enabled and Slave mode is not enabled, the block does not generate interrupts on externally generated Start conditions. I<sup>2</sup>C interfaces through the DSI routing and allows direct connections to any GPIO or SIO pins.

I<sup>2</sup>C provides hardware address detect of a 7-bit address without CPU intervention. Additionally the device can wake from low-power modes on a 7-bit hardware address match. If wakeup functionality is required, I2C pin connections are limited to one of two specific pairs of SIO pins. See descriptions of SCL and SDA pins in Pin Descriptions on page 12.

I<sup>2</sup>C features include:

- Slave and Master, Transmitter, and Receiver operation

- Byte processing for low CPU overhead

- Interrupt or polling CPU interface

- Support for bus speeds up to 1 Mbps

- 7 or 10-bit addressing (10-bit addressing requires firmware support)

- SMBus operation (through firmware support SMBus supported in hardware in UDBs)

- 7-bit hardware address compare

- Wake from low-power modes on address match

- Glitch filtering (active and alternate-active modes only)

Data transfers follow the format shown in Figure 7-16. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master.

7.7.1 External Electrical Connections

As Figure 7-17 shows, the I<sup>2</sup>C bus requires external pull-up resistors (R<sub>P</sub>). These resistors are primarily determined by the supply voltage, bus speed, and bus capacitance. For detailed

information on how to calculate the optimum pull-up resistor value for your design, we recommend using the UM10204 I2C-bus specification and user manual Rev 6, or newer, available from the NXP website at www.nxp.com.

#### Notes

<sup>13.</sup> The I<sup>2</sup>C peripheral is non-compliant with the NXP I2C specification in the following areas: analog glitch filter, I/O VOL/IOL, I/O hysteresis. The I<sup>2</sup>C Block has a digital glitch filter (not available in sleep mode). The Fast-mode minimum fall-time specification can be met by setting the I/Os to slow speed mode. See the I/O Electrical Specifications in "Inputs and Outputs" section on page 76 for details.

<sup>14.</sup> Fixed-block I<sup>2</sup>C does not support undefined bus conditions, nor does it support Repeated Start in Slave mode. These conditions should be avoided, or the UDB-based I<sup>2</sup>C component should be used instead.

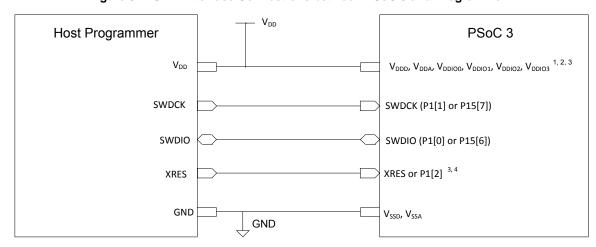

## 9.2 Serial Wire Debug Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D- pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8 µs (key window) after reset, that pin pair

(JTAG or USB) receives a predetermined acquire sequence of 1s and 0s. If the NVL latches are set for SWD (see *Section 5.5*), this sequence need not be applied to the JTAG pin pair. The acquire sequence must always be applied to the USB pin pair.

SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

Figure 9-2. SWD Interface Connections between PSoC 3 and Programmer

- The voltage levels of the Host Programmer and the PSoC 3 voltage domains involved in Programming should be the same. XRES pin (XRES\_N or P1[2]) is powered by V<sub>DDIO1</sub>. The USB SWD pins are powered by V<sub>DDD</sub>. So for Programming using the USB SWD pins with XRES pin, the V<sub>DDD</sub>, V<sub>DDIO1</sub> of PSoC 3 should be at the same voltage level as Host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDIO1</sub>. So V<sub>DDIO1</sub> of PSoC 3 should be at same voltage level as host V<sub>DD</sub> for Port 1 SWD programming. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDIO2</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer.

- Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

- For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48-pin devices, but use dedicated XRES pin for rest of devices.

Document Number: 001-56955 Rev. \*Y Page 64 of 128

Table 11-3. AC Specifications [30]

| Parameter              | Description                                                                                                                    | Conditions                                                                                      | Min | Тур | Max   | Units |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|-------|-------|

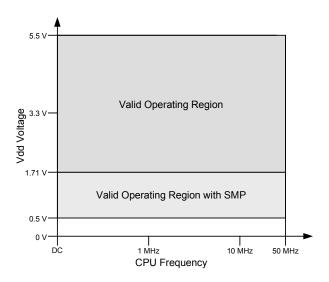

| F <sub>CPU</sub>       | CPU frequency                                                                                                                  | 1.71 V ≤ V <sub>DDD</sub> ≤ 5.5 V                                                               | DC  | -   | 50.01 | MHz   |

| F <sub>BUSCLK</sub>    | Bus frequency                                                                                                                  | 1.71 V ≤ V <sub>DDD</sub> ≤ 5.5 V                                                               | DC  | _   | 50.01 | MHz   |

| Svdd                   | V <sub>DD</sub> ramp rate                                                                                                      |                                                                                                 | -   | -   | 0.066 | V/µs  |

| T <sub>IO_INIT</sub>   | Time from V <sub>DDD</sub> /V <sub>DDA</sub> /V <sub>CCD</sub> /V <sub>CCA</sub> ≥ IPOR to I/O ports set to their reset states |                                                                                                 | -   | _   | 10    | μs    |

| T <sub>STARTUP</sub>   | Time from V <sub>DDD</sub> /V <sub>DDA</sub> /V <sub>CCD</sub> /V <sub>CCA</sub> ≥ PRES to CPU executing code at reset vector  | $V_{CCA}/V_{CCD}$ = regulated from $V_{DDA}/V_{DDD}$ , no PLL used, IMO boot mode (12 MHz typ.) | _   | _   | 74    | μs    |

| T <sub>SLEEP</sub>     | Wakeup from sleep mode –<br>Application of non-LVD interrupt to<br>beginning of execution of next CPU<br>instruction           |                                                                                                 | -   | _   | 15    | μs    |

| T <sub>HIBERNATE</sub> | Wakeup from hibernate mode –<br>Application of external interrupt to<br>beginning of execution of next CPU<br>instruction      |                                                                                                 | _   | -   | 100   | μs    |

Figure 11-4.  $F_{CPU}$  vs.  $V_{DD}$

# 11.3 Power Regulators

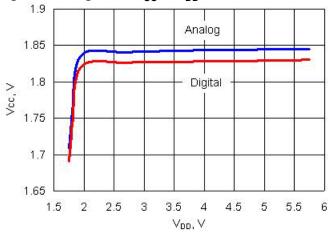

Specifications are valid for  $-40~^{\circ}C \le T_{A} \le 85~^{\circ}C$  and  $T_{J} \le 100~^{\circ}C$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

## 11.3.1 Digital Core Regulator

Table 11-4. Digital Core Regulator DC Specifications

| Parameter | Description                | Conditions                                                                                                                                          | Min | Тур  | Max | Units |

|-----------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| $V_{DDD}$ | Input voltage              |                                                                                                                                                     | 1.8 | _    | 5.5 | V     |

| $V_{CCD}$ | Output voltage             |                                                                                                                                                     | _   | 1.80 | _   | V     |

|           | Regulator output capacitor | $\pm 10\%$ , X5R ceramic or better. The two $V_{CCD}$ pins must be shorted together, with as short a trace as possible, see Power System on page 31 | 0.9 | 1    | 1.1 | μF    |

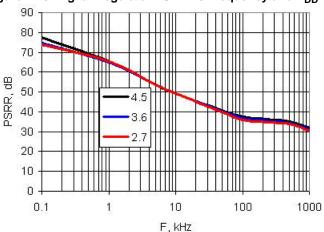

Figure 11-5. Regulators V<sub>CC</sub> vs V<sub>DD</sub>

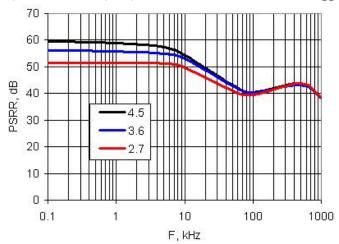

Figure 11-6. Digital Regulator PSRR vs Frequency and V<sub>DD</sub>

# 11.3.2 Analog Core Regulator

Table 11-5. Analog Core Regulator DC Specifications

| Parameter | Description                | Conditions                  | Min | Тур  | Max | Units |

|-----------|----------------------------|-----------------------------|-----|------|-----|-------|

| $V_{DDA}$ | Input voltage              |                             | 1.8 | _    | 5.5 | V     |

| $V_{CCA}$ | Output voltage             |                             | -   | 1.80 | 1   | V     |

|           | Regulator output capacitor | ±10%, X5R ceramic or better | 0.9 | 1    | 1.1 | μF    |

Figure 11-7. Analog Regulator PSRR vs Frequency and  $V_{\rm DD}$

Table 11-13. SIO Comparator Specifications<sup>[42]</sup>

| Parameter | Description                    | Conditions                | Min | Тур | Max | Units |

|-----------|--------------------------------|---------------------------|-----|-----|-----|-------|

| Vos       | Offset voltage                 | V <sub>DDIO</sub> = 2 V   | _   | _   | 68  | mV    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | _   | _   | 72  |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | _   | _   | 82  |       |

| TCVos     | Offset voltage drift with temp |                           | -   | _   | 250 | μV/°C |

| CMRR      | Common mode rejection ratio    | V <sub>DDIO</sub> = 2 V   | 30  | _   | -   | dB    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | 35  | _   | _   |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | 40  | _   | _   | ]     |

| Tresp     | Response time                  |                           | -   | -   | 30  | ns    |

## 11.4.3 USBIO

For operation in GPIO mode, the standard range for  $V_{DDD}$  applies, see Device Level Specifications on page 68.

Table 11-14. USBIO DC Specifications

| Parameter            | Description                            | Conditions                                         | Min            | Тур | Max            | Units |

|----------------------|----------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi                | USB D+ pull-up resistance              | With idle bus                                      | 0.900          | _   | 1.575          | kΩ    |

| Rusba                | USB D+ pull-up resistance              | While receiving traffic                            | 1.425          | _   | 3.090          | kΩ    |

| Vohusb               | Static output high                     | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | _   | 3.6            | V     |

| Volusb               | Static output low                      | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | -              | _   | 0.3            | V     |

| Vohgpio              | Output voltage high, GPIO mode         | $I_{OH}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | 2.4            | _   | -              | V     |

| Volgpio              | Output voltage low, GPIO mode          | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | -              | _   | 0.3            | V     |

| Vdi                  | Differential input sensitivity         | (D+)-(D-)                                          | -              | _   | 0.2            | V     |

| Vcm                  | Differential input common mode range   | -                                                  | 0.8            | _   | 2.5            | V     |

| Vse                  | Single ended receiver threshold        | _                                                  | 0.8            | _   | 2              | V     |

| Rps2                 | PS/2 pull-up resistance                | In PS/2 mode, with PS/2 pull-up enabled            | 3              | _   | 7              | kΩ    |

| Rext                 | External USB series resistor           | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo                   | USB driver output impedance            | Including Rext                                     | 28             | _   | 44             | Ω     |

| C <sub>IN</sub>      | USB transceiver input capacitance      | _                                                  | -              | _   | 20             | pF    |

| I <sub>IL</sub> [42] | Input leakage current (absolute value) | 25 °C, V <sub>DDD</sub> = 3.0 V                    | -              | _   | 2              | nA    |

#### Note

<sup>42.</sup> Based on device characterization (Not production tested).

Table 11-20. Delta-sigma ADC AC Specifications

| Parameter    | Description                                                       | Conditions                                   | Min | Тур | Max    | Units   |

|--------------|-------------------------------------------------------------------|----------------------------------------------|-----|-----|--------|---------|

|              | Startup time                                                      |                                              | -   | _   | 4      | Samples |

| THD          | Total harmonic distortion <sup>[48]</sup>                         | Buffer gain = 1, 12-bit,<br>Range = ±1.024 V | -   | _   | 0.0032 | %       |

| 12-Bit Resol | ution Mode                                                        |                                              |     | •   | •      | •       |

| SR12         | Sample rate, continuous, high power <sup>[48]</sup>               | Range = ±1.024 V, unbuffered                 | 4   | _   | 192    | ksps    |

| BW12         | Input bandwidth at max sample rate <sup>[48]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 44  | _      | kHz     |

| SINAD12int   | Signal to noise ratio, 12-bit, internal reference <sup>[48]</sup> | Range = ±1.024 V, unbuffered                 | 66  | _   | -      | dB      |

| 8-Bit Resolu | tion Mode                                                         |                                              |     | •   | •      | •       |

| SR8          | Sample rate, continuous, high power <sup>[48]</sup>               | Range = ±1.024 V, unbuffered                 | 8   | _   | 384    | ksps    |

| BW8          | Input bandwidth at max sample rate <sup>[48]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 88  | _      | kHz     |

| SINAD8int    | Signal to noise ratio, 8-bit, internal reference <sup>[48]</sup>  | Range = ±1.024 V, unbuffered                 | 43  | _   | -      | dB      |

Table 11-21. Delta-sigma ADC Sample Rates, Range = ±1.024 V

| Resolution, |      |        | Multi- | Sample |

|-------------|------|--------|--------|--------|

| Bits        | Min  | Max    | Min    | Max    |

| 8           | 8000 | 384000 | 1911   | 91701  |

| 9           | 6400 | 307200 | 1543   | 74024  |

| 10          | 5566 | 267130 | 1348   | 64673  |

| 11          | 4741 | 227555 | 1154   | 55351  |

| 12          | 4000 | 192000 | 978    | 46900  |

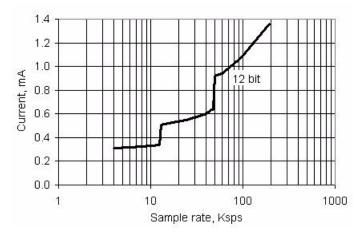

Figure 11-25. Delta-sigma ADC IDD vs sps, Range =  $\pm 1.024$  V, Continuous Sample Mode, Input Buffer Bypassed

#### Note

48. Based on device characterization (Not production tested).

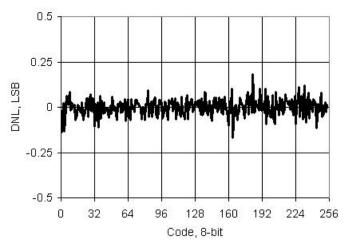

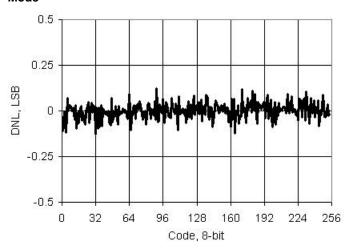

Figure 11-28. IDAC DNL vs Input Code, Range = 255  $\mu$ A, Source Mode

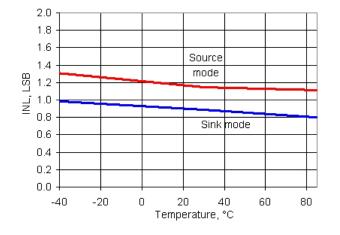

Figure 11-30. IDAC INL vs Temperature, Range = 255  $\mu$ A, High speed mode

Figure 11-29. IDAC DNL vs Input Code, Range = 255  $\mu$ A, Sink Mode

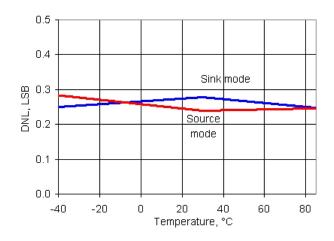

Figure 11-31. IDAC DNL vs Temperature, Range = 255  $\mu$ A, High speed mode

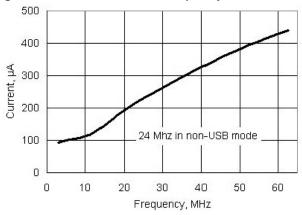

Figure 11-59. IMO Current vs. Frequency

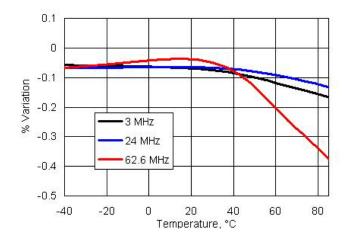

Table 11-66. IMO AC Specifications

| Parameter        | Description                                 | Conditions                                   | Min   | Тур | Max  | Units |

|------------------|---------------------------------------------|----------------------------------------------|-------|-----|------|-------|

| F <sub>IMO</sub> | IMO frequency stability (with factory trim) |                                              |       |     |      |       |

|                  | 24 MHz – Non USB mode                       |                                              | -4    | -   | 4    | %     |

|                  | 24 MHz – USB mode                           | With oscillator locking to USB bus           | -0.25 | -   | 0.25 | %     |

|                  | 12 MHz                                      |                                              | -3    | _   | 3    | %     |

|                  | 6 MHz                                       |                                              | -2    | -   | 2    | %     |

|                  | 3 MHz                                       |                                              | -2    | -   | 2    | %     |

|                  | Startup time <sup>[69]</sup>                | From enable (during normal system operation) | -     | _   | 13   | μs    |

| Jp-p             | Jitter (peak to peak) <sup>[69]</sup>       |                                              |       |     |      |       |

|                  | F = 24 MHz                                  |                                              | _     | 0.9 | _    | ns    |

|                  | F = 3 MHz                                   |                                              | _     | 1.6 | _    | ns    |

| Jperiod          | Jitter (long term) <sup>[69]</sup>          |                                              |       |     |      |       |

|                  | F = 24 MHz                                  |                                              | _     | 0.9 | _    | ns    |

|                  | F = 3 MHz                                   |                                              | _     | 12  | _    | ns    |

Figure 11-60. IMO Frequency Variation vs. Temperature

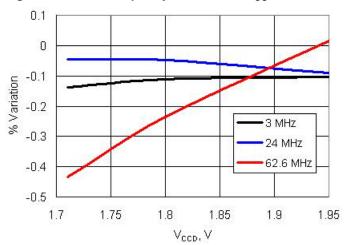

Figure 11-61. IMO Frequency Variation vs. V<sub>CC</sub>

# Note

69. Based on device characterization (Not production tested).

# 13. Packaging

**Table 13-1. Package Characteristics**

| Parameter      | Description                            | Conditions | Min | Тур   | Max | Units   |

|----------------|----------------------------------------|------------|-----|-------|-----|---------|

| T <sub>A</sub> | Operating ambient temperature          |            | -40 | 25.00 | 85  | °C      |

| $T_J$          | Operating junction temperature         |            | -40 | _     | 100 | °C      |

| $T_{JA}$       | Package θ <sub>JA</sub> (48-pin SSOP)  |            | -   | 49    | -   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (48-pin QFN)   |            | -   | 14    | -   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (68-pin QFN)   |            | -   | 15    | -   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (100-pin TQFP) |            | _   | 34    | _   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (48-pin SSOP)  |            | -   | 24    | -   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (48-pin QFN)   |            | -   | 15    | -   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (68-pin QFN)   |            | -   | 13    | -   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (100-pin TQFP) |            | -   | 10    | -   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (72-pin CSP)   |            | -   | 18    | -   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (72-pin CSP)   |            | _   | 0.13  | _   | °C/Watt |

Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at Peak<br>Temperature |

|--------------|-----------------------------|-------------------------------------|

| 48-pin SSOP  | 260 °C                      | 30 seconds                          |

| 48-pin QFN   | 260 °C                      | 30 seconds                          |

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

| 72-pin CSP   | 260 °C                      | 30 seconds                          |

Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 3 |

| 48-pin QFN   | MSL 3 |

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

| 72-pin CSP   | MSL 1 |

Document Number: 001-56955 Rev. \*Y Page 113 of 128

# 16. Document Conventions

# 16.1 Units of Measure

Table 16-1. Units of Measure

| Symbol | Unit of Measure        |

|--------|------------------------|

| °C     | degrees Celsius        |

| dB     | decibels               |

| fF     | femtofarads            |

| Hz     | hertz                  |

| KB     | 1024 bytes             |

| kbps   | kilobits per second    |

| Khr    | kilohours              |

| kHz    | kilohertz              |

| kΩ     | kilohms                |

| ksps   | kilosamples per second |

| LSB    | least significant bit  |

| Mbps   | megabits per second    |

| MHz    | megahertz              |

| ΜΩ     | megaohms               |

| Msps   | megasamples per second |

| μΑ     | microamperes           |

Table 16-1. Units of Measure (continued)

| Symbol | Unit of Measure      |

|--------|----------------------|

| μF     | microfarads          |

| μH     | microhenrys          |

| μs     | microseconds         |

| μV     | microvolts           |

| μW     | microwatts           |

| mA     | milliamperes         |

| ms     | milliseconds         |

| mV     | millivolts           |

| nA     | nanoamperes          |

| ns     | nanoseconds          |

| nV     | nanovolts            |

| Ω      | ohms                 |

| pF     | picofarads           |

| ppm    | parts per million    |

| ps     | picoseconds          |

| s      | seconds              |

| sps    | samples per second   |

| sqrtHz | square root of hertz |

| V      | volts                |

Document Number: 001-56955 Rev. \*Y Page 119 of 128