#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 50MHz                                                                       |

| Connectivity               | EBI/EMI, I²C, LINbus, SPI, UART/USART                                       |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                                |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 48-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3245pvi-134t |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Contents

| 1. Architectural Overview             | 4  |

|---------------------------------------|----|

| 2. Pinouts                            | 6  |

| 3. Pin Descriptions                   | 12 |

| 4. CPU                                | 13 |

| 4.1 8051 CPU                          | 13 |

| 4.2 Addressing Modes                  |    |

| 4.3 Instruction Set                   |    |

| 4.4 DMA and PHUB                      |    |

| 4.5 Interrupt Controller              | 20 |

| 5. Memory                             | 24 |

| 5.1 Static RAM                        | 24 |

| 5.2 Flash Program Memory              | 24 |

| 5.3 Flash Security                    |    |

| 5.4 EEPROM                            |    |

| 5.5 Nonvolatile Latches (NVLs)        |    |

| 5.6 External Memory Interface         |    |

| 5.7 Memory Map                        |    |

| 6. System Integration                 |    |

| 6.1 Clocking System                   |    |

| 6.2 Power System                      |    |

| 6.3 Reset                             |    |

| 6.4 I/O System and Routing            |    |

| 7. Digital Subsystem                  |    |

| 7.1 Example Peripherals               |    |

| 7.2 Universal Digital Block           |    |

| 7.3 UDB Array Description             |    |

| 7.4 DSI Routing Interface Description |    |

| 7.5 USB                               |    |

| 7.6 Timers, Counters, and PWMs        |    |

| 7.7 l <sup>2</sup> C                  |    |

| 8. Analog Subsystem                   |    |

| 8.1 Analog Routing                    |    |

| 8.2 Delta-sigma ADC                   |    |

| 8.3 Comparators                       |    |

| 8.4 LCD Direct Drive<br>8.5 CapSense  |    |

| 8.6 Temp Sensor                       |    |

| 8.7 DAC                               |    |

|                                       | 01 |

| 9. Programming, Debug Interfaces, Resources      |     |

|--------------------------------------------------|-----|

| 9.1 JTAG Interface                               |     |

| 9.2 Serial Wire Debug Interface                  |     |

| 9.3 Debug Features<br>9.4 Trace Features         |     |

| 9.5 Single Wire Viewer Interface                 |     |

| 9.6 Programming Features                         |     |

| 9.7 Device Security                              |     |

| 9.8 CSP Package Bootloader                       |     |

| 10. Development Support                          | 66  |

| 10.1 Documentation                               |     |

| 10.2 Online                                      |     |

| 10.3 Tools                                       |     |

| 11. Electrical Specifications                    |     |

| 11.1 Absolute Maximum Ratings                    |     |

| 11.2 Device Level Specifications                 |     |

| 11.3 Power Regulators<br>11.4 Inputs and Outputs |     |

| 11.5 Analog Peripherals                          |     |

| 11.6 Digital Peripherals                         |     |

| 11.7 Memory                                      |     |

| 11.8 PSoC System Resources                       |     |

| 11.9 Clocking                                    | 107 |

| 12. Ordering Information                         |     |

| 12.1 Part Numbering Conventions                  |     |

| 13. Packaging                                    | 113 |

| 14. Acronyms                                     | 117 |

| 15. Reference Documents                          | 118 |

| 16. Document Conventions                         | 119 |

| 16.1 Units of Measure                            | 119 |

| 17. Revision History                             | 120 |

| 18. Sales, Solutions, and Legal Information      | 128 |

| Worldwide Sales and Design Support               |     |

| Products                                         |     |

| PSoC® Solutions                                  |     |

| Cypress Developer Community                      |     |

| Technical Support                                | 128 |

## 4.4.4.5 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

#### 4.4.4.6 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase "subchains" can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

#### 4.4.4.7 Nested DMA

One TD may modify another TD, as the TD configuration space is memory mapped similar to any other peripheral. For example, a first TD loads a second TD's configuration and then calls the second TD. The second TD moves data as required by the application. When complete, the second TD calls the first TD, which again updates the second TD's configuration. This process repeats as often as necessary.

## 4.5 Interrupt Controller

The interrupt controller provides a mechanism for hardware resources to change program execution to a new address, independent of the current task being executed by the main code. The interrupt controller provides enhanced features not found on original 8051 interrupt controllers:

- Thirty two interrupt vectors

- Jumps directly to ISR anywhere in code space with dynamic vector addresses

- Multiple sources for each vector

- Flexible interrupt to vector matching

- Each interrupt vector is independently enabled or disabled

- Each interrupt can be dynamically assigned one of eight priorities

- Eight level nestable interrupts

- Multiple I/O interrupt vectors

- Software can send interrupts

- Software can clear pending interrupts

When an interrupt is pending, the current instruction is completed and the program counter is pushed onto the stack. Code execution then jumps to the program address provided by the vector. After the ISR is completed, a RETI instruction is executed and returns execution to the instruction following the previously interrupted instruction. To do this the RETI instruction pops the program counter from the stack.

If the same priority level is assigned to two or more interrupts, the interrupt with the lower vector number is executed first. Each interrupt vector may choose from three interrupt sources: Fixed Function, DMA, and UDB. The fixed function interrupts are direct connections to the most common interrupt sources and provide the lowest resource cost connection. The DMA interrupt sources provide direct connections to the two DMA interrupt sources provided per DMA channel. The third interrupt source for vectors is from the UDB digital routing array. This allows any digital signal available to the UDB array to be used as an interrupt source. Fixed function interrupts and all interrupt sources may be routed to any interrupt vector using the UDB interrupt source connections.

Figure 4-2 on page 21 represents typical flow of events when an interrupt triggered. Figure 4-3 on page 22 shows the interrupt structure and priority polling.

## 6.1.1 Internal Oscillators

Figure 6-1 shows that there are two internal oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

## 6.1.1.1 Internal Main Oscillator

In most designs the IMO is the only clock source required, due to its  $\pm$ 2-percent accuracy. The IMO operates with no external components and outputs a stable clock. A factory trim for each frequency range is stored in the device. With the factory trim, tolerance varies from  $\pm$ 2 percent at 3 MHz, up to  $\pm$ 4-percent at 24 MHz. The IMO, in conjunction with the PLL, allows generation of other clocks up to the device's maximum frequency (see Phase-locked Loop)

The IMO provides clock outputs at 3, 6, 12, and 24 MHz.

#### 6.1.1.2 Clock Doubler

The clock doubler outputs a clock at twice the frequency of the input clock. The doubler works at input frequency of 24 MHz, providing 48 MHz for the USB. It can be configured to use a clock from the IMO, MHzECO, or the DSI (external pin).

#### 6.1.1.3 Phase-locked Loop

The PLL allows low-frequency, high-accuracy clocks to be multiplied to higher frequencies. This is a tradeoff between higher clock frequency and accuracy and, higher power consumption and increased startup time.

The PLL block provides a mechanism for generating clock frequencies based upon a variety of input sources. The PLL outputs clock frequencies in the range of 24 to 50 MHz. Its input and feedback dividers supply 4032 discrete ratios to create almost any desired clock frequency. The accuracy of the PLL output depends on the accuracy of the PLL input source. The most common PLL use is to multiply the IMO clock at 3 MHz, where it is most accurate to generate the other clocks up to the device's maximum frequency.

The PLL achieves phase lock within 250 µs (verified by bit setting). It can be configured to use a clock from the IMO, MHZECO or DSI (external pin). The PLL clock source can be used until lock is complete and signaled with a lock bit. The lock signal can be routed through the DSI to generate an interrupt. Disable the PLL before entering low-power modes.

#### 6.1.1.4 Internal Low-Speed Oscillator

The ILO provides clock frequencies for low-power consumption, including the watchdog timer, and sleep timer. The ILO generates up to three different clocks: 1 kHz, 33 kHz, and 100 kHz.

The 1 kHz clock (CLK1K) is typically used for a background 'heartbeat' timer. This clock inherently lends itself to low-power supervisory operations such as the watchdog timer and long sleep intervals using the central timewheel (CTW).

The central timewheel is a 1 kHz, free running, 13-bit counter clocked by the ILO. The central timewheel is always enabled, except in hibernate mode and when the CPU is stopped during debug on chip mode. It can be used to generate periodic interrupts for timing purposes or to wake the system from a low-power mode. Firmware can reset the central timewheel. Systems that require accurate timing should use the RTC capability instead of the central timewheel.

The 100-kHz clock (CLK100K) can be used as a low power master clock. It can also generate time intervals using the fast timewheel.

The fast timewheel is a 5-bit counter, clocked by the 100-kHz clock. It features programmable settings and automatically resets when the terminal count is reached. An optional interrupt can be generated each time the terminal count is reached. This enables flexible, periodic interrupts of the CPU at a higher rate than is allowed using the central timewheel.

The 33-kHz clock (CLK33K) comes from a divide-by-3 operation on CLK100K. This output can be used as a reduced accuracy version of the 32.768-kHz ECO clock with no need for a crystal.

#### 6.1.2 External Oscillators

Figure 6-1 shows that there are two external oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

#### 6.1.2.1 MHz External Crystal Oscillator

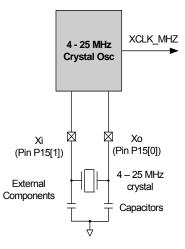

The MHzECO provides high frequency, high precision clocking using an external crystal (see Figure 6-2). It supports a wide variety of crystal types, in the range of 4 to 25 MHz. When used in conjunction with the PLL, it can generate other clocks up to the device's maximum frequency (see "Phase-locked Loop" section on page 30). The GPIO pins connecting to the external crystal and capacitors are fixed. MHzECO accuracy depends on the crystal chosen.

## Figure 6-2. MHzECO Block Diagram

## 6.1.2.2 32.768-kHz ECO

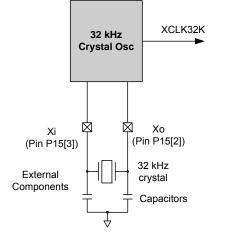

The 32.768-kHz External Crystal Oscillator (32kHzECO) provides precision timing with minimal power consumption using an external 32.768-kHz watch crystal (see Figure 6-3). The 32kHzECO also connects directly to the sleep timer and provides the source for the RTC. The RTC uses a 1-second interrupt to implement the RTC functionality in firmware.

The oscillator works in two distinct power modes. This allows users to trade off power consumption with noise immunity from neighboring circuits. The GPIO pins connected to the external crystal and capacitors are fixed.

## Figure 6-3. 32kHzECO Block Diagram

It is recommended that the external 32.768-kHz watch crystal have a load capacitance (CL) of 6 pF or 12.5 pF. Check the crystal manufacturer's datasheet. The two external capacitors, CL1 and CL2, are typically of the same value, and their total capacitance, CL1CL2 / (CL1 + CL2), including pin and trace capacitance, should equal the crystal CL value. For more information, refer to application note AN54439: PSoC 3 and PSoC 5 External Oscillators. See also pin capacitance specifications in the "GPIO" section on page 76.

#### 6.1.2.3 Digital System Interconnect

The DSI provides routing for clocks taken from external clock oscillators connected to I/O. The oscillators can also be generated within the device in the digital system and Universal Digital Blocks.

While the primary DSI clock input provides access to all clocking resources, up to eight other DSI clocks (internally or externally generated) may be routed directly to the eight digital clock dividers. This is only possible if there are multiple precision clock sources.

## 6.1.3 Clock Distribution

All seven clock sources are inputs to the central clock distribution system. The distribution system is designed to create multiple high precision clocks. These clocks are customized for the design's requirements and eliminate the common problems found with limited resolution prescalers attached to peripherals. The clock distribution system generates several types of clock trees.

The master clock is used to select and supply the fastest clock in the system for general clock requirements and clock synchronization of the PSoC device.

- Bus Clock 16-bit divider uses the master clock to generate the bus clock used for data transfers. Bus clock is the source clock for the CPU clock divider.

- Eight fully programmable 16-bit clock dividers generate digital system clocks for general use in the digital system, as configured by the design's requirements. Digital system clocks can generate custom clocks derived from any of the seven clock sources for any purpose. Examples include baud rate generators, accurate PWM periods, and timer clocks, and many others. If more than eight digital clock dividers are required, the Universal Digital Blocks (UDBs) and fixed function Timer/Counter/PWMs can also generate clocks.

- Four 16-bit clock dividers generate clocks for the analog system components that require clocking, such as ADC. The analog clock dividers include skew control to ensure that critical analog events do not occur simultaneously with digital switching events. This is done to reduce analog system noise.

Each clock divider consists of an 8-input multiplexer, a 16-bit clock divider (divide by 2 and higher) that generates ~50 percent duty cycle clocks, master clock resynchronization logic, and deglitch logic. The outputs from each digital clock tree can be routed into the digital system interconnect and then brought back into the clock system as an input, allowing clock chaining of up to 32 bits.

## 6.1.4 USB Clock Domain

The USB clock domain is unique in that it operates largely asynchronously from the main clock network. The USB logic contains a synchronous bus interface to the chip, while running on an asynchronous clock to process USB data. The USB logic requires a 48 MHz frequency. This frequency can be generated from different sources, including DSI clock at 48 MHz or doubled value of 24 MHz from internal oscillator, DSI signal, or crystal oscillator.

## 6.2 Power System

The power system consists of separate analog, digital, and I/O supply pins, labeled VDDA, VDDD, and VDDIOX, respectively. It also includes two internal 1.8 V regulators that provide the digital (VCCD) and analog (VCCA) supplies for the internal core logic. The output pins of the regulators (VCCD and VCCA) and the VDDIO pins must have capacitors connected as shown in Figure 6-4. The two VCCD pins must be shorted together, with as short a trace as possible, and connected to a 1- $\mu$ F ±10-percent X5R capacitor. The power system also contains a sleep regulator, an I<sup>2</sup>C regulator, and a hibernate regulator.

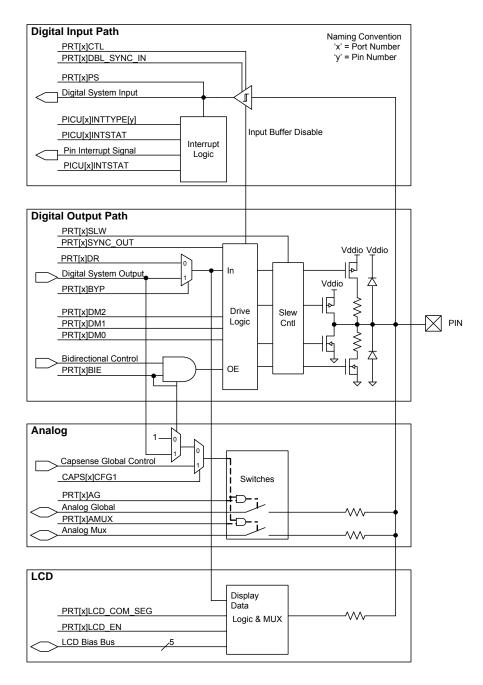

## Figure 6-9. GPIO Block Diagram

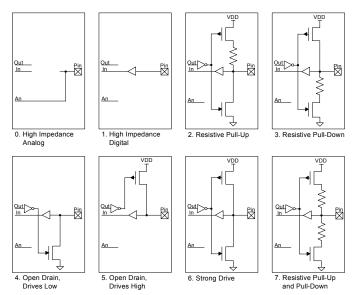

## 6.4.1 Drive Modes

Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-6. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-12 depicts a simplified pin view based on each of the eight drive modes. Table 6-6 shows the I/O pin's drive state based on the port data register value or digital array signal if bypass mode is selected. Note that the actual I/O pin voltage is determined by a combination of the selected drive mode and the load at the pin. For example, if a GPIO pin is configured for resistive pull-up mode and driven high while the pin is floating, the voltage measured at the pin is a high logic state. If the same GPIO pin is externally tied to ground then the voltage unmeasured at the pin is a low logic state.

#### Figure 6-12. Drive Mode

The 'Out' connection is driven from either the Digital System (when the Digital Output terminal is connected) or the Data Register (when HW connection is disabled). The 'in' connection drives the Pin State register, and the Digital System if the Digital Input terminal is enabled and connected. The 'An' connection connects to the Analog System.

#### Table 6-6. Drive Modes

| Diagram | Drive Mode                                      | PRTxDM2 | PRTxDM1 | PRTxDM0 | PRTxDR = 1    | PRTxDR = 0   |

|---------|-------------------------------------------------|---------|---------|---------|---------------|--------------|

| 0       | High impedence analog                           | 0       | 0       | 0       | High Z        | High Z       |

| 1       | High Impedance digital                          | 0       | 0       | 1       | High Z        | High Z       |

| 2       | Resistive pull-up <sup>[12]</sup>               | 0       | 1       | 0       | Res High (5K) | Strong Low   |

| 3       | Resistive pull-down <sup>[12]</sup>             | 0       | 1       | 1       | Strong High   | Res Low (5K) |

| 4       | Open drain, drives low                          | 1       | 0       | 0       | High Z        | Strong Low   |

| 5       | Open drain, drive high                          | 1       | 0       | 1       | Strong High   | High Z       |

| 6       | Strong drive                                    | 1       | 1       | 0       | Strong High   | Strong Low   |

| 7       | Resistive pull-up and pull-down <sup>[12]</sup> | 1       | 1       | 1       | Res High (5K) | Res Low (5K) |

The USBIO pins (P15[7] and P15[6]), when enabled for I/O mode, have limited drive mode control. The drive mode is set using the PRT15.DM0[7, 6] register. A resistive pull option is also available at the USBIO pins, which can be enabled using the PRT15.DM1[7, 6] register. When enabled for USB mode, the drive mode control has no impact on the configuration of the USB pins. Unlike the GPIO and SIO configurations, the port wide configuration registers do not configure the USB drive mode bits. Table 6-7 shows the drive mode configuration for the USBIO pins.

| PRT15.DM1[7,6]<br>Pull up enable | PRT15.DM0[7,6]<br>Drive Mode enable | PRT15.DR[7,6] = 1 | PRT15.DR[7,6] = 0 | Description                   |

|----------------------------------|-------------------------------------|-------------------|-------------------|-------------------------------|

| 0                                | 0                                   | High Z            | Strong Low        | Open Drain, Strong Low        |

| 0                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

| 1                                | 0                                   | Res High (5k)     | Strong Low        | Resistive Pull Up, Strong Low |

| 1                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

## Table 6-7. USBIO Drive Modes (P15[7] and P15[6])

## High Impedance Analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

High Impedance Digital

The input buffer is enabled for digital signal input. This is the standard high impedance (HiZ) state recommended for digital inputs.

Resistive pull-up or resistive pull-down

Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

Open Drain, Drives High and Open Drain, Drives Low

Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the  $I^2C$  bus signal lines.

Strong Drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

Resistive pull-up and pull-down

Similar to the resistive pull-up and resistive pull-down modes except the pin is always in series with a resistor. The high data state is pull-up while the low data state is pull-down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

## 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

## 6.4.3 Bidirectional Mode

High-speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRT×DM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

## 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRT×SLW registers.

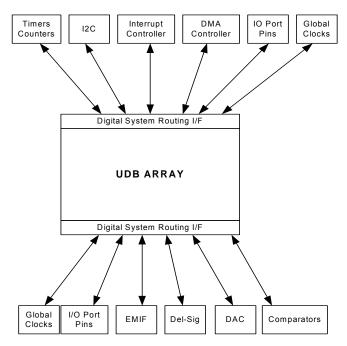

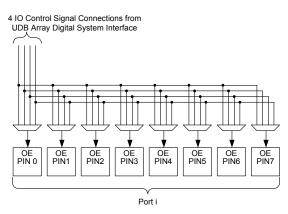

## Figure 7-9. Digital System Interconnect

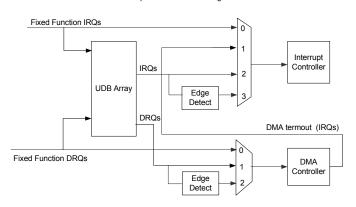

Interrupt and DMA routing is very flexible in the CY8C32 programmable architecture. In addition to the numerous fixed function peripherals that can generate interrupt requests, any data signal in the UDB array routing can also be used to generate a request. A single peripheral may generate multiple independent interrupt requests simplifying system and firmware design. Figure 7-10 shows the structure of the IDMUX (Interrupt/DMA Multiplexer).

## Figure 7-10. Interrupt and DMA Processing in the IDMUX

Interrupt and DMA Processing in IDMUX

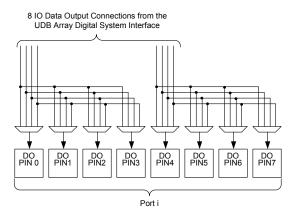

## 7.4.1 I/O Port Routing

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

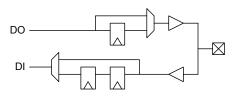

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In

conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

## Figure 7-11. I/O Pin Synchronization Routing

## Figure 7-12. I/O Pin Output Connectivity

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

## Figure 7-13. I/O Pin Output Enable Connectivity

## 8.1 Analog Routing

The CY8C32 family of devices has a flexible analog routing architecture that provides the capability to connect GPIOs and different analog blocks, and also route signals between different analog blocks. One of the strong points of this flexible routing architecture is that it allows dynamic routing of input and output connections to the different analog blocks.

For information on how to make pin selections for optimal analog routing, refer to the application note, AN58304 - PSoC® 3 and PSoC® 5 - Pin Selection for Analog Designs.

- 8.1.1 Features

- Flexible, configurable analog routing architecture

- 16 analog globals (AG) and two analog mux buses (AMUXBUS) to connect GPIOs and the analog blocks

- Each GPIO is connected to one analog global and one analog mux bus

- Eight analog local buses (abus) to route signals between the different analog blocks

- Multiplexers and switches for input and output selection of the analog blocks

#### 8.1.2 Functional Description

Analog globals (AGs) and analog mux buses (AMUXBUS) provide analog connectivity between GPIOs and the various analog blocks. There are 16 AGs in the CY8C32 family. The analog routing architecture is divided into four quadrants as shown in Figure 8-2. Each quadrant has four analog globals (AGL[0..3], AGL[4..7], AGR[0..3], AGR[4..7]). Each GPIO is connected to the corresponding AG through an analog switch. The analog mux bus is a shared routing resource that connects to every GPIO through an analog switch. There are two AMUXBUS routes in CY8C32, one in the left half (AMUXBUSL) and one in the right half (AMUXBUSR), as shown in Figure 8-2.

## 9. Programming, Debug Interfaces, Resources

PSoC devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware. Three interfaces are available: JTAG, SWD, and SWV. JTAG and SWD support all programming and debug features of the device. JTAG also supports standard JTAG scan chains for board level test and chaining multiple JTAG devices to a single JTAG connection.

For more information on PSoC 3 Programming, refer to the PSoC<sup>®</sup> 3 Device Programming Specifications.

Complete Debug on Chip (DoC) functionality enables full device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator IDE software provides fully integrated programming and debug support for PSoC devices. The low cost MiniProg3 programmer and debugger is designed to provide full programming and debug support of PSoC devices in conjunction with the PSoC Creator IDE. PSoC JTAG, SWD, and SWV interfaces are fully compatible with industry standard third party tools.

All DOC circuits are disabled by default and can only be enabled in firmware. If not enabled, the only way to reenable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables DOC. Disabling DOC features, robust flash protection, and hiding custom analog and digital functionality inside the PSoC device provide a level of security not possible with multichip application solutions. Additionally, all device interfaces can be permanently disabled (Device Security) for applications concerned about phishing attacks due to a maliciously reprogrammed device. Permanently disabling interfaces is not recommended in most applications because you cannot access the device later. Because all programming, debug, and test interfaces are disabled when Device Security is enabled, PSoCs with Device Security enabled may not be returned for failure analysis.

#### Table 9-1. Debug Configurations

| Debug and Trace Configuration | GPIO Pins Used |

|-------------------------------|----------------|

| All debug and trace disabled  | 0              |

| JTAG                          | 4 or 5         |

| SWD                           | 2              |

| SWV                           | 1              |

| SWD + SWV                     | 3              |

## 9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG interface is used for programming the flash memory, debugging, I/O scan chains, and JTAG device chaining.

PSoC 3 has certain timing requirements to be met for entering programming mode through the JTAG interface. Due to these timing requirements, not all standard JTAG programmers, or standard JTAG file formats such as SVF or STAPL, can support PSoC 3 programming. The list of programmers that support PSoC 3 programming is available at

http://www.cypress.com/go/programming.

The JTAG clock frequency can be up to 14 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit transfers, or 1/5 of the CPU clock frequency for 32-bit transfers. By default, the JTAG pins are enabled on new devices but the JTAG interface can be disabled, allowing these pins to be used as GPIO instead.

## 9.8 CSP Package Bootloader

A factory-installed bootloader program is included in all devices with CSP packages. The bootloader is compatible with PSoC Creator 3.0 bootloadable project files and has the following features:

- I<sup>2</sup>C-based

- SCLK and SDAT available at P1[6] and P1[7], respectively

- External pull-up resistors required

- I<sup>2</sup>C slave, address 4, data rate = 100 kbps

- Single application

- Wait two seconds for bootload command

- Other bootloader options are as set by the PSoC Creator 3.0 Bootloader Component default

- Occupies the bottom 9K of flash

For more information on this bootloader, see the following Cypress application notes:

- AN89611 PSoC<sup>®</sup> 3 AND PSoC 5LP Getting Started With Chip Scale Packages (CSP)

- AN73854 PSoC 3 and PSoC 5 LP Introduction to Bootloaders

- AN60317 PSoC 3 and PSoC 5 LP I<sup>2</sup>C Bootloader

Note that a PSoC Creator bootloadable project must be associated with .hex and .elf files for a bootloader project that is configured for the target device. Bootloader .hex and .elf files can be found at www.cypress.com/go/PSoC3datasheet.

The factory-installed bootloader can be overwritten using JTAG or SWD programming.

## 10. Development Support

The CY8C32 family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit psoc.cypress.com/getting-started to find out more.

## **10.1 Documentation**

A suite of documentation, supports the CY8C32 family to ensure that you can find answers to your questions quickly. This section contains a list of some of the key documents.

**Software User Guide**: A step-by-step guide for using PSoC Creator. The software user guide shows you how the PSoC Creator build process works in detail, how to use source control with PSoC Creator, and much more.

**Component Datasheets**: The flexibility of PSoC allows the creation of new peripherals (components) long after the device has gone into production. Component datasheets provide all of the information needed to select and use a particular component, including a functional description, API documentation, example code, and AC/DC specifications.

**Application Notes**: PSoC application notes discuss a particular application of PSoC in depth; examples include brushless DC motor control and on-chip filtering. Application notes often include example projects in addition to the application note document.

**Technical Reference Manual**: The Technical Reference Manual (TRM) contains all the technical detail you need to use a PSoC device, including a complete description of all PSoC registers.

## 10.2 Online

In addition to print documentation, the Cypress PSoC forums connect you with fellow PSoC users and experts in PSoC from around the world, 24 hours a day, 7 days a week.

## 10.3 Tools

With industry standard cores, programming, and debugging interfaces, the CY8C32 family is part of a development tool ecosystem. Visit us at www.cypress.com/go/psoccreator for the latest information on the revolutionary, easy to use PSoC Creator IDE, supported third party compilers, programmers, debuggers, and development kits.

## **11.2 Device Level Specifications**

Specifications are valid for –40  $^{\circ}C \le T_A \le 85 ~^{\circ}C$  and  $T_J \le 100 ~^{\circ}C$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.2.1 Device Level Specifications

## Table 11-2. DC Specifications

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Description                                                                   | Conditions                                                   |                                                        | Min  | Typ <sup>[22]</sup> | Max                                    | Units |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------|------|---------------------|----------------------------------------|-------|

| V <sub>DDA</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Analog supply voltage and input to analog core regulator                      | Analog core regulato                                         | r enabled                                              | 1.8  | _                   | 5.5                                    | V     |

| V <sub>DDA</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Analog supply voltage, analog regulator bypassed                              | Analog core regulato                                         | r disabled                                             | 1.71 | 1.8                 | 1.89                                   | V     |

| Vaaa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                               | Digital core regulator                                       | enabled                                                | 1.8  | -                   | V <sub>DDA</sub> <sup>[18]</sup>       | V     |

| • DDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               | Digital core regulator                                       | Chabled                                                | 1    | -                   | V <sub>DDA</sub> + 0.1 <sup>[24]</sup> | v     |

| V <sub>DDD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Digital supply voltage, digital regulator<br>bypassed                         | Digital core regulator                                       | disabled                                               | 1.71 | 1.8                 | 1.89                                   | V     |

| VDDIO <sup>[19]</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O supply voltage relative to Vesio                                          |                                                              |                                                        | 1.71 | -                   | V <sub>DDA</sub> <sup>[18]</sup>       | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |                                                              |                                                        | -    | -                   | V <sub>DDA</sub> + 0.1 <sup>[24]</sup> |       |

| V <sub>CCA</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Direct analog core voltage input (Analog regulator bypass)                    | Analog core regulato                                         | r disabled                                             | 1.71 | 1.8                 | 1.89                                   | V     |

| V <sub>CCD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Direct digital core voltage input (Digital regulator bypass)                  | Digital core regulator                                       | disabled                                               | 1.71 | 1.8                 | 1.89                                   | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Active Mode                                                                   |                                                              |                                                        |      |                     |                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Only IMO and CPU clock enabled. CPU<br>executing simple loop from instruction | $V_{DDX} = 2.7 V - 5.5 V;$<br>$F_{CPU} = 6 MHz^{[23]}$ T = 2 | T = -40 °C                                             | -    | 1.2                 | 2.9                                    |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |                                                              |                                                        | -    | 1.2                 |                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |                                                              |                                                        | -    |                     |                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               | $V_{PPV} = 27V - 55V$                                        |                                                        | -    |                     |                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               | $F_{CPU} = 3 \text{ MHz}^{[23]}$                             | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |      |                     |                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |                                                              |                                                        | -    | 4.8                 | 7.5                                    |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |                                                              |                                                        | -    | 2.1                 | 3.7                                    |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               | $V_{DDX} = 2.7 V - 5.5 V;$<br>E <sub>CDU</sub> = 6 MHz       | T = 25 °C                                              | -    | 2.3                 | 3.9                                    |       |

| I <sub>DD</sub> <sup>[20, 21]</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                               |                                                              | T = 85 °C                                              | _    | 5.6                 | 8.5                                    | m۸    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IMO enabled, bus clock and CPU clock                                          | $V_{DDX} = 2.7 V - 5.5 V;$                                   | T = -40 °C                                             | -    | 3.5                 | 5.2                                    |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | enabled. CPU executing program from                                           | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $      |                                                        |      |                     |                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |                                                              |                                                        |      |                     |                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               | $V_{DDX} = 2.7 V - 5.5 V;$                                   | T = -40 °C                                             | -    | 6.3                 | 8.1                                    |       |

| VDDD       bypassed         VDDIO       bypassed         VDDIO       I/O supply voltage relative to VSSIO         VCCA       Direct analog core voltage input (Analog regulator bypass)         VCCD       Direct digital core voltage input (Digital regulator bypass)         VCCD       Direct digital core voltage input (Digital regulator bypass)         Active Mode       Only IMO and CPU clock enabled. CPU executing simple loop from instruction buffer.         IDD       IMO enabled, bus clock and CPU clock enabled. CPU executing program from                                                                             | E 04 MIL [23]                                                                 | T = 25 °C                                                    | -                                                      | 6.6  | 8.3                 |                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |                                                              | T = 85 °C                                              | -    | 10                  | 13                                     |       |

| VDDD       Digital supply voltage relative to         VDDD       Digital supply voltage, digital reg bypassed         VDDD       Digital supply voltage, digital reg bypassed         VDDIO       I/O supply voltage relative to Vss         VCCA       Direct analog core voltage input regulator bypass)         VCCD       Direct digital core voltage input (regulator bypass)         VCCD       Direct digital core voltage input (regulator bypass)         Active Mode       Only IMO and CPU clock enable executing simple loop from instrubuffer.         IDD       IMO enabled, bus clock and CPU enabled. CPU executing program |                                                                               | $V_{DDX} = 2.7 V - 5.5 V;$                                   | T = -40 °C                                             | _    | 11.5                | 13.5                                   |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               | F <sub>CPU</sub> = 48 MHz <sup>[23]</sup>                    | T = 25 °C                                              | -    | 12                  | 14                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |                                                              | T = 85 °C                                              | _    | 15.5                | 18.5                                   |       |

#### Notes

18. The power supplies can be brought up in any sequence however once stable  $V_{DDA}$  must be greater than or equal to all other supplies. 19. The  $V_{DDIO}$  supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin  $\leq V_{DDIO} \leq V_{DDA}$ . 20. Total current for all power domains: digital ( $I_{DDD}$ ), analog ( $I_{DDA}$ ), and I/Os ( $I_{DDIO0, 1, 2, 3}$ ). Boost not included. All I/Os floating.

21. The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find the CPU current at the frequency of interest and add peripheral currents for your particular system from the device datasheet and component datasheets.

22.  $V_{DDX}$  = 3.3 V. 23. Based on device characterizations (Not production tested).

24. Guaranteed by design, not production tested.

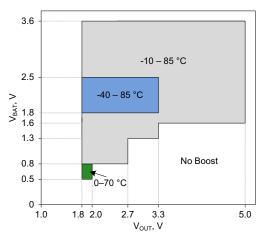

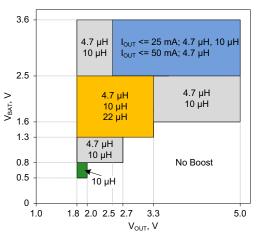

## 11.3.3 Inductive Boost Regulator

Unless otherwise specified, operating conditions are:  $V_{BAT} = 0.5 V-3.6 V$ ,  $V_{OUT} = 1.8 V-5.0 V$ ,  $I_{OUT} = 0 mA-50 mA$ ,  $L_{BOOST} = 4.7 \mu H-22 \mu$ H,  $C_{BOOST} = 22 \mu$ F || 3 × 1.0  $\mu$ F || 3 × 0.1  $\mu$ F,  $C_{BAT} = 22 \mu$ F,  $I_F = 1.0 A$ . Unless otherwise specified, all charts and graphs show typical values.

| Table 11-6. Inductive Boost Regulator DC Specification | Table 11-6. | Inductive | Boost | Regulator | DC S | pecifications |

|--------------------------------------------------------|-------------|-----------|-------|-----------|------|---------------|

|--------------------------------------------------------|-------------|-----------|-------|-----------|------|---------------|

| Parameter           | Description                            | Cond                          | ditions                                                               | Min  | Тур  | Max  | Units      |

|---------------------|----------------------------------------|-------------------------------|-----------------------------------------------------------------------|------|------|------|------------|

| V <sub>OUT</sub>    | Boost output voltage <sup>[31]</sup>   | vsel = 1.8 V in regist        | ter BOOST_CR0                                                         | 1.71 | 1.8  | 1.89 | V          |

|                     |                                        | vsel = 1.9 V in regist        | ter BOOST_CR0                                                         | 1.81 | 1.90 | 2.00 | V          |

|                     |                                        | vsel = 2.0 V in regist        | ter BOOST_CR0                                                         | 1.90 | 2.00 | 2.10 | V          |

|                     |                                        | vsel = 2.4 V in regist        | ter BOOST_CR0                                                         | 2.16 | 2.40 | 2.64 | V          |

|                     |                                        | vsel = 2.7 V in regist        | ter BOOST_CR0                                                         | 2.43 | 2.70 | 2.97 | V          |

|                     |                                        | vsel = 3.0 V in regist        | ter BOOST_CR0                                                         | 2.70 | 3.00 | 3.30 | V          |

|                     |                                        | vsel = 3.3 V in regist        | ter BOOST_CR0                                                         | 2.97 | 3.30 | 3.63 | V          |

|                     |                                        | vsel = 3.6 V in regist        | ter BOOST_CR0                                                         | 3.24 | 3.60 | 3.96 | V          |

|                     |                                        | vsel = 5.0 V in regist        | ter BOOST_CR0                                                         | 4.50 | 5.00 | 5.50 | V          |

| V <sub>BAT</sub>    | Input voltage to boost <sup>[32]</sup> | I <sub>OUT</sub> = 0 mA–5 mA  | vsel = 1.8 V–2.0 V,<br>T <sub>A</sub> = 0 °C–70 °C                    | 0.5  | -    | 0.8  | V          |

|                     |                                        | I <sub>OUT</sub> = 0 mA–15 mA | vsel = 1.8 V–5.0 V <sup>[33]</sup> ,<br>T <sub>A</sub> = –10 °C–85 °C | 1.6  | -    | 3.6  | V          |

|                     |                                        | I <sub>OUT</sub> = 0 mA–25 mA | vsel = 1.8 V–2.7 V,<br>T <sub>A</sub> = –10 °C–85 °C                  | 0.8  | -    | 1.6  | V          |

|                     |                                        | I <sub>OUT</sub> = 0 mA–50 mA | vsel = 1.8 V–3.3 V <sup>[33]</sup> ,<br>T <sub>A</sub> = –40 °C–85 °C | 1.8  | -    | 2.5  | V          |

|                     |                                        |                               | vsel = 1.8 V–3.3 V <sup>[33]</sup> ,<br>T <sub>A</sub> = –10 °C–85 °C | 1.3  | -    | 2.5  | V          |

|                     |                                        |                               | vsel = 2.5 V–5.0 V <sup>[33]</sup> ,<br>T <sub>A</sub> = –10 °C–85 °C | 2.5  | -    | 3.6  | V          |

| I <sub>OUT</sub>    | Output current                         | T <sub>A</sub> = 0 °C–70 °C   | V <sub>BAT</sub> = 0.5 V–0.8 V                                        | 0    | _    | 5    | mA         |

|                     |                                        | T <sub>A</sub> = −10 °C−85 °C | V <sub>BAT</sub> = 1.6 V–3.6 V                                        | 0    | -    | 15   | mA         |

|                     |                                        |                               | V <sub>BAT</sub> = 0.8 V–1.6 V                                        | 0    | _    | 25   | mA         |

|                     |                                        |                               | V <sub>BAT</sub> = 1.3 V–2.5 V                                        | 0    | _    | 50   | mA         |

|                     |                                        |                               | V <sub>BAT</sub> = 2.5 V–3.6 V                                        | 0    | _    | 50   | mA         |

|                     |                                        | T <sub>A</sub> = -40 °C-85 °C |                                                                       | 0    | _    | 50   | mA         |

| I <sub>LPK</sub>    | Inductor peak current                  | A                             |                                                                       | _    | _    | 700  | mA         |

|                     | Quiescent current                      | Boost active mode             |                                                                       | _    | 250  | -    | μΑ         |

| νQ                  |                                        | Boost sleep mode, I           | out < 1 µA                                                            |      | 250  | _    | μΑ         |

| Pog                 | Load regulation                        |                               |                                                                       |      |      | 10   | μ <u>γ</u> |

| Reg <sub>LOAD</sub> | -                                      |                               |                                                                       | _    | -    | _    |            |

| Reg <sub>LINE</sub> | Line regulation                        |                               |                                                                       | -    | -    | 10   | %          |

#### Notes

- 31. Listed vsel options are characterized. Additional vsel options are valid and guaranteed by design.

32. The boost will start at all valid V<sub>BAT</sub> conditions including down to V<sub>BAT</sub> = 0.5 V.

33. If V<sub>BAT</sub> is greater than or equal to V<sub>OUT</sub> boost setting, then V<sub>OUT</sub> will be less than V<sub>BAT</sub> due to resistive losses in the boost circuit.

| Table 11-7. | Recommended External Components for Boost Circuit |

|-------------|---------------------------------------------------|

|             |                                                   |

| Parameter          | Description                                                                                      | Conditions     | Min  | Тур  | Max  | Units |

|--------------------|--------------------------------------------------------------------------------------------------|----------------|------|------|------|-------|

| L <sub>BOOST</sub> | Boost inductor                                                                                   | 4.7 μH nominal | 3.7  | 4.7  | 5.7  | μH    |

|                    |                                                                                                  | 10 μH nominal  | 8.0  | 10.0 | 12.0 | μH    |

|                    |                                                                                                  | 22 μH nominal  | 17.0 | 22.0 | 27.0 | μH    |

| C <sub>BOOST</sub> | Total capacitance sum of V <sub>DDD</sub> , V <sub>DDA</sub> , V <sub>DDIO</sub> <sup>[34]</sup> |                | 17.0 | 26.0 | 31.0 | μF    |

| C <sub>BAT</sub>   | Battery filter capacitor                                                                         |                | 17.0 | 22.0 | 27.0 | μF    |

| I <sub>F</sub>     | Schottky diode average forward current                                                           |                | 1.0  | _    | -    | A     |

| V <sub>R</sub>     | Schottky reverse voltage                                                                         |                | 20.0 | -    | -    | V     |

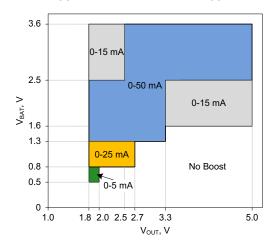

## Figure 11-8. T<sub>A</sub> range over $V_{BAT}$ and $V_{OUT}$

Figure 11-10.  $L_{BOOST}$  values over  $V_{BAT}$  and  $V_{OUT}$

## Figure 11-9. $I_{OUT}$ range over $V_{BAT}$ and $V_{OUT}$

#### Note

34. Based on device characterization (Not production tested).

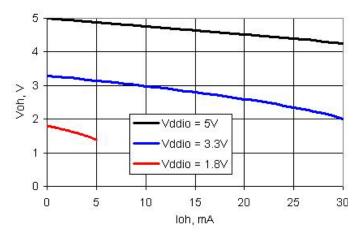

Figure 11-17. SIO Output High Voltage and Current, Unregulated Mode

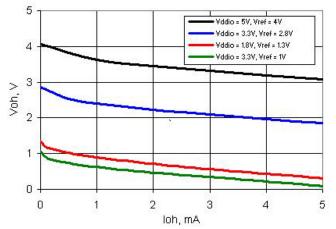

Figure 11-19. SIO Output High Voltage and Current, Regulated Mode

Table 11-12. SIO AC Specifications

| Parameter | Description                                            | Conditions                               | Min | Тур | Max | Units |

|-----------|--------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in Fast Strong Mode (90/10%) <sup>[41]</sup> | Cload = 25 pF, $V_{DDIO}$ = 3.3 V        | _   | -   | 12  | ns    |

| TfallF    | Fall time in Fast Strong Mode (90/10%) <sup>[41]</sup> | Cload = 25 pF, $V_{DDIO}$ = 3.3 V        | -   | -   | 12  | ns    |

| TriseS    | Rise time in Slow Strong Mode (90/10%) <sup>[41]</sup> | Cload = 25 pF, $V_{DDIO}$ = 3.0 V        | -   | _   | 75  | ns    |

| TfallS    | Fall time in Slow Strong Mode (90/10%) <sup>[41]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | -   | -   | 60  | ns    |

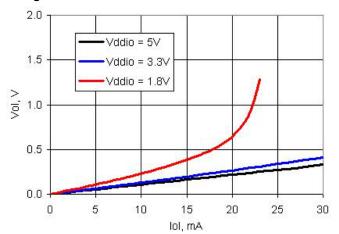

# Figure 11-18. SIO Output Low Voltage and Current, Unregulated Mode

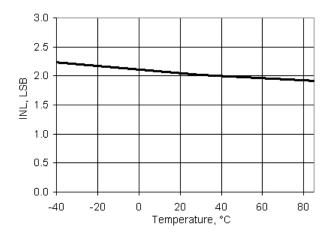

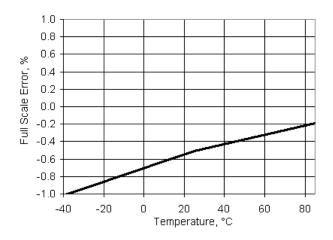

Figure 11-42. VDAC INL vs Temperature, 1 V Mode

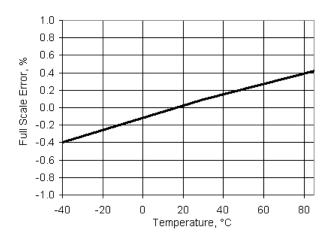

Figure 11-44. VDAC Full Scale Error vs Temperature, 1 V Mode

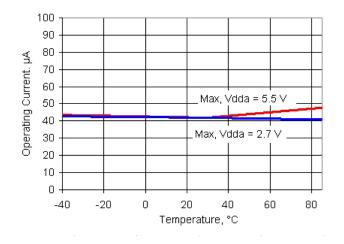

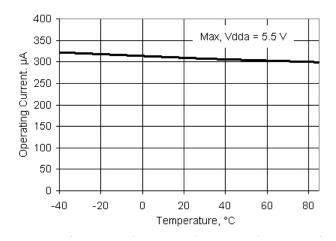

Figure 11-46. VDAC Operating Current vs Temperature, 1V Mode, Low speed mode

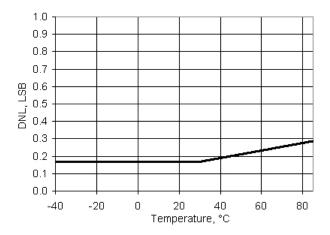

Figure 11-43. VDAC DNL vs Temperature, 1 V Mode

Figure 11-45. VDAC Full Scale Error vs Temperature, 4 V Mode

Figure 11-47. VDAC Operating Current vs Temperature, 1 V Mode, High speed mode

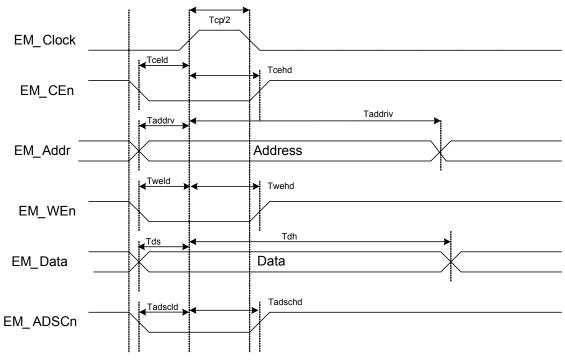

Figure 11-56. Synchronous Write Cycle Timing

| Table 11-56. | Synchronous | Write Cycle | Specifications |