Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 68-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3246lti-128 |

### 1. Architectural Overview

Introducing the CY8C32 family of ultra low-power, flash Programmable System-on-Chip (PSoC®) devices, part of a scalable 8-bit PSoC 3 and 32-bit PSoC 5 platform. The CY8C32 family provides configurable blocks of analog, digital, and interconnect circuitry around a CPU subsystem. The combination of a CPU with a flexible analog subsystem, digital subsystem, routing, and I/O enables a high level of integration in a wide variety of consumer, industrial, and medical applications.

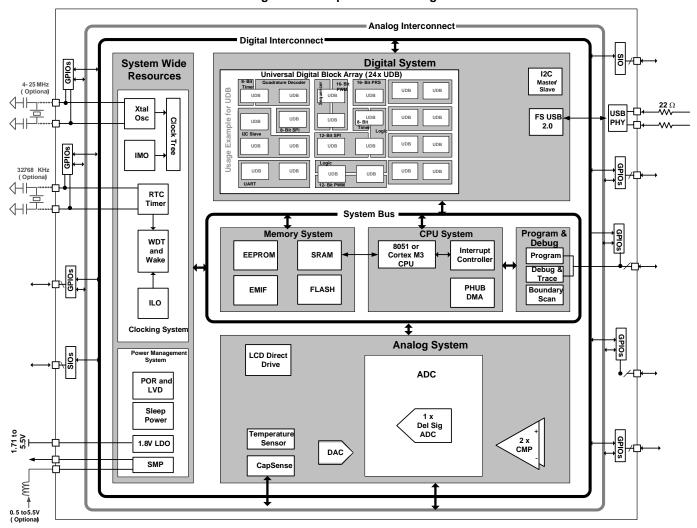

Figure 1-1. Simplified Block Diagram

Figure 1-1 illustrates the major components of the CY8C32 family. They are:

- 8051 CPU subsystem

- Nonvolatile subsystem

- Programming, debug, and test subsystem

- Inputs and outputs

- Clocking

- Power

- Digital subsystem

- Analog subsystem

PSoC's digital subsystem provides half of its unique configurability. It connects a digital signal from any peripheral to any pin through the Digital System Interconnect (DSI). It also provides functional flexibility through an array of small, fast, low-power UDBs. PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. You can also easily create a digital circuit using boolean primitives by means of graphical design entry. Each UDB contains programmable array logic (PAL)/programmable logic device (PLD) functionality, together with a small state machine engine to support a wide variety of peripherals.

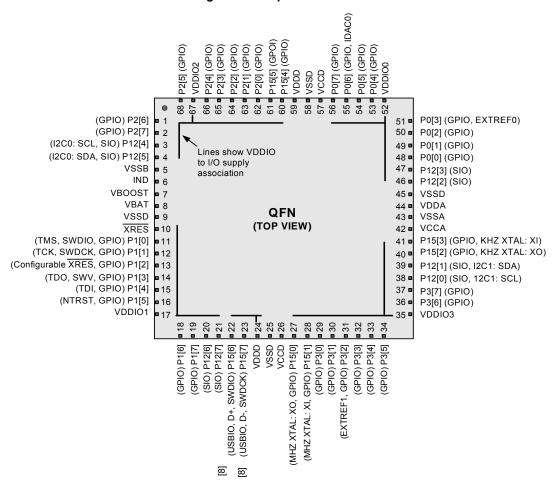

Figure 2-5. 68-pin QFN Part Pinout<sup>[7]</sup>

### Notes

The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices.

Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

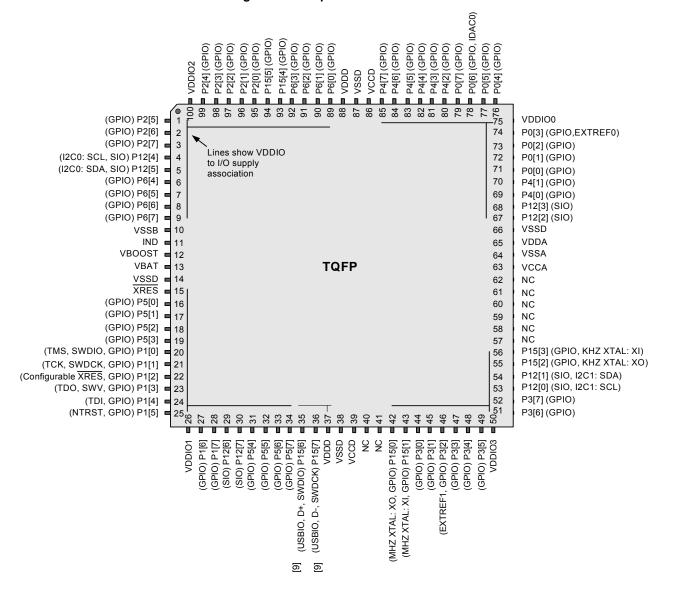

Figure 2-6. 100-pin TQFP Part Pinout

Table 2-1. VDDIO and Port Pin Associations

| VDDIO  | Port Pins                            |

|--------|--------------------------------------|

| VDDIO0 | P0[7:0], P4[7:0], P12[3:2]           |

| VDDIO1 | P1[7:0], P5[7:0], P12[7:6]           |

| VDDIO2 | P2[7:0], P6[7:0], P12[5:4], P15[5:4] |

| VDDIO3 | P3[7:0], P12[1:0], P15[3:0]          |

| VDDD   | P15[7:6] (USB D+, D-)                |

### Note

<sup>9.</sup> Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

Table 2-2 shows the pinout for the 72-pin CSP package. Since there are four  $V_{DDIO}$  pins, the set of I/O pins associated with any  $V_{DDIO}$  may sink up to 100 mA total, same as for the 100-pin and 68-pin devices.

Table 2-2. CSP Pinout

| Ball | Name   | Ball               | Name   | Ball | Name   |

|------|--------|--------------------|--------|------|--------|

| G6   | P2[5]  | F1                 | VDDD   | A5   | VDDA   |

| E5   | P2[6]  | E1                 | VSSD   | A6   | VSSD   |

| F5   | P2[7]  | E2                 | VCCD   | B6   | P12[2] |

| J7   | P12[4] | C1                 | P15[0] | C6   | P12[3] |

| H6   | P12[5] | C2                 | P15[1] | A7   | P0[0]  |

| J6   | VSSB   | D2                 | P3[0]  | B7   | P0[1]  |

| J5   | Ind    | D3                 | P3[1]  | B5   | P0[2]  |

| H5   | VBOOST | D4                 | P3[2]  | C5   | P0[3]  |

| J4   | VBAT   | D5                 | P3[3]  | A8   | VIO0   |

| H4   | VSSD   | B4                 | P3[4]  | D6   | P0[4]  |

| J3   | XRES_N | B3                 | P3[5]  | D7   | P0[5]  |

| H3   | P1[0]  | A1                 | VIO3   | C7   | P0[6]  |

| G3   | P1[1]  | B2                 | P3[6]  | C8   | P0[7]  |

| H2   | P1[2]  | A2                 | P3[7]  | E8   | VCCD   |

| J2   | P1[3]  | C3                 | P12[0] | F8   | VSSD   |

| G4   | P1[4]  | C4                 | P12[1] | G8   | VDDD   |

| G5   | P1[5]  | E3                 | P15[2] | E7   | P15[4] |

| J1   | VIO1   | E4                 | P15[3] | F7   | P15[5] |

| F4   | P1[6]  | B1 <sup>[10]</sup> | NC     | G7   | P2[0]  |

| F3   | P1[7]  | B8 <sup>[10]</sup> | NC     | H7   | P2[1]  |

| H1   | P12[6] | D1 <sup>[10]</sup> | NC     | H8   | P2[2]  |

| G1   | P12[7] | D8 <sup>[10]</sup> | NC     | F6   | P2[3]  |

| G2   | P15[6] | A3                 | VCCA   | E6   | P2[4]  |

| F2   | P15[7] | A4                 | VSSA   | J8   | VIO2   |

Figure 2-7 and Figure 2-8 show an example schematic and an example PCB layout, for the 100-pin TQFP part, for optimal analog performance on a two layer board.

- The two pins labeled VDDD must be connected together.

- The two pins labeled VCCD must be connected together, with capacitance added, as shown in Figure 2-7 and Power System on page 31. The trace between the two VCCD pins should be as short as possible.

- The two pins labeled VSSD must be connected together.

For information on circuit board layout issues for mixed signals, refer to the application note AN57821 - Mixed Signal Circuit Board Layout Considerations for PSoC® 3 and PSoC 5.

### Note

10. These pins are Do Not Use (DNU); they must be left floating.

Document Number: 001-56955 Rev. \*Y Page 10 of 128

### 4.4.2 DMA Features

- 24 DMA channels

- Each channel has one or more transaction descriptors (TDs) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64k bytes

- TDs may be nested and/or chained for complex transactions

### 4.4.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100 percent of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-7 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

Table 4-7. Priority Levels

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

### 4.4.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

### 4.4.4.1 Simple DMA

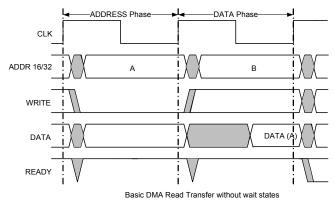

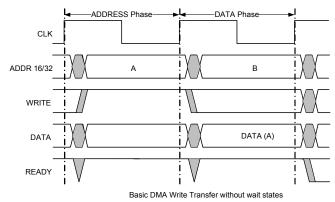

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles are shown in Figure 4-1. For more description on other transfer modes, refer to the Technical Reference Manual.

Figure 4-1. DMA Timing Diagram

### 4.4.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself.

### 4.4.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer to be filled by one client while another client is consuming the

data previously received in the other buffer. In its simplest form, this is done by chaining two TDs together so that each TD calls the opposite TD when complete.

### 4.4.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more than two buffers. In this case there are multiple TDs; after the last TD is complete it chains back to the first TD.

Table 4-8. Interrupt Vector Table

| #  | Fixed Function          | DMA               | UDB          |

|----|-------------------------|-------------------|--------------|

| 0  | LVD                     | phub_termout0[0]  | udb_intr[0]  |

| 1  | Cache/ECC               | phub_termout0[1]  | udb_intr[1]  |

| 2  | Reserved                | phub_termout0[2]  | udb_intr[2]  |

| 3  | Sleep (Pwr Mgr)         | phub_termout0[3]  | udb_intr[3]  |

| 4  | PICU[0]                 | phub_termout0[4]  | udb_intr[4]  |

| 5  | PICU[1]                 | phub_termout0[5]  | udb_intr[5]  |

| 6  | PICU[2]                 | phub_termout0[6]  | udb_intr[6]  |

| 7  | PICU[3]                 | phub_termout0[7]  | udb_intr[7]  |

| 8  | PICU[4]                 | phub_termout0[8]  | udb_intr[8]  |

| 9  | PICU[5]                 | phub_termout0[9]  | udb_intr[9]  |

| 10 | PICU[6]                 | phub_termout0[10] | udb_intr[10] |

| 11 | PICU[12]                | phub_termout0[11] | udb_intr[11] |

| 12 | PICU[15]                | phub_termout0[12] | udb_intr[12] |

| 13 | Comparators<br>Combined | phub_termout0[13] | udb_intr[13] |

| 14 | Reserved                | phub_termout0[14] | udb_intr[14] |

| 15 | I <sup>2</sup> C        | phub_termout0[15] | udb_intr[15] |

| 16 | Reserved                | phub_termout1[0]  | udb_intr[16] |

| 17 | Timer/Counter0          | phub_termout1[1]  | udb_intr[17] |

| 18 | Timer/Counter1          | phub_termout1[2]  | udb_intr[18] |

| 19 | Timer/Counter2          | phub_termout1[3]  | udb_intr[19] |

| 20 | Timer/Counter3          | phub_termout1[4]  | udb_intr[20] |

| 21 | USB SOF Int             | phub_termout1[5]  | udb_intr[21] |

| 22 | USB Arb Int             | phub_termout1[6]  | udb_intr[22] |

| 23 | USB Bus Int             | phub_termout1[7]  | udb_intr[23] |

| 24 | USB Endpoint[0]         | phub_termout1[8]  | udb_intr[24] |

| 25 | USB Endpoint Data       | phub_termout1[9]  | udb_intr[25] |

| 26 | Reserved                | phub_termout1[10] | udb_intr[26] |

| 27 | LCD                     | phub_termout1[11] | udb_intr[27] |

| 28 | Reserved                | phub_termout1[12] | udb_intr[28] |

| 29 | Decimator Int           | phub_termout1[13] | udb_intr[29] |

| 30 | PHUB Error Int          | phub_termout1[14] | udb_intr[30] |

| 31 | EEPROM Fault Int        | phub_termout1[15] | udb_intr[31] |

Document Number: 001-56955 Rev. \*Y

### 5.6 External Memory Interface

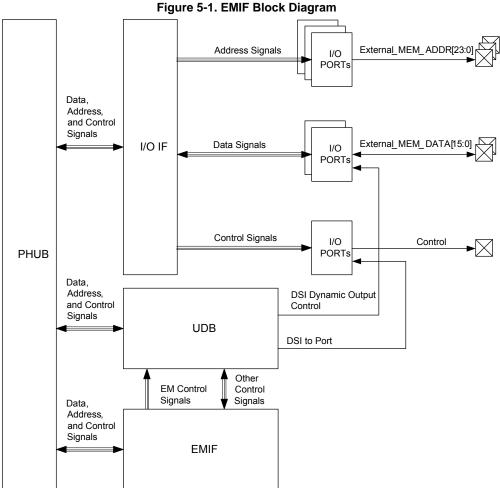

CY8C32 provides an external memory interface (EMIF) for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles.

Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C32 supports only one type of external memory device at a time.

External memory can be accessed via the 8051 xdata space; up to 24 address bits can be used. See "xdata Space" section on page 28. The memory can be 8 or 16 bits wide.

### 5.7 Memory Map

The CY8C32 8051 memory map is very similar to the MCS-51 memory map.

### 5.7.1 Code Space

The CY8C32 8051 code space is 64 KB. Only main flash exists in this space. See the "Flash Program Memory" section on page 24.

### 5.7.2 Internal Data Space

The CY8C32 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in Static RAM on page 24) and a 128-byte space for Special Function Registers (SFRs). See Figure 5-2. The lowest 32 bytes are used for 4 banks of registers R0-R7. The next 16 bytes are bit-addressable.

### 6.2.1 Power Modes

PSoC 3 devices have four different power modes, as shown in Table 6-2 and Table 6-3. The power modes allow a design to easily provide required functionality and processing power while simultaneously minimizing power consumption and maximizing battery life in low-power and portable devices.

PSoC 3 power modes, in order of decreasing power consumption are:

- Active

- Alternate Active

- Sleep

- Hibernate

Table 6-2. Power Modes

Active is the main processing mode. Its functionality is configurable. Each power controllable subsystem is enabled or disabled by using separate power configuration template registers. In alternate active mode, fewer subsystems are enabled, reducing power. In sleep mode most resources are disabled regardless of the template settings. Sleep mode is optimized to provide timed sleep intervals and RTC functionality. The lowest power mode is hibernate, which retains register and SRAM state, but no clocks, and allows wakeup only from I/O pins. Figure 6-5 illustrates the allowable transitions between power modes. Sleep and hibernate modes should not be entered until all VDDIO supplies are at valid voltage levels.

| <b>Power Modes</b>  | Description                                                                                                                                                                                                   | <b>Entry Condition</b>                     | Wakeup Source                                           | Active Clocks         | Regulator                                                                                                             |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|

| Active              | Primary mode of operation, all peripherals available (programmable)                                                                                                                                           | Wakeup, reset,<br>manual register<br>entry | Any interrupt                                           | Any<br>(programmable) | All regulators available. Digital and analog regulators can be disabled if external regulation used.                  |

| Alternate<br>Active | Similar to Active mode, and is<br>typically configured to have<br>fewer peripherals active to<br>reduce power. One possible<br>configuration is to use the UDBs<br>for processing, with the CPU<br>turned off | Manual register<br>entry                   | Any interrupt                                           | Any<br>(programmable) | All regulators available. Digital and analog regulators can be disabled if external regulation used.                  |

| Sleep               | All subsystems automatically disabled                                                                                                                                                                         | Manual register<br>entry                   | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | ILO/kHzECO            | Both digital and analog regulators buzzed. Digital and analog regulators can be disabled if external regulation used. |

| Hibernate           | All subsystems automatically disabled Lowest power consuming mode with all peripherals and internal regulators disabled, except hibernate regulator is enabled Configuration and memory contents retained     | Manual register<br>entry                   | PICU                                                    |                       | Only hibernate regulator active.                                                                                      |

Table 6-3. Power Modes Wakeup Time and Power Consumption

| Sleep<br>Modes      | Wakeup<br>Time | Current<br>(typ)       | Code<br>Execution | Digital<br>Resources | Analog<br>Resources | Clock Sources<br>Available | Wakeup Sources                                          | Reset<br>Sources  |

|---------------------|----------------|------------------------|-------------------|----------------------|---------------------|----------------------------|---------------------------------------------------------|-------------------|

| Active              | _              | 1.2 mA <sup>[11]</sup> | Yes               | All                  | All                 | All                        | _                                                       | All               |

| Alternate<br>Active | _              | -                      | User<br>defined   | All                  | All                 | All                        | -                                                       | All               |

| Sleep               | <15 µs         | 1 μΑ                   | No                | I <sup>2</sup> C     | Comparator          | ILO/kHzECO                 | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | XRES, LVD,<br>WDR |

| Hibernate           | <100 µs        | 200 nA                 | No                | None                 | None                | None                       | PICU                                                    | XRES              |

Document Number: 001-56955 Rev. \*Y

<sup>11.</sup> Bus clock off. Execute from cache at 6 MHz. See Table 11-2 on page 68.

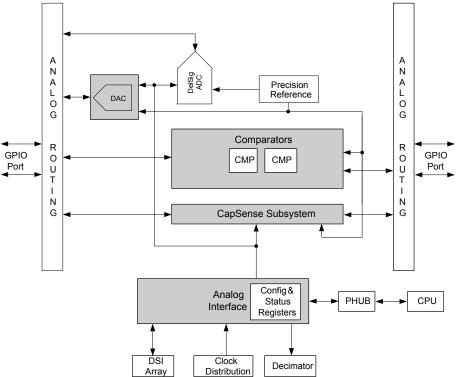

### 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

■ Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution delta-sigma ADC.

- One 8-bit DAC that provides either voltage or current output.

- Two comparators with optional connection to configurable LUT outputs.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

Figure 8-1. Analog Subsystem Block Diagram

The PSoC Creator software program provides a user friendly interface to configure the analog connections between the GPIO and various analog resources and connections from one analog resource to another. PSoC Creator also provides component libraries that allow you to configure the various analog blocks to perform application specific functions. The tool also generates API interface libraries that allow you to write firmware that allows the communication between the analog peripheral and CPU/Memory.

Document Number: 001-56955 Rev. \*Y Page 55 of 128

### 8.1 Analog Routing

The CY8C32 family of devices has a flexible analog routing architecture that provides the capability to connect GPIOs and different analog blocks, and also route signals between different analog blocks. One of the strong points of this flexible routing architecture is that it allows dynamic routing of input and output connections to the different analog blocks.

For information on how to make pin selections for optimal analog routing, refer to the application note, AN58304 - PSoC® 3 and PSoC® 5 - Pin Selection for Analog Designs.

### 8.1.1 Features

- Flexible, configurable analog routing architecture

- 16 analog globals (AG) and two analog mux buses (AMUXBUS) to connect GPIOs and the analog blocks

- Each GPIO is connected to one analog global and one analog mux bus

- Eight analog local buses (abus) to route signals between the different analog blocks

- Multiplexers and switches for input and output selection of the analog blocks

### 8.1.2 Functional Description

Analog globals (AGs) and analog mux buses (AMUXBUS) provide analog connectivity between GPIOs and the various analog blocks. There are 16 AGs in the CY8C32 family. The analog routing architecture is divided into four quadrants as shown in Figure 8-2. Each quadrant has four analog globals (AGL[0..3], AGL[4..7], AGR[0..3], AGR[4..7]). Each GPIO is connected to the corresponding AG through an analog switch. The analog mux bus is a shared routing resource that connects to every GPIO through an analog switch. There are two AMUXBUS routes in CY8C32, one in the left half (AMUXBUSL) and one in the right half (AMUXBUSR), as shown in Figure 8-2.

Document Number: 001-56955 Rev. \*Y Page 56 of 128

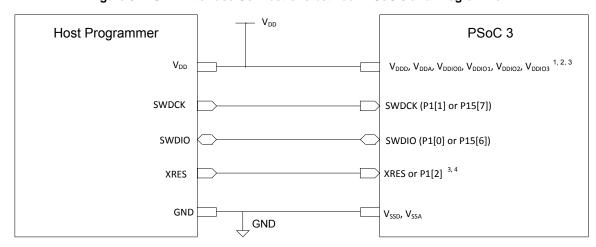

### 9.2 Serial Wire Debug Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D- pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8 µs (key window) after reset, that pin pair

(JTAG or USB) receives a predetermined acquire sequence of 1s and 0s. If the NVL latches are set for SWD (see *Section 5.5*), this sequence need not be applied to the JTAG pin pair. The acquire sequence must always be applied to the USB pin pair.

SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

Figure 9-2. SWD Interface Connections between PSoC 3 and Programmer

- The voltage levels of the Host Programmer and the PSoC 3 voltage domains involved in Programming should be the same. XRES pin (XRES\_N or P1[2]) is powered by V<sub>DDIO1</sub>. The USB SWD pins are powered by V<sub>DDD</sub>. So for Programming using the USB SWD pins with XRES pin, the V<sub>DDD</sub>, V<sub>DDIO1</sub> of PSoC 3 should be at the same voltage level as Host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDIO1</sub>. So V<sub>DDIO1</sub> of PSoC 3 should be at same voltage level as host V<sub>DD</sub> for Port 1 SWD programming. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDIO2</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer.

- Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

- For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48-pin devices, but use dedicated XRES pin for rest of devices.

Document Number: 001-56955 Rev. \*Y Page 64 of 128

Table 11-7. Recommended External Components for Boost Circuit

| Parameter          | Description                                                        | Conditions     | Min  | Тур  | Max  | Units |

|--------------------|--------------------------------------------------------------------|----------------|------|------|------|-------|

| L <sub>BOOST</sub> | Boost inductor                                                     | 4.7 μH nominal | 3.7  | 4.7  | 5.7  | μH    |

|                    |                                                                    | 10 μH nominal  | 8.0  | 10.0 | 12.0 | μH    |

|                    |                                                                    | 22 μH nominal  | 17.0 | 22.0 | 27.0 | μΗ    |

| C <sub>BOOST</sub> | Total capacitance sum of $V_{DDD}$ , $V_{DDA}$ , $V_{DDIO}^{[34]}$ |                | 17.0 | 26.0 | 31.0 | μF    |

| C <sub>BAT</sub>   | Battery filter capacitor                                           |                | 17.0 | 22.0 | 27.0 | μF    |

| l <sub>F</sub>     | Schottky diode average forward current                             |                | 1.0  | _    | 1    | Α     |

| V <sub>R</sub>     | Schottky reverse voltage                                           |                | 20.0 | _    | 1    | V     |

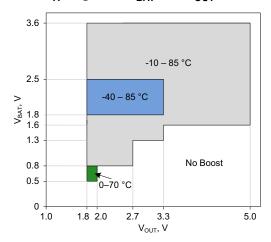

Figure 11-8.  $T_A$  range over  $V_{BAT}$  and  $V_{OUT}$

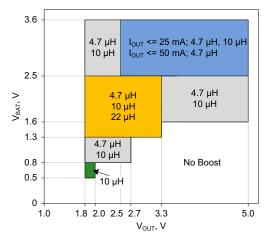

Figure 11-10.  $L_{\mbox{\footnotesize{BOOST}}}$  values over  $V_{\mbox{\footnotesize{BAT}}}$  and  $V_{\mbox{\footnotesize{OUT}}}$

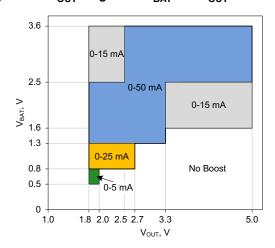

Figure 11-9.  $I_{OUT}$  range over  $V_{BAT}$  and  $V_{OUT}$

### Note

34. Based on device characterization (Not production tested).

### 11.4.2 SIO

### Table 11-11. SIO DC Specifications

| Parameter                                             | Description                                            | Conditions                                                                             | Min                     | Тур                                                                                                                                    | Max                                                                                                                                                               | Units |

|-------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Vinmax                                                | Maximum input voltage                                  | All allowed values of V <sub>DDIO</sub> and V <sub>DDD</sub> , see <i>Section 11.1</i> | -                       | _                                                                                                                                      | 5.5                                                                                                                                                               | V     |

| Vinref                                                | Input voltage reference (Differential input mode)      |                                                                                        | 0.5                     | -                                                                                                                                      | $0.52 \times V_{DDIO}$                                                                                                                                            | V     |

|                                                       | Output voltage reference (Regulat                      | red output mode)                                                                       |                         |                                                                                                                                        |                                                                                                                                                                   |       |

| Voutref                                               |                                                        | V <sub>DDIO</sub> > 3.7                                                                | 1                       | -                                                                                                                                      | V <sub>DDIO</sub> – 1                                                                                                                                             | V     |

|                                                       |                                                        | V <sub>DDIO</sub> < 3.7                                                                | 1                       | - V <sub>DDIO</sub> - 1 - V <sub>DDIO</sub> - 0.5 - V <sub>DDIO</sub> - 0.5 SIO_ref - 0.3 - SIO_ref + 0.3 - 0.4 - 0.4 - 0.4 - 0.4 - 14 | $V_{\rm DDIO} - 0.5$                                                                                                                                              | V     |

|                                                       | Input voltage high threshold                           |                                                                                        |                         |                                                                                                                                        |                                                                                                                                                                   |       |

| $V_{IH}$                                              | GPIO mode                                              | CMOS input                                                                             | $0.7 \times V_{DDIO}$   | -                                                                                                                                      | _                                                                                                                                                                 | V     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | SIO_ref + 0.2                                          | _                                                                                      | _                       | V                                                                                                                                      |                                                                                                                                                                   |       |

|                                                       | Input voltage low threshold                            |                                                                                        |                         |                                                                                                                                        |                                                                                                                                                                   |       |

| $V_{IL}$                                              | GPIO mode                                              | CMOS input                                                                             | _                       | _                                                                                                                                      | $0.3 \times V_{DDIO}$                                                                                                                                             | V     |

|                                                       | Differential input mode <sup>[39]</sup>                | Hysteresis disabled                                                                    | _                       | -                                                                                                                                      | SIO_ref - 0.2                                                                                                                                                     | V     |

|                                                       | Output voltage high                                    |                                                                                        |                         |                                                                                                                                        |                                                                                                                                                                   |       |

| V                                                     | Unregulated mode                                       | I <sub>OH</sub> = 4 mA, V <sub>DDIO</sub> = 3.3 V                                      | V <sub>DDIO</sub> – 0.4 | -                                                                                                                                      | _                                                                                                                                                                 | V     |

| $V_{OH}$                                              | Regulated mode <sup>[39]</sup>                         | I <sub>OH</sub> = 1 mA                                                                 | SIO_ref - 0.65          | -                                                                                                                                      | SIO_ref + 0.2                                                                                                                                                     | V     |

|                                                       | Regulated mode <sup>[39]</sup>                         | I <sub>OH</sub> = 0.1 mA                                                               | SIO_ref - 0.3           | _                                                                                                                                      | 5.5  0.52 × V <sub>DDIO</sub> V <sub>DDIO</sub> - 1  V <sub>DDIO</sub> - 0.5   0.3 × V <sub>DDIO</sub> SIO_ref - 0.2  SIO_ref + 0.2  0.8  0.4  0.4  8.5  8.5  8.5 | V     |

|                                                       | Output voltage low                                     | V <sub>DDIO</sub> = 3.30 V, I <sub>OL</sub> = 25 mA                                    | _                       | -                                                                                                                                      | 0.52 × V <sub>DDIO</sub> V <sub>DDIO</sub> - 1 V <sub>DDIO</sub> - 0.5                                                                                            | V     |

| $V_{OL}$                                              |                                                        | V <sub>DDIO</sub> = 3.30 V, I <sub>OL</sub> = 20 mA                                    | _                       | _                                                                                                                                      | 0.4                                                                                                                                                               | V     |

|                                                       |                                                        | V <sub>DDIO</sub> = 1.80 V, I <sub>OL</sub> = 4 mA                                     | _                       | _                                                                                                                                      | 0.4                                                                                                                                                               | V     |

| Rpullup                                               | Pull-up resistor                                       |                                                                                        | 3.5                     | 5.6                                                                                                                                    | 8.5                                                                                                                                                               | kΩ    |

| Rpulldown                                             | Pull-down resistor                                     |                                                                                        | 3.5                     | 5.6                                                                                                                                    | 8.5                                                                                                                                                               | kΩ    |

| I <sub>IL</sub>                                       | Input leakage current (absolute value) <sup>[40]</sup> |                                                                                        |                         |                                                                                                                                        |                                                                                                                                                                   |       |

|                                                       | V <sub>IH</sub> ≤ Vddsio                               | 25 °C, Vddsio = 3.0 V, V <sub>IH</sub> = 3.0 V                                         | _                       | -                                                                                                                                      | 14                                                                                                                                                                | nA    |

|                                                       | V <sub>IH</sub> > Vddsio                               | 25 °C, Vddsio = 0 V, V <sub>IH</sub> = 3.0 V                                           | _                       | _                                                                                                                                      | 10                                                                                                                                                                | μA    |

| C <sub>IN</sub>                                       | Input Capacitance <sup>[40]</sup>                      |                                                                                        | _                       | -                                                                                                                                      | 7                                                                                                                                                                 | pF    |

|                                                       | Input voltage hysteresis                               | Single ended mode (GPIO mode)                                                          | _                       | 40                                                                                                                                     | _                                                                                                                                                                 | mV    |

| VН                                                    | (Schmitt-Trigger) <sup>[40]</sup>                      | Differential mode                                                                      | _                       | 35                                                                                                                                     | _                                                                                                                                                                 | mV    |

| Idiode                                                | Current through protection diode to V <sub>SSIO</sub>  |                                                                                        | -                       | _                                                                                                                                      | 100                                                                                                                                                               | μΑ    |

Notes

39. See Figure 6-10 on page 40 and Figure 6-13 on page 43 for more information on SIO reference

40. Based on device characterization (Not production tested).

Table 11-13. SIO Comparator Specifications<sup>[42]</sup>

| Parameter | Description                    | Conditions                | Min | Тур | Max | Units |

|-----------|--------------------------------|---------------------------|-----|-----|-----|-------|

| Vos       | Offset voltage                 | V <sub>DDIO</sub> = 2 V   | _   | _   | 68  | mV    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | _   | _   | 72  |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | _   | _   | 82  |       |

| TCVos     | Offset voltage drift with temp |                           | -   | _   | 250 | μV/°C |

| CMRR      | Common mode rejection ratio    | V <sub>DDIO</sub> = 2 V   | 30  | _   | -   | dB    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | 35  | _   | _   |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | 40  | _   | _   | ]     |

| Tresp     | Response time                  |                           | -   | -   | 30  | ns    |

### 11.4.3 USBIO

For operation in GPIO mode, the standard range for  $V_{DDD}$  applies, see Device Level Specifications on page 68.

Table 11-14. USBIO DC Specifications

| Parameter            | Description                            | Conditions                                         | Min            | Тур | Max            | Units |

|----------------------|----------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi                | USB D+ pull-up resistance              | With idle bus                                      | 0.900          | _   | 1.575          | kΩ    |

| Rusba                | USB D+ pull-up resistance              | While receiving traffic                            | 1.425          | _   | 3.090          | kΩ    |

| Vohusb               | Static output high                     | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | _   | 3.6            | V     |

| Volusb               | Static output low                      | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | -              | _   | 0.3            | V     |

| Vohgpio              | Output voltage high, GPIO mode         | $I_{OH}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | 2.4            | _   | _              | V     |

| Volgpio              | Output voltage low, GPIO mode          | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | -              | _   | 0.3            | V     |

| Vdi                  | Differential input sensitivity         | (D+)-(D-)                                          | -              | _   | 0.2            | V     |

| Vcm                  | Differential input common mode range   | -                                                  | 0.8            | _   | 2.5            | V     |

| Vse                  | Single ended receiver threshold        | _                                                  | 0.8            | _   | 2              | V     |

| Rps2                 | PS/2 pull-up resistance                | In PS/2 mode, with PS/2 pull-up enabled            | 3              | _   | 7              | kΩ    |

| Rext                 | External USB series resistor           | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo                   | USB driver output impedance            | Including Rext                                     | 28             | _   | 44             | Ω     |

| C <sub>IN</sub>      | USB transceiver input capacitance      | _                                                  | -              | _   | 20             | pF    |

| I <sub>IL</sub> [42] | Input leakage current (absolute value) | 25 °C, V <sub>DDD</sub> = 3.0 V                    | -              | _   | 2              | nA    |

### Note

Document Number: 001-56955 Rev. \*Y

<sup>42.</sup> Based on device characterization (Not production tested).

### 11.5.5 Current Digital-to-analog Converter (IDAC)

All specifications are based on use of the low-resistance IDAC output pins (see Pin Descriptions on page 12 for details). See the IDAC component data sheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

Table 11-26. IDAC DC Specifications

| Parameter        | Description                           | Conditions                                                                                                                                                                                           | Min | Тур    | Max  | Units  |

|------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------|--------|

|                  | Resolution                            |                                                                                                                                                                                                      | -   | _      | 8    | bits   |

| I <sub>OUT</sub> | Output current at code = 255          | Range = 2.04 mA, code = 255, $V_{DDA} \ge 2.7$ V, Rload = 600 $\Omega$                                                                                                                               | -   | 2.04   | -    | mA     |

|                  |                                       | Range = 2.04 mA, high speed mode, code = 255, $V_{DDA} \le 2.7 \text{ V}$ , Rload = 300 $\Omega$                                                                                                     | -   | 2.04   | -    | mA     |

|                  |                                       | Range = 255 $\mu$ A, code = 255, Rload<br>= 600 $\Omega$                                                                                                                                             | _   | 255    | _    | μA     |

|                  |                                       | Range = 31.875 $\mu$ A, code = 255,<br>Rload = 600 $\Omega$                                                                                                                                          | _   | 31.875 | _    | μA     |

|                  | Monotonicity                          |                                                                                                                                                                                                      | -   | _      | Yes  |        |

| Ezs              | Zero scale error                      |                                                                                                                                                                                                      | _   | 0      | ±1   | LSB    |

| Eg               | Gain error                            | Range = 2.04 mA, 25 °C                                                                                                                                                                               | _   | _      | ±2.5 | %      |

|                  |                                       | Range = 255 μA, 25 ° C                                                                                                                                                                               | -   | _      | ±2.5 | %      |

|                  |                                       | Range = 31.875 μA, 25 ° C                                                                                                                                                                            | _   | _      | ±3.5 | %      |

| TC_Eg            | Temperature coefficient of gain error | Range = 2.04 mA                                                                                                                                                                                      | _   | _      | 0.04 | % / °C |

|                  |                                       | Range = 255 μA                                                                                                                                                                                       | _   | _      | 0.04 | % / °C |

|                  |                                       | Range = 31.875 μA                                                                                                                                                                                    | _   | _      | 0.05 | % / °C |

| INL              | Integral nonlinearity                 | Sink mode, range = 255 $\mu$ A, Codes 8 – 255, Rload = 2.4 $k\Omega$ , Cload = 15 pF                                                                                                                 | _   | ±0.9   | ±1   | LSB    |

|                  |                                       | Source mode, range = 255 $\mu$ A,<br>Codes 8 – 255, Rload = 2.4 $k\Omega$ ,<br>Cload = 15 pF                                                                                                         | _   | ±1.2   | ±1.6 | LSB    |

| DNL              | Differential nonlinearity             | Sink mode, range = 255 μA, Rload<br>= 2.4 kΩ, Cload = 15 pF                                                                                                                                          | _   | ±0.3   | ±1   | LSB    |

|                  |                                       | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 $k\Omega$ , Cload = 15 pF                                                                                                                           | -   | ±0.3   | ±1   | LSB    |

| Vcompliance      | Dropout voltage, source or sink mode  | $ \begin{array}{c} \text{Voltage headroom at max current,} \\ \text{Rload to V}_{\text{DDA}} \text{ or Rload to V}_{\text{SSA}}, \\ \text{V}_{\text{DIFF}} \text{ from V}_{\text{DDA}} \end{array} $ | 1   | _      | -    | V      |

Document Number: 001-56955 Rev. \*Y Page 87 of 128

### 11.6 Digital Peripherals

Specifications are valid for  $-40~^{\circ}C \le T_{A} \le 85~^{\circ}C$  and  $T_{J} \le 100~^{\circ}C$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

### 11.6.1 Timer

The following specifications apply to the Timer/Counter/PWM peripheral in timer mode. Timers can also be implemented in UDBs; for more information, see the Timer component datasheet in PSoC Creator.

Table 11-33. Timer DC Specifications

| Parameter | Description               | Conditions                                    | Min | Тур | Max | Units |

|-----------|---------------------------|-----------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit timer, at listed input clock frequency | _   | _   | _   | μA    |

|           | 3 MHz                     |                                               | _   | 15  | _   | μA    |

|           | 12 MHz                    |                                               | _   | 60  | _   | μA    |

|           | 50 MHz                    |                                               | -   | 260 | -   | μA    |

### Table 11-34. Timer AC Specifications

| Parameter | Description                    | Conditions | Min | Тур | Max   | Units |

|-----------|--------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency            |            | DC  | _   | 50.01 | MHz   |

|           | Capture pulse width (Internal) |            | 21  | _   | _     | ns    |

|           | Capture pulse width (external) |            | 42  | _   | -     | ns    |

|           | Timer resolution               |            | 21  | -   | -     | ns    |

|           | Enable pulse width             |            | 21  | _   | _     | ns    |

|           | Enable pulse width (external)  |            | 42  | _   | -     | ns    |

|           | Reset pulse width              |            | 21  | _   | _     | ns    |

|           | Reset pulse width (external)   |            | 42  | _   | _     | ns    |

### 11.6.2 Counter

The following specifications apply to the Timer/Counter/PWM peripheral, in counter mode. Counters can also be implemented in UDBs; for more information, see the Counter component datasheet in PSoC Creator.

Table 11-35. Counter DC Specifications

| Parameter | Description               | Conditions                                      | Min | Тур | Max | Units |

|-----------|---------------------------|-------------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit counter, at listed input clock frequency | -   | _   | -   | μA    |

|           | 3 MHz                     |                                                 | ı   | 15  | _   | μΑ    |

|           | 12 MHz                    |                                                 | _   | 60  | _   | μA    |

|           | 50 MHz                    |                                                 | _   | 260 | _   | μA    |

### Table 11-36. Counter AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max   | Units |

|-----------|-------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency           |            | DC  | _   | 50.01 | MHz   |

|           | Capture pulse                 |            | 21  | -   | _     | ns    |

|           | Resolution                    |            | 21  | _   | _     | ns    |

|           | Pulse width                   |            | 21  | -   | _     | ns    |

|           | Pulse width (external)        |            | 42  | -   | -     | ns    |

|           | Enable pulse width            |            | 21  | _   | _     | ns    |

|           | Enable pulse width (external) |            | 42  | -   | _     | ns    |

|           | Reset pulse width             |            | 21  | -   | -     | ns    |

|           | Reset pulse width (external)  |            | 42  | _   | _     | ns    |

Document Number: 001-56955 Rev. \*Y Page 96 of 128

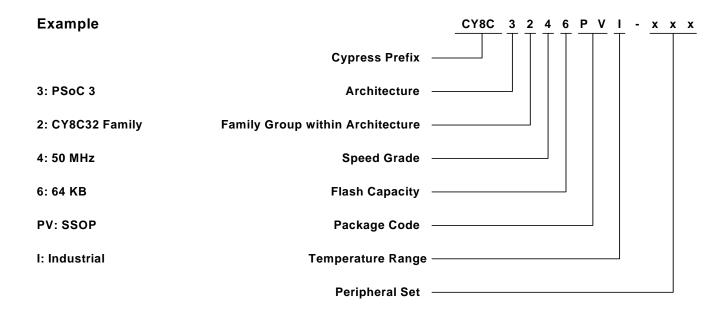

### 12.1 Part Numbering Conventions

PSoC 3 devices follow the part numbering convention described here. All fields are single character alphanumeric (0, 1, 2, ..., 9, A, B, ..., Z) unless stated otherwise.

CY8Cabcdefg-xxx

■ a: Architecture

■ 3: PSoC 3 □ 5: PSoC 5

■ b: Family group within architecture

□ 2: CY8C32 family

□ 4: CY8C34 family

□ 6: CY8C36 family

■ 8: CY8C38 family

■ c: Speed grade

■ 4: 50 MHz

□ 6: 67 MHz

■ d: Flash capacity

□ 4: 16 KB

□ 5: 32 KB

□ 6: 64 KB

■ ef: Package code

Two character alphanumeric

■ AX: TQFP LT: QFN

□ PV: SSOP

□ FN: CSP

■ g: Temperature range

□ C: commercial

□ I: industrial

■ A: automotive

■ xxx: Peripheral set

□ Three character numeric

■ No meaning is associated with these three characters.

Tape and reel versions of these devices are available and are marked with a "T" at the end of the part number.

All devices in the PSoC 3 CY8C32 family comply to RoHS-6 specifications, demonstrating the commitment by Cypress to lead-free products. Lead (Pb) is an alloying element in solders that has resulted in environmental concerns due to potential toxicity. Cypress uses nickel-palladium-gold (NiPdAu) technology for the majority of leadframe-based packages.

A high level review of the Cypress Pb-free position is available on our website. Specific package information is also available. Package Material Declaration Datasheets (PMDDs) identify all substances contained within Cypress packages. PMDDs also confirm the absence of many banned substances. The information in the PMDDs will help Cypress customers plan for recycling or other "end of life" requirements.

## 13. Packaging

**Table 13-1. Package Characteristics**

| Parameter      | Description                            | Conditions | Min | Тур   | Max | Units   |

|----------------|----------------------------------------|------------|-----|-------|-----|---------|

| T <sub>A</sub> | Operating ambient temperature          |            | -40 | 25.00 | 85  | °C      |

| $T_J$          | Operating junction temperature         |            | -40 | _     | 100 | °C      |

| $T_{JA}$       | Package θ <sub>JA</sub> (48-pin SSOP)  |            | -   | 49    | -   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (48-pin QFN)   |            | -   | 14    | _   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (68-pin QFN)   |            | -   | 15    | -   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (100-pin TQFP) |            | _   | 34    | _   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (48-pin SSOP)  |            | -   | 24    | _   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (48-pin QFN)   |            | -   | 15    | -   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (68-pin QFN)   |            | -   | 13    | _   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (100-pin TQFP) |            | -   | 10    | _   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (72-pin CSP)   |            | -   | 18    | _   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (72-pin CSP)   |            | _   | 0.13  | -   | °C/Watt |

Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at Peak<br>Temperature |

|--------------|-----------------------------|-------------------------------------|

| 48-pin SSOP  | 260 °C                      | 30 seconds                          |

| 48-pin QFN   | 260 °C                      | 30 seconds                          |

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

| 72-pin CSP   | 260 °C                      | 30 seconds                          |

Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 3 |

| 48-pin QFN   | MSL 3 |

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

| 72-pin CSP   | MSL 1 |

Document Number: 001-56955 Rev. \*Y Page 113 of 128

|          | Description Title: PSoC® 3: CY8C32 Family Data Sheet Programmable System-on-Chip (PSoC®) (continued) Document Number: 001-56955 |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision | ECN                                                                                                                             | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| *X       | 4932879                                                                                                                         | 09/24/2015         | MKEA               | Changed the Regulator Output Capacitor min and max from "-" to 0.9 and 1.1, respectively.  Added reference to AN54439 in Section 11.9.3.  Added MHz ECO DC specs table.  Removed references to IPOR rearm issues in Section 6.3.1.1.  Table 6-1: Changed DSI Fmax to 33 MHz.  Figure 6-1: Changed External I/O or DSI to 0-33 MHz.  Table 11-10: Changed Fgpioin Max to 33 MHz.  Table 11-12: Changed Fsioin Max to 33 MHz. |  |  |

| *Y       | 5322536                                                                                                                         | 06/27/2016         | MKEA               | Updated More Information. Corrected typos in External Electrical Connections. Added links to CAD Libraries in Section 2.                                                                                                                                                                                                                                                                                                    |  |  |

Document Number: 001-56955 Rev. \*Y Page 127 of 128

### 18. Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### **Products**

Automotive Clocks & Buffers Interface

Lighting & Power Control

Memory PSoC

Touch Sensing

USB Controllers

Wireless/RF

cypress.com/go/automotive cypress.com/go/clocks cypress.com/go/interface cypress.com/go/powerpsoc cypress.com/go/memory cypress.com/go/psoc cypress.com/go/touch cypress.com/go/USB cypress.com/go/wireless

### PSoC® Solutions

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

### **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

### **Technical Support**

cypress.com/go/support

© Cypress Semiconductor Corporation, 2009-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, copyrights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems of the medical devices or systems (including resuscitation equipment and surjoical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 001-56955 Rev. \*Y Revised June 27, 2016 Page 128 of 128