#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 68-QFN (8×8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3246lti-149 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Contents

| 1. Architectural Overview             | 4  |

|---------------------------------------|----|

| 2. Pinouts                            | 6  |

| 3. Pin Descriptions                   | 12 |

| 4. CPU                                | 13 |

| 4.1 8051 CPU                          | 13 |

| 4.2 Addressing Modes                  |    |

| 4.3 Instruction Set                   |    |

| 4.4 DMA and PHUB                      |    |

| 4.5 Interrupt Controller              | 20 |

| 5. Memory                             | 24 |

| 5.1 Static RAM                        | 24 |

| 5.2 Flash Program Memory              | 24 |

| 5.3 Flash Security                    |    |

| 5.4 EEPROM                            |    |

| 5.5 Nonvolatile Latches (NVLs)        |    |

| 5.6 External Memory Interface         |    |

| 5.7 Memory Map                        |    |

| 6. System Integration                 |    |

| 6.1 Clocking System                   |    |

| 6.2 Power System                      |    |

| 6.3 Reset                             |    |

| 6.4 I/O System and Routing            |    |

| 7. Digital Subsystem                  |    |

| 7.1 Example Peripherals               |    |

| 7.2 Universal Digital Block           |    |

| 7.3 UDB Array Description             |    |

| 7.4 DSI Routing Interface Description |    |

| 7.5 USB                               |    |

| 7.6 Timers, Counters, and PWMs        |    |

| 7.7 l <sup>2</sup> C                  |    |

| 8. Analog Subsystem                   |    |

| 8.1 Analog Routing                    |    |

| 8.2 Delta-sigma ADC                   |    |

| 8.3 Comparators                       |    |

| 8.4 LCD Direct Drive<br>8.5 CapSense  |    |

| 8.6 Temp Sensor                       |    |

| 8.7 DAC                               |    |

|                                       | 01 |

| 9. Programming, Debug Interfaces, Resources      |     |

|--------------------------------------------------|-----|

| 9.1 JTAG Interface                               |     |

| 9.2 Serial Wire Debug Interface                  |     |

| 9.3 Debug Features<br>9.4 Trace Features         |     |

| 9.5 Single Wire Viewer Interface                 |     |

| 9.6 Programming Features                         |     |

| 9.7 Device Security                              |     |

| 9.8 CSP Package Bootloader                       |     |

| 10. Development Support                          | 66  |

| 10.1 Documentation                               |     |

| 10.2 Online                                      |     |

| 10.3 Tools                                       |     |

| 11. Electrical Specifications                    |     |

| 11.1 Absolute Maximum Ratings                    |     |

| 11.2 Device Level Specifications                 |     |

| 11.3 Power Regulators<br>11.4 Inputs and Outputs |     |

| 11.5 Analog Peripherals                          |     |

| 11.6 Digital Peripherals                         |     |

| 11.7 Memory                                      |     |

| 11.8 PSoC System Resources                       |     |

| 11.9 Clocking                                    | 107 |

| 12. Ordering Information                         |     |

| 12.1 Part Numbering Conventions                  |     |

| 13. Packaging                                    | 113 |

| 14. Acronyms                                     | 117 |

| 15. Reference Documents                          | 118 |

| 16. Document Conventions                         | 119 |

| 16.1 Units of Measure                            | 119 |

| 17. Revision History                             | 120 |

| 18. Sales, Solutions, and Legal Information      | 128 |

| Worldwide Sales and Design Support               |     |

| Products                                         |     |

| PSoC® Solutions                                  |     |

| Cypress Developer Community                      |     |

| Technical Support                                | 128 |

This enables the device to be powered directly from a single battery or solar cell. In addition, you can use the boost converter to generate other voltages required by the device, such as a 3.3-V supply for LCD glass drive. The boost's output is available on the V<sub>BOOST</sub> pin, allowing other devices in the application to be powered from the PSoC.

PSoC supports a wide range of low-power modes. These include a 200-nA hibernate mode with RAM retention and a  $1-\mu$ A sleep mode with RTC. In the second mode the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC.

Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low-power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 1.2 mA when the CPU is running at 6 MHz, or 0.8 mA running at 3 MHz.

The details of the PSoC power modes are covered in the "Power System" section on page 31 of this datasheet.

PSoC uses JTAG (4-wire) or SWD (2-wire) interfaces for programming, debug, and test. The 1-wire SWV may also be used for "printf" style debugging. By combining SWD and SWV, you can implement a full debugging interface with just three pins. Using these standard interfaces enables you to debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. PSoC supports on-chip break points and 4-KB instruction and data race memory for debug. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 62 of this datasheet.

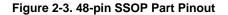

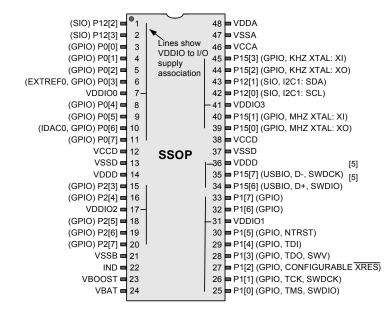

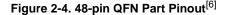

## 2. Pinouts

Each VDDIO pin powers a specific set of I/O pins. (The USBIOs are powered from VDDD.) Using the VDDIO pins, a single PSoC can support multiple voltage levels, reducing the need for off-chip level shifters. The black lines drawn on the pinout diagrams in Figure 2-3 through Figure 2-6, as well as Table 2-1, show the pins that are powered by each VDDIO.

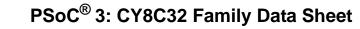

Each VDDIO may source up to 100 mA total to its associated I/O pins, as shown in Figure 2-1.

#### Figure 2-1. VDDIO Current Limit

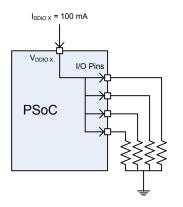

Conversely, for the 100-pin and 68-pin devices, the set of I/O pins associated with any VDDIO may sink up to 100 mA total, as shown in Figure 2-2.

#### Figure 2-2. I/O Pins Current Limit

For the 48-pin devices, the set of I/O pins associated with VDDIO0 plus VDDIO2 may sink up to 100 mA total. The set of I/O pins associated with VDDIO1 plus VDDIO3 may sink up to a total of 100 mA.

Notes

- 5. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

- The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices.

Table 2-2 shows the pinout for the 72-pin CSP package. Since there are four  $V_{DDIO}$  pins, the set of I/O pins associated with any  $V_{DDIO}$  may sink up to 100 mA total, same as for the 100-pin and 68-pin devices.

| Table 2-2. | COD | Dinout |

|------------|-----|--------|

| Table Z-Z. | LOP | Pinout |

| Ball | Name   | Ball               | Name   | Ball | Name   |

|------|--------|--------------------|--------|------|--------|

| G6   | P2[5]  | F1                 | VDDD   | A5   | VDDA   |

| E5   | P2[6]  | E1                 | VSSD   | A6   | VSSD   |

| F5   | P2[7]  | E2                 | VCCD   | B6   | P12[2] |

| J7   | P12[4] | C1                 | P15[0] | C6   | P12[3] |

| H6   | P12[5] | C2                 | P15[1] | A7   | P0[0]  |

| J6   | VSSB   | D2                 | P3[0]  | B7   | P0[1]  |

| J5   | Ind    | D3                 | P3[1]  | B5   | P0[2]  |

| H5   | VBOOST | D4                 | P3[2]  | C5   | P0[3]  |

| J4   | VBAT   | D5                 | P3[3]  | A8   | VIO0   |

| H4   | VSSD   | B4                 | P3[4]  | D6   | P0[4]  |

| J3   | XRES_N | B3                 | P3[5]  | D7   | P0[5]  |

| H3   | P1[0]  | A1                 | VIO3   | C7   | P0[6]  |

| G3   | P1[1]  | B2                 | P3[6]  | C8   | P0[7]  |

| H2   | P1[2]  | A2                 | P3[7]  | E8   | VCCD   |

| J2   | P1[3]  | C3                 | P12[0] | F8   | VSSD   |

| G4   | P1[4]  | C4                 | P12[1] | G8   | VDDD   |

| G5   | P1[5]  | E3                 | P15[2] | E7   | P15[4] |

| J1   | VIO1   | E4                 | P15[3] | F7   | P15[5] |

| F4   | P1[6]  | B1 <sup>[10]</sup> | NC     | G7   | P2[0]  |

| F3   | P1[7]  | B8 <sup>[10]</sup> | NC     | H7   | P2[1]  |

| H1   | P12[6] | D1 <sup>[10]</sup> | NC     | H8   | P2[2]  |

| G1   | P12[7] | D8 <sup>[10]</sup> | NC     | F6   | P2[3]  |

| G2   | P15[6] | A3                 | VCCA   | E6   | P2[4]  |

| F2   | P15[7] | A4                 | VSSA   | J8   | VIO2   |

Figure 2-7 and Figure 2-8 show an example schematic and an example PCB layout, for the 100-pin TQFP part, for optimal analog performance on a two layer board.

- The two pins labeled VDDD must be connected together.

- The two pins labeled VCCD must be connected together, with capacitance added, as shown in Figure 2-7 and Power System on page 31. The trace between the two VCCD pins should be as short as possible.

- The two pins labeled VSSD must be connected together.

For information on circuit board layout issues for mixed signals, refer to the application note AN57821 - Mixed Signal Circuit Board Layout Considerations for PSoC® 3 and PSoC 5.

## 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2Table 4-2 on page 15 shows the list of logical instructions and their description.

#### Table 4-2. Logical Instructions

|     | Mnemonic      | Description                             | Bytes | Cycles |

|-----|---------------|-----------------------------------------|-------|--------|

| ANL | A,Rn          | AND register to accumulator             | 1     | 1      |

| ANL | A,Direct      | AND direct byte to accumulator          | 2     | 2      |

| ANL | A,@Ri         | AND indirect RAM to accumulator         | 1     | 2      |

| ANL | A,#data       | AND immediate data to accumulator       | 2     | 2      |

| ANL | Direct, A     | AND accumulator to direct byte          | 2     | 3      |

| ANL | Direct, #data | AND immediate data to direct byte       | 3     | 3      |

| ORL | A,Rn          | OR register to accumulator              | 1     | 1      |

| ORL | A,Direct      | OR direct byte to accumulator           | 2     | 2      |

| ORL | A,@Ri         | OR indirect RAM to accumulator          | 1     | 2      |

| ORL | A,#data       | OR immediate data to accumulator        | 2     | 2      |

| ORL | Direct, A     | OR accumulator to direct byte           | 2     | 3      |

| ORL | Direct, #data | OR immediate data to direct byte        | 3     | 3      |

| XRL | A,Rn          | XOR register to accumulator             | 1     | 1      |

| XRL | A,Direct      | XOR direct byte to accumulator          | 2     | 2      |

| XRL | A,@Ri         | XOR indirect RAM to accumulator         | 1     | 2      |

| XRL | A,#data       | XOR immediate data to accumulator       | 2     | 2      |

| XRL | Direct, A     | XOR accumulator to direct byte          | 2     | 3      |

| XRL | Direct, #data | XOR immediate data to direct byte       | 3     | 3      |

| CLR | А             | Clear accumulator                       | 1     | 1      |

| CPL | А             | Complement accumulator                  | 1     | 1      |

| RL  | А             | Rotate accumulator left                 | 1     | 1      |

| RLC | A             | Rotate accumulator left through carry 1 |       | 1      |

| RR  | А             | Rotate accumulator right                | 1     | 1      |

| RRC | А             | Rotate accumulator right though carry   | 1     | 1      |

| SWA | PA            | Swap nibbles within accumulator         | 1     | 1      |

#### 4.3.1.5 Program Branching Instructions

The 8051 supports a set of conditional and unconditional jump instructions that help to modify the program execution flow. Table 4-5 shows the list of jump instructions.

#### Table 4-5. Jump Instructions

| Mnemonic             | Description                                                  | Bytes | Cycles |

|----------------------|--------------------------------------------------------------|-------|--------|

| ACALL addr11         | Absolute subroutine call                                     | 2     | 4      |

| LCALL addr16         | Long subroutine call                                         | 3     | 4      |

| RET                  | Return from subroutine                                       | 1     | 4      |

| RETI                 | Return from interrupt                                        | 1     | 4      |

| AJMP addr11          | Absolute jump                                                | 2     | 3      |

| LJMP addr16          | Long jump                                                    | 3     | 4      |

| SJMP rel             | Short jump (relative address)                                | 2     | 3      |

| JMP @A + DPTR        | Jump indirect relative to DPTR                               | 1     | 5      |

| JZ rel               | Jump if accumulator is zero                                  | 2     | 4      |

| JNZ rel              | Jump if accumulator is nonzero                               | 2     | 4      |

| CJNE A, Direct, rel  | Compare direct byte to accumulator and jump if not equal     | 3     | 5      |

| CJNE A, #data, rel   | Compare immediate data to accumulator and jump if not equal  | 3     | 4      |

| CJNE Rn, #data, rel  | Compare immediate data to register and jump if not equal     | 3     | 4      |

| CJNE @Ri, #data, rel | Compare immediate data to indirect RAM and jump if not equal | 3     | 5      |

| DJNZ Rn,rel          | Decrement register and jump if not zero                      | 2     | 4      |

| DJNZ Direct, rel     | Decrement direct byte and jump if not zero                   | 3     | 5      |

| NOP                  | No operation                                                 | 1     | 1      |

#### 4.4 DMA and PHUB

The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of:

- A central hub that includes the DMA controller, arbiter, and router

- Multiple spokes that radiate outward from the hub to most peripherals

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

## 4.4.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight Multi-layer AHB Bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8, 16, 24, and 32-bit addressing and data

#### Table 4-6. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, USB, I <sup>2</sup> C, Timers, Counters, and PWMs                                              |

| 5           | Reserved                                                                                            |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

#### 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2.

Table 5-2.

Device Configuration NVL Register Map

| Register Address | 7       | 6         | 5                         | 4 | 3                           | 2        | 1         | 0        |

|------------------|---------|-----------|---------------------------|---|-----------------------------|----------|-----------|----------|

| 0x00             | PRT3RE  | DM[1:0]   | PRT2RDM[1:0] PRT1RDM[1:0] |   | PRT0                        | RDM[1:0] |           |          |

| 0x01             | PRT12R  | DM[1:0]   | PRT6RDM[1:0] PRT5RDM[1:0] |   | PRT6RDM[1:0] PRT5RDM[1:0] P |          | PRT4      | RDM[1:0] |

| 0x02             | XRESMEN | DBGEN     |                           |   |                             | PRT18    | 5RDM[1:0] |          |

| 0x03             |         | DIG_PHS_I | DLY[3:0]                  |   | ECCEN                       | DPS      | [1:0]     |          |

The details for individual fields and their factory default settings are shown in Table 5-3:.

#### Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                                        | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     | Controls reset drive mode of the corresponding IO port.<br>See "Reset Configuration" on page 44. All pins of the<br>port are set to the same mode. | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as an external reset. See "Pin Descriptions" on page 12, XRES description.                         | 0 (default for 68-pin 72-pin, and 100-pin parts) - GPIO<br>1 (default for 48-pin parts) - external reset                      |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                                       | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| DPS[1:0]         |                                                                                                                                                    | 00b - 5-wire JTAG<br>01b (default) - 4-wire JTAG<br>10b - SWD<br>11b - debug ports disabled                                   |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 24.                   | 0 - ECC disabled<br>1 (default) - ECC enabled                                                                                 |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                                             | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase / write cycles is limited – see "Nonvolatile Latches (NVL))" on page 100.

#### 5.6 External Memory Interface

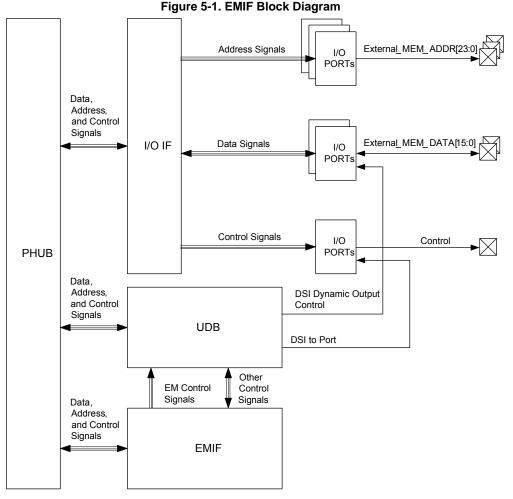

CY8C32 provides an external memory interface (EMIF) for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles. Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C32 supports only one type of external memory device at a time.

External memory can be accessed via the 8051 xdata space; up to 24 address bits can be used. See "xdata Space" section on page 28. The memory can be 8 or 16 bits wide.

#### 5.7 Memory Map

The CY8C32 8051 memory map is very similar to the MCS-51 memory map.

#### 5.7.1 Code Space

The CY8C32 8051 code space is 64 KB. Only main flash exists in this space. See the "Flash Program Memory" section on page 24.

#### 5.7.2 Internal Data Space

The CY8C32 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in Static RAM on page 24) and a 128-byte space for Special Function Registers (SFRs). See Figure 5-2. The lowest 32 bytes are used for 4 banks of registers R0-R7. The next 16 bytes are bit-addressable.

#### Table 6-1. Oscillator Summary

| Source  | Fmin   | Tolerance at Fmin                | Fmax    | Tolerance at Fmax | Startup Time                            |

|---------|--------|----------------------------------|---------|-------------------|-----------------------------------------|

| IMO     | 3 MHz  | ±2% over voltage and temperature | 24 MHz  | ±4%               | 13-µs max                               |

| MHzECO  | 4 MHz  | Crystal dependent                | 25 MHz  | Crystal dependent | 5 ms typ, max is<br>crystal dependent   |

| DSI     | 0 MHz  | Input dependent                  | 33 MHz  | Input dependent   | Input dependent                         |

| PLL     | 24 MHz | Input dependent                  | 50 MHz  | Input dependent   | 250 µs max                              |

| Doubler | 48 MHz | Input dependent                  | 48 MHz  | Input dependent   | 1 µs max                                |

| ILO     | 1 kHz  | -50%, +100%                      | 100 kHz | -55%, +100%       | 15 ms max in lowest power mode          |

| kHzECO  | 32 kHz | Crystal dependent                | 32 kHz  | Crystal dependent | 500 ms typ, max is<br>crystal dependent |

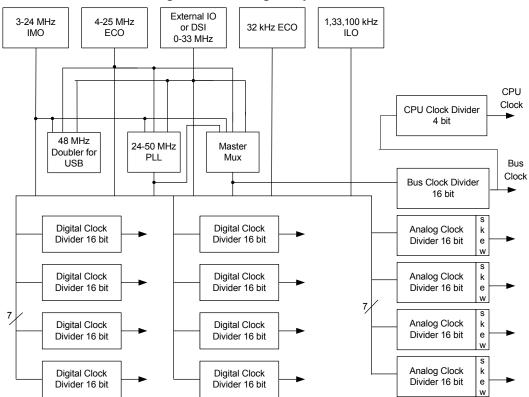

Figure 6-1. Clocking Subsystem

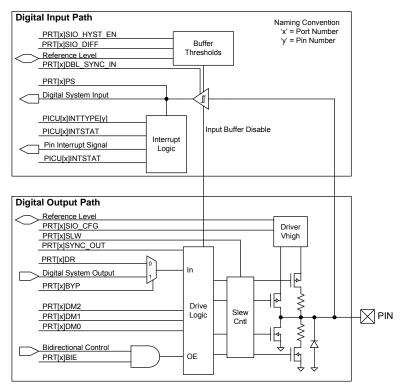

#### Figure 6-10. SIO Input/Output Block Diagram

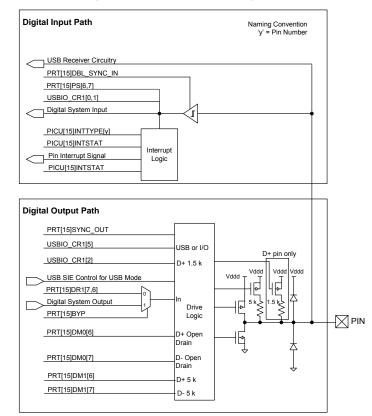

Figure 6-11. USBIO Block Diagram

The USBIO pins (P15[7] and P15[6]), when enabled for I/O mode, have limited drive mode control. The drive mode is set using the PRT15.DM0[7, 6] register. A resistive pull option is also available at the USBIO pins, which can be enabled using the PRT15.DM1[7, 6] register. When enabled for USB mode, the drive mode control has no impact on the configuration of the USB pins. Unlike the GPIO and SIO configurations, the port wide configuration registers do not configure the USB drive mode bits. Table 6-7 shows the drive mode configuration for the USBIO pins.

| PRT15.DM1[7,6]<br>Pull up enable | PRT15.DM0[7,6]<br>Drive Mode enable | PRT15.DR[7,6] = 1 | PRT15.DR[7,6] = 0 | Description                   |

|----------------------------------|-------------------------------------|-------------------|-------------------|-------------------------------|

| 0                                | 0                                   | High Z            | Strong Low        | Open Drain, Strong Low        |

| 0                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

| 1                                | 0                                   | Res High (5k)     | Strong Low        | Resistive Pull Up, Strong Low |

| 1                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

## Table 6-7. USBIO Drive Modes (P15[7] and P15[6])

#### High Impedance Analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

High Impedance Digital

The input buffer is enabled for digital signal input. This is the standard high impedance (HiZ) state recommended for digital inputs.

Resistive pull-up or resistive pull-down

Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

Open Drain, Drives High and Open Drain, Drives Low

Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the  $I^2C$  bus signal lines.

Strong Drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

Resistive pull-up and pull-down

Similar to the resistive pull-up and resistive pull-down modes except the pin is always in series with a resistor. The high data state is pull-up while the low data state is pull-down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

#### 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

#### 6.4.3 Bidirectional Mode

High-speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRT×DM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

#### 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRT×SLW registers.

#### 7.1.4 Designing with PSoC Creator

#### 7.1.4.1 More Than a Typical IDE

A successful design tool allows for the rapid development and deployment of both simple and complex designs. It reduces or eliminates any learning curve. It makes the integration of a new design into the production stream straightforward.

PSoC Creator is that design tool.

PSoC Creator is a full featured Integrated Development Environment (IDE) for hardware and software design. It is optimized specifically for PSoC devices and combines a modern, powerful software development platform with a sophisticated graphical design tool. This unique combination of tools makes PSoC Creator the most flexible embedded design platform available.

Graphical design entry simplifies the task of configuring a particular part. You can select the required functionality from an extensive catalog of components and place it in your design. All components are parameterized and have an editor dialog that allows you to tailor functionality to your needs.

PSoC Creator automatically configures clocks and routes the I/O to the selected pins and then generates APIs to give the application complete control over the hardware. Changing the PSoC device configuration is as simple as adding a new component, setting its parameters, and rebuilding the project.

At any stage of development you are free to change the hardware configuration and even the target processor. To retarget your application (hardware and software) to new devices, even from 8- to 32-bit families, just select the new device and rebuild.

You also have the ability to change the C compiler and evaluate an alternative. Components are designed for portability and are validated against all devices, from all families, and against all supported tool chains. Switching compilers is as easy as editing the from the project options and rebuilding the application with no errors from the generated APIs or boot code.

#### 7.1.4.2 Component Catalog

The component catalog is a repository of reusable design elements that select device functionality and customize your PSoC device. It is populated with an impressive selection of content; from simple primitives such as logic gates and device registers, through the digital timers, counters and PWMs, plus analog components such as ADC and DAC, and communication protocols, such as  $I^2C$ , and USB. See Example Peripherals on page 45 for more details about available peripherals. All content is fully characterized and carefully documented in datasheets with code examples, AC/DC specifications, and user code ready APIs.

#### 7.1.4.3 Design Reuse

The symbol editor gives you the ability to develop reusable components that can significantly reduce future design time. Just draw a symbol and associate that symbol with your proven design. PSoC Creator allows for the placement of the new symbol anywhere in the component catalog along with the content provided by Cypress. You can then reuse your content as many times as you want, and in any number of projects, without ever having to revisit the details of the implementation.

#### 7.1.4.4 Software Development

Anchoring the tool is a modern, highly customizable user interface. It includes project management and integrated editors for C and assembler source code, as well the design entry tools.

Project build control leverages compiler technology from top commercial vendors such as ARM<sup>®</sup> Limited, Keil<sup>™</sup>, and CodeSourcery (GNU). Free versions of Keil C51 and GNU C Compiler (GCC) for ARM, with no restrictions on code size or end product distribution, are included with the tool distribution. Upgrading to more optimizing compilers is a snap with support for the professional Keil C51 product and ARM RealView<sup>™</sup> compiler.

#### 7.1.4.5 Nonintrusive Debugging

With JTAG (4-wire) and SWD (2-wire) debug connectivity available on all devices, the PSoC Creator debugger offers full control over the target device with minimum intrusion. Breakpoints and code execution commands are all readily available from toolbar buttons and an impressive lineup of windows—register, locals, watch, call stack, memory and peripherals—make for an unparalleled level of visibility into the system.

PSoC Creator contains all the tools necessary to complete a design, and then to maintain and extend that design for years to come. All steps of the design flow are carefully integrated and optimized for ease-of-use and to maximize productivity.

More information on output formats is provided in the Technical Reference Manual.

#### 8.2.3 Start of Conversion Input

The SoC signal is used to start an ADC conversion. A digital clock or UDB output can be used to drive this input. It can be used when the sampling period must be longer than the ADC conversion time or when the ADC must be synchronized to other hardware. This signal is optional and does not need to be connected if ADC is running in a continuous mode.

#### 8.2.4 End of Conversion Output

The EoC signal goes high at the end of each ADC conversion. This signal may be used to trigger either an interrupt or DMA request.

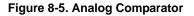

#### 8.3 Comparators

The CY8C32 family of devices contains two comparators in a device. Comparators have these features:

- Input offset factory trimmed to less than 5 mV

- Rail-to-rail common mode input range (VSSA to VDDA)

- Speed and power can be traded off by using one of three modes: fast, slow, or ultra low-power

- Comparator outputs can be routed to lookup tables to perform simple logic functions and then can also be routed to digital blocks

- The positive input of the comparators may be optionally passed through a low pass filter. Two filters are provided

- Comparator inputs can be connections to GPIO or DAC output

#### 8.3.1 Input and Output Interface

The positive and negative inputs to the comparators come from the analog global buses, the analog mux line, the analog local bus and precision reference through multiplexers. The output from each comparator could be routed to any of the two input LUTs. The output of that LUT is routed to the UDB Digital System Interface.

# 11. Electrical Specifications

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. The unique flexibility of the PSoC UDBs and analog blocks enable many functions to be implemented in PSoC Creator components, see the component datasheets for full AC/DC specifications of individual functions. See the "Example Peripherals" section on page 45 for further explanation of PSoC Creator components.

#### 11.1 Absolute Maximum Ratings

| Table 11-1. Absolute Maximum Ratings DC Specifications <sup>[15]</sup> | Table 11-1. | Absolute | Maximum | Ratings | DC S | Specifications <sup>[15]</sup> |

|------------------------------------------------------------------------|-------------|----------|---------|---------|------|--------------------------------|

|------------------------------------------------------------------------|-------------|----------|---------|---------|------|--------------------------------|

| Parameter                         | Description                                             | Conditions                                                                              | Min                   | Тур | Max                        | Units |

|-----------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------|-----|----------------------------|-------|

| V <sub>DDA</sub>                  | Analog supply voltage relative to V <sub>SSA</sub>      |                                                                                         | -0.5                  | -   | 6                          | V     |

| V <sub>DDD</sub>                  | Digital supply voltage relative to V <sub>SSD</sub>     |                                                                                         | -0.5                  | -   | 6                          | V     |

| V <sub>DDIO</sub>                 | I/O supply voltage relative to $V_{SSD}$                |                                                                                         | -0.5                  | -   | 6                          | V     |

| V <sub>CCA</sub>                  | Direct analog core voltage input                        |                                                                                         | -0.5                  | I   | 1.95                       | V     |

| V <sub>CCD</sub>                  | Direct digital core voltage input                       |                                                                                         | -0.5                  | 1   | 1.95                       | V     |

| V <sub>SSA</sub>                  | Analog ground voltage                                   |                                                                                         | V <sub>SSD</sub> –0.5 | -   | V <sub>SSD</sub> +<br>0.5  | V     |

| V <sub>GPIO</sub> <sup>[16]</sup> | DC input voltage on GPIO                                | Includes signals sourced by $V_{\mbox{\scriptsize DDA}}$ and routed internal to the pin | V <sub>SSD</sub> –0.5 | -   | V <sub>DDIO</sub> +<br>0.5 | V     |

| V <sub>SIO</sub>                  | DC input voltage on SIO                                 | Output disabled                                                                         | V <sub>SSD</sub> –0.5 | -   | 7                          | V     |

|                                   |                                                         | Output enabled                                                                          | V <sub>SSD</sub> –0.5 | -   | 6                          | V     |

| V <sub>IND</sub>                  | Voltage at boost converter input                        |                                                                                         | 0.5                   | -   | 5.5                        | V     |

| V <sub>BAT</sub>                  | Boost converter supply                                  |                                                                                         | V <sub>SSD</sub> –0.5 | -   | 5.5                        | V     |

| I <sub>VDDIO</sub>                | Current per V <sub>DDIO</sub> supply pin                |                                                                                         | -                     | -   | 100                        | mA    |

| I <sub>GPIO</sub>                 | GPIO current                                            |                                                                                         | -30                   | -   | 41                         | mA    |

| I <sub>SIO</sub>                  | SIO current                                             |                                                                                         | -49                   | -   | 28                         | mA    |

| I <sub>USBIO</sub>                | USBIO current                                           |                                                                                         | -56                   | -   | 59                         | mA    |

| VEXTREF                           | ADC external reference inputs                           | Pins P0[3], P3[2]                                                                       | -                     | I   | 2                          | V     |

| LU                                | Latch up current <sup>[17]</sup>                        |                                                                                         | -140                  | -   | 140                        | mA    |

| ESD <sub>HBM</sub>                | Electrostatic discharge voltage,                        | V <sub>SSA</sub> tied to V <sub>SSD</sub>                                               | 2200                  | I   | -                          | V     |

|                                   | Human body model                                        | V <sub>SSA</sub> not tied to V <sub>SSD</sub>                                           | 750                   | -   | -                          | V     |

| ESD <sub>CDM</sub>                | Electrostatic discharge voltage,<br>Charge device model |                                                                                         | 500                   | -   | -                          | V     |

Notes

15. Usage above the absolute maximum conditions listed in Table 11-1 may cause permanent damage to the device. Exposure to Absolute Maximum conditions for extended periods of time may affect device reliability. The Maximum Storage Temperature is 150 °C in compliance with JEDEC Standard JESD22-A103, High Temperature Storage Life. When used below Absolute Maximum conditions but above normal operating conditions, the device may not operate to specification.

16. The V<sub>DDIO</sub> supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin ≤ V<sub>DDIO</sub> ≤ V<sub>DDA</sub>. 17. Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch-up Test.

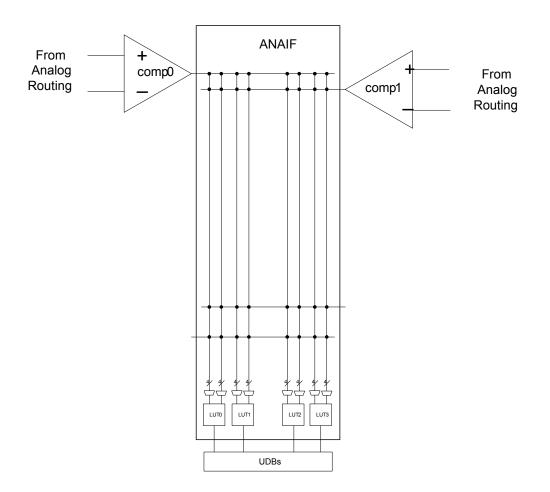

Figure 11-1. Active Mode Current vs F<sub>CPU</sub>, V<sub>DD</sub> = 3.3 V, Temperature = 25 °C

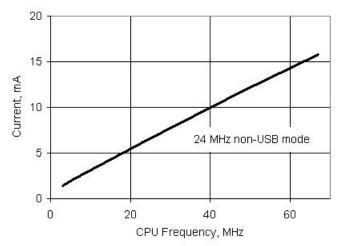

Figure 11-3. Active Mode Current vs  $V_{\text{DD}}$  and Temperature,  $F_{\text{CPU}}$  = 24 MHz

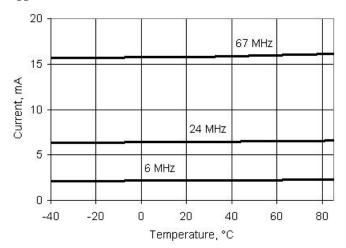

Figure 11-2. Active Mode Current vs Temperature and F<sub>CPU</sub>,  $V_{DD} = 3.3 V$

#### Notes

25. If V<sub>CCD</sub> and V<sub>CCA</sub> are externally regulated, the voltage difference between V<sub>CCD</sub> and V<sub>CCA</sub> must be less than 50 mV. 26. Sleep timer generates periodic interrupts to wake up the CPU. This specification applies only to those times that the CPU is off. 27. Externally regulated mode.

Based on device characterization (not production tested).

Based on device characterization (not production tested). USBIO pins tied to ground (V<sub>SSD</sub>).

Table 11-12. SIO AC Specifications (continued)

| Parameter | Description                                                                                        | Conditions                               | Min | Тур | Max | Units |  |  |

|-----------|----------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|--|--|

|           | SIO output operating frequency                                                                     |                                          |     |     |     |       |  |  |

| Fsioout   | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Unregu-<br>lated output (GPIO) mode, fast<br>strong drive mode  | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 33  | MHz   |  |  |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Unregu-<br>lated output (GPIO) mode, fast<br>strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 16  | MHz   |  |  |

|           | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Unregu-<br>lated output (GPIO) mode, slow<br>strong drive mode  | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 5   | MHz   |  |  |

|           | 1.71 V < V <sub>DDIO</sub> < 3.3 V, Unregu-<br>lated output (GPIO) mode, slow<br>strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | -   | 4   | MHz   |  |  |

|           | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Regulated<br>output mode, fast strong drive<br>mode             | Output continuously switching into 25 pF | -   | -   | 20  | MHz   |  |  |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Regulated<br>output mode, fast strong drive<br>mode            | Output continuously switching into 25 pF | -   | -   | 10  | MHz   |  |  |

|           | 1.71 V < V <sub>DDIO</sub> < 5.5 V, Regulated<br>output mode, slow strong drive<br>mode            | Output continuously switching into 25 pF | -   | -   | 2.5 | MHz   |  |  |

| Fsioin    | SIO input operating frequency                                                                      | ·                                        | -   | · · |     |       |  |  |

|           | 1.71 V <u>≤</u> V <sub>DDIO</sub> <u>≤</u> 5.5 V                                                   | 90/10% V <sub>DDIO</sub>                 | -   | -   | 33  | MHz   |  |  |

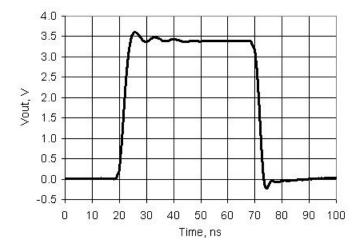

# Figure 11-20. SIO Output Rise and Fall Times, Fast Strong Mode, $V_{DDIO}$ = 3.3 V, 25 pF Load

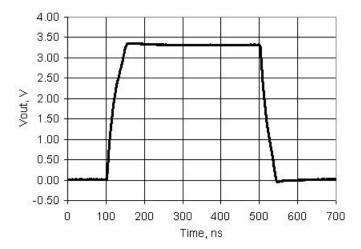

Figure 11-21. SIO Output Rise and Fall Times, Slow Strong Mode,  $V_{\mbox{DDIO}}$  = 3.3 V, 25 pF Load

#### Table 11-20. Delta-sigma ADC AC Specifications

| Parameter    | Description                                                       | Conditions                                   | Min | Тур | Max    | Units   |

|--------------|-------------------------------------------------------------------|----------------------------------------------|-----|-----|--------|---------|

|              | Startup time                                                      |                                              | 1   | -   | 4      | Samples |

| THD          | Total harmonic distortion <sup>[48]</sup>                         | Buffer gain = 1, 12-bit,<br>Range = ±1.024 V | -   | -   | 0.0032 | %       |

| 12-Bit Resol | ution Mode                                                        |                                              |     |     |        |         |

| SR12         | Sample rate, continuous, high power <sup>[48]</sup>               | Range = ±1.024 V, unbuffered                 | 4   | -   | 192    | ksps    |

| BW12         | Input bandwidth at max sample rate <sup>[48]</sup>                | Range = ±1.024 V, unbuffered                 | 1   | 44  | -      | kHz     |

| SINAD12int   | Signal to noise ratio, 12-bit, internal reference <sup>[48]</sup> | Range = ±1.024 V, unbuffered                 | 66  | -   | -      | dB      |

| 8-Bit Resolu | tion Mode                                                         |                                              |     | •   |        |         |

| SR8          | Sample rate, continuous, high power <sup>[48]</sup>               | Range = $\pm 1.024$ V, unbuffered            | 8   | -   | 384    | ksps    |

| BW8          | Input bandwidth at max sample rate <sup>[48]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 88  | -      | kHz     |

| SINAD8int    | Signal to noise ratio, 8-bit, internal reference <sup>[48]</sup>  | Range = ±1.024 V, unbuffered                 | 43  | _   | -      | dB      |

Table 11-21. Delta-sigma ADC Sample Rates, Range = ±1.024 V

| Resolution, | Conti | Continuous |      | Sample |

|-------------|-------|------------|------|--------|

| Bits        | Min   | Max        | Min  | Max    |

| 8           | 8000  | 384000     | 1911 | 91701  |

| 9           | 6400  | 307200     | 1543 | 74024  |

| 10          | 5566  | 267130     | 1348 | 64673  |

| 11          | 4741  | 227555     | 1154 | 55351  |

| 12          | 4000  | 192000     | 978  | 46900  |

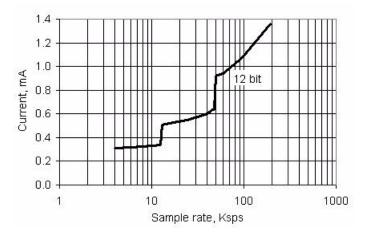

Figure 11-25. Delta-sigma ADC IDD vs sps, Range = ±1.024 V, Continuous Sample Mode, Input Buffer Bypassed

Note 48. Based on device characterization (Not production tested).

# 13. Packaging

## Table 13-1. Package Characteristics

| Parameter       | Description                          | Conditions | Min | Тур   | Max | Units   |

|-----------------|--------------------------------------|------------|-----|-------|-----|---------|

| T <sub>A</sub>  | Operating ambient temperature        |            | -40 | 25.00 | 85  | °C      |

| TJ              | Operating junction temperature       |            | -40 | -     | 100 | °C      |

| T <sub>JA</sub> | Package $\theta_{JA}$ (48-pin SSOP)  |            | -   | 49    | -   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (48-pin QFN)   |            | -   | 14    | _   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (68-pin QFN)   |            | -   | 15    | -   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (100-pin TQFP) |            | -   | 34    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (48-pin SSOP)  |            | -   | 24    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (48-pin QFN)   |            | -   | 15    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (68-pin QFN)   |            | -   | 13    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (100-pin TQFP) |            | -   | 10    | -   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (72-pin CSP)   |            | -   | 18    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (72-pin CSP)   |            | _   | 0.13  | _   | °C/Watt |

#### Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at Peak<br>Temperature |

|--------------|-----------------------------|-------------------------------------|

| 48-pin SSOP  | 260 °C                      | 30 seconds                          |

| 48-pin QFN   | 260 °C                      | 30 seconds                          |

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

| 72-pin CSP   | 260 °C                      | 30 seconds                          |

## Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 3 |

| 48-pin QFN   | MSL 3 |

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

| 72-pin CSP   | MSL 1 |

#### Description Acronym PHUB peripheral hub PHY physical layer PICU port interrupt control unit PLA programmable logic array PI D programmable logic device, see also PAL PLL phase-locked loop PMDD package material declaration datasheet POR power-on reset PRES precise low-voltage reset PRS pseudo random sequence PS port read data register PSoC® Programmable System-on-Chip™ PSRR power supply rejection ratio PWM pulse-width modulator RAM random-access memory RISC reduced-instruction-set computing RMS root-mean-square RTC real-time clock RTL register transfer language RTR remote transmission request RX receive SAR successive approximation register SC/CT switched capacitor/continuous time I<sup>2</sup>C serial clock SCI SDA I<sup>2</sup>C serial data S/H sample and hold SINAD signal to noise and distortion ratio SIO special input/output. GPIO with advanced features. See GPIO. SOC start of conversion

## Table 14-1. Acronyms Used in this Document (continued)

#### Table 14-1. Acronyms Used in this Document (continued)

| Acronym | Description                                                               |

|---------|---------------------------------------------------------------------------|

| SOF     | start of frame                                                            |

| SPI     | Serial Peripheral Interface, a communications protocol                    |

| SR      | slew rate                                                                 |

| SRAM    | static random access memory                                               |

| SRES    | software reset                                                            |

| SWD     | serial wire debug, a test protocol                                        |

| SWV     | single-wire viewer                                                        |

| TD      | transaction descriptor, see also DMA                                      |

| THD     | total harmonic distortion                                                 |

| TIA     | transimpedance amplifier                                                  |

| TRM     | technical reference manual                                                |

| TTL     | transistor-transistor logic                                               |

| ТХ      | transmit                                                                  |

| UART    | Universal Asynchronous Transmitter Receiver, a<br>communications protocol |

| UDB     | universal digital block                                                   |

| USB     | Universal Serial Bus                                                      |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port                 |

| VDAC    | voltage DAC, see also DAC, IDAC                                           |

| WDT     | watchdog timer                                                            |

| WOL     | write once latch, see also NVL                                            |

| WRES    | watchdog timer reset                                                      |

| XRES    | external reset I/O pin                                                    |

| XTAL    | crystal                                                                   |

## **15. Reference Documents**

PSoC® 3, PSoC® 5 Architecture TRM PSoC® 3 Registers TRM

| Descript<br>Docume | Description Title: PSoC <sup>®</sup> 3: CY8C32 Family Data Sheet Programmable System-on-Chip (PSoC <sup>®</sup> ) (continued)<br>Document Number: 001-56955 |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Revision           | ECN                                                                                                                                                         | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| *L                 | 3464258                                                                                                                                                     | 12/14/2011         | MKEA               | Updated Analog Global specs<br>Updated IDAC range<br>Modified VDDIO description in Section 3<br>Added note on Sleep and Hibernate modes in the Power Modes section<br>Updated Boost Converter section<br>Updated Boost Converter section<br>Updated conditions for Inductive boost AC specs<br>Added VDAC/IDAC noise graphs and specs<br>Added VDAC/IDAC noise graphs and specs<br>Added pin capacitance specs for ECO pins<br>Removed C <sub>L</sub> from 32 kHz External Crystal DC Specs table.<br>Added reference to AN54439 in Section 6.1.2.2<br>Deleted T_SWDO_hold row from the SWD Interface AC Specifications table<br>Removed Pin 46 connections in "Example Schematic for 100-pin TQFP Part with<br>Power Connections"<br>Updated Active Mode IDD description in Table 11-2.<br>Added I <sub>DDDR</sub> and I <sub>DDAR</sub> specs in Table 11-2.<br>Replaced "total device program time" with T <sub>PROG</sub> in Flash AC specs table<br>Added I <sub>GPIO</sub> , I <sub>SIO</sub> and I <sub>USBIO</sub> specs in Absolute Maximum Ratings<br>Added conditions to I <sub>CC</sub> spec in 32 kHz External Crystal DC Specs table.<br>Updated TCV <sub>OS</sub> value<br>Removed Boost Efficiency vs V <sub>OUT</sub> graph<br>Updated boost graphs<br>Updated boost graphs<br>Updated USBIO Block diagram; added USBIO drive mode description<br>Updated Analog Interconnect diagram<br>Changed max IMO startup time to 12 µs<br>Added note for I <sub>IL</sub> spec in USBIO DC specs table<br>Updated GPIO Block diagram<br>Updated GPIO Block diagram<br>Updated GPIO Block diagram<br>Updated voltage reference specs<br>Added text explaining power supply ramp up in Section 11-4. |  |  |  |  |