#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 50MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 48-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3246pvi-147 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Notes

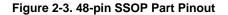

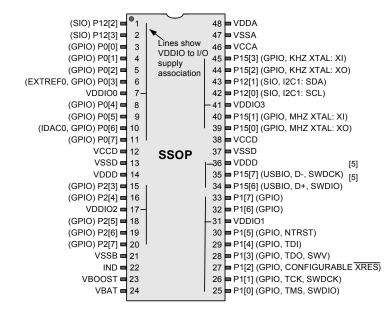

- 5. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

- The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices.

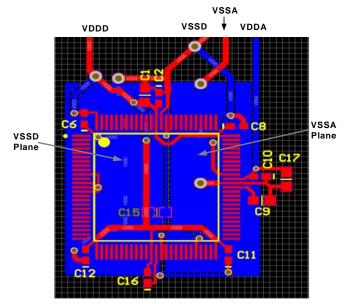

## Figure 2-8. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

# 3. Pin Descriptions

### IDAC0

Low resistance output pin for high current DAC (IDAC).

### Extref0, Extref1

External reference input to the analog system.

## GPIO

General purpose I/O pin provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense.

### 12C0: SCL, 12C1: SCL

$I^2C$  SCL line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SCL if wake from sleep is not required.

### 12C0: SDA, 12C1: SDA

$\rm I^2C$  SDA line providing wake from sleep on an address match. Any I/O pin can be used for  $\rm I^2C$  SDA if wake from sleep is not required.

### Ind

Inductor connection to boost pump.

### kHz XTAL: Xo, kHz XTAL: Xi

32.768-kHz crystal oscillator pin.

### MHz XTAL: Xo, MHz XTAL: Xi

4- to 25- MHz crystal oscillator pin.

## nTRST

Optional JTAG test reset programming and debug port connection to reset the JTAG connection.

### SIO

Special I/O provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

### SWDCK

Serial wire debug clock programming and debug port connection.

## SWDIO

Serial wire debug input and output programming and debug port connection.

## SWV.

Single wire viewer debug output.

## тск

JTAG test clock programming and debug port connection.

# TDI

JTAG test data in programming and debug port connection.

## TDO

JTAG test data out programming and debug port connection.

## TMS

JTAG test mode select programming and debug port connection.

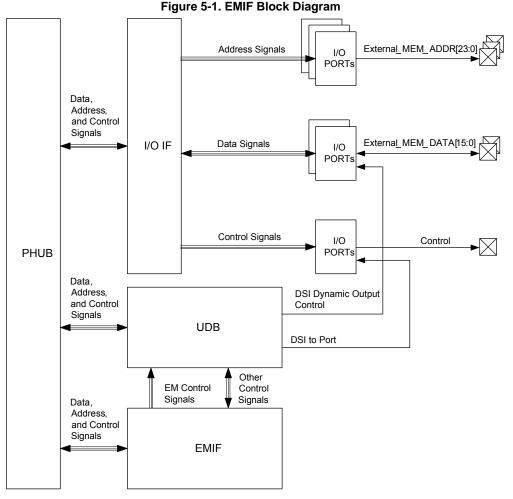

## 5.6 External Memory Interface

CY8C32 provides an external memory interface (EMIF) for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles. Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C32 supports only one type of external memory device at a time.

External memory can be accessed via the 8051 xdata space; up to 24 address bits can be used. See "xdata Space" section on page 28. The memory can be 8 or 16 bits wide.

## 5.7 Memory Map

The CY8C32 8051 memory map is very similar to the MCS-51 memory map.

### 5.7.1 Code Space

The CY8C32 8051 code space is 64 KB. Only main flash exists in this space. See the "Flash Program Memory" section on page 24.

### 5.7.2 Internal Data Space

The CY8C32 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in Static RAM on page 24) and a 128-byte space for Special Function Registers (SFRs). See Figure 5-2. The lowest 32 bytes are used for 4 banks of registers R0-R7. The next 16 bytes are bit-addressable.

I/O ports are linked to the CPU through the PHUB and are also available in the SFRs. Using the SFRs allows faster access to a limited set of I/O port registers, while using the PHUB allows boot configuration and access to all I/O port registers.

Each SFR supported I/O port provides three SFRs:

- SFRPRTxDR sets the output data state of the port (where x is port number and includes ports 0 6, 12 and 15).

- The SFRPRTxSEL selects whether the PHUB PRTxDR register or the SFRPRTxDR controls each pin's output buffer within the port. If a SFRPRTxSEL[y] bit is high, the corresponding SFRPRTxDR[y] bit sets the output state for that pin. If a SFRPRTxSEL[y] bit is low, the corresponding PRTxDR[y] bit sets the output state of the pin (where y varies from 0 to 7).

- The SFRPRTxPS is a read only register that contains pin state values of the port pins.

### 5.7.4 xdata Space

The 8051 xdata space is 24-bit, or 16 MB in size. The majority of this space is not "external"—it is used by on-chip components. See Table 5-5. External, that is, off-chip, memory can be accessed using the EMIF. See External Memory Interface on page 26.

| Address Range         | Purpose                                            |

|-----------------------|----------------------------------------------------|

| 0×00 0000 – 0×00 1FFF | SRAM                                               |

| 0×00 4000 – 0×00 42FF | Clocking, PLLs, and oscillators                    |

| 0×00 4300 – 0×00 43FF | Power management                                   |

| 0×00 4400 – 0×00 44FF | Interrupt controller                               |

| 0×00 4500 – 0×00 45FF | Ports interrupt control                            |

| 0×00 4700 – 0×00 47FF | Flash programming interface                        |

| 0×00 4800 – 0×00 48FF | Cache controller                                   |

| 0×00 4900 – 0×00 49FF | I <sup>2</sup> C controller                        |

| 0×00 4E00 – 0×00 4EFF | Decimator                                          |

| 0×00 4F00 – 0×00 4FFF | Fixed timer/counter/PWMs                           |

| 0×00 5000 – 0×00 51FF | I/O ports control                                  |

| 0×00 5400 – 0×00 54FF | External Memory Interface (EMIF) control registers |

| 0×00 5800 – 0×00 5FFF | Analog Subsystem interface                         |

| 0×00 6000 – 0×00 60FF | USB controller                                     |

| 0×00 6400 – 0×00 6FFF | UDB Working Registers                              |

| 0×00 7000 – 0×00 7FFF | PHUB configuration                                 |

| 0×00 8000 – 0×00 8FFF | EEPROM                                             |

| 0×01 0000 – 0×01 FFFF | Digital Interconnect configuration                 |

| 0×05 0220 – 0×05 02F0 | Debug controller                                   |

| 0×08 0000 – 0×08 1FFF | Flash ECC bytes                                    |

| 0×80 0000 – 0×FF FFFF | External Memory Interface                          |

#### Table 5-5. XDATA Data Address Map

## 6. System Integration

### 6.1 Clocking System

The clocking system generates, divides, and distributes clocks throughout the PSoC system. For the majority of systems, no external crystal is required. The IMO and PLL together can generate up to a 50 MHz clock, accurate to  $\pm 2$  percent over voltage and temperature. Additional internal and external clock sources allow each design to optimize accuracy, power, and cost. Any of the clock sources can be used to generate other clock frequencies in the 16-bit clock dividers and UDBs for anything the user wants, for example a UART baud rate generator.

Clock generation and distribution is automatically configured through the PSoC Creator IDE graphical interface. This is based on the complete system's requirements. It greatly speeds the design process. PSoC Creator allows you to build clocking systems with minimal input. You can specify desired clock frequencies and accuracies, and the software locates or builds a clock that meets the required specifications. This is possible because of the programmability inherent in PSoC.

Key features of the clocking system include:

- Seven general purpose clock sources

- □ 3- to 24-MHz IMO, ±2 percent at 3 MHz

- □ 4- to 25-MHz external crystal oscillator (MHzECO)

- Clock doubler provides a doubled clock frequency output for the USB block, see USB Clock Domain on page 31

- DSI signal from an external I/O pin or other logic

- 24- to 50- MHz fractional PLL sourced from IMO, MHzECO, or DSI

- I-kHz, 33-kHz, 100-kHz ILO for watchdog timer (WDT) and sleep timer

- 32.768-kHz external crystal oscillator (kHzECO) for RTC

- IMO has a USB mode that auto locks to the USB bus clock requiring no external crystal for USB. (USB equipped parts only)

- Independently sourced clock in all clock dividers

- Eight 16-bit clock dividers for the digital system

- Four 16-bit clock dividers for the analog system

- Dedicated 16-bit divider for the bus clock

- Dedicated 4-bit divider for the CPU clock

- Automatic clock configuration in PSoC Creator

- Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- CapSense

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- Higher drive strength than GPIO

- $\blacksquare$  Hot swap capability (5 V tolerance at any operating V\_{DD})

- Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- Overvoltage tolerance up to 5.5 V

- □ SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- Highest drive strength for general purpose use

- Input, output, or both for CPU and DMA

- Input, output, or both for digital peripherals

- Digital output (CMOS) drive mode

- Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

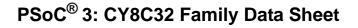

## 7.2 Universal Digital Block

The Universal Digital Block (UDB) represents an evolutionary step to the next generation of PSoC embedded digital peripheral functionality. The architecture in first generation PSoC digital blocks provides coarse programmability in which a few fixed functions with a small number of options are available. The new UDB architecture is the optimal balance between configuration granularity and efficient implementation. A cornerstone of this approach is to provide the ability to customize the devices digital operation to match application requirements.

To achieve this, UDBs consist of a combination of uncommitted logic (PLD), structured logic (Datapath), and a flexible routing scheme to provide interconnect between these elements, I/O connections, and other peripherals. UDB functionality ranges from simple self contained functions that are implemented in one UDB, or even a portion of a UDB (unused resources are available for other functions), to more complex functions that require multiple UDBs. Examples of basic functions are timers, counters, CRC generators, PWMs, dead band generators, and communications functions, such as UARTs, SPI, and I<sup>2</sup>C. Also, the PLD blocks and connectivity provide full featured general purpose programmable logic within the limits of the available resources.

### Figure 7-2. UDB Block Diagram

Routing Channel

The main component blocks of the UDB are:

- PLD blocks There are two small PLDs per UDB. These blocks take inputs from the routing array and form registered or combinational sum-of-products logic. PLDs are used to implement state machines, state bits, and combinational logic equations. PLD configuration is automatically generated from graphical primitives.

- Datapath Module This 8-bit wide datapath contains structured logic to implement a dynamically configurable ALU, a variety of compare configurations and condition generation. This block also contains input/output FIFOs, which are the primary parallel data interface between the CPU/DMA system and the UDB.

- Status and Control Module The primary role of this block is to provide a way for CPU firmware to interact and synchronize with UDB operation.

- Clock and Reset Module This block provides the UDB clocks and reset selection and control.

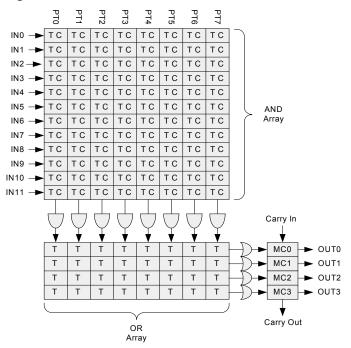

### 7.2.1 PLD Module

The primary purpose of the PLD blocks is to implement logic expressions, state machines, sequencers, lookup tables, and decoders. In the simplest use model, consider the PLD blocks as a standalone resource onto which general purpose RTL is synthesized and mapped. The more common and efficient use model is to create digital functions from a combination of PLD and datapath blocks, where the PLD implements only the random logic and state portion of the function while the datapath (ALU) implements the more structured elements.

### Figure 7-3. PLD 12C4 Structure

One 12C4 PLD block is shown in Figure 7-3. This PLD has 12 inputs, which feed across eight product terms. Each product term (AND function) can be from 1 to 12 inputs wide, and in a given product term, the true (T) or complement (C) of each input can be selected. The product terms are summed (OR function) to create the PLD outputs. A sum can be from 1 to 8 product terms wide. The 'C' in 12C4 indicates that the width of the OR gate (in this case 8) is constant across all outputs (rather than variable as in a 22V10 device). This PLA like structure gives maximum flexibility and insures that all inputs and outputs are permutable for ease of allocation by the software tools. There are two 12C4 PLDs in each UDB.

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

### 7.2.2.3 Conditionals

Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers in a variety of configurations. Other conditions include zero detect, all ones detect, and overflow. These conditions are the primary datapath outputs, a selection of which can be driven out to the UDB routing matrix. Conditional computation can use the built in chaining to neighboring UDBs to operate on wider data widths without the need to use routing resources.

### 7.2.2.4 Variable MSB

The most significant bit of an arithmetic and shift function can be programmatically specified. This supports variable width CRC and PRS functions, and in conjunction with ALU output masking, can implement arbitrary width timers, counters and shift blocks.

### 7.2.2.5 Built in CRC/PRS

The datapath has built in support for single cycle Cyclic Redundancy Check (CRC) computation and Pseudo Random Sequence (PRS) generation of arbitrary width and arbitrary polynomial. CRC/PRS functions longer than 8 bits may be implemented in conjunction with PLD logic, or built in chaining may be use to extend the function into neighboring UDBs.

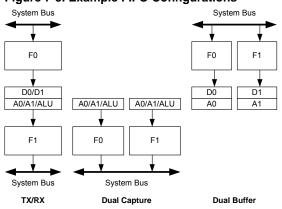

### 7.2.2.6 Input/Output FIFOs

Each datapath contains two four-byte deep FIFOs, which can be independently configured as an input buffer (system bus writes to the FIFO, datapath internal reads the FIFO), or an output buffer (datapath internal writes to the FIFO, the system bus reads from the FIFO). The FIFOs generate status that are selectable as datapath outputs and can therefore be driven to the routing, to interact with sequencers, interrupts, or DMA.

### Figure 7-5. Example FIFO Configurations

## 7.2.2.7 Chaining

The datapath can be configured to chain conditions and signals such as carries and shift data with neighboring datapaths to create higher precision arithmetic, shift, CRC/PRS functions.

### 7.2.2.8 Time Multiplexing

In applications that are over sampled, or do not need high clock rates, the single ALU block in the datapath can be efficiently shared with two sets of registers and condition generators. Carry and shift out data from the ALU are registered and can be selected as inputs in subsequent cycles. This provides support for 16-bit functions in one (8-bit) datapath.

### 7.2.2.9 Datapath I/O

There are six inputs and six outputs that connect the datapath to the routing matrix. Inputs from the routing provide the configuration for the datapath operation to perform in each cycle, and the serial data inputs. Inputs can be routed from other UDB blocks, other device peripherals, device I/O pins, and so on. The outputs to the routing can be selected from the generated conditions, and the serial data outputs. Outputs can be routed to other UDB blocks, device peripherals, interrupt and DMA controller, I/O pins, and so on.

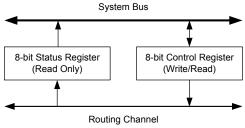

### 7.2.3 Status and Control Module

The primary purpose of this circuitry is to coordinate CPU firmware interaction with internal UDB operation.

### Figure 7-6. Status and Control Registers

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

### 7.2.3.2 Clock Generation

Each subcomponent block of a UDB including the two PLDs, the datapath, and Status and Control, has a clock selection and control block. This promotes a fine granularity with respect to allocating clocking resources to UDB component blocks and allows unused UDB resources to be used by other functions for maximum system efficiency.

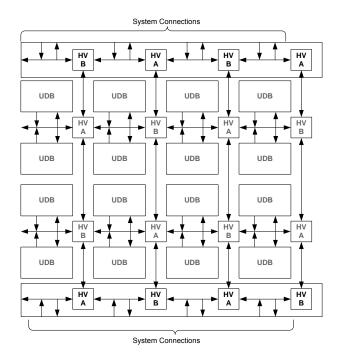

## 7.3 UDB Array Description

Figure 7-7 shows an example of a 16 UDB array. In addition to the array core, there are a DSI routing interfaces at the top and bottom of the array. Other interfaces that are not explicitly shown include the system interfaces for bus and clock distribution. The UDB array includes multiple horizontal and vertical routing channels each comprised of 96 wires. The wire connections to UDBs, at horizontal/vertical intersection and at the DSI interface are highly permutable providing efficient automatic routing in PSoC Creator. Additionally the routing allows wire by wire segmentation along the vertical and horizontal routing to further increase routing flexibility and capability.

### Figure 7-7. Digital System Interface Structure

### 7.3.1 UDB Array Programmable Resources

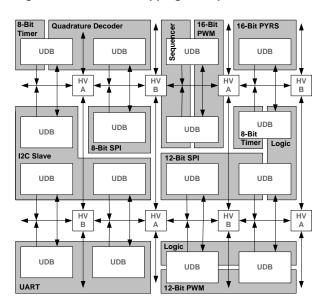

Figure 7-8 shows an example of how functions are mapped into a bank of 16 UDBs. The primary programmable resources of the UDB are two PLDs, one datapath and one status/control register. These resources are allocated independently, because they have independently selectable clocks, and therefore unused blocks are allocated to other unrelated functions. An example of this is the 8-bit Timer in the upper left corner of the array. This function only requires one datapath in the UDB, and therefore the PLD resources may be allocated to another function. A function such as a Quadrature Decoder may require more PLD logic than one UDB can supply and in this case can utilize the unused PLD blocks in the 8-bit Timer UDB. Programmable resources in the UDB array are generally homogeneous so functions can be mapped to arbitrary boundaries in the array.

### Figure 7-8. Function Mapping Example in a Bank of UDBs

## 7.4 DSI Routing Interface Description

The DSI routing interface is a continuation of the horizontal and vertical routing channels at the top and bottom of the UDB array core. It provides general purpose programmable routing between device peripherals, including UDBs, I/Os, analog peripherals, interrupts, DMA and fixed function peripherals.

Figure 7-9 illustrates the concept of the digital system interconnect, which connects the UDB array routing matrix with other device peripherals. Any digital core or fixed function peripheral that needs programmable routing is connected to this interface.

Signals in this category include:

- Interrupt requests from all digital peripherals in the system.

- DMA requests from all digital peripherals in the system.

- Digital peripheral data signals that need flexible routing to I/Os.

- Digital peripheral data signals that need connections to UDBs.

- Connections to the interrupt and DMA controllers.

- Connection to I/O pins.

- Connection to analog system digital signals.

## 8.1 Analog Routing

The CY8C32 family of devices has a flexible analog routing architecture that provides the capability to connect GPIOs and different analog blocks, and also route signals between different analog blocks. One of the strong points of this flexible routing architecture is that it allows dynamic routing of input and output connections to the different analog blocks.

For information on how to make pin selections for optimal analog routing, refer to the application note, AN58304 - PSoC® 3 and PSoC® 5 - Pin Selection for Analog Designs.

- 8.1.1 Features

- Flexible, configurable analog routing architecture

- 16 analog globals (AG) and two analog mux buses (AMUXBUS) to connect GPIOs and the analog blocks

- Each GPIO is connected to one analog global and one analog mux bus

- Eight analog local buses (abus) to route signals between the different analog blocks

- Multiplexers and switches for input and output selection of the analog blocks

### 8.1.2 Functional Description

Analog globals (AGs) and analog mux buses (AMUXBUS) provide analog connectivity between GPIOs and the various analog blocks. There are 16 AGs in the CY8C32 family. The analog routing architecture is divided into four quadrants as shown in Figure 8-2. Each quadrant has four analog globals (AGL[0..3], AGL[4..7], AGR[0..3], AGR[4..7]). Each GPIO is connected to the corresponding AG through an analog switch. The analog mux bus is a shared routing resource that connects to every GPIO through an analog switch. There are two AMUXBUS routes in CY8C32, one in the left half (AMUXBUSL) and one in the right half (AMUXBUSR), as shown in Figure 8-2.

## 8.3.2 LUT

The CY8C32 family of devices contains four LUTs. The LUT is a two input, one output lookup table that is driven by any one or two of the comparators in the chip. The output of any LUT is routed to the digital system interface of the UDB array. From the digital system interface of the UDB array, these signals can be connected to UDBs, DMA controller, I/O, or the interrupt controller.

The LUT control word written to a register sets the logic function on the output. The available LUT functions and the associated control word is shown in Table 8-2.

| Control Word | Output (A and B are LUT inputs) |

|--------------|---------------------------------|

| 0000b        | <b>FALSE</b> ('0')              |

| 0001b        | A AND B                         |

| 0010b        | A AND (NOT B)                   |

| 0011b        | A                               |

| 0100b        | (NOT <b>A</b> ) AND <b>B</b>    |

| 0101b        | В                               |

| 0110b        | A XOR B                         |

| 0111b        | A OR B                          |

| 1000b        | A NOR B                         |

| 1001b        | A XNOR B                        |

| 1010b        | NOT <b>B</b>                    |

| 1011b        | A OR (NOT B)                    |

| 1100b        | NOT A                           |

| 1101b        | (NOT <b>A</b> ) OR <b>B</b>     |

| 1110b        | A NAND B                        |

| 1111b        | <b>TRUE</b> ('1')               |

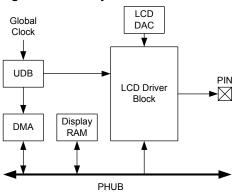

## 8.4 LCD Direct Drive

The PSoC Liquid Crystal Display (LCD) driver system is a highly configurable peripheral designed to allow PSoC to directly drive a broad range of LCD glass. All voltages are generated on chip, eliminating the need for external components. With a high multiplex ratio of up to 1/16, the CY8C32 family LCD driver system can drive a maximum of 736 segments. The PSoC LCD driver module was also designed with the conservative power budget of portable devices in mind, enabling different LCD drive modes and power down modes to conserve power.

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low-power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

- Adjustable LCD refresh rate from 10 Hz to 150 Hz

- Ability to invert LCD display for negative image

- Three LCD driver drive modes, allowing power optimization

#### Figure 8-6. LCD System

### 8.4.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

### 8.4.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers via DMA.

#### 8.4.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

# 11. Electrical Specifications

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. The unique flexibility of the PSoC UDBs and analog blocks enable many functions to be implemented in PSoC Creator components, see the component datasheets for full AC/DC specifications of individual functions. See the "Example Peripherals" section on page 45 for further explanation of PSoC Creator components.

## 11.1 Absolute Maximum Ratings

| Parameter                         | Description                                             | Conditions                                                                              | Min                   | Тур | Max                       | Units |

|-----------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------|-----|---------------------------|-------|

| V <sub>DDA</sub>                  | Analog supply voltage relative to V <sub>SSA</sub>      |                                                                                         | -0.5                  | _   | 6                         | V     |

| V <sub>DDD</sub>                  | Digital supply voltage relative to V <sub>SSD</sub>     |                                                                                         | -0.5                  | -   | 6                         | V     |

| V <sub>DDIO</sub>                 | I/O supply voltage relative to $V_{SSD}$                |                                                                                         | -0.5                  | -   | 6                         | V     |

| V <sub>CCA</sub>                  | Direct analog core voltage input                        |                                                                                         | -0.5                  | -   | 1.95                      | V     |

| V <sub>CCD</sub>                  | Direct digital core voltage input                       |                                                                                         | -0.5                  | I   | 1.95                      | V     |

| V <sub>SSA</sub>                  | Analog ground voltage                                   |                                                                                         | V <sub>SSD</sub> –0.5 | -   | V <sub>SSD</sub> +<br>0.5 | V     |

| V <sub>GPIO</sub> <sup>[16]</sup> | DC input voltage on GPIO                                | Includes signals sourced by $V_{\mbox{\scriptsize DDA}}$ and routed internal to the pin | V <sub>SSD</sub> –0.5 | -   | V <sub>DDIO</sub> + 0.5   | V     |

| V <sub>SIO</sub>                  | DC input voltage on SIO                                 | Output disabled                                                                         | V <sub>SSD</sub> –0.5 | -   | 7                         | V     |

|                                   |                                                         | Output enabled                                                                          | V <sub>SSD</sub> –0.5 | -   | 6                         | V     |

| V <sub>IND</sub>                  | Voltage at boost converter input                        |                                                                                         | 0.5                   | -   | 5.5                       | V     |

| V <sub>BAT</sub>                  | Boost converter supply                                  |                                                                                         | V <sub>SSD</sub> –0.5 | -   | 5.5                       | V     |

| I <sub>VDDIO</sub>                | Current per V <sub>DDIO</sub> supply pin                |                                                                                         | -                     | -   | 100                       | mA    |

| I <sub>GPIO</sub>                 | GPIO current                                            |                                                                                         | -30                   | -   | 41                        | mA    |

| I <sub>SIO</sub>                  | SIO current                                             |                                                                                         | -49                   | -   | 28                        | mA    |

| I <sub>USBIO</sub>                | USBIO current                                           |                                                                                         | -56                   | -   | 59                        | mA    |

| VEXTREF                           | ADC external reference inputs                           | Pins P0[3], P3[2]                                                                       | -                     | -   | 2                         | V     |

| LU                                | Latch up current <sup>[17]</sup>                        |                                                                                         | -140                  | I   | 140                       | mA    |

|                                   | Electrostatic discharge voltage,                        | V <sub>SSA</sub> tied to V <sub>SSD</sub>                                               | 2200                  | -   | -                         | V     |

| ESD <sub>HBM</sub>                | Human body model                                        | V <sub>SSA</sub> not tied to V <sub>SSD</sub>                                           | 750                   | I   | -                         | V     |

| ESD <sub>CDM</sub>                | Electrostatic discharge voltage,<br>Charge device model |                                                                                         | 500                   | -   | -                         | V     |

Notes

15. Usage above the absolute maximum conditions listed in Table 11-1 may cause permanent damage to the device. Exposure to Absolute Maximum conditions for extended periods of time may affect device reliability. The Maximum Storage Temperature is 150 °C in compliance with JEDEC Standard JESD22-A103, High Temperature Storage Life. When used below Absolute Maximum conditions but above normal operating conditions, the device may not operate to specification.

16. The V<sub>DDIO</sub> supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin ≤ V<sub>DDIO</sub> ≤ V<sub>DDA</sub>. 17. Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch-up Test.

## **11.3 Power Regulators**

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

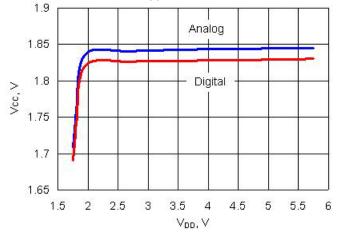

## 11.3.1 Digital Core Regulator

## Table 11-4. Digital Core Regulator DC Specifications

| Parameter        | Description                | Conditions                                                                                                                                               | Min | Тур  | Max | Units |

|------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| V <sub>DDD</sub> | Input voltage              |                                                                                                                                                          | 1.8 | -    | 5.5 | V     |

| V <sub>CCD</sub> | Output voltage             |                                                                                                                                                          | -   | 1.80 | I   | V     |

|                  | Regulator output capacitor | $\pm$ 10%, X5R ceramic or better. The two V <sub>CCD</sub> pins must be shorted together, with as short a trace as possible, see Power System on page 31 | 0.9 | 1    | 1.1 | μF    |

### Figure 11-5. Regulators V<sub>CC</sub> vs V<sub>DD</sub>

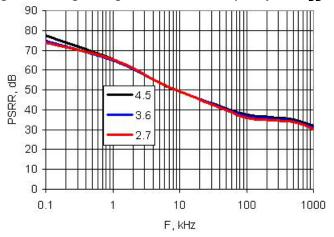

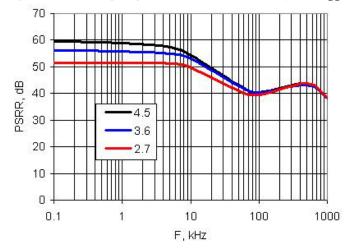

# Figure 11-6. Digital Regulator PSRR vs Frequency and V<sub>DD</sub>

## 11.3.2 Analog Core Regulator

### Table 11-5. Analog Core Regulator DC Specifications

| Parameter        | Description                | Conditions                  | Min | Тур  | Max | Units |

|------------------|----------------------------|-----------------------------|-----|------|-----|-------|

| V <sub>DDA</sub> | Input voltage              |                             | 1.8 | -    | 5.5 | V     |

| V <sub>CCA</sub> | Output voltage             |                             | -   | 1.80 | -   | V     |

|                  | Regulator output capacitor | ±10%, X5R ceramic or better | 0.9 | 1    | 1.1 | μF    |

Figure 11-7. Analog Regulator PSRR vs Frequency and  $V_{DD}$

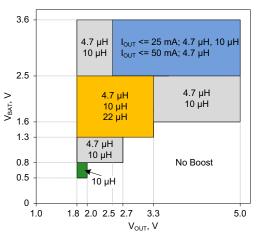

| Table 11-7. | Recommended External Components for Boost Circuit |

|-------------|---------------------------------------------------|

|             |                                                   |

| Parameter          | Description                                                                                      | Conditions     | Min  | Тур  | Max  | Units |

|--------------------|--------------------------------------------------------------------------------------------------|----------------|------|------|------|-------|

| L <sub>BOOST</sub> | Boost inductor                                                                                   | 4.7 μH nominal | 3.7  | 4.7  | 5.7  | μH    |

|                    |                                                                                                  | 10 μH nominal  | 8.0  | 10.0 | 12.0 | μH    |

|                    |                                                                                                  | 22 μH nominal  | 17.0 | 22.0 | 27.0 | μH    |

| C <sub>BOOST</sub> | Total capacitance sum of V <sub>DDD</sub> , V <sub>DDA</sub> , V <sub>DDIO</sub> <sup>[34]</sup> |                | 17.0 | 26.0 | 31.0 | μF    |

| C <sub>BAT</sub>   | Battery filter capacitor                                                                         |                | 17.0 | 22.0 | 27.0 | μF    |

| I <sub>F</sub>     | Schottky diode average forward current                                                           |                | 1.0  | _    | -    | A     |

| V <sub>R</sub>     | Schottky reverse voltage                                                                         |                | 20.0 | -    | -    | V     |

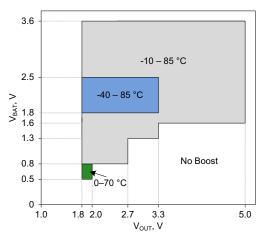

## Figure 11-8. T<sub>A</sub> range over $V_{BAT}$ and $V_{OUT}$

Figure 11-10.  $L_{BOOST}$  values over  $V_{BAT}$  and  $V_{OUT}$

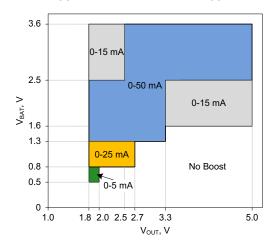

## Figure 11-9. $I_{OUT}$ range over $V_{BAT}$ and $V_{OUT}$

#### Note

34. Based on device characterization (Not production tested).

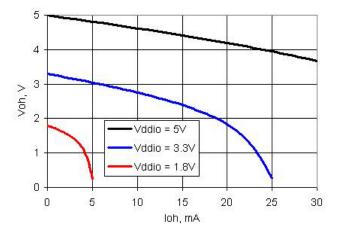

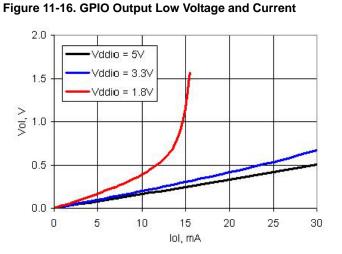

## Figure 11-15. GPIO Output High Voltage and Current

# Table 11-10. GPIO AC Specifications

| Parameter | Description                                                                             | Conditions                            | Min | Тур | Мах | Units |

|-----------|-----------------------------------------------------------------------------------------|---------------------------------------|-----|-----|-----|-------|

| TriseF    |                                                                                         | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | _   | -   | 6   | ns    |

| TfallF    | Fall time in Fast Strong Mode <sup>[38]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | _   | -   | 6   | ns    |

| TriseS    | Rise time in Slow Strong Mode <sup>[38]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

| TfallS    | Fall time in Slow Strong Mode <sup>[38]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

|           | GPIO output operating frequency                                                         |                                       |     |     |     |       |

|           | 2.7 V $\leq$ V <sub>DDIO</sub> $\leq$ 5.5 V, fast strong drive mode                     | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 33  | MHz   |

| Fgpioout  | $1.71 \text{ V} \leq \text{V}_{\text{DDIO}} < 2.7 \text{ V}$ , fast strong drive mode   | 90/10% V <sub>DDIO</sub> into 25 pF   | _   | -   | 20  | MHz   |

|           | $3.3 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , slow strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | _   | -   | 7   | MHz   |

|           | 1.71 V $\leq$ V <sub>DDIO</sub> < 3.3 V, slow strong drive mode                         | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 3.5 | MHz   |

| Fgpioin   | GPIO input operating frequency                                                          |                                       |     |     |     |       |

|           | 1.71 V <u>≤</u> V <sub>DDIO</sub> <u>≤</u> 5.5 V                                        | 90/10% V <sub>DDIO</sub>              | -   | -   | 33  | MHz   |

<sup>38.</sup> Based on device characterization (Not production tested).

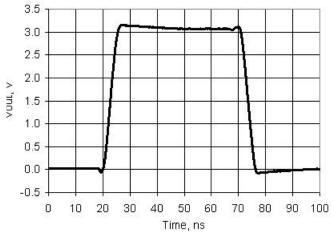

V<sub>DDD</sub> = 3.3 V, 25 pF Load

Table 11-16. USB Driver AC Specifications

| Parameter | Description                     | Conditions                                                                          | Min | Тур | Max  | Units |

|-----------|---------------------------------|-------------------------------------------------------------------------------------|-----|-----|------|-------|

| Tr        | Transition rise time            |                                                                                     | -   | -   | 20   | ns    |

| Tf        | Transition fall time            |                                                                                     | -   | -   | 20   | ns    |

| TR        | Rise/fall time matching         | V <sub>USB_5</sub> , V <sub>USB_3.3</sub> , see USB DC<br>Specifications on page 98 | 90% | -   | 111% |       |

| Vcrs      | Output signal crossover voltage |                                                                                     | 1.3 | -   | 2    | V     |

## 11.4.4 XRES

## Table 11-17. XRES DC Specifications

| Parameter       | Description                                                   | Conditions | Min                   | Тур | Max               | Units |

|-----------------|---------------------------------------------------------------|------------|-----------------------|-----|-------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  |            | $0.7 \times V_{DDIO}$ | _   | _                 | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   |            | -                     | -   | 0.3 ×             | V     |

|                 |                                                               |            |                       |     | V <sub>DDIO</sub> |       |

| Rpullup         | Pull-up resistor                                              |            | 3.5                   | 5.6 | 8.5               | kΩ    |

| C <sub>IN</sub> | Input capacitance <sup>[43]</sup>                             |            | -                     | 3   | -                 | pF    |

| V <sub>H</sub>  | Input voltage hysteresis<br>(Schmitt-Trigger) <sup>[43]</sup> |            | -                     | 100 | _                 | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |            | -                     | _   | 100               | μA    |

## Table 11-18. XRES AC Specifications

| Parameter          | Description       | Conditions | Min | Тур | Max | Units |

|--------------------|-------------------|------------|-----|-----|-----|-------|

| T <sub>RESET</sub> | Reset pulse width |            | 1   | -   | -   | μs    |

## Figure 11-52. Clock to Output Performance

## 11.7 Memory

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

### 11.7.1 Flash

### Table 11-45. Flash DC Specifications

| Parameter | Description               | Conditions           | Min  | Тур | Max | Units |

|-----------|---------------------------|----------------------|------|-----|-----|-------|

|           | Erase and program voltage | V <sub>DDD</sub> pin | 1.71 | _   | 5.5 | V     |

### Table 11-46. Flash AC Specifications

| Parameter                                                               | Description                       | Conditions                                                           | Min | Тур | Max | Units   |

|-------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------|-----|-----|-----|---------|

| T <sub>WRITE</sub>                                                      | Row write time (erase + program)  |                                                                      | -   | 15  | 20  | ms      |

| T <sub>ERASE</sub>                                                      | Row erase time                    |                                                                      | -   | 10  | 13  | ms      |

|                                                                         | Row program time                  |                                                                      | -   | 5   | 7   | ms      |

| T <sub>BULK</sub>                                                       | Bulk erase time (16 KB to 64 KB)  |                                                                      | -   | -   | 35  | ms      |

|                                                                         | Sector erase time (8 KB to 16 KB) |                                                                      | -   | -   | 15  | ms      |

| T <sub>PROG</sub>                                                       | Total device programming time     | No overhead <sup>[55]</sup>                                          | -   | 1.5 | 2   | seconds |

| Flash data retention time, retention period measured from last erase cy |                                   | Average ambient temp.<br>$T_A \le 55$ °C, 100 K erase/program cycles | 20  | -   | -   | years   |

|                                                                         |                                   | Average ambient temp.<br>$T_A \le 85$ °C, 10 K erase/program cycles  | 10  | -   | _   |         |

## 11.8 PSoC System Resources

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

### 11.8.1 POR with Brown Out

For brown out detect in regulated mode,  $V_{DDD}$  and  $V_{DDA}$  must be  $\geq$  2.0 V. Brown out detect is not available in externally regulated mode.

### Table 11-57. Precise Low-Voltage Reset (PRES) with Brown Out DC Specifications

| Parameter | Description          | Conditions   | Min  | Тур | Max  | Units |

|-----------|----------------------|--------------|------|-----|------|-------|

| PRESR     | Rising trip voltage  | Factory trim | 1.64 | -   | 1.68 | V     |

| PRESF     | Falling trip voltage |              | 1.62 | -   | 1.66 | V     |

### Table 11-58. Power-on Reset (POR) with Brown Out AC Specifications

| Parameter | Description                                   | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------------------------------|------------|-----|-----|-----|-------|

| PRES_TR   | Response time                                 |            | _   | _   | 0.5 | μs    |

|           | V <sub>DDD</sub> /V <sub>DDA</sub> droop rate | Sleep mode | -   | 5   | -   | V/sec |

### 11.8.2 Voltage Monitors

## Table 11-59. Voltage Monitors DC Specifications

| Parameter | Description              | Conditions | Min  | Тур  | Max  | Units |

|-----------|--------------------------|------------|------|------|------|-------|

| LVI       | Trip voltage             |            |      |      |      |       |

|           | LVI_A/D_SEL[3:0] = 0000b |            | 1.68 | 1.73 | 1.77 | V     |

|           | LVI_A/D_SEL[3:0] = 0001b |            | 1.89 | 1.95 | 2.01 | V     |

|           | LVI_A/D_SEL[3:0] = 0010b |            | 2.14 | 2.20 | 2.27 | V     |

|           | LVI_A/D_SEL[3:0] = 0011b |            | 2.38 | 2.45 | 2.53 | V     |

|           | LVI_A/D_SEL[3:0] = 0100b |            | 2.62 | 2.71 | 2.79 | V     |

|           | LVI_A/D_SEL[3:0] = 0101b |            | 2.87 | 2.95 | 3.04 | V     |

|           | LVI_A/D_SEL[3:0] = 0110b |            | 3.11 | 3.21 | 3.31 | V     |

|           | LVI_A/D_SEL[3:0] = 0111b |            | 3.35 | 3.46 | 3.56 | V     |

|           | LVI_A/D_SEL[3:0] = 1000b |            | 3.59 | 3.70 | 3.81 | V     |

|           | LVI_A/D_SEL[3:0] = 1001b |            | 3.84 | 3.95 | 4.07 | V     |

|           | LVI_A/D_SEL[3:0] = 1010b |            | 4.08 | 4.20 | 4.33 | V     |

|           | LVI_A/D_SEL[3:0] = 1011b |            | 4.32 | 4.45 | 4.59 | V     |

|           | LVI_A/D_SEL[3:0] = 1100b |            | 4.56 | 4.70 | 4.84 | V     |

|           | LVI_A/D_SEL[3:0] = 1101b |            | 4.83 | 4.98 | 5.13 | V     |

|           | LVI_A/D_SEL[3:0] = 1110b |            | 5.05 | 5.21 | 5.37 | V     |

|           | LVI_A/D_SEL[3:0] = 1111b |            | 5.30 | 5.47 | 5.63 | V     |

| HVI       | Trip voltage             |            | 5.57 | 5.75 | 5.92 | V     |

## Table 11-60. Voltage Monitors AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max | Units |

|-----------|-------------------------------|------------|-----|-----|-----|-------|

|           | Response time <sup>[64]</sup> |            | _   | -   | 1   | μs    |

| Descript<br>Docume | Description Title: PSoC <sup>®</sup> 3: CY8C32 Family Data Sheet Programmable System-on-Chip (PSoC <sup>®</sup> ) (continued)<br>Document Number: 001-56955 |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Revision           | ECN                                                                                                                                                         | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| *X                 | 4932879                                                                                                                                                     | 09/24/2015         | MKEA               | Changed the Regulator Output Capacitor min and max from "-" to 0.9 and 1.1,<br>respectively.<br>Added reference to AN54439 in Section 11.9.3.<br>Added MHz ECO DC specs table.<br>Removed references to IPOR rearm issues in Section 6.3.1.1.<br>Table 6-1: Changed DSI Fmax to 33 MHz.<br>Figure 6-1: Changed External I/O or DSI to 0-33 MHz.<br>Table 11-10: Changed Fgpioin Max to 33 MHz.<br>Table 11-12: Changed Fsioin Max to 33 MHz. |  |  |  |  |

| *Y                 | 5322536                                                                                                                                                     | 06/27/2016         | MKEA               | Updated More Information.<br>Corrected typos in External Electrical Connections.<br>Added links to CAD Libraries in Section 2.                                                                                                                                                                                                                                                                                                               |  |  |  |  |

# 18. Sales, Solutions, and Legal Information

## Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

## Products

| Automotive               | cypress.com/go/automotive |

|--------------------------|---------------------------|

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

| Memory                   | cypress.com/go/memory     |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

## **PSoC<sup>®</sup> Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Community | Forums | Blogs | Video | Training

Technical Support cypress.com/go/support

© Cypress Semiconductor Corporation, 2009-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and ober countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software in binary code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 001-56955 Rev. \*Y

Revised June 27, 2016