Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 50MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 48-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3246pvi-147t |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 3:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes and code examples covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 3 are:

- AN54181: Getting Started With PSoC 3

- AN61290: Hardware Design Considerations

- AN57821: Mixed Signal Circuit Board Layout

- AN58304: Pin Selection for Analog Designs

- AN81623: Digital Design Best Practices

- AN73854: Introduction To Bootloaders

using the PSoC Creator IDE C compiler

- Development Kits:

- CY8CKIT-030 is designed for analog performance, for developing high-precision analog, low-power, and low-voltage applications.

- CY8CKIT-001 provides a common development platform for any one of the PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP families of devices.

- The MiniProg3 device provides an interface for flash programming and debug.

- Technical Reference Manuals (TRM)

- Architecture TRM

- Registers TRM

- Programming Specification

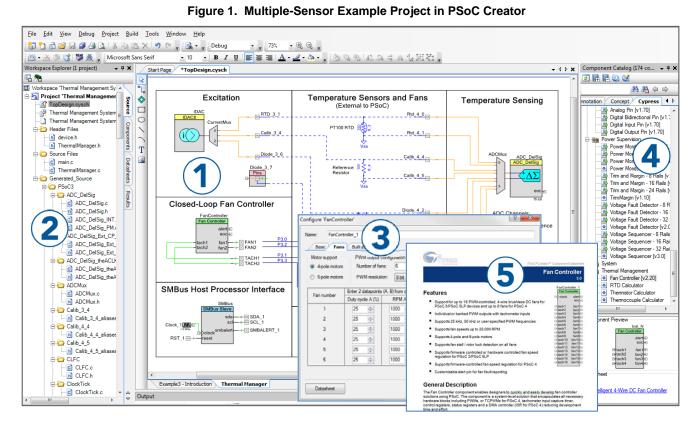

# PSoC Creator

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100 pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can:

1. Drag and drop component icons to build your hardware system design in the main design workspace

2. Codesign your application firmware with the PSoC hardware,

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- 5. Review component datasheets

# Document Number: 001-56955 Rev. \*Y

# Contents

| 1. Architectural Overview             | 4  |

|---------------------------------------|----|

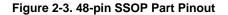

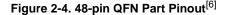

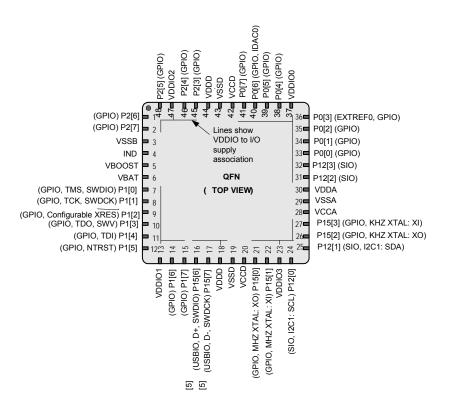

| 2. Pinouts                            | 6  |

| 3. Pin Descriptions                   | 12 |

| 4. CPU                                | 13 |

| 4.1 8051 CPU                          | 13 |

| 4.2 Addressing Modes                  |    |

| 4.3 Instruction Set                   |    |

| 4.4 DMA and PHUB                      |    |

| 4.5 Interrupt Controller              | 20 |

| 5. Memory                             | 24 |

| 5.1 Static RAM                        | 24 |

| 5.2 Flash Program Memory              | 24 |

| 5.3 Flash Security                    |    |

| 5.4 EEPROM                            |    |

| 5.5 Nonvolatile Latches (NVLs)        |    |

| 5.6 External Memory Interface         |    |

| 5.7 Memory Map                        |    |

| 6. System Integration                 |    |

| 6.1 Clocking System                   |    |

| 6.2 Power System                      |    |

| 6.3 Reset                             |    |

| 6.4 I/O System and Routing            |    |

| 7. Digital Subsystem                  |    |

| 7.1 Example Peripherals               |    |

| 7.2 Universal Digital Block           |    |

| 7.3 UDB Array Description             |    |

| 7.4 DSI Routing Interface Description |    |

| 7.5 USB                               |    |

| 7.6 Timers, Counters, and PWMs        |    |

| 7.7 l <sup>2</sup> C                  |    |

| 8. Analog Subsystem                   |    |

| 8.1 Analog Routing                    |    |

| 8.2 Delta-sigma ADC                   |    |

| 8.3 Comparators                       |    |

| 8.4 LCD Direct Drive<br>8.5 CapSense  |    |

| 8.6 Temp Sensor                       |    |

| 8.7 DAC                               |    |

|                                       | 01 |

| 9. Programming, Debug Interfaces, Resources      |     |

|--------------------------------------------------|-----|

| 9.1 JTAG Interface                               |     |

| 9.2 Serial Wire Debug Interface                  |     |

| 9.3 Debug Features<br>9.4 Trace Features         |     |

| 9.5 Single Wire Viewer Interface                 |     |

| 9.6 Programming Features                         |     |

| 9.7 Device Security                              |     |

| 9.8 CSP Package Bootloader                       |     |

| 10. Development Support                          | 66  |

| 10.1 Documentation                               |     |

| 10.2 Online                                      |     |

| 10.3 Tools                                       |     |

| 11. Electrical Specifications                    |     |

| 11.1 Absolute Maximum Ratings                    |     |

| 11.2 Device Level Specifications                 |     |

| 11.3 Power Regulators<br>11.4 Inputs and Outputs |     |

| 11.5 Analog Peripherals                          |     |

| 11.6 Digital Peripherals                         |     |

| 11.7 Memory                                      |     |

| 11.8 PSoC System Resources                       |     |

| 11.9 Clocking                                    | 107 |

| 12. Ordering Information                         |     |

| 12.1 Part Numbering Conventions                  |     |

| 13. Packaging                                    | 113 |

| 14. Acronyms                                     | 117 |

| 15. Reference Documents                          | 118 |

| 16. Document Conventions                         | 119 |

| 16.1 Units of Measure                            | 119 |

| 17. Revision History                             | 120 |

| 18. Sales, Solutions, and Legal Information      | 128 |

| Worldwide Sales and Design Support               |     |

| Products                                         |     |

| PSoC® Solutions                                  |     |

| Cypress Developer Community                      |     |

| Technical Support                                | 128 |

Notes

- 5. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

- The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices.

# USBIO, D+

Provides D+ connection directly to a USB 2.0 bus. May be used as a digital I/O pin. Pins are Do Not Use (DNU) on devices without USB.

## USBIO, D-

Provides D– connection directly to a USB 2.0 bus. May be used as a digital I/O pin. Pins are No Connect (NC) on devices without USB.

#### VBOOST

Power sense connection to boost pump.

#### VBAT

Battery supply to boost pump.

### VCCA.

Output of the analog core regulator or the input to the analog core. Requires a 1uF capacitor to VSSA. The regulator output is not designed to drive external circuits. Note that if you use the device with an external core regulator (externally regulated mode), the voltage applied to this pin must not exceed the allowable range of 1.71 V to 1.89 V. When using the internal core regulator, (internally regulated mode, the default), do not tie any power to this pin. For details see Power System on page 31.

#### VCCD.

Output of the digital core regulator or the input to the digital core. The two VCCD pins must be shorted together, with the trace between them as short as possible, and a 1uF capacitor to VSSD. The regulator output is not designed to drive external circuits. Note that if you use the device with an external core regulator (externally regulated mode), the voltage applied to this pin must not exceed the allowable range of 1.71 V to 1.89 V. When using the internal core regulator (internally regulated mode, the default), do not tie any power to this pin. For details see Power System on page 31.

#### VDDA

Supply for all analog peripherals and analog core regulator. VDDA must be the highest voltage present on the device. All other supply pins must be less than or equal to VDDA.

#### VDDD

Supply for all digital peripherals and digital core regulator. VDDD must be less than or equal to VDDA.

#### VSSA

Ground for all analog peripherals.

#### VSSB

Ground connection for boost pump.

#### VSSD

Ground for all digital logic and I/O pins.

#### VDDIO0, VDDIO1, VDDIO2, VDDIO3

Supply for I/O pins. See pinouts for specific I/O pin to VDDIO mapping. Each VDDIO must be tied to a valid operating voltage (1.71 V to 5.5 V), and must be less than or equal to VDDA.

# XRES (and configurable XRES)

External reset pin. Active low with internal pull-up. Pin P1[2] may be configured to be a XRES pin; see "Nonvolatile Latches (NVLs)" on page 25.

# 4. CPU

# 4.1 8051 CPU

The CY8C32 devices use a single cycle 8051 CPU, which is fully compatible with the original MCS-51 instruction set. The CY8C32 family uses a pipelined RISC architecture, which executes most instructions in 1 to 2 cycles to provide peak performance of up to 24 MIPS with an average of 2 cycles per instruction. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor.

The 8051 CPU subsystem includes these features:

- Single cycle 8051 CPU

- Up to 64 KB of flash memory, up to 2 KB of EEPROM, and up to 8 KB of SRAM

- 512-byte instruction cache between CPU and flash

- Programmable nested vector interrupt controller

- Direct memory access (DMA) controller

- Peripheral HUB (PHUB)

- External memory interface (EMIF)

# 4.2 Addressing Modes

The following addressing modes are supported by the 8051:

- Direct Addressing: The operand is specified by a direct 8-bit address field. Only the internal RAM and the SFRs can be accessed using this mode.

- Indirect Addressing: The instruction specifies the register which contains the address of the operand. The registers R0 or R1 are used to specify the 8-bit address, while the data pointer (DPTR) register is used to specify the 16-bit address.

- Register Addressing: Certain instructions access one of the registers (R0 to R7) in the specified register bank. These instructions are more efficient because there is no need for an address field.

- Register Specific Instructions: Some instructions are specific to certain registers. For example, some instructions always act on the accumulator. In this case, there is no need to specify the operand.

- Immediate Constants: Some instructions carry the value of the constants directly instead of an address.

- Indexed Addressing: This type of addressing can be used only for a read of the program memory. This mode uses the data pointer as the base and the accumulator value as an offset to read a program memory.

- Bit Addressing: In this mode, the operand is one of 256 bits.

#### 4.4.4.5 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

#### 4.4.4.6 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase "subchains" can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

#### 4.4.4.7 Nested DMA

One TD may modify another TD, as the TD configuration space is memory mapped similar to any other peripheral. For example, a first TD loads a second TD's configuration and then calls the second TD. The second TD moves data as required by the application. When complete, the second TD calls the first TD, which again updates the second TD's configuration. This process repeats as often as necessary.

#### 4.5 Interrupt Controller

The interrupt controller provides a mechanism for hardware resources to change program execution to a new address, independent of the current task being executed by the main code. The interrupt controller provides enhanced features not found on original 8051 interrupt controllers:

- Thirty two interrupt vectors

- Jumps directly to ISR anywhere in code space with dynamic vector addresses

- Multiple sources for each vector

- Flexible interrupt to vector matching

- Each interrupt vector is independently enabled or disabled

- Each interrupt can be dynamically assigned one of eight priorities

- Eight level nestable interrupts

- Multiple I/O interrupt vectors

- Software can send interrupts

- Software can clear pending interrupts

When an interrupt is pending, the current instruction is completed and the program counter is pushed onto the stack. Code execution then jumps to the program address provided by the vector. After the ISR is completed, a RETI instruction is executed and returns execution to the instruction following the previously interrupted instruction. To do this the RETI instruction pops the program counter from the stack.

If the same priority level is assigned to two or more interrupts, the interrupt with the lower vector number is executed first. Each interrupt vector may choose from three interrupt sources: Fixed Function, DMA, and UDB. The fixed function interrupts are direct connections to the most common interrupt sources and provide the lowest resource cost connection. The DMA interrupt sources provide direct connections to the two DMA interrupt sources provided per DMA channel. The third interrupt source for vectors is from the UDB digital routing array. This allows any digital signal available to the UDB array to be used as an interrupt source. Fixed function interrupts and all interrupt sources may be routed to any interrupt vector using the UDB interrupt source connections.

Figure 4-2 on page 21 represents typical flow of events when an interrupt triggered. Figure 4-3 on page 22 shows the interrupt structure and priority polling.

# 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2.

Table 5-2.

Device Configuration NVL Register Map

| Register Address | 7       | 6                   | 5                         | 4                                      | 3            | 2                                   | 1     | 0                         |  |      |          |

|------------------|---------|---------------------|---------------------------|----------------------------------------|--------------|-------------------------------------|-------|---------------------------|--|------|----------|

| 0x00             | PRT3RE  | M[1:0] PRT2RDM[1:0] |                           | PRT3RDM[1:0] PRT2RDM[1:0] PRT1RDM[1:0] |              | 3RDM[1:0] PRT2RDM[1:0] PRT1RDM[1:0] |       | PRT2RDM[1:0] PRT1RDM[1:0] |  | PRT0 | RDM[1:0] |

| 0x01             | PRT12R  | DM[1:0]             | PRT6RDM[1:0] PRT5RDM[1:0] |                                        | PRT6RDM[1:0] |                                     | PRT4  | RDM[1:0]                  |  |      |          |

| 0x02             | XRESMEN | DBGEN               |                           |                                        | PRT18        | 5RDM[1:0]                           |       |                           |  |      |          |

| 0x03             |         | DIG_PHS_I           | DLY[3:0] ECCEN DPS        |                                        | DLY[3:0]     |                                     | [1:0] |                           |  |      |          |

The details for individual fields and their factory default settings are shown in Table 5-3:.

### Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                                        | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     | Controls reset drive mode of the corresponding IO port.<br>See "Reset Configuration" on page 44. All pins of the<br>port are set to the same mode. | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as an external reset. See "Pin Descriptions" on page 12, XRES description.                         | 0 (default for 68-pin 72-pin, and 100-pin parts) - GPIO<br>1 (default for 48-pin parts) - external reset                      |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                                       | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| DPS[1:0]         |                                                                                                                                                    | 00b - 5-wire JTAG<br>01b (default) - 4-wire JTAG<br>10b - SWD<br>11b - debug ports disabled                                   |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 24.                   | 0 - ECC disabled<br>1 (default) - ECC enabled                                                                                 |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                                             | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase / write cycles is limited – see "Nonvolatile Latches (NVL))" on page 100.

# 6.2.1 Power Modes

PSoC 3 devices have four different power modes, as shown in Table 6-2 and Table 6-3. The power modes allow a design to easily provide required functionality and processing power while simultaneously minimizing power consumption and maximizing battery life in low-power and portable devices.

PSoC 3 power modes, in order of decreasing power consumption are:

- Active

- Alternate Active

- Sleep

- Hibernate

#### Table 6-2. Power Modes

Active is the main processing mode. Its functionality is configurable. Each power controllable subsystem is enabled or disabled by using separate power configuration template registers. In alternate active mode, fewer subsystems are enabled, reducing power. In sleep mode most resources are disabled regardless of the template settings. Sleep mode is optimized to provide timed sleep intervals and RTC functionality. The lowest power mode is hibernate, which retains register and SRAM state, but no clocks, and allows wakeup only from I/O pins. Figure 6-5 illustrates the allowable transitions between power modes. Sleep and hibernate modes should not be entered until all VDDIO supplies are at valid voltage levels.

| Power Modes         | Description                                                                                                                                                                                                                    | <b>Entry Condition</b>                     | Wakeup Source                                           | Active Clocks         | Regulator                                                                                                                         |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Active              | Primary mode of operation, all<br>peripherals available (program-<br>mable)                                                                                                                                                    | Wakeup, reset,<br>manual register<br>entry | Any interrupt                                           | Any<br>(programmable) | All regulators available.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used.                     |

| Alternate<br>Active | Similar to Active mode, and is<br>typically configured to have<br>fewer peripherals active to<br>reduce power. One possible<br>configuration is to use the UDBs<br>for processing, with the CPU<br>turned off                  | Manual register<br>entry                   | Any interrupt                                           | Any<br>(programmable) | All regulators available.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used.                     |

| Sleep               | All subsystems automatically disabled                                                                                                                                                                                          | Manual register<br>entry                   | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | ILO/kHzECO            | Both digital and analog<br>regulators buzzed.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used. |

| Hibernate           | All subsystems automatically<br>disabled<br>Lowest power consuming mode<br>with all peripherals and internal<br>regulators disabled, except<br>hibernate regulator is enabled<br>Configuration and memory<br>contents retained | Manual register<br>entry                   | PICU                                                    |                       | Only hibernate regulator active.                                                                                                  |

#### Table 6-3. Power Modes Wakeup Time and Power Consumption

| Sleep<br>Modes      | Wakeup<br>Time | Current<br>(typ)       | Code<br>Execution | Digital<br>Resources | Analog<br>Resources | Clock Sources<br>Available | Wakeup Sources                                          | Reset<br>Sources  |

|---------------------|----------------|------------------------|-------------------|----------------------|---------------------|----------------------------|---------------------------------------------------------|-------------------|

| Active              | _              | 1.2 mA <sup>[11]</sup> | Yes               | All                  | All                 | All                        | -                                                       | All               |

| Alternate<br>Active | -              | -                      | User<br>defined   | All                  | All                 | All                        | _                                                       | All               |

| Sleep               | <15 µs         | 1 µA                   | No                | l <sup>2</sup> C     | Comparator          | ILO/kHzECO                 | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | XRES, LVD,<br>WDR |

| Hibernate           | <100 µs        | 200 nA                 | No                | None                 | None                | None                       | PICU                                                    | XRES              |

Note

11. Bus clock off. Execute from cache at 6 MHz. See Table 11-2 on page 68.

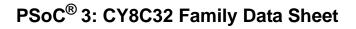

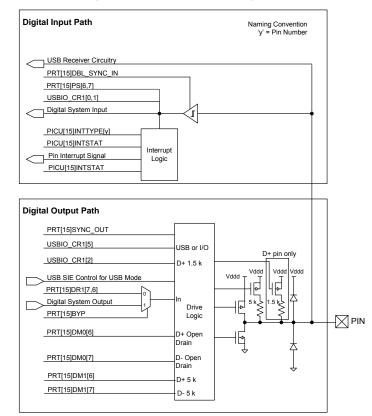

# Figure 6-9. GPIO Block Diagram

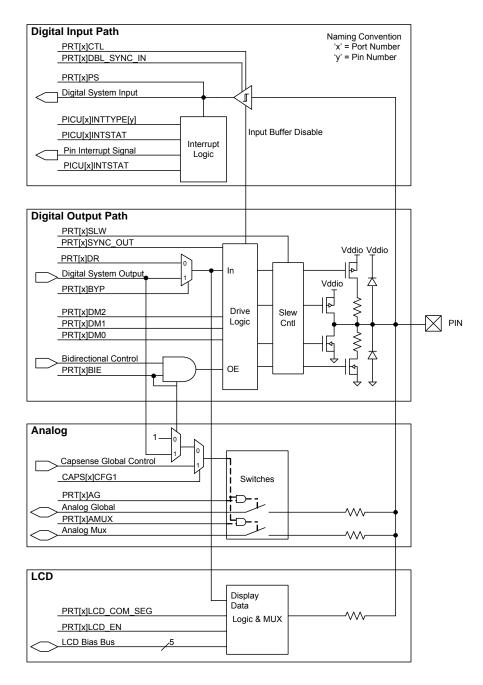

### Figure 6-10. SIO Input/Output Block Diagram

Figure 6-11. USBIO Block Diagram

#### 6.4.13 SIO as Comparator

This section applies only to SIO pins. The adjustable input level feature of the SIOs as explained in the Adjustable Input Level section can be used to construct a comparator. The threshold for the comparator is provided by the SIO's reference generator. The reference generator has the option to set the analog signal routed through the analog global line as threshold for the comparator. Note that a pair of SIO pins share the same threshold.

The digital input path in Figure 6-10 on page 40 illustrates this functionality. In the figure, 'Reference level' is the analog signal routed through the analog global. The hysteresis feature can also be enabled for the input buffer of the SIO, which increases noise immunity for the comparator.

#### 6.4.14 Hot Swap

This section applies only to SIO pins. SIO pins support 'hot swap' capability to plug into an application without loading the signals that are connected to the SIO pins even when no power is applied to the PSoC device. This allows the unpowered PSoC to maintain a high impedance load to the external device while also preventing the PSoC from being powered through a SIO pin's protection diode.

Powering the device up or down while connected to an operational  $I^2C$  bus may cause transient states on the SIO pins. The overall  $I^2C$  bus design should take this into account.

#### 6.4.15 Over Voltage Tolerance

All I/O pins provide an over voltage tolerance feature at any operating VDD.

- There are no current limitations for the SIO pins as they present a high impedance load to the external circuit where VDDIO < VIN ≤ 5.5 V.

- The GPIO pins must be limited to 100 µA using a current limiting resistor. GPIO pins clamp the pin voltage to approximately one diode above the VDDIO supply where VDDIO < VIN < VDDA.</p>

- In case of a GPIO pin configured for analog input/output, the analog voltage on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs.

A common application for this feature is connection to a bus such as I<sup>2</sup>C where different devices are running from different supply voltages. In the I<sup>2</sup>C case, the PSoC chip is configured into the Open Drain, Drives Low mode for the SIO pin. This allows an external pull-up to pull the I<sup>2</sup>C bus voltage above the PSoC pin supply. For example, the PSoC chip could operate at 1.8 V, and an external device could run from 5 V. Note that the SIO pin's V<sub>IH</sub> and V<sub>IL</sub> levels are determined by the associated V<sub>DDIO</sub> supply pin.

The SIO pin must be in one of the following modes: 0 (high impedance analog), 1 (high impedance digital), or 4 (open drain drives low). See Figure 6-12 for details. Absolute maximum ratings for the device must be observed for all I/O pins.

#### 6.4.16 Reset Configuration

While reset is active all I/Os are reset to and held in the High Impedance Analog state. After reset is released, the state can be reprogrammed on a port-by-port basis to pull-down or pull-up. To ensure correct reset operation, the port reset configuration data is stored in special nonvolatile registers. The stored reset data is automatically transferred to the port reset configuration registers at reset release.

#### 6.4.17 Low-Power Functionality

In all low-power modes the I/O pins retain their state until the part is awakened and changed or reset. To awaken the part, use a pin interrupt, because the port interrupt logic continues to function in all low-power modes.

#### 6.4.18 Special Pin Functionality

Some pins on the device include additional special functionality in addition to their GPIO or SIO functionality. The specific special function pins are listed in Pinouts on page 6. The special features are:

- Digital

- 4- to 25- MHz crystal oscillator

- □ 32.768-kHz crystal oscillator

- Wake from sleep on I<sup>2</sup>C address match. Any pin can be used for I<sup>2</sup>C if wake from sleep is not required.

- JTAG interface pins

- SWD interface pins

- SWV interface pins

- External reset

- Analog

- High current IDAC output

- External reference inputs

#### 6.4.19 JTAG Boundary Scan

The device supports standard JTAG boundary scan chains on all I/O pins for board level test.

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

### 7.2.2.3 Conditionals

Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers in a variety of configurations. Other conditions include zero detect, all ones detect, and overflow. These conditions are the primary datapath outputs, a selection of which can be driven out to the UDB routing matrix. Conditional computation can use the built in chaining to neighboring UDBs to operate on wider data widths without the need to use routing resources.

#### 7.2.2.4 Variable MSB

The most significant bit of an arithmetic and shift function can be programmatically specified. This supports variable width CRC and PRS functions, and in conjunction with ALU output masking, can implement arbitrary width timers, counters and shift blocks.

### 7.2.2.5 Built in CRC/PRS

The datapath has built in support for single cycle Cyclic Redundancy Check (CRC) computation and Pseudo Random Sequence (PRS) generation of arbitrary width and arbitrary polynomial. CRC/PRS functions longer than 8 bits may be implemented in conjunction with PLD logic, or built in chaining may be use to extend the function into neighboring UDBs.

#### 7.2.2.6 Input/Output FIFOs

Each datapath contains two four-byte deep FIFOs, which can be independently configured as an input buffer (system bus writes to the FIFO, datapath internal reads the FIFO), or an output buffer (datapath internal writes to the FIFO, the system bus reads from the FIFO). The FIFOs generate status that are selectable as datapath outputs and can therefore be driven to the routing, to interact with sequencers, interrupts, or DMA.

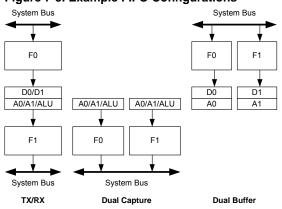

#### Figure 7-5. Example FIFO Configurations

# 7.2.2.7 Chaining

The datapath can be configured to chain conditions and signals such as carries and shift data with neighboring datapaths to create higher precision arithmetic, shift, CRC/PRS functions.

#### 7.2.2.8 Time Multiplexing

In applications that are over sampled, or do not need high clock rates, the single ALU block in the datapath can be efficiently shared with two sets of registers and condition generators. Carry and shift out data from the ALU are registered and can be selected as inputs in subsequent cycles. This provides support for 16-bit functions in one (8-bit) datapath.

### 7.2.2.9 Datapath I/O

There are six inputs and six outputs that connect the datapath to the routing matrix. Inputs from the routing provide the configuration for the datapath operation to perform in each cycle, and the serial data inputs. Inputs can be routed from other UDB blocks, other device peripherals, device I/O pins, and so on. The outputs to the routing can be selected from the generated conditions, and the serial data outputs. Outputs can be routed to other UDB blocks, device peripherals, interrupt and DMA controller, I/O pins, and so on.

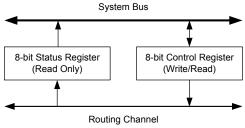

#### 7.2.3 Status and Control Module

The primary purpose of this circuitry is to coordinate CPU firmware interaction with internal UDB operation.

### Figure 7-6. Status and Control Registers

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

#### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

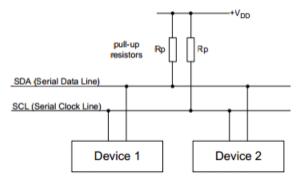

#### Figure 7-17. Connection of Devices to the I<sup>2</sup>C Bus

For most designs, the default values in Table 7-2 will provide excellent performance without any calculations. The default values were chosen to use standard resistor values between the minimum and maximum limits. The values in Table 7-2 work for designs with 1.8 V to 5.0V V<sub>DD</sub>, less than 200-pF bus capacitance (C<sub>B</sub>), up to 25  $\mu$ A of total input leakage (I<sub>IL</sub>), up to 0.4 V output voltage level (V<sub>OL</sub>), and a max V<sub>IH</sub> of 0.7 \* V<sub>DD</sub>. Standard Mode and Fast Mode can use either GPIO or SIO PSoC pins. Fast Mode Plus requires use of SIO pins to meet the V<sub>OL</sub> spec at 20 mA. Calculation of custom pull-up resistor values is required; if your design does not meet the default assumptions, you use series resistor value for low power consumption.

Table 7-2. Recommended default Pull-up Resistor Values

|                          | R <sub>P</sub> | Units |

|--------------------------|----------------|-------|

| Standard Mode – 100 kbps | 4.7 k, 5%      | Ω     |

| Fast Mode – 400 kbps     | 1.74 k, 1%     | Ω     |

| Fast Mode Plus – 1 Mbps  | 620, 5%        | Ω     |

Calculation of the ideal pull-up resistor value involves finding a value between the limits set by three equations detailed in the NXP  $I^2C$  specification. These equations are:

#### Equation 1:

$$R_{PMIN} = (V_{DD}(max) - V_{OL}(max))/(I_{OL}(min))$$

Equation 2:

$$R_{PMAX} = T_R(max)/0.8473 \times C_R(max)$$

### **Equation 3:**

$R_{PMAX} = V_{DD}(min) - V_{IH}(min) + V_{NH}(min) / I_{IH}(max)$

Equation parameters:

$V_{DD}$  = Nominal supply voltage for I<sup>2</sup>C bus

$V_{OL}$  = Maximum output low voltage of bus devices.

$I_{OL}$  = Low-level output current from I<sup>2</sup>C specification

$T_R$  = Rise Time of bus from I<sup>2</sup>C specification

C<sub>B</sub> = Capacitance of each bus line including pins and PCB traces

VIH = Minimum high-level input voltage of all bus devices

$V_{\text{NH}}$  = Minimum high-level input noise margin from  $\text{I}^2\text{C}$  specification

I<sub>IH</sub> = Total input leakage current of all devices on the bus

The supply voltage (V<sub>DD</sub>) limits the minimum pull-up resistor value due to bus devices maximum low output voltage (V<sub>DL</sub>) specifications. Lower pull-up resistance increases current through the pins and can, therefore, exceed the spec conditions of V<sub>OL</sub>. Equation 1 is derived using Ohm's law to determine the minimum resistance that will still meet the V<sub>OL</sub> specification at 3 mA for standard and fast modes, and 20 mA for fast mode plus at the given V<sub>DD</sub>.

Equation 2 determines the maximum pull-up resistance due to bus capacitance. Total bus capacitance is comprised of all pin, wire, and trace capacitance on the bus. The higher the bus capacitance, the lower the pull-up resistance required to meet the specified bus speeds rise time due to RC delays. Choosing a pull-up resistance higher than allowed can result in failing timing requirements resulting in communication errors. Most designs with five or less  $I^2C$  devices and up to 20 centimeters of bus trace length have less than 100 pF of bus capacitance.

A secondary effect that limits the maximum pull-up resistor value is total bus leakage calculated in Equation 3. The primary source of leakage is I/O pins connected to the bus. If leakage is too high, the pull-ups will have difficulty maintaining an acceptable  $V_{IH}$  level causing communication errors. Most designs with five or less I<sup>2</sup>C devices on the bus have less than 10 µA of total leakage current.

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in CY8C32, four in the left half (abusl [0:3]) and four in the right half (abusr [0:3]) as shown in Figure 8-2. Using the abus saves the analog globals and analog mux buses from being used for interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct signals into and out of the analog blocks. A multiplexer can have only one connection on at a time, whereas a switch can have multiple connections on simultaneously. In Figure 8-2, multiplexers are indicated by grayed ovals and switches are indicated by transparent ovals.

# 8.2 Delta-sigma ADC

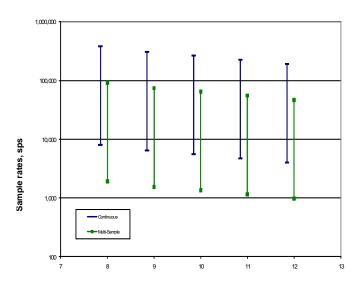

The CY8C32 device contains one delta-sigma ADC. This ADC offers differential input, high resolution and excellent linearity, making it a good ADC choice for measurement applications. The converter can be configured to output 12-bit resolution at data rates of up to 192 ksps. At a fixed clock rate, resolution can be traded for faster data rates as shown in Table 8-1 and Figure 8-3.

| Table 8-1. | Delta-sigma | ADC | Performance |

|------------|-------------|-----|-------------|

|------------|-------------|-----|-------------|

| Bits | Maximum Sample Rate<br>(sps) | SINAD (dB) |

|------|------------------------------|------------|

| 12   | 192 k                        | 66         |

| 8    | 384 k                        | 43         |

#### Figure 8-3. Delta-sigma ADC Sample Rates, Range = ±1.024 V

#### 8.2.1 Functional Description

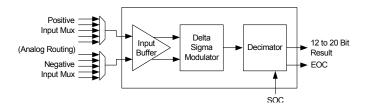

The ADC connects and configures three basic components, input buffer, delta-sigma modulator, and decimator. The basic block diagram is shown in Figure 8-4. The signal from the input muxes is delivered to the delta-sigma modulator either directly or through the input buffer. The delta-sigma modulator performs the actual analog to digital conversion. The modulator over-samples the input and generates a serial data stream output. This high

speed data stream is not useful for most applications without some type of post processing, and so is passed to the decimator through the Analog Interface block. The decimator converts the high speed serial data stream into parallel ADC results. The modulator/decimator frequency response is  $[(\sin x)/x]^4$ .

#### Figure 8-4. Delta-sigma ADC Block Diagram

Resolution and sample rate are controlled by the Decimator. Data is pipelined in the decimator; the output is a function of the last four samples. When the input multiplexer is switched, the output data is not valid until after the fourth sample after the switch.

#### 8.2.2 Operational Modes

The ADC can be configured by the user to operate in one of four modes: Single Sample, Multi Sample, Continuous, or Multi Sample (Turbo). All four modes are started by either a write to the start bit in a control register or an assertion of the Start of Conversion (SoC) signal. When the conversion is complete, a status bit is set and the output signal End of Conversion (EoC) asserts high and remains high until the value is read by either the DMA controller or the CPU.

#### 8.2.2.1 Single Sample

In Single Sample mode, the ADC performs one sample conversion on a trigger. In this mode, the ADC stays in standby state waiting for the SoC signal to be asserted. When SoC is signaled the ADC performs four successive conversions. The first three conversions prime the decimator. The ADC result is valid and available after the fourth conversion, at which time the EoC signal is generated. To detect the end of conversion, the system may poll a control register for status or configure the external EoC signal to generate an interrupt or invoke a DMA request. When the transfer is done the ADC reenters the standby state where it stays until another SoC event.

#### 8.2.2.2 Continuous

Continuous sample mode is used to take multiple successive samples of a single input signal. Multiplexing multiple inputs should not be done with this mode. There is a latency of three conversion times before the first conversion result is available. This is the time required to prime the decimator. After the first result, successive conversions are available at the selected sample rate.

#### 8.2.2.3 Multi Sample

Multi sample mode is similar to continuous mode except that the ADC is reset between samples. This mode is useful when the input is switched between multiple signals. The decimator is re-primed between each sample so that previous samples do not affect the current conversion. Upon completion of a sample, the next sample is automatically initiated. The results can be transferred using either firmware polling, interrupt, or DMA.

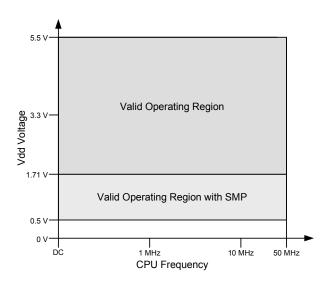

# Table 11-3. AC Specifications<sup>[30]</sup>

| Parameter              | Description                                                                                                               | Conditions                                                                                            | Min | Тур | Max   | Units |

|------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|-------|-------|

| F <sub>CPU</sub>       | CPU frequency                                                                                                             | $1.71~V \le V_{DDD} \le 5.5~V$                                                                        | DC  | -   | 50.01 | MHz   |

| F <sub>BUSCLK</sub>    | Bus frequency                                                                                                             | $1.71~V \le V_{DDD} \le 5.5~V$                                                                        | DC  | -   | 50.01 | MHz   |

| Svdd                   | V <sub>DD</sub> ramp rate                                                                                                 |                                                                                                       | -   | -   | 0.066 | V/µs  |

| T <sub>IO_INIT</sub>   | Time from $V_{DDD}/V_{DDA}/V_{CCD}/V_{CCA} \ge IPOR$ to I/O ports set to their reset states                               |                                                                                                       | -   | -   | 10    | μs    |

| T <sub>STARTUP</sub>   | Time from $V_{DDD}/V_{DDA}/V_{CCD}/V_{CCA} \ge PRES$ to CPU executing code at reset vector                                | $V_{CCA}/V_{CCD}$ = regulated from<br>$V_{DDA}/V_{DDD}$ , no PLL used, IMO<br>boot mode (12 MHz typ.) | -   | -   | 74    | μs    |

| T <sub>SLEEP</sub>     | Wakeup from sleep mode –<br>Application of non-LVD interrupt to<br>beginning of execution of next CPU<br>instruction      |                                                                                                       | -   | -   | 15    | μs    |

| T <sub>HIBERNATE</sub> | Wakeup from hibernate mode –<br>Application of external interrupt to<br>beginning of execution of next CPU<br>instruction |                                                                                                       | _   | -   | 100   | μs    |

Figure 11-4. F<sub>CPU</sub> vs. V<sub>DD</sub>

Note 30. Based on device characterization (Not production tested).

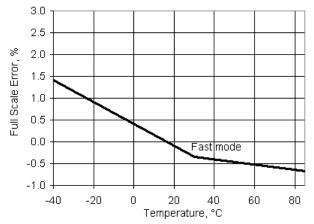

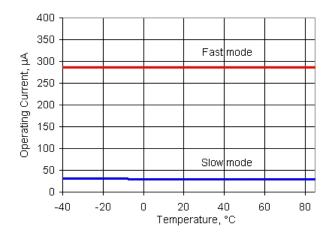

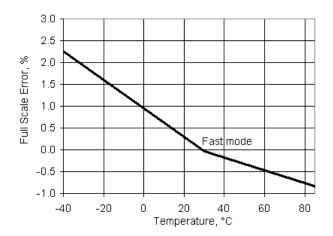

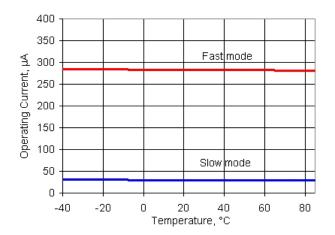

Figure 11-34. IDAC Operating Current vs Temperature, Range =  $255 \mu$ A, Code = 0, Source Mode

Figure 11-33. IDAC Full Scale Error vs Temperature, Range =  $255 \mu$ A, Sink Mode

Figure 11-35. IDAC Operating Current vs Temperature, Range = 255  $\mu$ A, Code = 0, Sink Mode

# 11.5.6 Voltage Digital to Analog Converter (VDAC)

See the VDAC component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

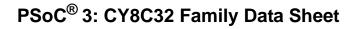

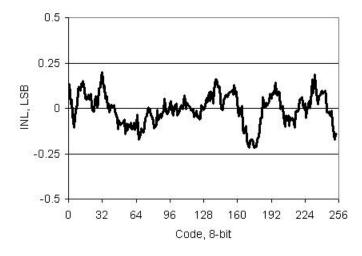

# Table 11-28. VDAC DC Specifications

| Parameter        | Description                               | Conditions                        | Min | Тур  | Max  | Units   |

|------------------|-------------------------------------------|-----------------------------------|-----|------|------|---------|

|                  | Resolution                                |                                   | -   | 8    | -    | bits    |

| INL1             | Integral nonlinearity                     | 1 V scale                         | -   | ±2.1 | ±2.5 | LSB     |

| INL4             | Integral nonlinearity <sup>[52]</sup>     | 4 V scale                         | -   | ±2.1 | ±2.5 | LSB     |

| DNL1             | Differential nonlinearity                 | 1 V scale                         | -   | ±0.3 | ±1   | LSB     |

| DNL4             | Differential nonlinearity <sup>[52]</sup> | 4 V scale                         | -   | ±0.3 | ±1   | LSB     |

| Rout             | Output resistance                         | 1 V scale                         | -   | 4    | -    | kΩ      |

|                  |                                           | 4 V scale                         | -   | 16   | -    | kΩ      |

| V <sub>OUT</sub> | Output voltage range, code = 255          | 1 V scale                         | -   | 1.02 | -    | V       |

|                  |                                           | 4 V scale, V <sub>DDA</sub> = 5 V | -   | 4.08 | -    | V       |

|                  | Monotonicity                              |                                   | -   | -    | Yes  | -       |

| V <sub>OS</sub>  | Zero scale error                          |                                   | -   | 0    | ±0.9 | LSB     |

| Eg               | Gain error                                | 1 V scale                         | -   | -    | ±2.5 | %       |

|                  |                                           | 4 V scale                         | -   | -    | ±2.5 | %       |

| TC_Eg            | Temperature coefficient, gain error       | 1 V scale                         | -   | -    | 0.03 | %FSR/°C |

|                  |                                           | 4 V scale                         | -   | -    | 0.03 | %FSR/°C |

| I <sub>DD</sub>  | Operating current                         | Low speed mode                    | -   | -    | 100  | μA      |

|                  |                                           | High speed mode                   | -   | -    | 500  | μA      |

# Figure 11-40. VDAC INL vs Input Code, 1 V Mode

# Figure 11-41. VDAC DNL vs Input Code, 1 V Mode

Note 52. Based on device characterization (Not production tested).

# 11.5.7 Temperature Sensor

# Table 11-30. Temperature Sensor Specifications

| Parameter | Description          | Conditions              | Min | Тур | Max | Units |

|-----------|----------------------|-------------------------|-----|-----|-----|-------|

|           | Temp sensor accuracy | Range: –40 °C to +85 °C | -   | ±5  | _   | °C    |

11.5.8 LCD Direct Drive

# Table 11-31. LCD Direct Drive DC Specifications

| Parameter           | Description                                                                         | Conditions                                                                                                                                                                                 | Min | Тур                    | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|------|-------|

| Icc                 | LCD system operating current                                                        | Device sleep mode with wakeup at 400-Hz rate to refresh LCDs, bus clock = 3 MHz, $V_{DDIO} = V_{DDA} = 3 V$ , 4 commons, 16 segments, 1/4 duty cycle, 50 Hz frame rate, no glass connected | -   | 38                     | -    | μΑ    |

| I <sub>CC_SEG</sub> | Current per segment driver                                                          | Strong drive mode                                                                                                                                                                          | -   | 260                    | -    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $V_{DDA} \geq 3~V$ and $V_{DDA} \geq V_{BIAS}$                                                                                                                                             | 2   | -                      | 5    | V     |

|                     | LCD bias step size                                                                  | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                | -   | 9.1 × V <sub>DDA</sub> | -    | mV    |

|                     | LCD capacitance per<br>segment/common driver                                        | Drivers may be combined                                                                                                                                                                    | _   | 500                    | 5000 | pF    |

|                     | Long term segment offset                                                            |                                                                                                                                                                                            | -   | -                      | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver)                                            | V <sub>DDIO</sub> = 5.5V, strong drive mode                                                                                                                                                | 355 | -                      | 710  | μA    |

# Table 11-32. LCD Direct Drive AC Specifications

| Parameter        | Description    | Conditions | Min | Тур | Max | Units |

|------------------|----------------|------------|-----|-----|-----|-------|

| f <sub>LCD</sub> | LCD frame rate |            | 10  | 50  | 150 | Hz    |

# 12. Ordering Information

In addition to the features listed in Table 12-1, every CY8C32 device includes: a precision on-chip voltage reference, precision oscillators, flash, ECC, DMA, a fixed function I<sup>2</sup>C, 4 KB trace RAM, JTAG/SWD programming and debug, external memory interface, and more. In addition to these features, the flexible UDBs and analog subsection support a wide range of peripherals. To assist you in selecting the ideal part, PSoC Creator makes a part recommendation after you choose the components required by your application. All CY8C32 derivatives incorporate device and flash security in user-selectable security levels; see the TRM for details.

|                 | Γ               | MCU Core   |           |             |                   | Analog         |     |            |                     |        |     |          |                      | Dig              | gital  |          | <b>I/O</b> <sup>[76]</sup> |      |     |       |              |                         |

|-----------------|-----------------|------------|-----------|-------------|-------------------|----------------|-----|------------|---------------------|--------|-----|----------|----------------------|------------------|--------|----------|----------------------------|------|-----|-------|--------------|-------------------------|

| Part Number     | CPU Speed (MHz) | Flash (KB) | SRAM (KB) | EEPROM (KB) | LCD Segment Drive | ADC            | DAC | Comparator | SC/CT Analog Blocks | Opamps | DFB | CapSense | UDBs <sup>[75]</sup> | 16-bit Timer/PWM | FS USB | CAN 2.0b | Total I/O                  | GPIO | SIO | USBIO | Package      | JTAG ID <sup>[77]</sup> |

| 16 KB Flash     |                 |            |           |             |                   |                |     |            |                     |        |     |          |                      |                  |        |          |                            |      |     |       |              |                         |

| CY8C3244AXI-153 | 50              | 16         | 2         | 0.5         | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | _   | ~        | 16                   | 4                | -      | -        | 70                         | 62   | 8   | 0     | 100-pin TQFP | 0×1E099069              |

| CY8C3244LTI-130 | 50              | 16         | 2         | 0.5         | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | -   | ~        | 16                   | 4                | -      | -        | 46                         | 38   | 8   | 0     | 68-pin QFN   | 0×1E082069              |

| CY8C3244LTI-123 | 50              | 16         | 2         | 0.5         | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | -   | ~        | 16                   | 4                | -      | -        | 29                         | 25   | 4   | 0     | 48-pin QFN   | 0×1E07B069              |

| CY8C3244PVI-133 | 50              | 16         | 2         | 0.5         | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | I   | ~        | 16                   | 4                | -      | -        | 29                         | 25   | 4   | 0     | 48-pin SSOP  | 0×1E085069              |

| 32 KB Flash     |                 |            |           |             |                   |                |     |            |                     |        |     |          |                      |                  |        |          |                            |      |     |       |              |                         |

| CY8C3245AXI-158 | 50              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | -   | ~        | 20                   | 4                | -      | -        | 70                         | 62   | 8   | 0     | 100-pin TQFP | 0×1E09E069              |

| CY8C3245LTI-163 | 50              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | I   | ~        | 20                   | 4                | -      | -        | 46                         | 38   | 8   | 0     | 68-pin QFN   | 0×1E0A3069              |

| CY8C3245LTI-139 | 50              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | -   | ~        | 20                   | 4                | -      | -        | 29                         | 25   | 4   | 0     | 48-pin QFN   | 0×1E08B069              |

| CY8C3245PVI-134 | 50              | 32         | 4         | 1           | ۲                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | -   | ~        | 20                   | 4                | -      | -        | 29                         | 25   | 4   | 0     | 48-pin SSOP  | 0×1E086069              |

| CY8C3245AXI-166 | 50              | 32         | 4         | 1           | 2                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | I   | ~        | 20                   | 4                | ~      | -        | 72                         | 62   | 8   | 2     | 100-pin TQFP | 0×1E0A6069              |

| CY8C3245LTI-144 | 50              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | -   | ~        | 20                   | 4                | ~      | -        | 31                         | 25   | 4   | 2     | 48-pin QFN   | 0×1E090069              |

| CY8C3245PVI-150 | 50              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | -   | ~        | 20                   | 4                | ~      | -        | 31                         | 25   | 4   | 2     | 48-pin SSOP  | 0×1E096069              |

| CY8C3245FNI-212 | 50              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | -   | ~        | 20                   | 4                | -      | -        | 46                         | 38   | 8   | 0     | 72-pin WLCSP | 0x1E0D4069              |

| 64 KB Flash     |                 |            |           |             |                   |                |     |            |                     |        |     |          |                      |                  |        |          |                            |      |     |       |              |                         |

| CY8C3246LTI-149 | 50              | 64         | 8         | 2           | ۲                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | -   | ~        | 24                   | 4                | -      | -        | 46                         | 38   | 8   | 0     | 68-pin QFN   | 0×1E095069              |

| CY8C3246PVI-147 | 50              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | I   | ~        | 24                   | 4                | ~      | -        | 31                         | 25   | 4   | 2     | 48-pin SSOP  | 0×1E093069              |

| CY8C3246AXI-131 | 50              | 64         | 8         | 2           | 5                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | I   | ~        | 24                   | 4                | -      | -        | 70                         | 62   | 8   | 0     | 100-pin TQFP | 0×1E083069              |

| CY8C3246LTI-162 | 50              | 64         | 8         | 2           | 5                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | I   | ~        | 24                   | 4                | -      | -        | 29                         | 25   | 4   | 0     | 48-pin QFN   | 0×1E0A2069              |

| CY8C3246PVI-122 | 50              | 64         | 8         | 2           | 2                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | -   | >        | 24                   | 4                | -      | -        | 29                         | 25   | 4   | 0     | 48-pin SSOP  | 0×1E07A069              |

| CY8C3246AXI-138 | 50              | 64         | 8         | 2           | >                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | 1   | >        | 24                   | 4                | ~      | -        | 72                         | 62   | 8   | 2     | 100-pin TQFP | 0×1E08A069              |

| CY8C3246LTI-128 | 50              | 64         | 8         | 2           | >                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | 1   | >        | 24                   | 4                | ~      | -        | 48                         | 38   | 8   | 2     | 68-pin QFN   | 0×1E080069              |

| CY8C3246LTI-125 | 50              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 1   | 2          | 0                   | 0      | -   | ~        | 24                   | 4                | >      | -        | 31                         | 25   | 4   | 2     | 48-pin QFN   | 0×1E07D069              |

| CY8C3246FNI-213 | 50              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 1   | 2          | -                   | _      | _   | ~        | 24                   | 4                | -      | -        | 46                         | 38   | 8   | -     | 72-pin WLCSP | 0x1E0D5069              |

Notes

75. UDBs support a wide variety of functionality including SPI, LIN, UART, timer, counter, PWM, PRS, and others. Individual functions may use a fraction of a UDB or multiple UDBs. Multiple functions can share a single UDB. See the Example Peripherals on page 45 for more information on how UDBs can be used.

76. The I/O Count includes all types of digital I/O: GPIO, SIO, and the two USB I/O. See the I/O System and Routing on page 37 for details on the functionality of each of

these types of I/O.

77. The JTAG ID has three major fields. The most significant nibble (left digit) is the version, followed by a 2 byte part number and a 3 nibble manufacturer ID.

# 14. Acronyms

# Table 14-1. Acronyms Used in this Document

| Acronym | Description                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------|

| abus    | analog local bus                                                                                        |

| ADC     | analog-to-digital converter                                                                             |

| AG      | analog global                                                                                           |

| АНВ     | AMBA (advanced microcontroller bus archi-<br>tecture) high-performance bus, an ARM data<br>transfer bus |

| ALU     | arithmetic logic unit                                                                                   |

| AMUXBUS | analog multiplexer bus                                                                                  |

| API     | application programming interface                                                                       |

| APSR    | application program status register                                                                     |

| ARM®    | advanced RISC machine, a CPU architecture                                                               |

| ATM     | automatic thump mode                                                                                    |

| BW      | bandwidth                                                                                               |

| CAN     | Controller Area Network, a communications protocol                                                      |

| CMRR    | common-mode rejection ratio                                                                             |

| CPU     | central processing unit                                                                                 |

| CRC     | cyclic redundancy check, an error-checking protocol                                                     |

| DAC     | digital-to-analog converter, see also IDAC, VDAC                                                        |

| DFB     | digital filter block                                                                                    |

| DIO     | digital input/output, GPIO with only digital capabilities, no analog. See GPIO.                         |

| DMA     | direct memory access, see also TD                                                                       |

| DNL     | differential nonlinearity, see also INL                                                                 |

| DNU     | do not use                                                                                              |

| DR      | port write data registers                                                                               |

| DSI     | digital system interconnect                                                                             |

| DWT     | data watchpoint and trace                                                                               |

| ECC     | error correcting code                                                                                   |

| ECO     | external crystal oscillator                                                                             |

| EEPROM  | electrically erasable programmable read-only<br>memory                                                  |

| EMI     | electromagnetic interference                                                                            |

| EMIF    | external memory interface                                                                               |

| EOC     | end of conversion                                                                                       |

| EOF     | end of frame                                                                                            |

| EPSR    | execution program status register                                                                       |

| ESD     | electrostatic discharge                                                                                 |

| ETM     | embedded trace macrocell                                                                                |

# Table 14-1. Acronyms Used in this Document (continued)

| Acronym                  | Description                                            |

|--------------------------|--------------------------------------------------------|

| FIR                      | finite impulse response, see also IIR                  |

| FPB                      | flash patch and breakpoint                             |

| FS                       | full-speed                                             |

| GPIO                     | general-purpose input/output, applies to a PSoC pin    |

| HVI                      | high-voltage interrupt, see also LVI, LVD              |

| IC                       | integrated circuit                                     |

| IDAC                     | current DAC, see also DAC, VDAC                        |

| IDE                      | integrated development environment                     |

| l <sup>2</sup> C, or IIC | Inter-Integrated Circuit, a communications protocol    |

| lir                      | infinite impulse response, see also FIR                |

| ILO                      | internal low-speed oscillator, see also IMO            |

| IMO                      | internal main oscillator, see also ILO                 |

| INL                      | integral nonlinearity, see also DNL                    |

| I/O                      | input/output, see also GPIO, DIO, SIO, USBIO           |

| IPOR                     | initial power-on reset                                 |

| IPSR                     | interrupt program status register                      |

| IRQ                      | interrupt request                                      |

| ITM                      | instrumentation trace macrocell                        |

| LCD                      | liquid crystal display                                 |

| LIN                      | Local Interconnect Network, a communications protocol. |

| LR                       | link register                                          |

| LUT                      | lookup table                                           |

| LVD                      | low-voltage detect, see also LVI                       |

| LVI                      | low-voltage interrupt, see also HVI                    |

| LVTTL                    | low-voltage transistor-transistor logic                |

| MAC                      | multiply-accumulate                                    |

| MCU                      | microcontroller unit                                   |

| MISO                     | master-in slave-out                                    |

| NC                       | no connect                                             |

| NMI                      | nonmaskable interrupt                                  |

| NRZ                      | non-return-to-zero                                     |

| NVIC                     | nested vectored interrupt controller                   |

| NVL                      | nonvolatile latch, see also WOL                        |

| opamp                    | operational amplifier                                  |

| PAL                      | programmable array logic, see also PLD                 |

| PC                       | program counter                                        |

| РСВ                      | printed circuit board                                  |

| PGA                      | programmable gain amplifier                            |

# 18. Sales, Solutions, and Legal Information

# Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

# Products

| Automotive               | cypress.com/go/automotive |

|--------------------------|---------------------------|

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

| Memory                   | cypress.com/go/memory     |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

# **PSoC<sup>®</sup> Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Community | Forums | Blogs | Video | Training

Technical Support cypress.com/go/support

© Cypress Semiconductor Corporation, 2009-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and ober countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software in binary code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.