Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c242-e-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**TABLE 1-2:** PIC18C2X2 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Din Name        | Pin Number |       | Pin Buffer |      | Decembries                                                       |  |  |

|-----------------|------------|-------|------------|------|------------------------------------------------------------------|--|--|

| Pin Name        | DIP        | SOIC  | Туре       | Type | Description                                                      |  |  |

|                 |            |       |            |      | PORTC is a bi-directional I/O port.                              |  |  |

| RC0/T1OSO/T1CKI | 11         | 11    |            |      |                                                                  |  |  |

| RC0             |            |       | I/O        | ST   | Digital I/O.                                                     |  |  |

| T1OSO           |            |       | 0          | _    | Timer1 oscillator output.                                        |  |  |

| T1CKI           |            |       | I          | ST   | Timer1/Timer3 external clock input.                              |  |  |

| RC1/T1OSI/CCP2  | 12         | 12    |            |      |                                                                  |  |  |

| RC1             |            |       | I/O        | ST   | Digital I/O.                                                     |  |  |

| T1OSI           |            |       | I          | CMOS | Timer1 oscillator input.                                         |  |  |

| CCP2            |            |       | I/O        | ST   | Capture2 input, Compare2 output, PWM2 output.                    |  |  |

| RC2/CCP1        | 13         | 13    |            |      |                                                                  |  |  |

| RC2             |            |       | I/O        | ST   | Digital I/O.                                                     |  |  |

| CCP1            |            |       | I/O        | ST   | Capture1 input/Compare1 output/PWM1 output.                      |  |  |

| RC3/SCK/SCL     | 14         | 14    |            |      |                                                                  |  |  |

| RC3             |            |       | I/O        | ST   | Digital I/O.                                                     |  |  |

| SCK             |            |       | I/O        | ST   | Synchronous serial clock input/output for SPI mode.              |  |  |

| SCL             |            |       | I/O        | ST   | Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |  |

| RC4/SDI/SDA     | 15         | 15    |            |      |                                                                  |  |  |

| RC4             |            |       | I/O        | ST   | Digital I/O.                                                     |  |  |

| SDI             |            |       | I          | ST   | SPI Data In.                                                     |  |  |

| SDA             |            |       | I/O        | ST   | I <sup>2</sup> C Data I/O.                                       |  |  |

| RC5/SDO         | 16         | 16    |            |      |                                                                  |  |  |

| RC5             |            |       | I/O        | ST   | Digital I/O.                                                     |  |  |

| SDO             |            |       | 0          | _    | SPI Data Out.                                                    |  |  |

| RC6/TX/CK       | 17         | 17    |            |      |                                                                  |  |  |

| RC6             |            |       | I/O        | ST   | Digital I/O.                                                     |  |  |

| TX              |            |       | 0          | _    | USART Asynchronous Transmit.                                     |  |  |

| CK              |            |       | I/O        | ST   | USART Synchronous Clock (see related RX/DT).                     |  |  |

| RC7/RX/DT       | 18         | 18    |            |      |                                                                  |  |  |

| RC7             |            |       | I/O        | ST   | Digital I/O.                                                     |  |  |

| RX              |            |       | I          | ST   | USART Asynchronous Receive.                                      |  |  |

| DT              |            |       | I/O        | ST   | USART Synchronous Data (see related TX/CK).                      |  |  |

| Vss             | 8, 19      | 8, 19 | Р          |      | Ground reference for logic and I/O pins.                         |  |  |

| VDD             | 20         | 20    | Р          | _    | Positive supply for logic and I/O pins.                          |  |  |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels I = Input

O = Output

OD = Open Drain (no P diode to VDD)

CMOS = CMOS compatible input or output

P = Power

PIC18C4X2 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-3:**

| Pin Name | Pin Number |      | Pin  | Buffer | Description |                                                       |

|----------|------------|------|------|--------|-------------|-------------------------------------------------------|

| Pin Name | DIP        | PLCC | TQFP | Туре   | Туре        | Description                                           |

|          |            |      |      |        |             | PORTB is a bi-directional I/O port. PORTB can be      |

|          |            |      |      |        |             | software programmed for internal weak pull-ups on all |

|          |            |      |      |        |             | inputs.                                               |

| RB0/INT0 | 33         | 36   | 8    |        |             |                                                       |

| RB0      |            |      |      | I/O    | TTL         | Digital I/O.                                          |

| INT0     |            |      |      | ı      | ST          | External Interrupt 0.                                 |

| RB1/INT1 | 34         | 37   | 9    |        |             |                                                       |

| RB1      |            |      |      | I/O    | TTL         |                                                       |

| INT1     |            |      |      | ı      | ST          | External Interrupt 1.                                 |

| RB2/INT2 | 35         | 38   | 10   |        |             |                                                       |

| RB2      |            |      |      | I/O    | TTL         | Digital I/O.                                          |

| INT2     |            |      |      | - 1    | ST          | External Interrupt 2.                                 |

| RB3/CCP2 | 36         | 39   | 11   |        |             |                                                       |

| RB3      |            |      |      | I/O    | TTL         | Digital I/O.                                          |

| CCP2     |            |      |      | I/O    | ST          | Capture2 input, Compare2 output, PWM2 output.         |

| RB4      | 37         | 41   | 14   | I/O    | TTL         | Digital I/O. Interrupt-on-change pin.                 |

| RB5      | 38         | 42   | 15   | I/O    | TTL         | Digital I/O. Interrupt-on-change pin.                 |

| RB6      | 39         | 43   | 16   | I/O    | TTL         | Digital I/O. Interrupt-on-change pin.                 |

|          |            |      |      | ı      | ST          | ICSP programming clock.                               |

| RB7      | 40         | 44   | 17   | I/O    | TTL         | Digital I/O. Interrupt-on-change pin.                 |

|          |            |      |      | I/O    | ST          | ICSP programming data.                                |

Legend: TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels I = Input

O = Output

P = Power

OD = Open Drain (no P diode to VDD)

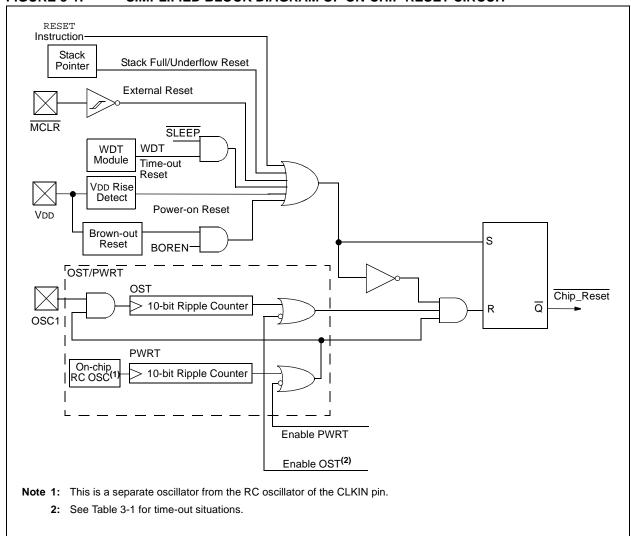

## 3.0 RESET

The PIC18CXX2 differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) Watchdog Timer (WDT) Reset (during normal operation)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

Most registers are unaffected by a RESET. Their status is unknown on POR and unchanged by all other RESETS. The other registers are forced to a "RESET state" on Power-on Reset, MCLR, WDT Reset, Brownout Reset, MCLR Reset during SLEEP, and by the RESET instruction.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR, are set or cleared differently in different RESET situations, as indicated in Table 3-2. These bits are used in software to determine the nature of the RESET. See Table 3-3 for a full description of the RESET states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The Enhanced MCU devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

MCLR pin is not driven low by any internal RESETS, including WDT.

FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register | App | olicabl | e Devi | ces | Power-on Reset,<br>Brown-out Reset | MCLR Resets WDT Reset RESET Instruction Stack Resets | Wake-up via WDT<br>or Interrupt |

|----------|-----|---------|--------|-----|------------------------------------|------------------------------------------------------|---------------------------------|

| TOSU     | 242 | 442     | 252    | 452 | 0 0000                             | 0 0000                                               | 0 uuuu <b>(3)</b>               |

| TOSH     | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                            | uuuu uuuu(3)                    |

| TOSL     | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                            | uuuu uuuu <sup>(3)</sup>        |

| STKPTR   | 242 | 442     | 252    | 452 | 00-0 0000                          | 00-0 0000                                            | uu-u uuuu <sup>(3)</sup>        |

| PCLATU   | 242 | 442     | 252    | 452 | 0 0000                             | 0 0000                                               | u uuuu                          |

| PCLATH   | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                            | uuuu uuuu                       |

| PCL      | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                            | PC + 2 <sup>(2)</sup>           |

| TBLPTRU  | 242 | 442     | 252    | 452 | 00 0000                            | 00 0000                                              | uu uuuu                         |

| TBLPTRH  | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                            | uuuu uuuu                       |

| TBLPTRL  | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                            | uuuu uuuu                       |

| TABLAT   | 242 | 442     | 252    | 452 | 0000 0000                          | 0000 0000                                            | uuuu uuuu                       |

| PRODH    | 242 | 442     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                            | uuuu uuuu                       |

| PRODL    | 242 | 442     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                            | uuuu uuuu                       |

| INTCON   | 242 | 442     | 252    | 452 | 0000 000x                          | 0000 000u                                            | uuuu uuuu(1)                    |

| INTCON2  | 242 | 442     | 252    | 452 | 1111 -1-1                          | 1111 -1-1                                            | uuuu -u-u <sup>(1)</sup>        |

| INTCON3  | 242 | 442     | 252    | 452 | 11-0 0-00                          | 11-0 0-00                                            | uu-u u-uu <sup>(1)</sup>        |

| INDF0    | 242 | 442     | 252    | 452 | N/A                                | N/A                                                  | N/A                             |

| POSTINC0 | 242 | 442     | 252    | 452 | N/A                                | N/A                                                  | N/A                             |

| POSTDEC0 | 242 | 442     | 252    | 452 | N/A                                | N/A                                                  | N/A                             |

| PREINC0  | 242 | 442     | 252    | 452 | N/A                                | N/A                                                  | N/A                             |

| PLUSW0   | 242 | 442     | 252    | 452 | N/A                                | N/A                                                  | N/A                             |

| FSR0H    | 242 | 442     | 252    | 452 | 0000                               | 0000                                                 | uuuu                            |

| FSR0L    | 242 | 442     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                            | uuuu uuuu                       |

| WREG     | 242 | 442     | 252    | 452 | xxxx xxxx                          | uuuu uuuu                                            | uuuu uuuu                       |

| INDF1    | 242 | 442     | 252    | 452 | N/A                                | N/A                                                  | N/A                             |

| POSTINC1 | 242 | 442     | 252    | 452 | N/A                                | N/A                                                  | N/A                             |

| POSTDEC1 | 242 | 442     | 252    | 452 | N/A                                | N/A                                                  | N/A                             |

| PREINC1  | 242 | 442     | 252    | 452 | N/A                                | N/A                                                  | N/A                             |

| PLUSW1   | 242 | 442     | 252    | 452 | N/A                                | N/A                                                  | N/A                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

- Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for RESET value for specific condition.

- **5:** Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

- **6:** The long write enable is only reset on a POR or  $\overline{MCLR}$  Reset.

- 7: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read as '0'.

#### 4.7.1 TWO-WORD INSTRUCTIONS

The PIC18CXX2 devices have four two-word instructions: MOVFF, CALL, GOTO and LFSR. The second word of these instructions has the 4 MSBs set to 1's and is a special kind of NOP instruction. The lower 12-bits of the second word contain data to be used by the instruction. If the first word of the instruction is executed, the data in the second word is accessed. If the

second word of the instruction is executed by itself (first word was skipped), it will execute as a NOP. This action is necessary when the two-word instruction is preceded by a conditional instruction that changes the PC. A program example that demonstrates this concept is shown in Example 4-3. Refer to Section 19.0 for further details of the instruction set.

**EXAMPLE 4-3: TWO-WORD INSTRUCTIONS**

| CASE 1:             |            |            |                                     |

|---------------------|------------|------------|-------------------------------------|

| Object Code         | Source Cod | е          |                                     |

| 0110 0110 0000 0000 | TSTFSZ     | REG1       | ; is RAM location 0?                |

| 1100 0001 0010 0011 | MOVFF      | REG1, REG2 | ; No, execute 2-word instruction    |

| 1111 0100 0101 0110 |            |            | ; 2nd operand holds address of REG2 |

| 0010 0100 0000 0000 | ADDWF      | REG3       | ; continue code                     |

| CASE 2:             |            |            |                                     |

| Object Code         | Source Cod | е          |                                     |

| 0110 0110 0000 0000 | TSTFSZ     | REG1       | ; is RAM location 0?                |

| 1100 0001 0010 0011 | MOVFF      | REG1, REG2 | ; Yes                               |

| 1111 0100 0101 0110 |            |            | ; 2nd operand becomes NOP           |

| 0010 0100 0000 0000 | ADDWF      | REG3       | ; continue code                     |

#### 4.8 Lookup Tables

Lookup tables are implemented two ways. These are:

- Computed GOTO

- · Table Reads

## 4.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL).

A lookup table can be formed with an ADDWF PCL instruction and a group of RETLW 0xnn instructions. WREG is loaded with an offset into the table, before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW 0xnn instructions that returns the value 0xnn to the calling function.

The offset value (value in WREG) specifies the number of bytes that the program counter should advance.

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### 4.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory allows 2 bytes of data to be stored in each instruction location.

Lookup table data may be stored 2 bytes per program word by using table reads and writes. The table pointer (TBLPTR) specifies the byte address and the table latch (TABLAT) contains the data that is read from, or written to program memory. Data is transferred to/from program memory one byte at a time.

A description of the Table Read/Table Write operation is shown in Section 5.0.

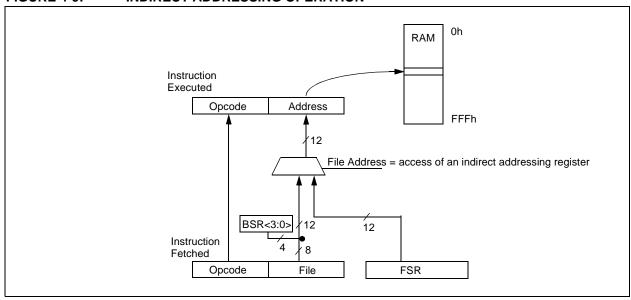

If an indirect addressing operation is done where the target address is an FSRnH or FSRnL register, the write operation will dominate over the pre- or post-increment/decrement functions.

FIGURE 4-9: INDIRECT ADDRESSING OPERATION

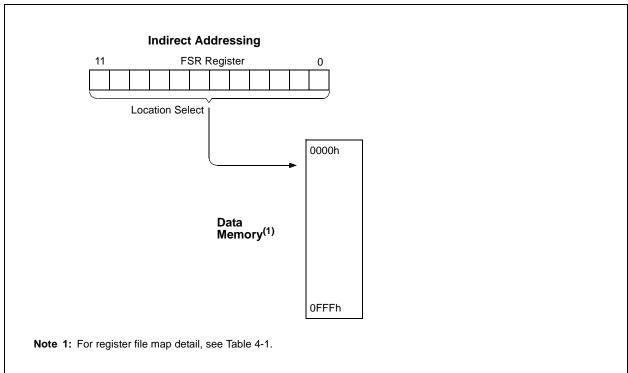

FIGURE 4-10: INDIRECT ADDRESSING

#### REGISTER 7-3: INTCON3 REGISTER

| R/W-1  | R/W-1  | U-0 | R/W-0  | R/W-0  | U-0 | R/W-0  | R/W-0  |

|--------|--------|-----|--------|--------|-----|--------|--------|

| INT2IP | INT1IP | _   | INT2IE | INT1IE | _   | INT2IF | INT1IF |

| hit 7  |        |     |        |        |     |        | bit 0  |

bit 7 INT2IP: INT2 External Interrupt Priority bit

1 = High priority

0 = Low priority

bit 6 INT1IP: INT1 External Interrupt Priority bit

1 = High priority

0 = Low priority

bit 5 **Unimplemented:** Read as '0'

bit 4 INT2IE: INT2 External Interrupt Enable bit

1 = Enables the INT2 external interrupt

0 = Disables the INT2 external interrupt

bit 3 **INT1IE:** INT1 External Interrupt Enable bit

1 = Enables the INT1 external interrupt0 = Disables the INT1 external interrupt

bit 2 Unimplemented: Read as '0'

bit 1 INT2IF: INT2 External Interrupt Flag bit

1 = The INT2 external interrupt occurred (must be cleared in software)

0 = The INT2 external interrupt did not occur

bit 0 INT1IF: INT1 External Interrupt Flag bit

1 = The INT1 external interrupt occurred (must be cleared in software)

0 = The INT1 external interrupt did not occur

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit, or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

**TABLE 10-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER**

| Name   | Bit 7                                                                       | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>RESETS |

|--------|-----------------------------------------------------------------------------|---------------|---------|---------|---------|--------|-----------|-----------|----------------------|---------------------------------|

| INTCON | GIE/GIEH                                                                    | PEIE/<br>GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF    | RBIF      | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>                                                        | ADIF          | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>                                                        | ADIE          | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>                                                        | ADIP          | RCIP    | TXIP    | SSPIP   | CCP1IP | TMR2IP    | TMR1IP    | 0000 0000            | 0000 0000                       |

| TMR1L  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |               |         |         |         |        |           | xxxx xxxx | uuuu uuuu            |                                 |

| TMR1H  | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |               |         |         |         |        | xxxx xxxx | uuuu uuuu |                      |                                 |

| T1CON  | RD16                                                                        |               | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC | TMR1CS    | TMR10N    | 00 0000              | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module. **Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

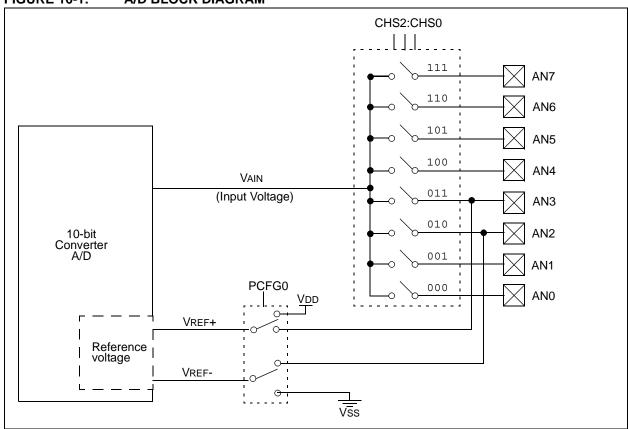

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and Vss) or the voltage level on the RA3/AN3/ VREF+ pin and RA2/AN2/VREF-.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off and any conversion is aborted.

Each port pin associated with the A/D converter can be configured as an analog input (RA3 can also be a voltage reference) or as a digital I/O.

The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ADRESL registers, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 16-1.

FIGURE 16-1: A/D BLOCK DIAGRAM

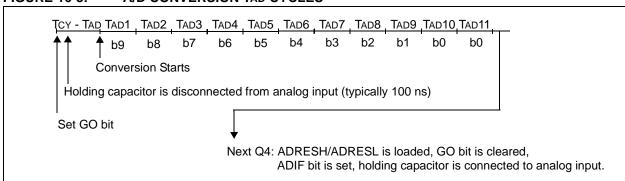

#### 16.4 A/D Conversions

Figure 16-3 shows the operation of the A/D converter after the GO bit has been set. Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

## 16.5 Use of the CCP2 Trigger

An A/D conversion can be started by the "special event trigger" of the CCP2 module. This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion and the Timer1 (or Timer3) counter will be reset to zero. Timer1 (or Timer3) is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH/ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 (or Timer3) counter.

#### FIGURE 16-3: A/D CONVERSION TAD CYCLES

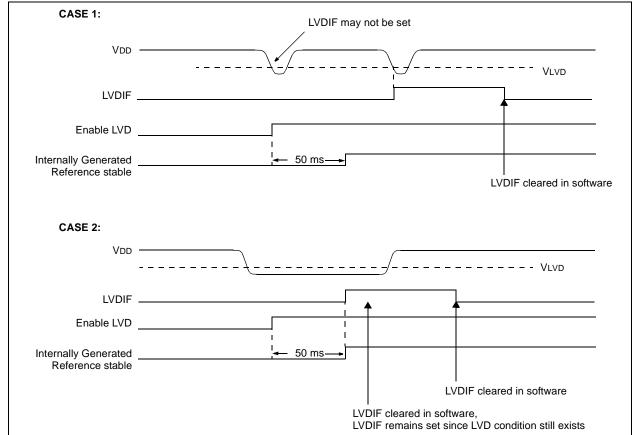

#### 17.2 Operation

Depending on the power source for the device voltage, the voltage normally decreases relatively slowly. This means that the LVD module does not need to be constantly operating. To decrease the current requirements, the LVD circuitry only needs to be enabled for short periods, where the voltage is checked. After doing the check, the LVD module may be disabled.

Each time that the LVD module is enabled, the circuitry requires some time to stabilize. After the circuitry has stabilized, all status flags may be cleared. The module will then indicate the proper state of the system.

The following steps are needed to set up the LVD module:

- 1. Write the value to the LVDL3:LVDL0 bits (LVD-CON register), which selects the desired LVD Trip Point.

- 2. Ensure that LVD interrupts are disabled (the LVDIE bit is cleared, or the GIE bit is cleared).

- 3. Enable the LVD module (set the LVDEN bit in the LVDCON register).

- 4. Wait for the LVD module to stabilize (the IRVST bit to become set).

- 5. Clear the LVD interrupt flag, which may have falsely become set until the LVD module has stabilized (clear the LVDIF bit).

- Enable the LVD interrupt (set the LVDIE and the GIE bits).

Figure 17-4 shows typical waveforms that the LVD module may be used to detect.

**FIGURE 17-4:** LOW VOLTAGE DETECT WAVEFORMS CASE 1:

TABLE 19-2: PIC18CXXX INSTRUCTION SET

| Mnemonic,<br>Operands |                                 | Decerintian                              | Cycles     | 16-k | oit Instr | uction V | Vord | Status           | Notes      |

|-----------------------|---------------------------------|------------------------------------------|------------|------|-----------|----------|------|------------------|------------|

|                       |                                 | Description                              | Cycles     | MSb  |           |          | LSb  | Affected         | Notes      |

| BYTE-ORII             | ENTED F                         | FILE REGISTER OPERATIONS                 |            |      |           |          |      |                  |            |

| ADDWF                 | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da      | ffff     | ffff | C, DC, Z, OV, N  | 1, 2       |

| ADDWFC                | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N  | 1, 2       |

| ANDWF                 | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff | Z, N             | 1,2        |

| CLRF                  | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z                | 2          |

| COMF                  | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff     | ffff | Z, N             | 1, 2       |

| CPFSEQ                | f, a                            | Compare f with WREG, skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None             | 4          |

| CPFSGT                | f, a                            | Compare f with WREG, skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None             | 4          |

| CPFSLT                | f, a                            | Compare f with WREG, skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None             | 1, 2       |

| DECF                  | f, d, a                         | Decrement f                              | 1 `        | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N  | 1, 2, 3, 4 |

| DECFSZ                | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None             | 1, 2, 3, 4 |

| DCFSNZ                | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff     | ffff | None             | 1, 2       |

| INCF                  | f, d, a                         | Increment f                              | 1 `        | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N  | 1, 2, 3, 4 |

| INCFSZ                | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     | ffff | None             | 4          |

| INFSNZ                | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff     | ffff | None             | 1, 2       |

| IORWF                 | f, d, a                         | Inclusive OR WREG with f                 | 1 ` ′      | 0001 | 00da      | ffff     | ffff | Z, N             | 1, 2       |

| MOVF                  | f, d, a                         | Move f                                   | 1          | 0101 | 00da      | ffff     | ffff | Z. N             | 1          |

| MOVFF                 | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          |      | ffff      | ffff     | ffff |                  |            |

|                       | -5, -u                          | f <sub>d</sub> (destination)2nd word     | _          |      | ffff      | ffff     | ffff |                  |            |

| MOVWF                 | f, a                            | Move WREG to f                           | 1          | 0110 | 111a      | ffff     | ffff | None             |            |

| MULWF                 | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a      | ffff     | ffff | None             |            |

| NEGF                  | f, a                            | Negate f                                 | 1          | 0110 | 110a      | ffff     | ffff | C, DC, Z, OV, N  | 1, 2       |

| RLCF                  | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 |           | ffff     |      | C, Z, N          | ., –       |

| RLNCF                 | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da      | ffff     |      | Z, N             | 1, 2       |

| RRCF                  | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da      | ffff     | ffff | C, Z, N          | ., _       |

| RRNCF                 | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 | 00da      | ffff     | ffff |                  |            |

| SETF                  | f, a, a                         | Set f                                    | <u> </u>   | 0110 | 100a      | ffff     | ffff | None             |            |

| SUBFWB                | f, d, a                         | Subtract f from WREG with                | <u> </u>   |      | 01da      | ffff     | ffff | C, DC, Z, OV, N  | 1, 2       |

| COBI WE               | 1, u, u                         | borrow                                   | 1.         | 0101 | olda      |          |      | 0, 50, 2, 00, 10 | 1, 2       |

| SUBWF                 | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff     | ffff | C, DC, Z, OV, N  |            |

| SUBWFB                | f, d, a                         | Subtract WREG from f with                | 1          |      | 10da      | ffff     | ffff | C, DC, Z, OV, N  | 1, 2       |

| OODWI B               | 1, u, u                         | borrow                                   | •          | 0101 | Ioda      | TTTT     | TTTT | 0, 50, 2, 00, 10 | 1, 2       |

| SWAPF                 | f, d, a                         | Swap nibbles in f                        | 1          | 0011 | 10da      | ffff     | ffff | None             | 4          |

| TSTFSZ                | f, a, a                         | Test f, skip if 0                        | 1 (2 or 3) | 0110 | 011a      | ffff     | ffff | None             | 1, 2       |

| XORWF                 | f, d, a                         | Exclusive OR WREG with f                 | 1          |      | 10da      | ffff     |      | Z, N             | 1, 2       |

|                       |                                 | E REGISTER OPERATIONS                    | Ţ          | 0001 | IUua      | TTTT     | TTTT | Z, IV            |            |

| BCF                   |                                 | Bit Clear f                              | 1          | 1001 | 1-1-1-    | £ £ £ £  | 5555 | None             | 1.2        |

|                       | f, b, a                         |                                          | 1          | 1001 | bbba      | ffff     | ffff | None             | 1, 2       |

| BSF                   | f, b, a                         | Bit Set f                                | · ·        |      | bbba      | ffff     | ffff | None             | 1, 2       |

| BTFSC                 | f, b, a                         | Bit Test f, Skip if Clear                | 1 (2 or 3) | 1011 |           | ffff     | ffff | None             | 3, 4       |

| BTFSS                 | f, b, a                         | Bit Test f, Skip if Set                  | 1 (2 or 3) | 1010 | bbba      | ffff     | ffff | None             | 3, 4       |

| BTG                   | f, d, a                         | Bit Toggle f                             | 1          | 0111 | bbba      | ffff     | ffff | ivone            | 1, 2       |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

<sup>2:</sup> If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

<sup>3:</sup> If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**<sup>4:</sup>** Some instructions are 2 word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

<sup>5:</sup> If the table write starts the write cycle to internal memory, the write will continue until terminated.

Compare f with WREG, **CPFSGT** skip if f > WREG

Syntax: [label] CPFSGT f[,a]

$0 \le f \le 255$ Operands:

$a \in [0,1]$

(f) - (WREG),Operation:

skip if (f) > (WREG)

(unsigned comparison)

Status Affected: None

Encodina: 0110 010a ffff ffff

Description: Compares the contents of data

memory location 'f' to the contents of the WREG by performing an

unsigned subtraction.

If the contents of 'f' are greater than the contents of WREG, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. If 'a' is 0, the Access Bank will be

selected, overriding the BSR value. If 'a' = 1, then the bank will be selected as per the BSR value

(default).

1(2)

1 Words:

Note: 3 cycles if skip and followed

by a 2-word instruction.

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read         | Process | No        |

|        | register 'f' | Data    | operation |

If skip:

Cycles:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

If skip and followed by 2-word instruction:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

| No        | No        | No        | No        |

| operation | operation | operation | operation |

CPFSGT REG, 0 Example: HERE

> NGREATER GREATER

Before Instruction

РC Address (HERE)

WREG

After Instruction

Tf REG WREG:

PC Address (GREATER) =

If REG  $\leq$ WREG:

> PC Address (NGREATER)

Compare f with WREG, **CPFSLT** skip if f < WREG

Syntax: [label] CPFSLT f[,a]

Operands:  $0 \le f \le 255$

$a \in [0,1]$

(f) - (WREG),Operation:

skip if (f) < (WREG)

(unsigned comparison)

Status Affected: None

Encodina: 0110 000a ffff ffff

Description: Compares the contents of data

memory location 'f' to the contents of WREG by performing an

unsigned subtraction.

If the contents of 'f' are less than the contents of WREG, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. If 'a' is 0. the Access Bank will be

selected. If 'a' is 1, the BSR will not

be overridden (default).

Words: 1 Cycles: 1(2)

Note: 3 cycles if skip and followed

by a 2-word instruction.

Q Cycle Activity:

| Q1     | Q2                | Q3              | Q4              |

|--------|-------------------|-----------------|-----------------|

| Decode | Read register 'f' | Process<br>Data | No<br>operation |

|        |                   |                 |                 |

If skip:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

If skip and followed by 2-word instruction:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

| No        | No        | No        | No        |

| operation | operation | operation | operation |

Example: HERE CPFSLT REG, 1

NLESS LESS

Before Instruction

After Instruction

Address (HERE) PC

If REG

WREG; PC Address (LESS)

If REG WREG;

PCAddress (NLESS)

| DAV   | V               | Decimal A                                                                                                                                                          | Adjust WRE                                                                                                            | G R | egister |  |  |  |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|---------|--|--|--|

| Synt  | ax:             | [label] Di                                                                                                                                                         | AW.                                                                                                                   |     |         |  |  |  |

| Оре   | rands:          | None                                                                                                                                                               |                                                                                                                       |     |         |  |  |  |

| Ope   | ration:         | (WREG<3 else                                                                                                                                                       | If [WREG<3:0> >9] or [DC = 1] ther (WREG<3:0>) + 6 $\rightarrow$ WREG<3:0>; else (WREG<3:0>) $\rightarrow$ WREG<3:0>; |     |         |  |  |  |

|       |                 | If [WREG<7:4> >9] or [C = 1] then (WREG<7:4>) + 6 $\rightarrow$ WREG<7:4> else (WREG<7:4>) $\rightarrow$ WREG<7:4>;                                                |                                                                                                                       |     |         |  |  |  |

| Statu | us Affected:    | С                                                                                                                                                                  |                                                                                                                       |     |         |  |  |  |

| Enco  | oding:          | 0000                                                                                                                                                               | 0000 00                                                                                                               | 00  | 0111    |  |  |  |

| Desc  | cription:       | DAW adjusts the eight-bit value in WREG, resulting from the earlier addition of two variables (each in packed BCD format) and produce a correct packed BCD result. |                                                                                                                       |     |         |  |  |  |

| Wor   | ds:             | 1                                                                                                                                                                  |                                                                                                                       |     |         |  |  |  |

| Cycl  | es:             | 1                                                                                                                                                                  |                                                                                                                       |     |         |  |  |  |

| QC    | cycle Activity: |                                                                                                                                                                    |                                                                                                                       |     |         |  |  |  |

|       | Q1              | Q2                                                                                                                                                                 | Q3                                                                                                                    |     | Q4      |  |  |  |

|       | Decode          | Read                                                                                                                                                               | Process                                                                                                               |     | Write   |  |  |  |

| Q1     | Q2                       | Q3              | Q4            |

|--------|--------------------------|-----------------|---------------|

| Decode | Read<br>register<br>WREG | Process<br>Data | Write<br>WREG |

Example1: DAW

#### Before Instruction

WREG = 0xA5 C = 0 DC = 0

### After Instruction

$\begin{array}{lll} \text{WREG} & = & 0 \times 05 \\ \text{C} & = & 1 \\ \text{DC} & = & 0 \\ \end{array}$

Example 2:

## **Before Instruction**

WREG = 0xCE C = 0 DC = 0

## After Instruction

$\begin{array}{rcl} \text{WREG} & = & 0 \times 34 \\ \text{C} & = & 1 \\ \text{DC} & = & 0 \end{array}$

| DECF             | Decreme                                                                          | nt f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                 |                                                      |  |

|------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------|--|

| Syntax:          | [ label ]                                                                        | DECF 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | f [,d [,a]                                      |                                                      |  |

| Operands:        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                 |                                                      |  |

| Operation:       | $(f)-1\rightarrow$                                                               | dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                 |                                                      |  |

| Status Affected: | C,DC,N,C                                                                         | OV,Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                 |                                                      |  |

| Encoding:        | 0000                                                                             | 01da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ffff                                            | ffff                                                 |  |

| Description:     | Decreme result is sthe result if (default Bank will the BSR bank will BSR value) | itored in is stored in is stored in its stor | WREG. In the Acted, over 'a' = 1, the ted as pe | f 'd' is 1,<br>register<br>ccess<br>riding<br>en the |  |

Words: 1 Cycles: 1

## Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

Example: DECF CNT, 1, 0

## Before Instruction

$\begin{array}{ccc} CNT & = & 0 \times 01 \\ Z & = & 0 \end{array}$

### After Instruction

CNT = 0x00 Z = 1

| RLNCF            | Rotate Left f (no carry)                                                                                        |       |           |      |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------|-------|-----------|------|--|--|--|--|

| Syntax:          | [ label ]                                                                                                       | RLNCF | f [,d [,a | a]   |  |  |  |  |

| Operands:        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                             |       |           |      |  |  |  |  |

| Operation:       | $(f) \rightarrow dest,$<br>$(f<7>) \rightarrow dest<0>$                                                         |       |           |      |  |  |  |  |

| Status Affected: | N,Z                                                                                                             |       |           |      |  |  |  |  |

| Encoding:        | 0100                                                                                                            | 01da  | ffff      | ffff |  |  |  |  |

| Description:     | The contents of register 'f' are rotated one bit to the left. If 'd' is 0, the result is placed in WREG. If 'd' |       |           |      |  |  |  |  |

The contents of register 'f' are rotated one bit to the left. If 'd' is 0, the result is placed in WREG. If 'd' is 1, the result is stored back in register 'f' (default). If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' is 1, then the bank will be selected as per the BSR value (default).

Words: 1

Cycles: 1

Q Cycle Activity:

| _ | Q1     | Q2           | Q3      | Q4          |

|---|--------|--------------|---------|-------------|

|   | Decode | Read         | Process | Write to    |

|   |        | register 'f' | Data    | destination |

Example: RLNCF REG, 1, 0

Before Instruction

REG = 1010 1011

After Instruction

REG = 0101 0111

RRCF Rotate Right f through Carry

Syntax: [ label ] RRCF f [,d [,a] Operands:  $0 \le f \le 255$

$d \in [0,1] \\ a \in [0,1]$

Operation:  $(f<n>) \rightarrow dest<n-1>$ ,

$(f<0>) \rightarrow C,$ (C)  $\rightarrow$  dest<7>

Status Affected: C,N,Z

Encoding: 0011 00da ffff ffff

Description: The contents of register 'f' are

rotated one bit to the right through the Carry Flag. If 'd' is 0, the result is placed in WREG. If 'd' is 1, the result is placed back in register 'f' (default). If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' is 1, then the bank will be selected as per the BSR value (default).

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

Example: RRCF REG, 0, 0

Before Instruction

REG = 1110 0110 C = 0

After Instruction

REG = 1110 0110 WREG = 0111 0011 C = 0

# 21.2 DC Characteristics: PIC18CXX2 (Industrial, Extended) PIC18LCXX2 (Industrial) (Continued)

| DC CHARACTERISTICS |        |                                         | Operating temperature |     |       | aditions (unless otherwise stated)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |  |  |

|--------------------|--------|-----------------------------------------|-----------------------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                          | Min                   | Max | Units | Conditions                                                                                                                                          |  |  |

|                    | Vol    | Output Low Voltage                      |                       |     |       |                                                                                                                                                     |  |  |

| D080               |        | I/O ports                               | _                     | 0.6 | V     | IOL = $8.5 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$                                                      |  |  |

| D080A              |        |                                         | _                     | 0.6 | V     | IOL = $7.0 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$                                                     |  |  |

| D083               |        | OSC2/CLKOUT<br>(RC mode)                | _                     | 0.6 | V     | IOL = $1.6 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$                                                      |  |  |

| D083A              |        |                                         | _                     | 0.6 | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                                                                                                        |  |  |

|                    | Vон    | Output High Voltage <sup>(3)</sup>      |                       |     |       |                                                                                                                                                     |  |  |

| D090               |        | I/O ports                               | VDD - 0.7             | _   | V     | IOH = $-3.0$ mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C                                                                                                |  |  |

| D090A              |        |                                         | VDD - 0.7             | _   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C                                                                                                       |  |  |

| D092               |        | OSC2/CLKOUT<br>(RC mode)                | VDD - 0.7             | _   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°C to +85°C                                                                                                        |  |  |

| D092A              |        |                                         | VDD - 0.7             | _   | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                                                                                                       |  |  |

| D150               | Vod    | Open Drain High Voltage                 | _                     | 8.5 | V     | RA4 pin                                                                                                                                             |  |  |

|                    |        | Capacitive Loading Specs on Output Pins |                       |     |       |                                                                                                                                                     |  |  |

| D101               | Cio    | All I/O pins and OSC2<br>(in RC mode)   | _                     | 50  | pF    | To meet the AC Timing Specifications                                                                                                                |  |  |

| D102               | Св     | SCL, SDA                                | _                     | 400 | pF    | In I <sup>2</sup> C mode                                                                                                                            |  |  |

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC MCU be driven with an external clock while in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

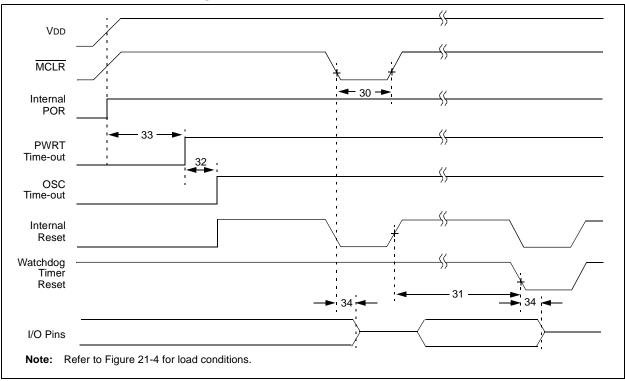

FIGURE 21-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

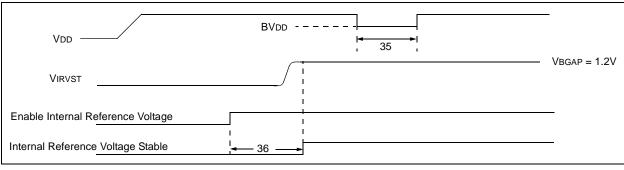

FIGURE 21-8: BROWN-OUT RESET TIMING

TABLE 21-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic                                          | Min      | Тур | Max      | Units | Conditions            |

|---------------|--------|---------------------------------------------------------|----------|-----|----------|-------|-----------------------|

| 30            | TmcL   | MCLR Pulse Width (low)                                  | 2        | _   | _        | μS    |                       |

| 31            | TWDT   | Watchdog Timer Time-out Period (No Postscaler)          | 7        | 18  | 33       | ms    |                       |

| 32            | Tost   | Oscillation Start-up Timer Period                       | 1024Tosc | 1   | 1024Tosc | _     | Tosc = OSC1 period    |

| 33            | TPWRT  | Power up Timer Period                                   | 28       | 72  | 132      | ms    |                       |

| 34            | Tıoz   | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset  |          | 2   | _        | μS    |                       |

| 35            | TBOR   | Brown-out Reset Pulse Width                             | 200      | _   | _        | μS    | VDD ≤ BVDD (See D005) |

| 36            | Tivrst | Time for Internal Reference<br>Voltage to become stable | _        | 20  | 50       | μS    |                       |

## Package Marking Information (Cont'd)

### 40-Lead PDIP

## Example

## 28- and 40-Lead JW (CERDIP)

## Example

### 44-Lead TQFP

## Example

#### 44-Lead PLCC

## Example

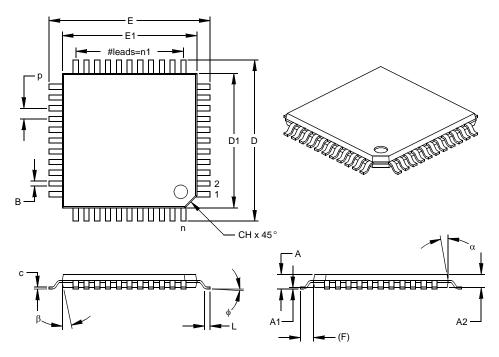

## 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units INCHES |      |      | MILLIMETERS* |       |       |       |

|--------------------------|--------------|------|------|--------------|-------|-------|-------|

| Dimensio                 | on Limits    | MIN  | NOM  | MAX          | MIN   | NOM   | MAX   |

| Number of Pins           | n            |      | 44   |              |       | 44    |       |

| Pitch                    | р            |      | .031 |              |       | 0.80  |       |

| Pins per Side            | n1           |      | 11   |              |       | 11    |       |

| Overall Height           | Α            | .039 | .043 | .047         | 1.00  | 1.10  | 1.20  |

| Molded Package Thickness | A2           | .037 | .039 | .041         | 0.95  | 1.00  | 1.05  |

| Standoff §               | A1           | .002 | .004 | .006         | 0.05  | 0.10  | 0.15  |

| Foot Length              | L            | .018 | .024 | .030         | 0.45  | 0.60  | 0.75  |

| Footprint (Reference)    | (F)          |      | .039 |              | 1.00  |       |       |

| Foot Angle               | ф            | 0    | 3.5  | 7            | 0     | 3.5   | 7     |

| Overall Width            | Е            | .463 | .472 | .482         | 11.75 | 12.00 | 12.25 |

| Overall Length           | D            | .463 | .472 | .482         | 11.75 | 12.00 | 12.25 |

| Molded Package Width     | E1           | .390 | .394 | .398         | 9.90  | 10.00 | 10.10 |

| Molded Package Length    | D1           | .390 | .394 | .398         | 9.90  | 10.00 | 10.10 |