Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

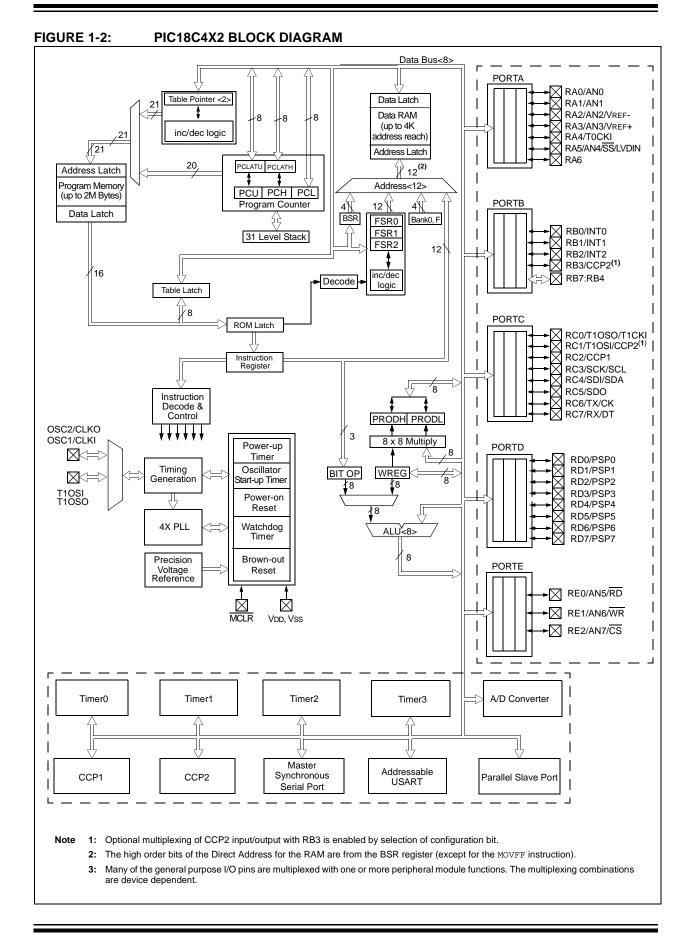

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c252-e-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

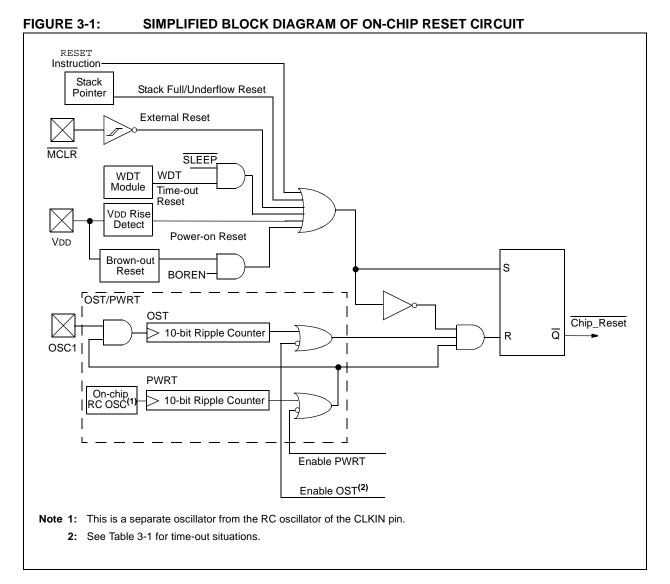

### 3.0 RESET

The PIC18CXX2 differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) Watchdog Timer (WDT) Reset (during normal operation)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

Most registers are unaffected by a RESET. Their status is unknown on POR and unchanged by all other RESETS. The other registers are forced to a "RESET state" on Power-on Reset, MCLR, WDT Reset, Brownout Reset, MCLR Reset during SLEEP, and by the RESET instruction. Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR, are set or cleared differently in different RESET situations, as indicated in Table 3-2. These bits are used in software to determine the nature of the RESET. See Table 3-3 for a full description of the RESET states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The Enhanced MCU devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

MCLR pin is not driven low by any internal RESETS, including WDT.

#### **REGISTER FILE SUMMARY (CONTINUED) TABLE 4-2:**

| File Name | Bit 7        | Bit 6                 | Bit 5          | Bit 4           | Bit 3          | Bit 2                     | Bit 1                         | Bit 0  | Value on<br>POR,<br>BOR | Details<br>on page: |

|-----------|--------------|-----------------------|----------------|-----------------|----------------|---------------------------|-------------------------------|--------|-------------------------|---------------------|

| IPR2      | _            | _                     | _              | —               | BCLIP          | LVDIP                     | TMR3IP                        | CCP2IP | 1111                    | 73                  |

| PIR2      | —            | —                     | _              | —               | BCLIF          | LVDIF                     | TMR3IF                        | CCP2IF | 0000                    | 69                  |

| PIE2      | _            | _                     | _              | _               | BCLIE          | LVDIE                     | TMR3IE                        | CCP2IE | 0000                    | 71                  |

| IPR1      | PSPIP        | ADIP                  | RCIP           | TXIP            | SSPIP          | CCP1IP                    | TMR2IP                        | TMR1IP | 1111 1111               | 72                  |

| PIR1      | PSPIF        | ADIF                  | RCIF           | TXIF            | SSPIF          | CCP1IF                    | TMR2IF                        | TMR1IF | 0000 0000               | 68                  |

| PIE1      | PSPIE        | ADIE                  | RCIE           | TXIE            | SSPIE          | CCP1IE                    | TMR2IE                        | TMR1IE | 0000 0000               | 70                  |

| TRISE     | IBF          | OBF                   | IBOV           | PSPMODE         | _              | Data Direction            | on bits for PO                | RTE    | 0000 -111               | 88                  |

| TRISD     | Data Directi | on Control Re         | gister for POR | TD              |                |                           |                               |        | 1111 1111               | 85                  |

| TRISC     | Data Directi | on Control Re         | gister for POR | TC              |                |                           |                               |        | 1111 1111               | 83                  |

| TRISB     | Data Directi | on Control Re         | gister for POR |                 | 1111 1111      | 80                        |                               |        |                         |                     |

| TRISA     | _            | TRISA6 <sup>(1)</sup> | Data Directi   | on Control Reg  | ister for PORT | A                         |                               |        | -111 1111               | 77                  |

| LATE      | -            | —                     | _              | —               | -              |                           | E Data Latch,<br>E Data Latch |        | xxx                     | 87                  |

| LATD      | Read PORT    | D Data Latch,         | Write PORTE    | Data Latch      | •              |                           |                               |        | xxxx xxxx               | 85                  |

| LATC      | Read PORT    | C Data Latch,         | Write PORTO    | C Data Latch    |                |                           |                               |        | xxxx xxxx               | 83                  |

| LATB      | Read PORT    | B Data Latch,         | Write PORTE    | B Data Latch    |                |                           |                               |        | xxxx xxxx               | 80                  |

| LATA      | _            | LATA6 <sup>(1)</sup>  | Read PORT      | A Data Latch, V | Write PORTA    | Data Latch <sup>(1)</sup> |                               |        | -xxx xxxx               | 77                  |

| PORTE     | Read PORT    | E pins, Write         | PORTE Data     | Latch           |                |                           |                               |        | 000                     | 87                  |

| PORTD     | Read PORT    | D pins, Write         | PORTD Data     | Latch           |                |                           |                               |        | xxxx xxxx               | 85                  |

| PORTC     | Read PORT    | C pins, Write         | PORTC Data     | Latch           |                |                           |                               |        | xxxx xxxx               | 83                  |

| PORTB     | Read PORT    | B pins, Write         | PORTB Data     | Latch           |                |                           |                               |        | xxxx xxxx               | 80                  |

| PORTA     | —            | RA6 <sup>(1)</sup>    | Read PORT      | A pins, Write P | ORTA Data La   | atch <sup>(1)</sup>       |                               |        | -x0x 0000               | 77                  |

Legend: x = unknown, u = unchanged, - = unimplemented, g = value depends on condition

Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO oscillator mode only, and read '0' in all other oscillator modes.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

#### 7.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable Registers (PIE1, PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

#### REGISTER 7-6: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (PIE1)

|       | R/W-0                                                                                                   | R/W-0                     | R/W-0         | R/W-0         | R/W-0          | R/W-0      | R/W-0         | R/W-0      |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------|---------------------------|---------------|---------------|----------------|------------|---------------|------------|--|--|--|

|       | PSPIE                                                                                                   | ADIE                      | RCIE          | TXIE          | SSPIE          | CCP1IE     | TMR2IE        | TMR1IE     |  |  |  |

|       | bit 7                                                                                                   |                           |               |               |                |            |               | bit 0      |  |  |  |

|       |                                                                                                         |                           |               |               |                |            |               |            |  |  |  |

| bit 7 | PSPIE: Parallel Slave Port Read/Write Interrupt Enable bit                                              |                           |               |               |                |            |               |            |  |  |  |

|       | <ol> <li>Enables the PSP read/write interrupt</li> <li>Disables the PSP read/write interrupt</li> </ol> |                           |               |               |                |            |               |            |  |  |  |

| bit 6 |                                                                                                         | Converter Ir              |               |               |                |            |               |            |  |  |  |

|       |                                                                                                         | s the A/D in              | •             |               |                |            |               |            |  |  |  |

|       | 0 = Disable                                                                                             | es the A/D ir             | nterrupt      |               |                |            |               |            |  |  |  |

| bit 5 | RCIE: USA                                                                                               | RT Receive                | e Interrupt E | nable bit     |                |            |               |            |  |  |  |

|       |                                                                                                         | s the USAR                |               |               |                |            |               |            |  |  |  |

| h:+ 4 |                                                                                                         | es the USAF               |               | •             |                |            |               |            |  |  |  |

| bit 4 |                                                                                                         | RT Transmi<br>s the USAR  |               |               |                |            |               |            |  |  |  |

|       |                                                                                                         | s the USAR                |               |               |                |            |               |            |  |  |  |

| bit 3 | SSPIE: Ma                                                                                               | ster Synchr               | onous Seria   | l Port Interr | upt Enable bit |            |               |            |  |  |  |

|       |                                                                                                         | s the MSSP                |               |               |                |            |               |            |  |  |  |

|       |                                                                                                         | es the MSSF               |               |               |                |            |               |            |  |  |  |

| bit 2 |                                                                                                         | CP1 Interru               |               | it            |                |            |               |            |  |  |  |

|       |                                                                                                         | s the CCP1<br>is the CCP1 | -             |               |                |            |               |            |  |  |  |

| bit 1 |                                                                                                         | MR2 to PR2                | •             | rrunt Enable  | - hit          |            |               |            |  |  |  |

| bit i |                                                                                                         | s the TMR2                |               | •             |                |            |               |            |  |  |  |

|       |                                                                                                         | es the TMR2               |               |               |                |            |               |            |  |  |  |

| bit 0 | TMR1IE: T                                                                                               | MR1 Overflo               | ow Interrupt  | Enable bit    |                |            |               |            |  |  |  |

|       |                                                                                                         | s the TMR1                |               |               |                |            |               |            |  |  |  |

|       | 0 = Disable                                                                                             | es the TMR1               | overflow in   | iterrupt      |                |            |               |            |  |  |  |

|       | Legend:                                                                                                 |                           |               |               |                |            |               | ]          |  |  |  |

|       | R = Reada                                                                                               | hla hit                   | \\/ \\        | /ritable bit  | U = Unimple    | omontad hi | it read as "  | <b>ר</b> י |  |  |  |

|       | - n = Value                                                                                             |                           |               | Bit is set    | 0 = 0 minipi   |            | x = Bit is ur |            |  |  |  |

|       | - n = value                                                                                             | al FUR                    | I = D         | IL IS SEL     | U = DILISC     | lealeu     | x = Dit is uf | INTOWN     |  |  |  |

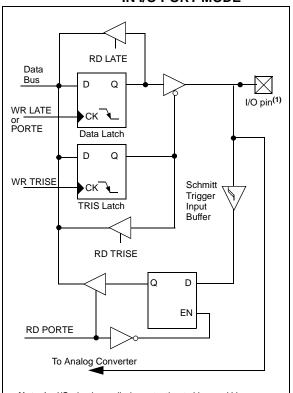

#### 8.5 PORTE, TRISE and LATE Registers

This section is only applicable to the PIC18C4X2 devices.

PORTE is a 3-bit wide, bi-directional port. The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

| Note: | On a Power-on Reset, these pins are con- |

|-------|------------------------------------------|

|       | figured as digital inputs.               |

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register reads and writes the latched output value for PORTE.

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7), which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

Register 8-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

| Note: | On a Power-on Reset, these pins are con- |

|-------|------------------------------------------|

|       | figured as analog inputs.                |

#### EXAMPLE 8-5: INITIALIZING PORTE

| CLRF  | PORTE  | ; Initialize PORTE by |

|-------|--------|-----------------------|

|       |        | ; clearing output     |

|       |        | ; data latches        |

| CLRF  | LATE   | ; Alternate method    |

|       |        | ; to clear output     |

|       |        | ; data latches        |

| MOVLW | 0x07   | ; Configure A/D       |

| MOVWF | ADCON1 | ; for digital inputs  |

| MOVLW | 0x03   | ; Value used to       |

|       |        | ; initialize data     |

|       |        | ; direction           |

| MOVWF | TRISC  | ; Set RE<0> as inputs |

|       |        | ; RE<1> as outputs    |

|       |        | ; RE<2> as inputs     |

|       |        |                       |

#### FIGURE 8-9:

#### PORTE BLOCK DIAGRAM IN I/O PORT MODE

Note 1: I/O pins have diode protection to VDD and Vss.

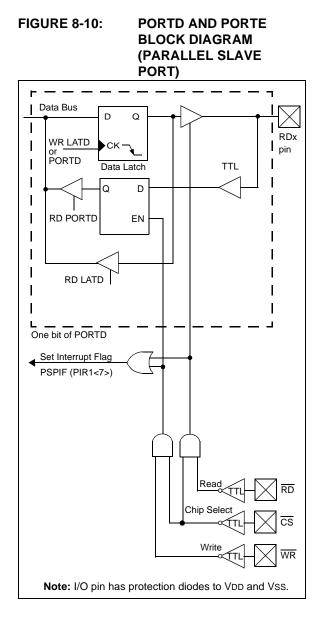

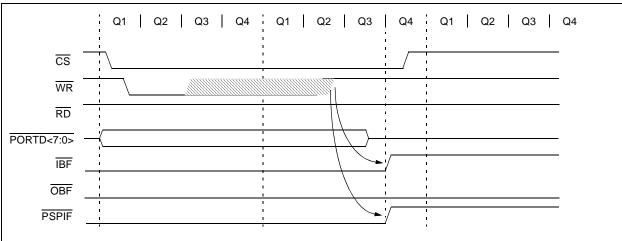

#### 8.6 Parallel Slave Port

The Parallel Slave Port is implemented on the 40-pin devices only (PIC18C4X2).

PORTD operates as an 8-bit wide, parallel slave port, or microprocessor port, when control bit PSPMODE (TRISE<4>) is set. It is asynchronously readable and writable by the external world through RD control input pin RE0/RD and WR control input pin RE1/WR.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, <u>RE1/WR</u> to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

A write to the PSP occurs when both the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  lines are first detected low.

The PORTE I/O pins become control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs), and the ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

#### FIGURE 8-11: PARALLEL SLAVE PORT WRITE WAVEFORMS

### 12.0 TIMER3 MODULE

The Timer3 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers: TMR3H and TMR3L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

- Reset from CCP module trigger

Figure 12-1 is a simplified block diagram of the Timer3 module.

Register 12-1 shows the Timer3 control register. This register controls the operating mode of the Timer3 module and sets the CCP clock source.

Register 10-1 shows the Timer1 control register. This register controls the operating mode of the Timer1 module, as well as contains the Timer1 oscillator enable bit (T1OSCEN), which can be a clock source for Timer3.

#### REGISTER 12-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|--------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |        |        | bit 0  |

| bit 7   | <b>RD16:</b> 16-bit Read/Write M<br>1 = Enables register Read/                                                                         |                                               | e 16-bit operation                   |      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------|------|

|         | 0 = Enables register Read/                                                                                                             | Write of Timer3 in two                        | 8-bit operations                     |      |

| bit 6-3 | T3CCP2:T3CCP1: Timer3                                                                                                                  | and Timer1 to CCPx B                          | Enable bits                          |      |

|         | 1x = Timer3 is the clock so<br>01 = Timer3 is the clock so<br>Timer1 is the clock so<br>00 = Timer1 is the clock so                    | urce for compare/cap<br>ource for compare/cap | ture of CCP2,<br>ture of CCP1        |      |

| bit 5-4 | T3CKPS1:T3CKPS0: Time                                                                                                                  | r3 Input Clock Presca                         | le Select bits                       |      |

|         | 11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                               |                                               |                                      |      |

| bit 2   | T3SYNC: Timer3 External (<br>(Not usable if the system clWhen TMR3CS = 1:1 = Do not synchronize external cl0 = Synchronize external cl | ock comes from Time<br>ernal clock input      |                                      |      |

|         | When TMR3CS = 0:                                                                                                                       |                                               |                                      |      |

|         | This bit is ignored. Timer3 u                                                                                                          | uses the internal clock                       | when TMR3CS = 0.                     |      |

| bit 1   | TMR3CS: Timer3 Clock So                                                                                                                | urce Select bit                               |                                      |      |

|         | <ol> <li>1 = External clock input from<br/>(on the rising edge after<br/>0 = Internal clock (Fosc/4)</li> </ol>                        |                                               |                                      |      |

| bit 0   | TMR3ON: Timer3 On bit                                                                                                                  |                                               |                                      |      |

|         | 1 = Enables Timer3<br>0 = Stops Timer3                                                                                                 |                                               |                                      |      |

|         | Legend:                                                                                                                                |                                               |                                      |      |

|         | R = Readable bit                                                                                                                       | W = Writable bit                              | U = Unimplemented bit, read as '0'   |      |

|         | - n = Value at POR reset                                                                                                               | '1' = Bit is set                              | '0' = Bit is cleared x = Bit is unkr | nown |

#### 13.5.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 13-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F       | 0x1F       | 0x17       |

| Maximum Resolution (bits)  | 14       | 12       | 10        | 8          | 7          | 6.58       |

#### TABLE 13-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Name    | Bit 7                | Bit 6                               | Bit 5       | Bit 4   | Bit 3 Bit 2 Bit 1 Bit 0 |        |         |         | PC   | ie on<br>)R,<br>)R | Value on<br>all other<br>RESETS |      |

|---------|----------------------|-------------------------------------|-------------|---------|-------------------------|--------|---------|---------|------|--------------------|---------------------------------|------|

| INTCON  | GIE/<br>GIEH         | PEIE/<br>GIEL                       | TMR0IE      | INTOIE  | RBIE                    | TMR0IF | INTOIF  | RBIF    | 0000 | 000x               | 0000                            | 000u |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                                | RCIF        | TXIF    | SSPIF                   | CCP1IF | TMR2IF  | TMR1IF  | 0000 | 0000               | 0000                            | 0000 |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                                | RCIE        | TXIE    | SSPIE                   | CCP1IE | TMR2IE  | TMR1IE  | 0000 | 0000               | 0000                            | 0000 |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP                                | RCIP        | TXIP    | SSPIP                   | CCP1IP | TMR2IP  | TMR1IP  | 0000 | 0000               | 0000                            | 0000 |

| TRISC   | PORTC Da             | ata Direction                       | Register    |         |                         |        |         |         | 1111 | 1111               | 1111                            | 1111 |

| TMR2    | Timer2 Mo            | dule Registe                        | er          |         |                         |        |         |         | 0000 | 0000               | 0000                            | 0000 |

| PR2     | Timer2 Mo            | dule Period                         | Register    |         |                         |        |         |         | 1111 | 1111               | 1111                            | 1111 |

| T2CON   | _                    | TOUTPS3                             | TOUTPS2     | TOUTPS1 | TOUTPS0                 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000               | -000                            | 0000 |

| CCPR1L  | Capture/Co           | ompare/PWI                          | M Register1 | (LSB)   |                         |        |         |         | xxxx | xxxx               | uuuu                            | uuuu |

| CCPR1H  | Capture/Co           | ompare/PWI                          | M Register1 | (MSB)   |                         |        |         |         | xxxx | xxxx               | uuuu                            | uuuu |

| CCP1CON | _                    | _                                   | DC1B1       | DC1B0   | CCP1M3                  | CCP1M2 | CCP1M1  | CCP1M0  | 00   | 0000               | 00                              | 0000 |

| CCPR2L  | Capture/Co           | Capture/Compare/PWM Register2 (LSB) |             |         |                         |        |         |         |      | xxxx               | uuuu                            | uuuu |

| CCPR2H  | Capture/Co           | ompare/PWI                          | M Register2 | (MSB)   |                         |        |         |         | xxxx | xxxx               | uuuu                            | uuuu |

| CCP2CON |                      |                                     | DC2B1       | DC2B0   | CCP2M3                  | CCP2M2 | CCP2M1  | CCP2M0  | 00   | 0000               | 00                              | 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

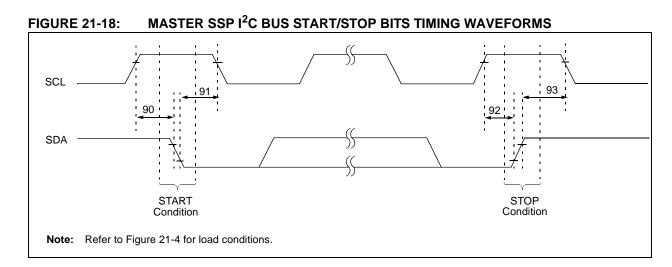

#### 14.4.8 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address, or the other half of a 10-bit address, is accomplished by simply writing a value to the SSPBUF register. This action will set the buffer full flag bit, BF, and allow the baud rate generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter 106). SCL is held low for one baud rate generator rollover count (TBRG). Data should be valid before SCL is released high (see Data setup time specification parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. allowing the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurs, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (baud rate generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 14-18).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will de-assert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the baud rate generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 14.4.8.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared, when all 8 bits are shifted out.

#### 14.4.8.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress, (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 14.4.8.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$ , and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

#### 14.4.9 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

# Note: The MSSP module must be in an IDLE state before the RCEN bit is set, or the RCEN bit will be disregarded.

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the baud rate generator is suspended from counting, holding SCL low. The MSSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception, by setting the Acknowledge sequence enable bit. ACKEN (SSPCON2<4>).

#### 14.4.9.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 14.4.9.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 14.4.9.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

| TABLE 15-5: | BAUD RATES FOR ASYNCHRONOUS MODE (B | 3RGH = 1) |

|-------------|-------------------------------------|-----------|

|-------------|-------------------------------------|-----------|

| BAUD        | Fosc = 40 MHz         |            |                             | Fosc = 20 MHz         |            |                             | Fosc = 16 MHz         |            |                             | Fosc = 10 MHz         |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 9.6         | 9.77                  | -1.70      | 255                         | 9.615                 | +0.16      | 129                         | 9.615                 | +0.16      | 103                         | 9.615                 | +0.16      | 64                          |

| 19.2        | 19.23                 | -0.16      | 129                         | 19.230                | +0.16      | 64                          | 19.230                | +0.16      | 51                          | 18.939                | -1.36      | 32                          |

| 38.4        | 38.46                 | -0.16      | 64                          | 37.878                | -1.36      | 32                          | 38.461                | +0.16      | 25                          | 39.062                | +1.7       | 15                          |

| 57.6        | 58.14                 | -0.93      | 42                          | 56.818                | -1.36      | 21                          | 58.823                | +2.12      | 16                          | 56.818                | -1.36      | 10                          |

| 115.2       | 113.64                | +1.38      | 21                          | 113.63                | -1.36      | 10                          | 111.11                | -3.55      | 8                           | 125                   | +8.51      | 4                           |

| 250         | 250.00                | 0          | 9                           | 250                   | 0          | 4                           | 250                   | 0          | 3                           | NA                    | _          | _                           |

| 625         | 625.00                | 0          | 3                           | 625                   | 0          | 1                           | NA                    | _          | _                           | 625                   | 0          | 0                           |

| 1250        | 1250.00               | 0          | 1                           | 1250                  | 0          | 0                           | NA                    | _          | _                           | NA                    | _          | _                           |

| BAUD        | Fo                    | SC = 7.16  | 6MHz                        | Fos                   | SC = 5.06  | 8 MHz                       | F                     | osc = 4 I  | MHz                         | Fosc                  | = 3.5795   | 645 MHz                     |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 9.6         | 9.520                 | -0.83      | 46                          | 9.6                   | 0          | 32                          | NA                    | _          | _                           | 9.727                 | +1.32      | 22                          |

| 19.2        | 19.454                | +1.32      | 22                          | 18.645                | -2.94      | 16                          | 1.202                 | +0.17      | 207                         | 18.643                | -2.90      | 11                          |

| 38.4        | 37.286                | -2.90      | 11                          | 39.6                  | +3.12      | 7                           | 2.403                 | +0.13      | 103                         | 37.286                | -2.90      | 5                           |

| 57.6        | 55.930                | -2.90      | 7                           | 52.8                  | -8.33      | 5                           | 9.615                 | +0.16      | 25                          | 55.930                | -2.90      | 3                           |

| 115.2       | 111.860               | -2.90      | 3                           | 105.6                 | -8.33      | 2                           | 19.231                | +0.16      | 12                          | 111.86                | -2.90      | 1                           |

| 250         | NA                    | _          | _                           | NA                    | _          | _                           | NA                    | _          | _                           | 223.72                | -10.51     | 0                           |

| 625         | NA                    | _          | _                           |

| 1250        | NA                    | —          | —                           |

| BAUD        | F                     | osc = 1    | MHz                         | Fos                   | c = 32.70  | 68 kHz                      |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 9.6         | 8.928                 | -6.99      | 6                           | NA                    | _          | _                           |

| 19.2        | 20.833                | +8.51      | 2                           | NA                    | —          | —                           |

| 38.4        | 31.25                 | -18.61     | 1                           | NA                    | —          | —                           |

| 57.6        | 62.5                  | +8.51      | 0                           | NA                    | —          | _                           |

| 115.2       | NA                    | —          | _                           | NA                    | —          | _                           |

| 250         | NA                    | —          | _                           | NA                    | —          | _                           |

| 625         | NA                    | —          | —                           | NA                    | —          | —                           |

| 1250        | NA                    | —          |                             | NA                    | —          | —                           |

#### 15.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner, (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 15.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 15-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and inter-

rupt bit TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE, and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit, which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 15.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

| Name   | Bit 7                | Bit 6         | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|----------------------|---------------|-------------|--------|-------|--------|--------|--------|-------------------------|---------------------------------|

| INTCON | GIE/<br>GIEH         | PEIE/<br>GIEL | TMR0IE      | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x               | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF          | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE          | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP          | RCIP        | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 0000 0000               | 0000 0000                       |

| RCSTA  | SPEN                 | RX9           | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| TXREG  | USART T              | ransmit F     | Register    |        |       |        |        |        | 0000 0000               | 0000 0000                       |

| TXSTA  | CSRC                 | TX9           | TXEN        | SYNC   |       | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| SPBRG  | Baud Rate            | e Genera      | ator Regist | er     |       |        |        |        | 0000 0000               | 0000 0000                       |

#### TABLE 15-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'.

Shaded cells are not used for Synchronous Master Transmission.

**Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

The value that is in the ADRESH/ADRESL registers is not modified for a Power-on Reset. The ADRESH/ ADRESL registers will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 16.1. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- · Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear ADIF bit

- Set ADIE bit

- · Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared

OR

- Waiting for the A/D interrupt

- 6. Read A/D Result registers (ADRESH/ADRESL); clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

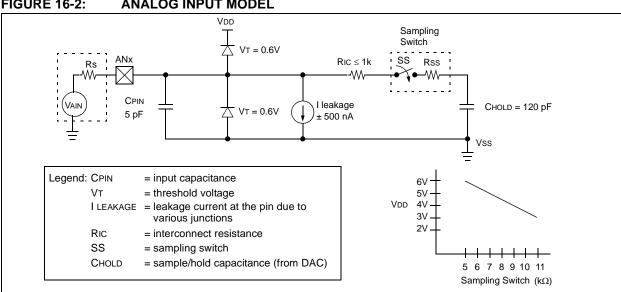

#### **FIGURE 16-2:** ANALOG INPUT MODEL

#### 16.1 A/D Acquisition Requirements

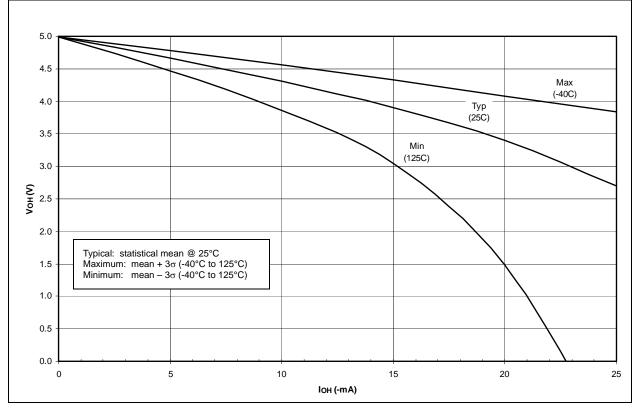

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 16-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

When the conversion is started, the hold-Note: ing capacitor is disconnected from the input pin.

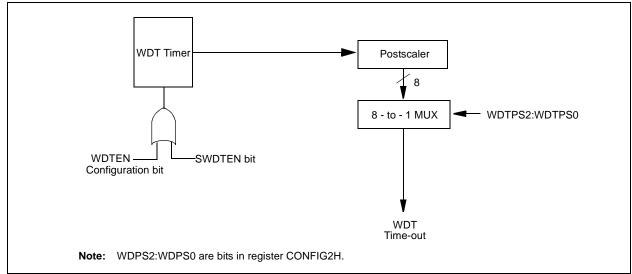

#### 18.2.2 WDT POSTSCALER

The WDT has a postscaler that can extend the WDT Reset period. The postscaler is selected at the time of device programming, by the value written to the CONFIG2H configuration register.

#### TABLE 18-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|

| CONFIG2H | —     | —     | _     | _     | WDTPS2 | WDTPS2 | WDTPS0 | WDTEN  |

| RCON     | IPEN  | LWRT  | —     | RI    | TO     | PD     | POR    | BOR    |

| WDTCON   | —     | _     |       |       |        |        | _      | SWDTEN |

Legend: Shaded cells are not used by the Watchdog Timer.

| RETFIE            | Return fr                                                                                                                                                | om Inte                                                                                                                       | rrupt                                                                                                               |                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Syntax:           | [ label ]                                                                                                                                                | RETFIE                                                                                                                        | [s]                                                                                                                 |                                                                                |

| Operands:         | $s \in [0,1]$                                                                                                                                            |                                                                                                                               |                                                                                                                     |                                                                                |

| Operation:        | $(TOS) \rightarrow$<br>$1 \rightarrow GIE/$<br>if $s = 1$<br>$(WS) \rightarrow V$<br>(STATUS)<br>(BSRS) -<br>PCLATU,                                     | GIEH or<br>WREG,<br>S) → ST<br>→ BSR,                                                                                         | ATUS,                                                                                                               | ·                                                                              |

| Status Affected:  | GIE/GIEF                                                                                                                                                 | H,PEIE/G                                                                                                                      | IEL.                                                                                                                |                                                                                |

| Encoding:         | 0000                                                                                                                                                     | 0000                                                                                                                          | 0001                                                                                                                | 000s                                                                           |

| Description:      | Return fro<br>popped a<br>loaded in<br>enabled b<br>or low pri<br>enable bi<br>the shado<br>STATUSS<br>into their<br>WREG, S<br>'s' = 0, no<br>occurs (d | nd Top-o<br>to the PC<br>by setting<br>ority glob<br>t. If 's' =<br>bw regist<br>S and BS<br>correspo<br>STATUS a<br>b update | of-Stack (<br>C. Interru<br>g either th<br>bal interru<br>1, the co<br>ers WS,<br>GRS are I<br>onding re<br>and BSR | TOS) is<br>pts are<br>he high<br>upt<br>ntents of<br>oaded<br>gisters,<br>. If |

| Words:            | 1                                                                                                                                                        |                                                                                                                               |                                                                                                                     |                                                                                |

| Cycles:           | 2                                                                                                                                                        |                                                                                                                               |                                                                                                                     |                                                                                |

| Q Cycle Activity: |                                                                                                                                                          |                                                                                                                               |                                                                                                                     |                                                                                |

| Q1                | Q2                                                                                                                                                       | Q3                                                                                                                            | }                                                                                                                   | Q4                                                                             |

| RET   | LW                                                                                                                                                                                                          | Return Li           | iteral to                                                                         | WREG | 3                                     |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------|------|---------------------------------------|--|--|--|

| Synt  | ax:                                                                                                                                                                                                         | [ label ]           | RETLW                                                                             | k    |                                       |  |  |  |

| Ope   | rands:                                                                                                                                                                                                      | $0 \le k \le 25$    | 5                                                                                 |      |                                       |  |  |  |

| Ope   | ration:                                                                                                                                                                                                     | $(TOS) \rightarrow$ | $k \rightarrow WREG$ ,<br>(TOS) $\rightarrow$ PC,<br>PCLATU, PCLATH are unchanged |      |                                       |  |  |  |

| Statu | us Affected:                                                                                                                                                                                                | None                |                                                                                   |      |                                       |  |  |  |

| Enco  | oding:                                                                                                                                                                                                      | 0000                | 1100                                                                              | kkkk | kkkk                                  |  |  |  |

| Desi  | Description: WREG is loaded with the eight-bit<br>literal 'k'. The program counter is<br>loaded from the top of the stack<br>(the return address). The high<br>address latch (PCLATH) remains<br>unchanged. |                     |                                                                                   |      |                                       |  |  |  |

| Wor   | ds:                                                                                                                                                                                                         | 1                   |                                                                                   |      |                                       |  |  |  |

| Cycl  | es:                                                                                                                                                                                                         | 2                   |                                                                                   |      |                                       |  |  |  |

| QC    | ycle Activity:                                                                                                                                                                                              |                     |                                                                                   |      |                                       |  |  |  |

|       | Q1                                                                                                                                                                                                          | Q2                  | Q3                                                                                | 3    | Q4                                    |  |  |  |

|       | Decode                                                                                                                                                                                                      | Read<br>literal 'k' | Proce<br>Data                                                                     | a s  | op PC from<br>stack, Write<br>to WREG |  |  |  |

|       | No<br>operation                                                                                                                                                                                             | No<br>operation     | No<br>operat                                                                      | ion  | No<br>operation                       |  |  |  |

#### Example:

| CALL I | ABLE | ;<br>;<br>; | WREG contains table<br>offset value<br>WREG now has<br>table value |

|--------|------|-------------|--------------------------------------------------------------------|

| :      |      |             |                                                                    |

| TABLE  |      |             |                                                                    |

| ADDWF  | PCL  | ;           | WREG = offset                                                      |

| RETLW  | k0   | ;           | Begin table                                                        |

| RETLW  | k1   | ;           |                                                                    |

| :      |      |             |                                                                    |

| :      |      |             |                                                                    |

| RETLW  | kn   | ;           | End of table                                                       |

#### **Before Instruction**

| WREG = UXU/ | WREG | = | 0x07 |  |

|-------------|------|---|------|--|

|-------------|------|---|------|--|

After Instruction

WREG = value of kn

| Q1        | Q2        | Q3        | Q4                   |

|-----------|-----------|-----------|----------------------|

| Decode    | No        | No        | pop PC from<br>stack |

|           | operation | operation | stack                |

|           |           |           | Set GIEH or          |

|           |           |           | GIEL                 |

| No        | No        | No        | No                   |

| operation | operation | operation | operation            |

#### Example: RETFIE 1

#### After Interrupt

| PC        | =          | TOS     |

|-----------|------------|---------|

| W         | =          | WS      |

| BSR       | =          | BSRS    |

| STATUS    | =          | STATUSS |

| GIE/GIEH, | PEIE/GIEL= | 1       |

| RLNCF                                     | Rotate Lo                                                                                      | eft f (no carı                                                                     | ry)                                                                                                                      |

|-------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                   | [ label ]                                                                                      | RLNCF f                                                                            | [,d [,a]                                                                                                                 |

| Operands:                                 | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                                             | 5                                                                                  |                                                                                                                          |

| Operation:                                | $(f) \rightarrow$<br>$(f<7>) \rightarrow$                                                      | dest <n+1>,<br/>dest&lt;0&gt;</n+1>                                                |                                                                                                                          |

| Status Affected:                          | N,Z                                                                                            |                                                                                    |                                                                                                                          |

| Encoding:                                 | 0100                                                                                           | 01da ff                                                                            | ff ffff                                                                                                                  |

| Description:                              | rotated or<br>the result<br>is 1, the r<br>ister 'f' (de<br>Access B<br>riding the<br>the bank | is placed in<br>esult is store<br>efault). If 'a' i<br>ank will be s<br>BSR value. | eft. If 'd' is 0,<br>WREG. If 'd'<br>d back in reg-<br>s 0, the<br>elected, over-<br>If 'a' is 1, then<br>red as per the |

| Words:                                    | 1                                                                                              |                                                                                    |                                                                                                                          |

| Cycles:                                   | 1                                                                                              |                                                                                    |                                                                                                                          |

| •                                         | 1                                                                                              |                                                                                    |                                                                                                                          |

| Q Cycle Activity:<br>Q1                   | Q2                                                                                             | Q3                                                                                 | Q4                                                                                                                       |

| Decode                                    | Read<br>register 'f'                                                                           | Process<br>Data                                                                    | Write to<br>destination                                                                                                  |

| Example:                                  | RLNCF                                                                                          | REG, 1,                                                                            | 0                                                                                                                        |

| Before Instruct<br>REG<br>After Instructi | = 1010 1                                                                                       | 011                                                                                |                                                                                                                          |

| REG                                       | = 0101 0                                                                                       | 111                                                                                |                                                                                                                          |

| RRCF             | Rotate Ri                                                                                                                              | ght f th                                                                                                   | rough C                                                                                                      | arry                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Syntax:          | [ label ]                                                                                                                              | RRCF                                                                                                       | f [,d [,a]                                                                                                   |                                                                            |

| Operands:        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                    | 5                                                                                                          |                                                                                                              |                                                                            |

| Operation:       | $(f < n >) \rightarrow (f < 0 >) \rightarrow (f < 0 >) \rightarrow (C) \rightarrow des$                                                | C,                                                                                                         | 1>,                                                                                                          |                                                                            |

| Status Affected: | C,N,Z                                                                                                                                  |                                                                                                            |                                                                                                              |                                                                            |

| Encoding:        | 0011                                                                                                                                   | 00da                                                                                                       | ffff                                                                                                         | ffff                                                                       |

|                  | The conterrotated on<br>the Carry<br>is placed in<br>result is p<br>(default).<br>Bank will<br>the BSR v<br>bank will the<br>BSR value | e bit to<br>Flag. If<br>in WRE<br>laced ba<br>lf 'a' is 0<br>be selec<br>value. If<br>be selec<br>e (defau | the right<br>'d' is 0, th<br>G. If 'd' is<br>ack in reg<br>the Acc<br>ted, over<br>'a' is 1, th<br>ted as pe | through<br>ne resu<br>s 1, the<br>gister 'f'<br>cess<br>rriding<br>hen the |

| Words:           | 1                                                                                                                                      |                                                                                                            |                                                                                                              |                                                                            |

| Cycles:          | 1                                                                                                                                      |                                                                                                            |                                                                                                              |                                                                            |

| Q Cycle Activity | /:                                                                                                                                     |                                                                                                            |                                                                                                              |                                                                            |

| Q1               | Q2                                                                                                                                     | Q                                                                                                          | 3                                                                                                            | Q4                                                                         |

| Decode           | Read<br>register 'f'                                                                                                                   | Proce<br>Data                                                                                              |                                                                                                              | Vrite to<br>stinatior                                                      |

| Example:         | RRCF                                                                                                                                   | REG,                                                                                                       | 0, 0                                                                                                         |                                                                            |

| Before Instr     | ruction<br>= 1110 (                                                                                                                    | 110                                                                                                        |                                                                                                              |                                                                            |

After Instruction

REG = 1110 0110 WREG = 0111 0011 C = 0

| DC CHARACTERISTICS |        |                                                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +40^{\circ}C$ |       |       |                                                       |  |  |  |

|--------------------|--------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------|-------|-------------------------------------------------------|--|--|--|

| Param.<br>No.      | Sym    | Characteristic                                        | Min                                                                                                                   | Max   | Units | Conditions                                            |  |  |  |