Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                              |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c442-e-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 3.1 Power-on Reset (POR)

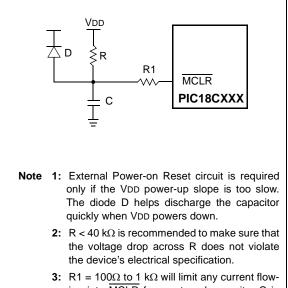

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR circuitry, just tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 3-2.

When the device starts normal operation (i.e., exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

FIGURE 3-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

ing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

### 3.2 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (parameter #33) only on power-up from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameter #33 for details.

## 3.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

### 3.4 PLL Lock Time-out

With the PLL enabled, the time-out sequence following a Power-on Reset is different from other oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator startup time-out (OST).

### 3.5 Brown-out Reset (BOR)

A configuration bit, BOREN, can disable (if clear/ programmed), or enable (if set) the Brown-out Reset circuitry. If VDD falls below parameter D005 for greater than parameter #35, the brown-out situation will reset the chip. A RESET may not occur if VDD falls below parameter D005 for less than parameter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer will then be invoked and will keep the chip in RESET an additional time delay (parameter #33). If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute the additional time delay.

### 3.6 Time-out Sequence

On power-up, the time-out sequence is as follows: First, PWRT time-out is invoked after the POR time delay has expired. Then, OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 3-3, Figure 3-4, Figure 3-5, Figure 3-6 and Figure 3-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC18CXXX device operating in parallel.

Table 3-2 shows the RESET conditions for some Special Function Registers, while Table 3-3 shows the RESET conditions for all the registers.

### $\ensuremath{\textcircled{}^{\circ}}$ 1999-2013 Microchip Technology Inc.

#### **REGISTER FILE SUMMARY (CONTINUED) TABLE 4-2:**

| File Name | Bit 7                                     | Bit 6                 | Bit 5          | Bit 4           | Bit 3          | Bit 2                     | Bit 1                         | Bit 0  | Value on<br>POR,<br>BOR | Details<br>on page: |

|-----------|-------------------------------------------|-----------------------|----------------|-----------------|----------------|---------------------------|-------------------------------|--------|-------------------------|---------------------|

| IPR2      | _                                         | _                     | _              | —               | BCLIP          | LVDIP                     | TMR3IP                        | CCP2IP | 1111                    | 73                  |

| PIR2      | —                                         | —                     | _              | —               | BCLIF          | LVDIF                     | TMR3IF                        | CCP2IF | 0000                    | 69                  |

| PIE2      | _                                         | _                     | _              | _               | BCLIE          | LVDIE                     | TMR3IE                        | CCP2IE | 0000                    | 71                  |

| IPR1      | PSPIP                                     | ADIP                  | RCIP           | TXIP            | SSPIP          | CCP1IP                    | TMR2IP                        | TMR1IP | 1111 1111               | 72                  |

| PIR1      | PSPIF                                     | ADIF                  | RCIF           | TXIF            | SSPIF          | CCP1IF                    | TMR2IF                        | TMR1IF | 0000 0000               | 68                  |

| PIE1      | PSPIE                                     | ADIE                  | RCIE           | TXIE            | SSPIE          | CCP1IE                    | TMR2IE                        | TMR1IE | 0000 0000               | 70                  |

| TRISE     | IBF                                       | OBF                   | IBOV           | PSPMODE         | _              | Data Direction            | on bits for PO                | RTE    | 0000 -111               | 88                  |

| TRISD     | Data Directi                              | on Control Re         | gister for POR | TD              |                |                           |                               |        | 1111 1111               | 85                  |

| TRISC     | Data Directi                              | on Control Re         | gister for POR | TC              |                |                           |                               |        | 1111 1111               | 83                  |

| TRISB     | Data Direction Control Register for PORTB |                       |                |                 |                |                           |                               |        |                         | 80                  |

| TRISA     | _                                         | TRISA6 <sup>(1)</sup> | Data Directi   | on Control Reg  | ister for PORT | A                         |                               |        | -111 1111               | 77                  |

| LATE      | -                                         | —                     | _              | —               | -              |                           | E Data Latch,<br>E Data Latch |        | xxx                     | 87                  |

| LATD      | Read PORT                                 | D Data Latch,         | Write PORTE    | Data Latch      | •              |                           |                               |        | xxxx xxxx               | 85                  |

| LATC      | Read PORT                                 | C Data Latch,         | Write PORTO    | C Data Latch    |                |                           |                               |        | xxxx xxxx               | 83                  |

| LATB      | Read PORT                                 | B Data Latch,         | Write PORTE    | B Data Latch    |                |                           |                               |        | xxxx xxxx               | 80                  |

| LATA      | _                                         | LATA6 <sup>(1)</sup>  | Read PORT      | A Data Latch, V | Write PORTA    | Data Latch <sup>(1)</sup> |                               |        | -xxx xxxx               | 77                  |

| PORTE     | Read PORT                                 | E pins, Write         | PORTE Data     | Latch           |                |                           |                               |        | 000                     | 87                  |

| PORTD     | Read PORT                                 | D pins, Write         | PORTD Data     | Latch           |                |                           |                               |        | xxxx xxxx               | 85                  |

| PORTC     | Read PORT                                 | C pins, Write         | PORTC Data     | Latch           |                |                           |                               |        | xxxx xxxx               | 83                  |

| PORTB     | Read PORT                                 | B pins, Write         | PORTB Data     | Latch           |                |                           |                               |        | xxxx xxxx               | 80                  |

| PORTA     | —                                         | RA6 <sup>(1)</sup>    | Read PORT      | A pins, Write P | ORTA Data La   | atch <sup>(1)</sup>       |                               |        | -x0x 0000               | 77                  |

Legend: x = unknown, u = unchanged, - = unimplemented, g = value depends on condition

Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO oscillator mode only, and read '0' in all other oscillator modes.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

### 4.13 STATUS Register

The STATUS register, shown in Register 4-2, contains the arithmetic status of the ALU. The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, then the write to these five bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the STATUS register as destination may be different than intended. For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits from the STATUS register. For other instructions not affecting any status bits, see Table 19-2.

| Note: | The C and DC bits operate as a borrow and      |

|-------|------------------------------------------------|

|       | digit borrow bit respectively, in subtraction. |

### REGISTER 4-2: STATUS REGISTER

| U-0   | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | N     | OV    | Z     | DC    | С     |

| bit 7 |     |     |       |       |       |       | bit 0 |

### bit 7-5 Unimplemented: Read as '0'

bit 4 N: Negative bit

This bit is used for signed arithmetic (2's complement). It indicates whether the result was negative, (ALU MSB = 1).

- 1 = Result was negative

- 0 = Result was positive

| bit 3 <b>OV:</b> Overflow bit |

|-------------------------------|

|-------------------------------|

This bit is used for signed arithmetic (2's complement). It indicates an overflow of the 7-bit magnitude, which causes the sign bit (bit7) to change state.

- 1 = Overflow occurred for signed arithmetic (in this arithmetic operation)

- 0 = No overflow occurred

bit 2 Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

#### bit 1 DC: Digit carry/borrow bit

For ADDWF, ADDLW, SUBLW, and SUBWF instructions

1 = A carry-out from the 4th low order bit of the result occurred

- 0 = No carry-out from the 4th low order bit of the result

- **Note:** For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the bit 4 or bit 3 of the source register.

#### bit 0 **C:** Carry/borrow bit

For ADDWF, ADDLW, SUBLW, and SUBWF instructions

- 1 = A carry-out from the Most Significant bit of the result occurred

- 0 = No carry-out from the Most Significant bit of the result occurred

- **Note:** For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### REGISTER 8-1: TRISE REGISTER

- n = Value at POR

|       | R-0              | R-0                            | R/W-0         | R/W-0            | U-0           | R/W-1       | R/W-1          | R/W-1  |

|-------|------------------|--------------------------------|---------------|------------------|---------------|-------------|----------------|--------|

|       | IBF              | OBF                            | IBOV          | PSPMODE          | _             | TRISE2      | TRISE1         | TRISE0 |

|       | bit 7            |                                |               |                  |               |             |                | bit 0  |

|       |                  |                                |               |                  |               |             |                |        |

| bit 7 | IBF: Input       | Buffer Full S                  | Status bit    |                  |               |             |                |        |

|       | 1 = A word       | d has been r                   | eceived an    | d waiting to be  | e read by the | e CPU       |                |        |

|       | 0 <b>= No wo</b> | rd has been                    | received      |                  |               |             |                |        |

| bit 6 | OBF: Outp        | out Buffer Fu                  | ull Status bi | t                |               |             |                |        |

|       |                  |                                |               | previously write | tten word     |             |                |        |

|       |                  | utput buffer I                 |               |                  |               |             |                |        |

| bit 5 | •                |                                |               | ct bit (in Micro | •             |             |                |        |

|       |                  |                                | •             | iously input wo  | ord has not   | been read   |                |        |

|       | •                | be cleared in<br>erflow occur  | ,             |                  |               |             |                |        |

| bit 4 |                  |                                |               | lode Select bit  |               |             |                |        |

| DIL 4 |                  | L. Faraller 3<br>el Slave Port |               | iode Select bit  |               |             |                |        |

|       |                  | al purpose l                   |               |                  |               |             |                |        |

| bit 3 |                  | nented: Rea                    |               |                  |               |             |                |        |

| bit 2 | •                | E2 Direction                   |               | t                |               |             |                |        |

|       | 1 = Input        |                                |               | -                |               |             |                |        |

|       | 0 = Output       | t                              |               |                  |               |             |                |        |

| bit 1 | TRISE1: R        | E1 Direction                   | n Control bi  | t                |               |             |                |        |

|       | 1 = Input        |                                |               |                  |               |             |                |        |

|       | 0 = Output       | t                              |               |                  |               |             |                |        |

| bit 0 | TRISE0: R        | E0 Direction                   | n Control bi  | t                |               |             |                |        |

|       | 1 = Input        |                                |               |                  |               |             |                |        |

|       | 0 = Output       | t                              |               |                  |               |             |                |        |

|       |                  |                                |               |                  |               |             |                |        |

|       | Legend:          |                                |               |                  |               |             |                |        |

|       | R = Reada        | able bit                       | W = V         | Writable bit     | U = Unim      | plemented l | oit, read as ' | 0'     |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

### 15.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register, and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete. An interrupt will be generated if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

| Name   | Bit 7                        | Bit 6         | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value<br>PO<br>BC | R,   | all o | e on<br>other<br>SETS |

|--------|------------------------------|---------------|--------|--------|-------|--------|--------|--------|-------------------|------|-------|-----------------------|

| INTCON | GIE/<br>GIEH                 | PEIE/<br>GIEL | TMR0IE | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000              | 000x | 0000  | 000u                  |

| PIR1   | PSPIF <sup>(1)</sup>         | ADIF          | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000              | 0000 | 0000  | 0000                  |

| PIE1   | PSPIE <sup>(1)</sup>         | ADIE          | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000              | 0000 | 0000  | 0000                  |

| IPR1   | PSPIP <sup>(1)</sup>         | ADIP          | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 0000              | 0000 | 0000  | 0000                  |

| RCSTA  | SPEN                         | RX9           | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000              | -00x | 0000  | -00x                  |

| RCREG  | USART Receive Register       |               |        |        |       |        |        |        | 0000              | 0000 | 0000  | 0000                  |

| TXSTA  | CSRC                         | TX9           | TXEN   | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000              | -010 | 0000  | -010                  |

| SPBRG  | Baud Rate Generator Register |               |        |        |       |        |        |        | 0000              | 0000 | 0000  | 0000                  |

### TABLE 15-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'.

Shaded cells are not used for Synchronous Slave Reception.

**Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

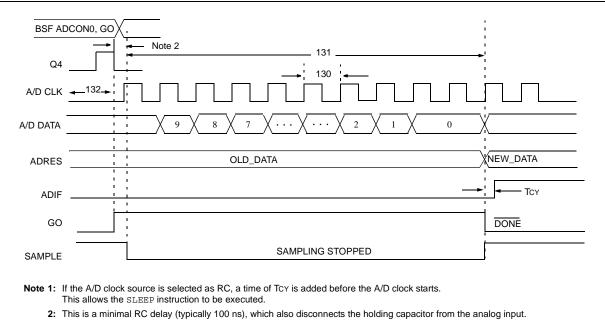

## 16.0 COMPATIBLE 10-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

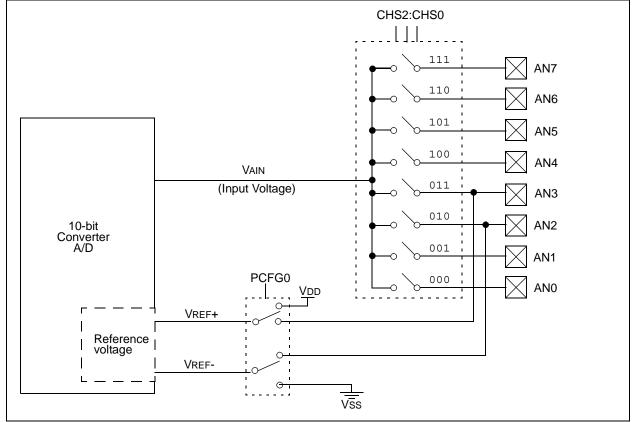

The analog-to-digital (A/D) converter module has five inputs for the PIC18C2x2 devices and eight for the PIC18C4x2 devices. This module has the ADCON0 and ADCON1 register definitions that are compatible with the mid-range A/D module.

The A/D allows conversion of an analog input signal to a corresponding 10-bit digital number.

### REGISTER 16-1: ADCON0 REGISTER

The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Register 16-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 16-2, configures the functions of the port pins.

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | _   | ADON  |

| bit 7 |       |       |       |       |         |     | bit 0 |

#### bit 7-6 ADCS1:ADCS0: A/D Conversion Clock Select bits (ADCON0 bits in **bold**)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |

|---------------------------|---------------------------------------|---------------------------------------------------------|

| 0                         | 00                                    | Fosc/2                                                  |

| 0                         | 01                                    | Fosc/8                                                  |

| 0                         | 10                                    | Fosc/32                                                 |

| 0                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 00                                    | Fosc/4                                                  |

| 1                         | 01                                    | Fosc/16                                                 |

| 1                         | 10                                    | Fosc/64                                                 |

| 1                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

bit 5-3 CHS2:CHS0: Analog Channel Select bits

- 000 = channel 0 (AN0)

- 001 = channel 1 (AN1)

- 010 = channel 2 (AN2)

- 011 = channel 3 (AN3)

- 100 = channel 4 (AN4)

- 101 = channel 5 (AN5)

- 110 = channel 6 (AN6)

- 111 = channel 7 (AN7)

- **Note:** The PIC18C2X2 devices do not implement the full 8 A/D channels; the unimplemented selections are reserved. Do not select any unimplemented channel.

bit 2 GO/DONE: A/D Conversion Status bit

When ADON = 1:

- 1 = A/D conversion in progress (setting this bit starts the A/D conversion which is automatically cleared by hardware when the A/D conversion is complete)

- 0 = A/D conversion not in progress

bit 1 Unimplemented: Read as '0'

bit 0 ADON: A/D On bit

1 = A/D converter module is powered up

0 = A/D converter module is shut-off and consumes no operating current

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and VSS) or the voltage level on the RA3/AN3/ VREF+ pin and RA2/AN2/VREF-.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off and any conversion is aborted.

Each port pin associated with the A/D converter can be configured as an analog input (RA3 can also be a voltage reference) or as a digital I/O.

The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ ADRESL registers, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 16-1.

### FIGURE 16-1: A/D BLOCK DIAGRAM

| MOVFF                                                | Move f to                                                                                                                                                                                                                                            | o f          |              |                                        |  |  |  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|----------------------------------------|--|--|--|

| Syntax:                                              | [label]                                                                                                                                                                                                                                              | MOVFF        | $f_s, f_d$   |                                        |  |  |  |

| Operands:                                            | $\begin{array}{l} 0 \leq f_s \leq 4 \\ 0 \leq f_d \leq 4 \end{array}$                                                                                                                                                                                |              |              |                                        |  |  |  |

| Operation:                                           | $(f_s) \rightarrow f_d$                                                                                                                                                                                                                              |              |              |                                        |  |  |  |

| Status Affected:                                     | None                                                                                                                                                                                                                                                 |              |              |                                        |  |  |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.) | 1100<br>1111                                                                                                                                                                                                                                         | ffff<br>ffff | ffff<br>ffff | ffff <sub>s</sub><br>ffff <sub>d</sub> |  |  |  |

| Description:                                         | The contents of source register $f_{s}$ ' are moved to destination register $f_{s}$ ' are moved to destination register $f_{s}$ ' can be anywhere in the 4096 byte data space (000h to FFFh), and location of destination $f_{d}$ ' can also be any- |              |              |                                        |  |  |  |

where from 000h to FFFh. Either source or destination can be WREG (a useful special situation). MOVFF is particularly useful for transferring a data memory location to a peripheral register (such as the transmit buffer or an I/O port).

The MOVFF instruction cannot use the PCL, TOSU, TOSH or TOSL as the destination register.

Words:

Cycles:

Q Cycle Activity:

01

| Q1     | Q2                                  | Q2 Q3           |                                 |

|--------|-------------------------------------|-----------------|---------------------------------|

| Decode | Read<br>register 'f'<br>(src)       | Process<br>Data | No<br>operation                 |

| Decode | No<br>operation<br>No dummy<br>read | No<br>operation | Write<br>register 'f'<br>(dest) |

#### Example:

MOVFF REG1, REG2

| REG1<br>REG2      | =      | 0x33<br>0x11  |

|-------------------|--------|---------------|

| After Instruction |        |               |

| REG1<br>REG2      | =<br>= | 0x33,<br>0x33 |

2 2 (3)

| MO\                   | /LB                            | Move lite           | Move literal to low nibble in BSR                                    |     |       |                           |  |  |  |  |

|-----------------------|--------------------------------|---------------------|----------------------------------------------------------------------|-----|-------|---------------------------|--|--|--|--|

| Synt                  | ax:                            | MOVLB               | k                                                                    |     |       |                           |  |  |  |  |

| Ope                   | rands:                         | $0 \le k \le 25$    | 5                                                                    |     |       |                           |  |  |  |  |

| Ope                   | ration:                        | $k \to BSR$         |                                                                      |     |       |                           |  |  |  |  |

| Status Affected: None |                                |                     |                                                                      |     |       |                           |  |  |  |  |

| Enco                  | oding:                         | 0000                | 0001                                                                 | kkl | kk    | kkkk                      |  |  |  |  |

| Desc                  | cription:                      |                     | The 8-bit literal 'k' is loaded into the Bank Select Register (BSR). |     |       |                           |  |  |  |  |

| Wor                   | ds:                            | 1                   |                                                                      |     |       |                           |  |  |  |  |

| Cycl                  | es:                            | 1                   | 1                                                                    |     |       |                           |  |  |  |  |

| QC                    | ycle Activity                  |                     |                                                                      |     |       |                           |  |  |  |  |

|                       | Q1                             | Q2                  | Q3                                                                   |     |       | Q4                        |  |  |  |  |

|                       | Decode                         | Read literal<br>'k' | Proces<br>Data                                                       |     | liter | Vrite<br>al 'k' to<br>3SR |  |  |  |  |

|                       | <u>nple</u> :<br>Before Instru | MOVLB 5             | 5                                                                    |     |       |                           |  |  |  |  |

| Before I          | nstruction |   |      |  |  |  |  |

|-------------------|------------|---|------|--|--|--|--|

| BSR               | register   | = | 0x02 |  |  |  |  |

| After Instruction |            |   |      |  |  |  |  |

| Alterins          | liucion    |   |      |  |  |  |  |

| SLEEP             | Enter SL                             | EEP mode                     |             | SUBFWB           | Subtract          | Subtract f from WREG with borrow |                  |  |  |

|-------------------|--------------------------------------|------------------------------|-------------|------------------|-------------------|----------------------------------|------------------|--|--|

| Syntax:           | [ label ]                            | SLEEP                        |             | Syntax:          | [ label ]         | [ <i>label</i> ] SUBFWB f[,d[,a] |                  |  |  |

| Operands:         | None                                 | None                         |             | Operands:        |                   | $0 \leq f \leq 255$              |                  |  |  |

| Operation:        | $00h \rightarrow W$                  | /DT,                         |             |                  | d ∈ [0,1]         |                                  |                  |  |  |

|                   |                                      | T postscaler,                |             |                  | a ∈ [0,1]         |                                  |                  |  |  |

|                   | $1 \rightarrow TO, 0 \rightarrow PD$ |                              |             | Operation:       |                   | $-(f) - (\overline{C}) -$        | → dest           |  |  |

|                   |                                      |                              |             | Status Affected: | N,OV, C,          | DC, Z                            |                  |  |  |

| Status Affected:  | TO, PD                               |                              |             | Encoding:        | 0101              | 01da f                           | fff fff          |  |  |

| Encoding:         | 0000                                 | 0000 000                     |             | Description:     |                   | register 'f' an                  |                  |  |  |

| Description:      |                                      | er-down statu                |             |                  |                   | from WREG                        |                  |  |  |

|                   |                                      | The time-out<br>et. Watchdog |             |                  |                   | thod). If 'd' is<br>WREG. If 'd' |                  |  |  |

|                   |                                      | caler are clea               |             |                  | is stored i       | in register 'f' (                | default). If 'a' |  |  |

|                   | The proc                             | essor is put i               | nto SLEEP   |                  |                   | cess Bank w                      |                  |  |  |

|                   | mode wit                             | th the oscillat              | or stopped. |                  |                   | g the BSR va<br>bank will be s   |                  |  |  |

| Nords:            | 1                                    |                              |             |                  |                   | value (defau                     |                  |  |  |

| Cycles:           | 1                                    |                              |             | Words:           | 1                 |                                  |                  |  |  |

| Q Cycle Activity  | <i>/</i> :                           |                              |             | Cycles:          | 1                 |                                  |                  |  |  |

| Q1                | Q2                                   | Q3                           | Q4          | Q Cycle Activity |                   |                                  |                  |  |  |

| Decode            | No                                   | Process                      | Go to       | Q1               | Q2                | Q3                               | Q4               |  |  |

|                   | operation                            | Data                         | sleep       | Decode           | Read              | Process                          | Write to         |  |  |

| Example:          | SLEEP                                |                              |             |                  | register 'f'      | Data                             | destination      |  |  |

| Before Instr      | uction                               |                              |             | Example 1:       | SUBFWB            | REG, 1,                          | 0                |  |  |

| $\overline{TO} =$ | ?                                    |                              |             | Before Instru    | uction            |                                  |                  |  |  |

| PD =              | ?                                    |                              |             | REG              | = 3               |                                  |                  |  |  |

| After Instruc     | 1 †                                  |                              |             | WREG<br>C        | = 2<br>= 1        |                                  |                  |  |  |

| $\frac{10}{PD} =$ | 0                                    |                              |             | After Instruc    |                   |                                  |                  |  |  |

| If WDT cause      | es wake-up, tl                       | his bit is clea              | red.        | REG              | = FF              |                                  |                  |  |  |

|                   |                                      |                              |             | WREG             | = 2               |                                  |                  |  |  |

|                   |                                      |                              |             | C<br>Z           | = 0<br>= 0        |                                  |                  |  |  |

|                   |                                      |                              |             | Ν                | = 1               | ; result :                       | is negativ       |  |  |

|                   |                                      |                              |             | Example 2:       | SUBFWB            | REG, 0,                          | 0                |  |  |

|                   |                                      |                              |             | Before Instru    | uction            |                                  |                  |  |  |

|                   |                                      |                              |             | REG              | = 2               |                                  |                  |  |  |

|                   |                                      |                              |             | WREG<br>C        | = 5<br>= 1        |                                  |                  |  |  |

|                   |                                      |                              |             | After Instruc    | tion              |                                  |                  |  |  |

|                   |                                      |                              |             | REG              | = 2               |                                  |                  |  |  |

|                   |                                      |                              |             | WREG<br>C        | = 3<br>= 1        |                                  |                  |  |  |

|                   |                                      |                              |             | Z                | = 1<br>= 0        |                                  |                  |  |  |

|                   |                                      |                              |             | Ν                | = 0               | ; result :                       | is positiv       |  |  |

|                   |                                      |                              |             | Example 3:       | SUBFWB            | REG, 1,                          | 0                |  |  |

|                   |                                      |                              |             | Before Instru    |                   |                                  |                  |  |  |

|                   |                                      |                              |             | REG              | = 1               |                                  |                  |  |  |

|                   |                                      |                              |             | WREG<br>C        | = 2<br>= 0        |                                  |                  |  |  |

|                   |                                      |                              |             | After Instruc    | tion              |                                  |                  |  |  |

|                   |                                      |                              |             | REG              | = 0               |                                  |                  |  |  |

|                   |                                      |                              |             |                  |                   |                                  |                  |  |  |

|                   |                                      |                              |             | WREG             | = 2               |                                  |                  |  |  |

|                   |                                      |                              |             | WREG<br>C<br>Z   | = 2<br>= 1<br>= 1 | ; result :                       | is zero          |  |  |

## 20.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD for PIC16F87X

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

### 20.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the costeffective simulator to a full-featured emulator with minimal retraining.

## 20.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

### 20.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

### 20.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC16F87X and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. The MPLAB ICD utilizes the in-circuit debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

### 20.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

### 20.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

### 20.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

### 20.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

### 21.1 DC Characteristics

| PIC18LCXX2<br>(Industrial)          |        |                                                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial                                                      |     |      |       |                                           |  |  |

|-------------------------------------|--------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|-------------------------------------------|--|--|

| PIC18CXX2<br>(Industrial, Extended) |        |                                                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |     |      |       |                                           |  |  |

| Param<br>No.                        | Symbol | Characteristic                                                      | Min                                                                                                                                                                                     | Тур | Max  | Units | Conditions                                |  |  |

|                                     | Vdd    | Supply Voltage                                                      |                                                                                                                                                                                         |     |      |       |                                           |  |  |

| D001                                |        | PIC18LCXX2                                                          | 2.5                                                                                                                                                                                     | _   | 5.5  | V     | HS, XT, RC and LP osc mode                |  |  |

| D001                                |        | PIC18CXX2                                                           | 4.2                                                                                                                                                                                     |     | 5.5  | V     |                                           |  |  |

| D002                                | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                        | 1.5                                                                                                                                                                                     | -   | -    | V     |                                           |  |  |

| D003                                | VPOR   | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    |                                                                                                                                                                                         | _   | 0.7  | V     | See section on Power-on Reset for details |  |  |

| D004                                | Svdd   | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.05                                                                                                                                                                                    | —   |      | V/ms  | See section on Power-on Reset for details |  |  |

|                                     | VBOR   | Brown-out Reset Voltag                                              | ge                                                                                                                                                                                      |     |      |       |                                           |  |  |

| D005                                |        | PIC18LCXX2                                                          |                                                                                                                                                                                         |     |      |       |                                           |  |  |

|                                     |        | BORV1:BORV0 = 11                                                    | 2.5                                                                                                                                                                                     | _   | 2.66 | V     |                                           |  |  |

|                                     |        | BORV1:BORV0 = 10                                                    | 2.7                                                                                                                                                                                     |     | 2.86 | V     |                                           |  |  |

|                                     |        | BORV1:BORV0 = 01                                                    | 4.2                                                                                                                                                                                     | —   | 4.46 | V     |                                           |  |  |

|                                     |        | BORV1:BORV0 = 00                                                    | 4.5                                                                                                                                                                                     | —   | 4.78 | V     |                                           |  |  |

| D005                                |        | PIC18CXX2                                                           |                                                                                                                                                                                         |     |      |       |                                           |  |  |

|                                     |        | BORV1:BORV0 = 1x                                                    | N.A.                                                                                                                                                                                    | —   | N.A. | V     | Not in operating voltage range of device  |  |  |

|                                     |        | BORV1:BORV0 = 01                                                    | 4.2                                                                                                                                                                                     | —   | 4.46 | V     |                                           |  |  |

|                                     |        | BORV1:BORV0 = 00                                                    | 4.5                                                                                                                                                                                     | —   | 4.78 | V     |                                           |  |  |

Legend: Shading of rows is to assist in readability of the table.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode, or during a device RESET, without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss, and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR,...).

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

### 21.1 DC Characteristics (Continued)

| PIC18LCXX2<br>(Industrial)          |        | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |                                                                                                                                                                                             |                 |                |                                                                                                                                                 |  |  |

|-------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIC18CXX2<br>(Industrial, Extended) |        |                                                                                                                                    |     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for extended |                 |                |                                                                                                                                                 |  |  |

| Param<br>No.                        | Symbol | Characteristic                                                                                                                     | Min | Тур                                                                                                                                                                                         | Max             | Units          | Conditions                                                                                                                                      |  |  |

|                                     | Idd    | Supply Current <sup>(2,4)</sup>                                                                                                    |     |                                                                                                                                                                                             |                 |                |                                                                                                                                                 |  |  |

| D010                                |        | PIC18LCXX2                                                                                                                         |     | —                                                                                                                                                                                           | 2               | mA             | XT, RC, RCIO osc configurations<br>Fosc = 4 MHz, VDD = 2.5V                                                                                     |  |  |

| D010                                |        | PIC18CXX2                                                                                                                          | —   | —                                                                                                                                                                                           | 4               | mA             | XT, RC, RCIO osc configurations<br>Fosc = 4 MHz, VDD = $4.2V$                                                                                   |  |  |

| D010A                               |        | PIC18LCXX2                                                                                                                         | —   | —                                                                                                                                                                                           | 55              | μA             | LP osc configuration<br>Fosc = 32 kHz, VDD = $2.5V$                                                                                             |  |  |

| D010A                               |        | PIC18CXX2                                                                                                                          |     | _                                                                                                                                                                                           | 250             | μA             | LP osc configuration<br>Fosc = 32 kHz, VDD = 4.2V                                                                                               |  |  |

| D010C                               |        | PIC18LCXX2                                                                                                                         | —   | —                                                                                                                                                                                           | 38              | mA             | EC, ECIO osc configurations<br>Fosc = 40 MHz, VDD = 5.5V                                                                                        |  |  |

| D010C                               |        | PIC18CXX2                                                                                                                          | —   | —                                                                                                                                                                                           | 38              | mA             | EC, ECIO osc configurations<br>Fosc = 40 MHz, VDD = 5.5V                                                                                        |  |  |

| D013                                |        | PIC18LCXX2                                                                                                                         |     |                                                                                                                                                                                             | 3.5<br>25<br>38 | mA<br>mA<br>mA | HS osc configuration<br>Fosc = 6 MHz, VDD = $2.5V$<br>Fosc = 25 MHz, VDD = $5.5V$<br>HS + PLL osc configurations<br>Fosc = 10 MHz, VDD = $5.5V$ |  |  |

| D013                                |        | PIC18CXX2                                                                                                                          | _   | _                                                                                                                                                                                           | 25<br>38        | mA<br>mA       | HS osc configuration<br>Fosc = 25 MHz, $VDD = 5.5V$<br>HS + PLL osc configurations<br>Fosc = 10 MHz, $VDD = 5.5V$                               |  |  |

| D014                                |        | PIC18LCXX2                                                                                                                         | _   | _                                                                                                                                                                                           | 55              | μA             | Timer1 osc configuration<br>Fosc = $32 \text{ kHz}$ , VDD = $2.5 \text{V}$                                                                      |  |  |

| D014                                |        | PIC18CXX2                                                                                                                          | _   |                                                                                                                                                                                             | 200<br>250      | μA<br>μA       | OSCB osc configuration<br>Fosc = 32 kHz, VDD = 4.2V, -40°C to +85°C<br>Fosc = 32 kHz, VDD = 4.2V, -40°C to +125°C                               |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** This is the limit to which VDD can be lowered in SLEEP mode, or during a device RESET, without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS, and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR,...).

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

| TABLE 21-5: | PLL CLOCK TIMING SPECIFICATION ( | VDD = 4.2V - 5.5V) |

|-------------|----------------------------------|--------------------|

|             |                                  |                    |

| Param<br>No. | Symbol       | Characteristic                      | Min | Мах | Units | Conditions |

|--------------|--------------|-------------------------------------|-----|-----|-------|------------|

|              | TRC          | PLL Start-up Time (Lock Time)       |     | 2   | ms    |            |

|              | $\Delta CLK$ | CLKOUT Stability (Jitter) using PLL | -2  | +2  | %     |            |

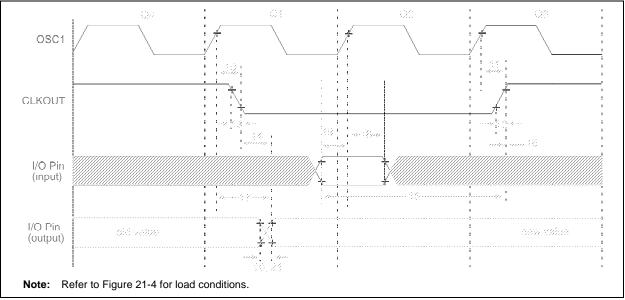

### FIGURE 21-6: CLKOUT AND I/O TIMING

### TABLE 21-6: CLKOUT AND I/O TIMING REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                                  |                 | Min          | Тур | Мах         | Units | Conditions |

|---------------|----------|-------------------------------------------------|-----------------|--------------|-----|-------------|-------|------------|

| 10            | TosH2ckL | OSC1↑ to CLKOUT↓                                |                 |              | 75  | 200         | ns    | (1)        |

| 11            | TosH2ckH | OSC1↑ to CLKOUT↑                                |                 | —            | 75  | 200         | ns    | (1)        |

| 12            | TckR     | CLKOUT rise time                                |                 | _            | 35  | 100         | ns    | (1)        |

| 13            | TckF     | CLKOUT fall time                                |                 | _            | 35  | 100         | ns    | (1)        |

| 14            | TckL2ioV | CLKOUT ↓ to Port out v                          | alid            | _            | _   | 0.5TCY + 20 | ns    | (1)        |

| 15            | TioV2ckH | Port in valid before CLK                        | OUT ↑           | 0.25Tcy + 25 | _   |             | ns    | (1)        |

| 16            | TckH2iol | Port in hold after CLKO                         | JT ↑            | 0            |     |             | ns    | (1)        |

| 17            | TosH2ioV | OSC1↑ (Q1 cycle) to Po                          | ort out valid   | _            | 50  | 150         | ns    |            |

| 18            | TosH2iol | OSC1↑ (Q2 cycle) to                             | PIC18CXXX       | 100          | _   |             | ns    |            |

| 18A           |          | Port input invalid<br>(I/O in hold time)        | PIC18LCXXX      | 200          | —   |             | ns    |            |

| 19            | TioV2osH | Port input valid to OSC1<br>(I/O in setup time) | 1               | 0            | —   | —           | ns    |            |

| 20            | TioR     | Port output rise time                           | PIC18CXXX       |              | 12  | 25          | ns    |            |

| 20A           |          |                                                 | PIC18LCXXX      |              | _   | 50          | ns    |            |

| 21            | TioF     | Port output fall time                           | PIC18CXXX       |              | 12  | 25          | ns    |            |

| 21A           |          |                                                 | PIC18LCXXX      | _            | _   | 50          | ns    |            |

| 22††          | TINP     | INT pin high or low time                        |                 | Тсү          | _   |             | ns    |            |

| 23††          | Trbp     | RB7:RB4 change INT high or low time             |                 | Тсү          | _   |             | ns    |            |

| 24††          | TRCP     | RC7:RC4 change INT h                            | igh or low time | 20           |     |             | ns    |            |

these parameters are asynchronous events not related to any internal clock edges.

**Note 1:** Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

### TABLE 21-22: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Symbol | Characte                                    | Characteristic              |          | Max               | Units    | Conditions                                                                                                                                                             |

|--------------|--------|---------------------------------------------|-----------------------------|----------|-------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD    | A/D clock period                            | PIC18CXXX                   | 1.6      | 20 <sup>(5)</sup> | μS       | Tosc based, VREF $\geq 3.0V$                                                                                                                                           |