Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                              |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c442-i-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

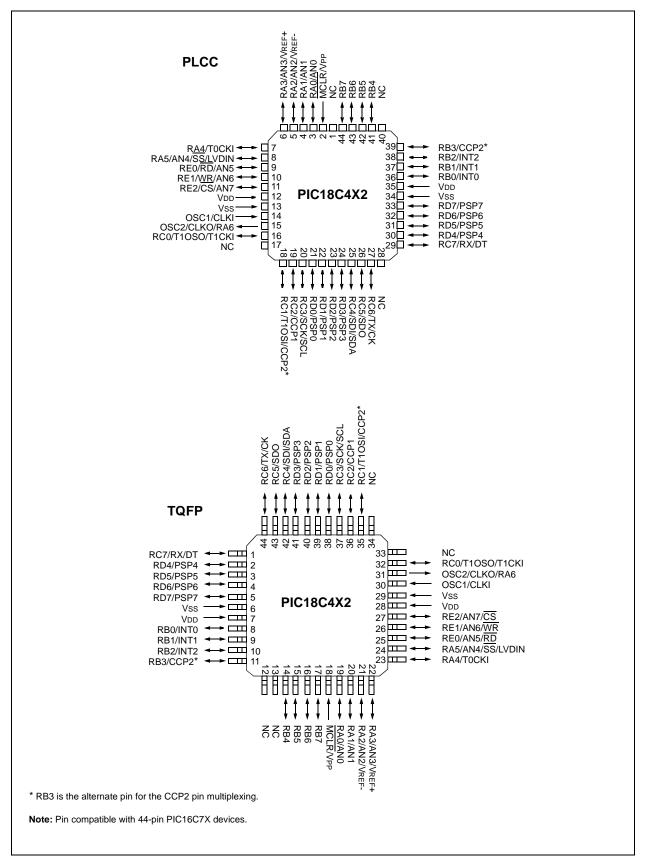

### **Pin Diagrams**

#### **TABLE 1-2:** PIC18C2X2 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                                                                  | Pin Number |       | Pin Buffer |          | Description                                                      |  |  |

|---------------------------------------------------------------------------|------------|-------|------------|----------|------------------------------------------------------------------|--|--|

| Pin Name                                                                  | DIP        | SOIC  | Туре       | Туре     | Description                                                      |  |  |

|                                                                           |            |       |            |          | PORTC is a bi-directional I/O port.                              |  |  |

| RC0/T1OSO/T1CKI                                                           | 11         | 11    |            |          |                                                                  |  |  |

| RC0                                                                       |            |       | I/O        | ST       | Digital I/O.                                                     |  |  |

| T1OSO                                                                     |            |       | 0          |          | Timer1 oscillator output.                                        |  |  |

| T1CKI                                                                     |            |       | I          | ST       | Timer1/Timer3 external clock input.                              |  |  |

| RC1/T1OSI/CCP2                                                            | 12         | 12    |            |          |                                                                  |  |  |

| RC1                                                                       |            |       | I/O        | ST       | Digital I/O.                                                     |  |  |

| T1OSI                                                                     |            |       | I          | CMOS     | Timer1 oscillator input.                                         |  |  |

| CCP2                                                                      |            |       | I/O        | ST       | Capture2 input, Compare2 output, PWM2 output.                    |  |  |

| RC2/CCP1                                                                  | 13         | 13    |            |          |                                                                  |  |  |

| RC2                                                                       |            |       | I/O        | ST       | Digital I/O.                                                     |  |  |

| CCP1                                                                      |            |       | I/O        | ST       | Capture1 input/Compare1 output/PWM1 output.                      |  |  |

| RC3/SCK/SCL                                                               | 14         | 14    |            |          |                                                                  |  |  |

| RC3                                                                       |            |       | I/O        | ST       | Digital I/O.                                                     |  |  |

| SCK                                                                       |            |       | I/O        | ST       | Synchronous serial clock input/output for SPI mode.              |  |  |

| SCL                                                                       |            |       | I/O        | ST       | Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |  |

| RC4/SDI/SDA                                                               | 15         | 15    |            |          |                                                                  |  |  |

| RC4                                                                       |            |       | I/O        | ST       | Digital I/O.                                                     |  |  |

| SDI                                                                       |            |       | Ι          | ST       | SPI Data In.                                                     |  |  |

| SDA                                                                       |            |       | I/O        | ST       | I <sup>2</sup> C Data I/O.                                       |  |  |

| RC5/SDO                                                                   | 16         | 16    |            |          |                                                                  |  |  |

| RC5                                                                       |            |       | I/O        | ST       | Digital I/O.                                                     |  |  |

| SDO                                                                       |            |       | 0          | —        | SPI Data Out.                                                    |  |  |

| RC6/TX/CK                                                                 | 17         | 17    |            |          |                                                                  |  |  |

| RC6                                                                       |            |       | I/O        | ST       | Digital I/O.                                                     |  |  |

| TX                                                                        |            |       | 0          |          | USART Asynchronous Transmit.                                     |  |  |

| СК                                                                        |            |       | I/O        | ST       | USART Synchronous Clock (see related RX/DT).                     |  |  |

| RC7/RX/DT                                                                 | 18         | 18    |            | <u> </u> |                                                                  |  |  |

| RC7                                                                       |            |       | I/O        | ST       | Digital I/O.                                                     |  |  |

| RX                                                                        |            |       |            | ST       | USART Asynchronous Receive.                                      |  |  |

| DT                                                                        |            |       | I/O        | ST       | USART Synchronous Data (see related TX/CK).                      |  |  |

| Vss                                                                       | 8, 19      | 8, 19 | Р          |          | Ground reference for logic and I/O pins.                         |  |  |

| Vdd                                                                       | 20         | 20    | Р          | _        | Positive supply for logic and I/O pins.                          |  |  |

| Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output |            |       |            |          |                                                                  |  |  |

TTL = TTL compatible input CMOS = ST = Schmitt Trigger input with CMOS levels I = Input egend:

CMOS compatible input or output

P = Power

O = Output OD = Open Drain (no P diode to VDD)

### 2.7 Effects of SLEEP Mode on the On-chip Oscillator

When the device executes a SLEEP instruction, the on-chip clocks and oscillator are turned off and the device is held at the beginning of an instruction cycle (Q1 state). With the oscillator off, the OSC1 and OSC2 signals will stop oscillating. Since all the transistor

switching currents have been removed, SLEEP mode achieves the lowest current consumption of the device (only leakage currents). Enabling any on-chip feature that will operate during SLEEP will increase the current consumed during SLEEP. The user can wake from SLEEP through external RESET, Watchdog Timer Reset, or through an interrupt.

### TABLE 2-3:OSC1 AND OSC2 PIN STATES IN SLEEP MODE

| OSC Mode       | OSC1 Pin                                                  | OSC2 Pin                                                  |

|----------------|-----------------------------------------------------------|-----------------------------------------------------------|

| RC             | Floating, external resistor should pull high              | At logic low                                              |

| RCIO           | Floating, external resistor should pull high              | Configured as PORTA, bit 6                                |

| ECIO           | Floating                                                  | Configured as PORTA, bit 6                                |

| EC             | Floating                                                  | At logic low                                              |

| LP, XT, and HS | Feedback inverter disabled, at<br>quiescent voltage level | Feedback inverter disabled, at<br>quiescent voltage level |

**Note:** See Table 3-1, in Section 3.0 RESET, for time-outs due to SLEEP and MCLR Reset.

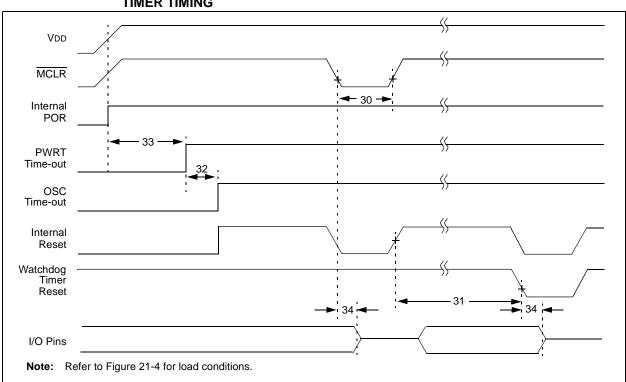

### 2.8 Power-up Delays

Power up delays are controlled by two timers, so that no external RESET circuitry is required for most applications. The delays ensure that the device is kept in RESET until the device power supply and clock are stable. For additional information on RESET operation, see the "RESET" section.

The first timer is the Power-up Timer (PWRT), which optionally provides a fixed delay of 72 ms (nominal) on power-up only (POR and BOR). The second timer is the Oscillator Start-up Timer, OST, intended to keep the chip in RESET until the crystal oscillator is stable.

With the PLL enabled (HS/PLL oscillator mode), the time-out sequence following a Power-on Reset is different from other oscillator modes. The time-out sequence is as follows: First, the PWRT time-out is invoked after a POR time delay has expired. Then, the Oscillator Start-up Timer (OST) is invoked. However, this is still not a sufficient amount of time to allow the PLL to lock at high frequencies. The PWRT timer is used to provide an additional fixed 2ms (nominal) time-out to allow the PLL ample time to lock to the incoming clock frequency.

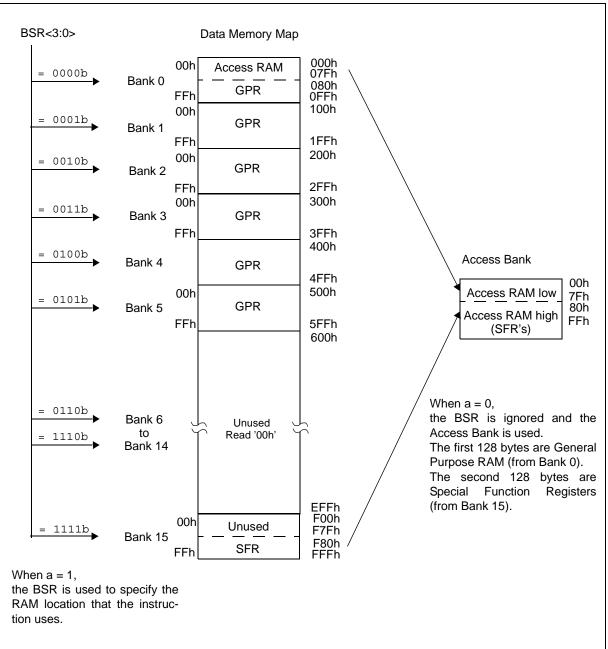

#### FIGURE 4-7: DATA MEMORY MAP FOR PIC18C252/452

### 7.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable Registers (PIE1, PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

### REGISTER 7-6: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (PIE1)

|       | R/W-0                                                                                                                 | R/W-0                       | R/W-0         | R/W-0         | R/W-0          | R/W-0      | R/W-0         | R/W-0      |  |

|-------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------|---------------|----------------|------------|---------------|------------|--|

|       | PSPIE                                                                                                                 | ADIE                        | RCIE          | TXIE          | SSPIE          | CCP1IE     | TMR2IE        | TMR1IE     |  |

|       | bit 7                                                                                                                 |                             |               |               |                |            |               | bit 0      |  |

|       |                                                                                                                       |                             |               |               |                |            |               |            |  |

| bit 7 | PSPIE: Parallel Slave Port Read/Write Interrupt Enable bit                                                            |                             |               |               |                |            |               |            |  |

|       |                                                                                                                       | s the PSP re<br>s the PSP r |               |               |                |            |               |            |  |

| bit 6 |                                                                                                                       | Converter Ir                |               |               |                |            |               |            |  |

|       |                                                                                                                       | s the A/D in                | •             |               |                |            |               |            |  |

|       | 0 = Disable                                                                                                           | es the A/D ir               | nterrupt      |               |                |            |               |            |  |

| bit 5 | RCIE: USA                                                                                                             | RT Receive                  | e Interrupt E | nable bit     |                |            |               |            |  |

|       |                                                                                                                       | s the USAR                  |               |               |                |            |               |            |  |

| h:+ 4 |                                                                                                                       | es the USAF                 |               | •             |                |            |               |            |  |

| bit 4 |                                                                                                                       | RT Transmi<br>s the USAR    |               |               |                |            |               |            |  |

|       |                                                                                                                       | s the USAR                  |               |               |                |            |               |            |  |

| bit 3 | SSPIE: Ma                                                                                                             | ster Synchr                 | onous Seria   | l Port Interr | upt Enable bit |            |               |            |  |

|       |                                                                                                                       | s the MSSP                  |               |               |                |            |               |            |  |

|       |                                                                                                                       | es the MSSF                 |               |               |                |            |               |            |  |

| bit 2 |                                                                                                                       | CP1 Interru                 |               | it            |                |            |               |            |  |

|       |                                                                                                                       | s the CCP1<br>is the CCP1   | -             |               |                |            |               |            |  |

| bit 1 |                                                                                                                       | MR2 to PR2                  | •             | rrunt Enable  | - hit          |            |               |            |  |

| bit i |                                                                                                                       |                             |               | •             |                |            |               |            |  |

|       | <ul> <li>1 = Enables the TMR2 to PR2 match interrupt</li> <li>0 = Disables the TMR2 to PR2 match interrupt</li> </ul> |                             |               |               |                |            |               |            |  |

| bit 0 | TMR1IE: T                                                                                                             | MR1 Overflo                 | ow Interrupt  | Enable bit    |                |            |               |            |  |

|       | 1 = Enables the TMR1 overflow interrupt                                                                               |                             |               |               |                |            |               |            |  |

|       | 0 = Disable                                                                                                           | es the TMR1                 | overflow in   | iterrupt      |                |            |               |            |  |

|       | Legend:                                                                                                               |                             |               |               |                |            |               | ]          |  |

|       | R = Reada                                                                                                             | hla hit                     | \\/ \\        | /ritable bit  | U = Unimple    | omontad hi | it read as "  | <b>ר</b> י |  |

|       | - n = Value                                                                                                           |                             |               | Bit is set    | 0 = 0 minipi   |            | x = Bit is ur |            |  |

|       | - n = value                                                                                                           | al FUR                      | I = D         | IL IS SEL     | U = DILISC     | lealeu     | x = Dit is uf | INTOWN     |  |

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                          |

|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in Parallel Slave Port mode<br>or analog input:<br>RD                                                                                                 |

|            |      |                       | <ul><li>1 = Not a read operation</li><li>0 = Read operation. Reads PORTD register (if chip selected).</li></ul>                                                                                   |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in Parallel Slave Port mode<br>or analog input:<br>WR<br>1 = Not a write operation<br>0 = Write operation. Writes PORTD register (if chip selected). |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in Parallel Slave Port<br>mode or analog input:<br>$\overline{CS}$<br>1 = Device is not selected<br>0 = Device is selected                     |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 8-10: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTE |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2                     | Bit 1      | Bit 0  | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|-------|-------|-------|---------|-------|---------------------------|------------|--------|-------------------------|---------------------------------|

| PORTE  | _     | —     | _     | _       | _     | RE2                       | RE1        | RE0    | 000                     | 000                             |

| LATE   | _     | —     |       | —       | _     | LATE Data                 | Output Reg | lister | xxx                     | uuu                             |

| TRISE  | IBF   | OBF   | IBOV  | PSPMODE | —     | PORTE Data Direction bits |            |        | 0000 -111               | 0000 -111                       |

| ADCON1 | ADFM  | ADCS2 | —     | _       | PCFG3 | PCFG2                     | PCFG1      | PCFG0  | 0000                    | 0000                            |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

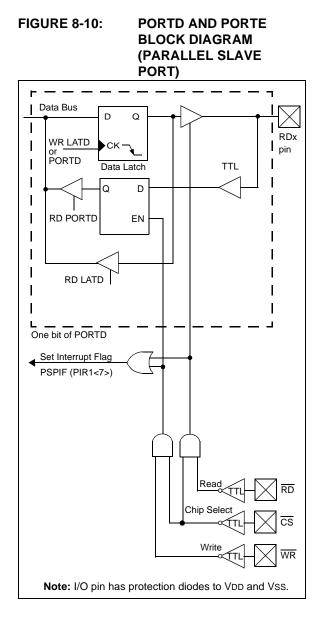

### 8.6 Parallel Slave Port

The Parallel Slave Port is implemented on the 40-pin devices only (PIC18C4X2).

PORTD operates as an 8-bit wide, parallel slave port, or microprocessor port, when control bit PSPMODE (TRISE<4>) is set. It is asynchronously readable and writable by the external world through RD control input pin RE0/RD and WR control input pin RE1/WR.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, <u>RE1/WR</u> to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

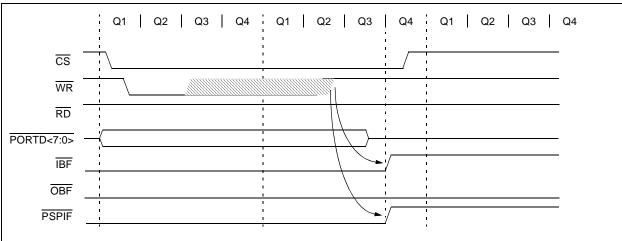

A write to the PSP occurs when both the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  lines are first detected low.

The PORTE I/O pins become control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs), and the ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

### FIGURE 8-11: PARALLEL SLAVE PORT WRITE WAVEFORMS

### 14.3.3 TYPICAL CONNECTION

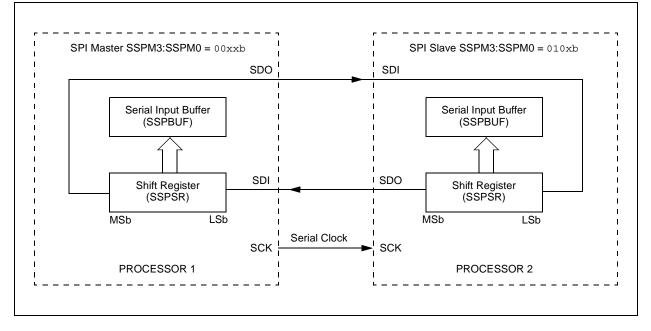

Figure 14-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (CKP), then both con-

trollers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

### FIGURE 14-2: SPI MASTER/SLAVE CONNECTION

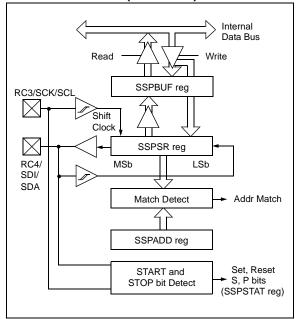

### 14.4 MSSP I<sup>2</sup>C Operation

The MSSP module in I<sup>2</sup>C mode, fully implements all master and slave functions (including general call support) and provides interrupts on START and STOP bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/ SCK/SCL pin, which is the clock (SCL), and the RC4/ SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The MSSP module functions are enabled by setting MSSP enable bit SSPEN (SSPCON<5>).

The MSSP module has six registers for  $I^2C$  operation. These are the:

- MSSP Control Register1 (SSPCON1)

- MSSP Control Register2 (SSPCON2)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address Register (SSPADD)

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with START and STOP bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with START and STOP bit interrupts enabled

- I<sup>2</sup>C Firmware controlled master operation, slave is idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to be inputs by setting the appropriate TRISC bits.

### 14.4.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the MSSP module not to give this ACK pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

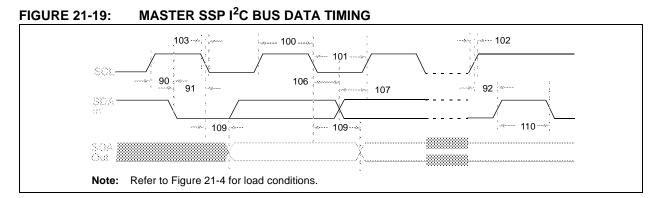

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter #100 and parameter #101.

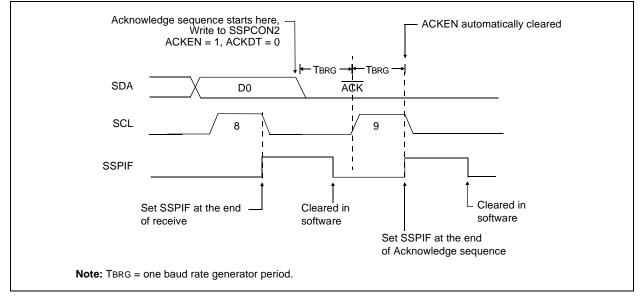

### 14.4.10 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit is presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The baud rate generator then counts for one rollover period (TBRG) and the SCL pin is de-asserted (pulled high). When the SCL pin is sampled high (clock arbitration), the baud rate generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off and the MSSP module then goes into IDLE mode (Figure 14-20).

### 14.4.10.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

### 14.4.11 STOP CONDITION TIMING

A STOP bit is asserted on the SDA pin at the end of a receive/transmit by setting the STOP sequence enable bit, PEN (SSPCON2<2>). At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the baud rate generator is reloaded and counts down to 0. When the baud rate generator times out, the SCL pin will be brought high, and one TBRG (baud rate generator rollover count) later, the SDA pin will be de-asserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 14-21).

### 14.4.11.1 WCOL Status Flag

If the user writes the SSPBUF when a STOP sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

### FIGURE 14-20: ACKNOWLEDGE SEQUENCE WAVEFORM

NOTES:

| ANDWF             | AND WRE                                                                    | EG with f                                                                                                                    |                                                                            | BC              | Branch if                                                        | Carry                                                       |                                                                                           |  |

|-------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------|------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| Syntax:           | [ <i>label</i> ] A                                                         | NDWF f[                                                                                                                      | ,d [,a]                                                                    | Syntax:         | [ <i>label</i> ] B                                               | [ <i>label</i> ]BC n                                        |                                                                                           |  |

| Operands:         | $0 \leq f \leq 255$                                                        |                                                                                                                              |                                                                            | Operands:       | -128 ≤ n ≤                                                       | $-128 \le n \le 127$                                        |                                                                                           |  |

|                   | $\begin{array}{l} d \in [0,1] \\ a \in [0,1] \end{array}$                  |                                                                                                                              |                                                                            | Operation:      | Operation: if carry bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC |                                                             | ;                                                                                         |  |

| Operation:        | (WREG) .                                                                   | AND. (f) $\rightarrow$ d                                                                                                     | est                                                                        | Status Affected | I: None                                                          |                                                             |                                                                                           |  |

| Status Affected:  | N,Z                                                                        |                                                                                                                              |                                                                            | Encoding:       | 1110                                                             | 0010 nn                                                     | nn nnnn                                                                                   |  |

| Encoding:         | 0001                                                                       | 01da ffi                                                                                                                     | ff ffff                                                                    | Description:    | If the Carr                                                      | y bit is '1', th                                            | nen the pro-                                                                              |  |

| Description:      | with regist<br>is stored in<br>result is st<br>(default). I<br>Bank will b | nts of WREG<br>ter 'f'. If 'd' is<br>in WREG. If 'd<br>tored back in<br>of 'a' is 0, the<br>be selected. I<br>not be overrid | 0, the result<br>d' is 1, the<br>register 'f'<br>Access<br>f 'a' is 1, the | Words:          | added to t<br>have incre<br>instructior<br>PC+2+2n               | omplement n<br>he PC. Sind<br>emented to f<br>n, the new ac | umber '2n' is<br>ce the PC will<br>etch the next<br>ddress will be<br>ction is then<br>n. |  |

| Words:            | 1                                                                          |                                                                                                                              |                                                                            | Cycles:         | 1(2)                                                             |                                                             |                                                                                           |  |

| Cycles:           | 1                                                                          |                                                                                                                              |                                                                            | Q Cycle Activi  |                                                                  |                                                             |                                                                                           |  |

| Q Cycle Activity: |                                                                            |                                                                                                                              |                                                                            | If Jump:        |                                                                  |                                                             |                                                                                           |  |

| Q1                | Q2                                                                         | Q3                                                                                                                           | Q4                                                                         | Q1              | Q2                                                               | Q3                                                          | Q4                                                                                        |  |

| Decode            | Read<br>register 'f'                                                       | Process<br>Data                                                                                                              | Write to<br>destination                                                    | Decode          | Read literal<br>'n'                                              | Process<br>Data                                             | Write to PC                                                                               |  |

| Example:          | ANDWF                                                                      | REG, 0, 0                                                                                                                    |                                                                            | No<br>operation | No<br>operation                                                  | No<br>operation                                             | No<br>operation                                                                           |  |

| Before Instru     |                                                                            |                                                                                                                              |                                                                            | If No Jump:     |                                                                  |                                                             |                                                                                           |  |

| WREG              | $= 0 \times 17$                                                            |                                                                                                                              |                                                                            | Q1              | Q2                                                               | Q3                                                          | Q4                                                                                        |  |

| REG               | = 0x17<br>= 0xC2                                                           |                                                                                                                              |                                                                            | Decode          | Read literal<br>'n'                                              | Process                                                     | No                                                                                        |  |

| After Instruct    | ion                                                                        |                                                                                                                              |                                                                            |                 | П                                                                | Data                                                        | operation                                                                                 |  |

| WREG<br>REG       | = 0x02<br>= 0xC2                                                           |                                                                                                                              |                                                                            | Example:        | HERE                                                             | BC 5                                                        |                                                                                           |  |

|                   |                                                                            |                                                                                                                              |                                                                            | Before Ins      |                                                                  | ldress (HER                                                 | )<br>()                                                                                   |  |

|                   |                                                                            |                                                                                                                              |                                                                            | PC              | = au                                                             | luiess (HER                                                 | LE)                                                                                       |  |

If Carry PC If Carry PC

= = = l; address (HERE+12) 0; address (HERE+2)

| MOVFF                                                | Move f to                                                                                                                                                                                                                                                              | o f          |              |                                        |  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|----------------------------------------|--|

| Syntax:                                              | [label]                                                                                                                                                                                                                                                                | MOVFF        | $f_s, f_d$   |                                        |  |

| Operands:                                            | $\begin{array}{l} 0 \leq f_s \leq 4 \\ 0 \leq f_d \leq 4 \end{array}$                                                                                                                                                                                                  |              |              |                                        |  |

| Operation:                                           | $(f_{S}) \to f_{d}$                                                                                                                                                                                                                                                    |              |              |                                        |  |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                   |              |              |                                        |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.) | 1100<br>1111                                                                                                                                                                                                                                                           | ffff<br>ffff | ffff<br>ffff | ffff <sub>s</sub><br>ffff <sub>d</sub> |  |

| Description:                                         | The contents of source register 'f <sub>s</sub> ' are moved to destination register 'f <sub>d</sub> '. Location of source 'f <sub>s</sub> ' can be anywhere in the 4096 byte data space (000h to FFFh), and location of destination 'f <sub>d</sub> ' can also be any- |              |              |                                        |  |

where from 000h to FFFh. Either source or destination can be WREG (a useful special situation). MOVFF is particularly useful for transferring a data memory location to a peripheral register (such as the transmit buffer or an I/O port).

The MOVFF instruction cannot use the PCL, TOSU, TOSH or TOSL as the destination register.

Words:

Cycles:

Q Cycle Activity:

Q1

| Q1     | Q2                                  | Q3              | Q4                              |

|--------|-------------------------------------|-----------------|---------------------------------|

| Decode | Read<br>register 'f'<br>(src)       | Process<br>Data | No<br>operation                 |

| Decode | No<br>operation<br>No dummy<br>read | No<br>operation | Write<br>register 'f'<br>(dest) |

#### Example:

MOVFF REG1, REG2

#### **Before Instruction**

| REG1<br>REG2      | =<br>= | 0x33<br>0x11 |

|-------------------|--------|--------------|

| After Instruction |        |              |

| REG1              | =      | 0x33,        |

| REG2              | =      | 0x33         |

2

2 (3)

| MO\         | /LB              | Move lite           | Move literal to low nibble in BSR                                    |      |                             |  |  |  |  |

|-------------|------------------|---------------------|----------------------------------------------------------------------|------|-----------------------------|--|--|--|--|

| Synt        | ax:              | [ label ]           | [ <i>label</i> ] MOVLB k                                             |      |                             |  |  |  |  |

| Ope         | rands:           | $0 \le k \le 25$    | $0 \le k \le 255$                                                    |      |                             |  |  |  |  |

| Ope         | ration:          | $k \to BSR$         | $k \rightarrow BSR$                                                  |      |                             |  |  |  |  |

| Statu       | us Affected:     | None                |                                                                      |      |                             |  |  |  |  |

| Enco        | oding:           | 0000                | 0001                                                                 | kkkk | kkkk                        |  |  |  |  |

| Desc        | cription:        |                     | The 8-bit literal 'k' is loaded into the Bank Select Register (BSR). |      |                             |  |  |  |  |

| Wor         | ds:              | 1                   |                                                                      |      |                             |  |  |  |  |

| Cycl        | es:              | 1                   |                                                                      |      |                             |  |  |  |  |

| QC          | ycle Activity    |                     |                                                                      |      |                             |  |  |  |  |

|             | Q1               | Q2                  | Q3                                                                   |      | Q4                          |  |  |  |  |

|             | Decode           | Read literal<br>'k' | Proce<br>Data                                                        |      | Write<br>eral 'k' to<br>BSR |  |  |  |  |

| <u>Exar</u> | Example: MOVLB 5 |                     |                                                                      |      |                             |  |  |  |  |

| Before Instruction |   |      |

|--------------------|---|------|

| BSR register       | = | 0x02 |

| After Instruction  |   |      |

| BSR register       | = | 0x05 |

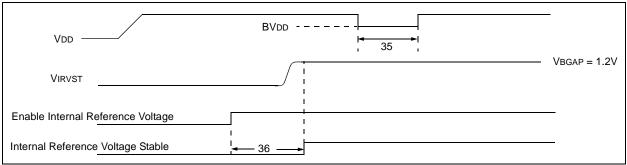

### FIGURE 21-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

### FIGURE 21-8: BROWN-OUT RESET TIMING

### TABLE 21-7:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic                                            | Min      | Тур | Мах      | Units | Conditions                |

|---------------|--------|-----------------------------------------------------------|----------|-----|----------|-------|---------------------------|

| 30            | TmcL   | MCLR Pulse Width (low)                                    | 2        |     |          | μS    |                           |

| 31            | Twdt   | Watchdog Timer Time-out Period (No Postscaler)            | 7        | 18  | 33       | ms    |                           |

| 32            | Tost   | Oscillation Start-up Timer Period                         | 1024Tosc | _   | 1024Tosc | —     | Tosc = OSC1 period        |

| 33            | TPWRT  | Power up Timer Period                                     | 28       | 72  | 132      | ms    |                           |

| 34            | Tıoz   | I/O Hi-impedance from MCLR<br>Low or Watchdog Timer Reset | _        | 2   | —        | μS    |                           |

| 35            | TBOR   | Brown-out Reset Pulse Width                               | 200      | _   | _        | μS    | $VDD \le BVDD$ (See D005) |

| 36            | Tivrst | Time for Internal Reference<br>Voltage to become stable   | —        | 20  | 50       | μS    |                           |

### TABLE 21-18: MASTER SSP I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param.<br>No. | Symbol  | Charac             | Min                       | Max              | Units | Conditions |                        |

|---------------|---------|--------------------|---------------------------|------------------|-------|------------|------------------------|

| 100           | Thigh   | Clock high time    | 100 kHz mode              | 2(Tosc)(BRG + 1) | —     | ms         |                        |

|               |         |                    | 400 kHz mode              | 2(Tosc)(BRG + 1) | _     | ms         |                        |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —     | ms         |                        |

| 101           | TLOW    | Clock low time     | 100 kHz mode              | 2(Tosc)(BRG + 1) | —     | ms         |                        |

|               |         |                    | 400 kHz mode              | 2(Tosc)(BRG + 1) | —     | ms         |                        |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _     | ms         |                        |

| 102           | Tr      | SDA and SCL        | 100 kHz mode              | —                | 1000  | ns         | CB is specified to be  |

|               |         | rise time          | 400 kHz mode              | 20 + 0.1Св       | 300   | ns         | from 10 to 400 pF      |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | _                | 300   | ns         |                        |

| 103           | TF      | SDA and SCL        | 100 kHz mode              |                  | 300   | ns         | CB is specified to be  |

|               |         | fall time          | 400 kHz mode              | 20 + 0.1Св       | 300   | ns         | from 10 to 400 pF      |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | —                | 100   | ns         |                        |

| 90            | TSU:STA | START condition    | 100 kHz mode              | 2(Tosc)(BRG + 1) |       | ms         | Only relevant for      |

|               |         | setup time         | 400 kHz mode              | 2(Tosc)(BRG + 1) | —     | ms         | Repeated START         |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _     | ms         | condition              |

| 91            | THD:STA | START condition    | 100 kHz mode              | 2(Tosc)(BRG + 1) |       | ms         | After this period the  |

|               |         | hold time          | 400 kHz mode              | 2(Tosc)(BRG + 1) |       | ms         | first clock pulse is   |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _     | ms         | generated              |

| 106           | THD:DAT | Data input         | 100 kHz mode              | 0                | —     | ns         |                        |

|               |         | hold time          | 400 kHz mode              | 0                | 0.9   | ms         |                        |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | TBD              | _     | ns         |                        |

| 107           | TSU:DAT | Data input         | 100 kHz mode              | 250              | _     | ns         | (Note 2)               |

|               |         | setup time         | 400 kHz mode              | 100              | —     | ns         |                        |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | TBD              | _     | ns         |                        |

| 92            | TSU:STO | STOP condition     | 100 kHz mode              | 2(Tosc)(BRG + 1) | —     | ms         |                        |

|               |         | setup time         | 400 kHz mode              | 2(Tosc)(BRG + 1) |       | ms         |                        |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _     | ms         |                        |

| 109           | ΤΑΑ     | Output valid from  | 100 kHz mode              | —                | 3500  | ns         |                        |

|               |         | clock              | 400 kHz mode              | —                | 1000  | ns         |                        |

|               |         |                    | 1 MHz mode <sup>(1)</sup> |                  |       | ns         |                        |

| 110           | TBUF    | Bus free time      | 100 kHz mode              | 4.7              |       | ms         | Time the bus must be   |

|               |         |                    | 400 kHz mode              | 1.3              | —     | ms         | free before a new      |

|               |         |                    | 1 MHz mode <sup>(1)</sup> | TBD              |       | ms         | transmission can start |

| D102          | Св      | Bus capacitive loa |                           | —                | 400   | pF         |                        |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

2: A fast mode I<sup>2</sup>C bus device can be used in a standard mode I<sup>2</sup>C bus system, but parameter #107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line, parameter #102 + parameter #107 = 1000 + 250 = 1250 ns (for 100 kHz mode) before the SCL line is released.

### TABLE 21-21: A/D CONVERTER CHARACTERISTICS: PIC18CXX2 (INDUSTRIAL, EXTENDED) PIC18LCXX2 (INDUSTRIAL)

| Param<br>No. | Symbol                               | Charac                                         | teristic           | Min            | Тур        | Max               | Units                                                                                                        | Conditions                                                                               |

|--------------|--------------------------------------|------------------------------------------------|--------------------|----------------|------------|-------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| A01          | NR                                   | Resolution                                     |                    | _              | _          | 10<br>10          | bit<br>bit                                                                                                   | $\label{eq:VREF} \begin{array}{l} VREF = VDD \geq 3.0V \\ VREF = VDD < 3.0V \end{array}$ |

| A03          | EIL                                  | Integral linearity                             | _                  | _              | <±1<br><±2 | LSb<br>LSb        | $\label{eq:VREF} \begin{array}{l} VREF = VDD \geq 3.0V \\ VREF = VDD < 3.0V \end{array}$                     |                                                                                          |

| A04          | Edl                                  | Differential lines                             | arity error        | _              | _          | <±1<br><±2        | LSb<br>LSb                                                                                                   | $\label{eq:VREF} \begin{array}{l} VREF = VDD \geq 3.0V \\ VREF = VDD < 3.0V \end{array}$ |

| A05          | Efs                                  | Full scale error                               |                    | _              | _          | <±1<br><±1        | LSb<br>LSb                                                                                                   | $\label{eq:VREF} \begin{array}{l} VREF = VDD \geq 3.0V \\ VREF = VDD < 3.0V \end{array}$ |

| A06          | EOFF                                 | Offset error                                   |                    | _              | _          | <±1<br><±1        | LSb<br>LSb                                                                                                   | $\label{eq:VREF} \begin{array}{l} VREF = VDD \geq 3.0V \\ VREF = VDD < 3.0V \end{array}$ |

| A10          | _                                    | Monotonicity                                   |                    | g              | uarantee   | ed <sup>(3)</sup> | —                                                                                                            | $VSS \leq VAIN \leq VREF$                                                                |

| A20          | Vref                                 | Reference voltage                              |                    | 0V             |            | —                 | V                                                                                                            |                                                                                          |

| A20A         |                                      | (VREFH - VREFL)                                |                    | 3V             |            | _                 | V                                                                                                            | For 10-bit resolution                                                                    |

| A21          | Vrefh                                | Reference voltage High                         |                    | AVss           | —          | AVDD + 0.3V       | V                                                                                                            |                                                                                          |

| A22          | Vrefl                                | Reference voltage Low                          |                    | AVss -<br>0.3V | —          | AVdd              | V                                                                                                            |                                                                                          |

| A25          | VAIN                                 | Analog input voltage                           |                    | AVss -<br>0.3V | —          | VREF + 0.3V       | V                                                                                                            |                                                                                          |

| A30          | ZAIN                                 | Recommended impedance of analog voltage source |                    | —              | —          | 10.0              | kΩ                                                                                                           |                                                                                          |

| A40          | IAD                                  | A/D conversion                                 | PIC18 <b>C</b> XXX |                | 180        | —                 | μΑ                                                                                                           | Average current                                                                          |

|              |                                      | current (VDD)                                  | PIC18LCXXX         | —              | 90         | —                 | μΑ                                                                                                           | consumption when<br>A/D is on <b>(Note 1)</b> .                                          |

| A50          | A50 IREF VREF input current (Note 2) |                                                | 10                 |                | 1000       | μΑ                | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN. To charge<br>CHOLD, see Section 16.0. |                                                                                          |

|              |                                      |                                                |                    | —              | —          | 10                | μΑ                                                                                                           | During A/D conversion cycle.                                                             |

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module. VREF current is from RA2/AN2/VREF- and RA3/AN3/VREF+ pins or AVDD and AVss pins, whichever is selected as reference input.

**2:** VSS  $\leq$  VAIN  $\leq$  VREF

**3:** The A/D conversion result never decreases with an increase in the Input Voltage, and has no missing codes.

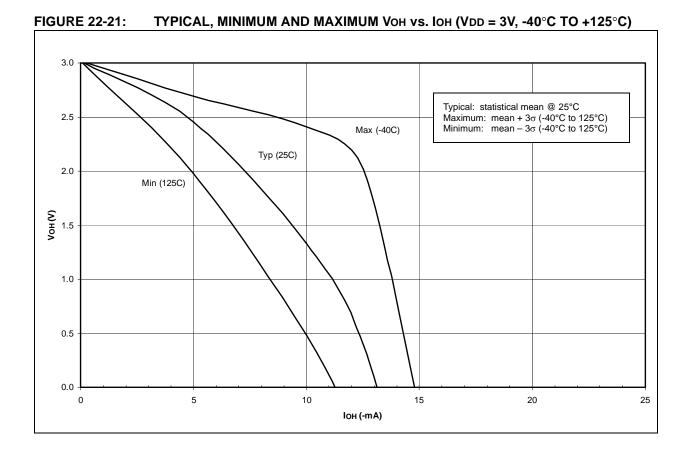

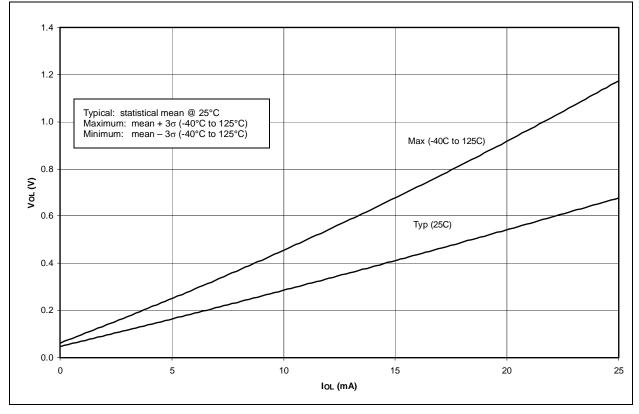

FIGURE 22-22: TYPICAL AND MAXIMUM Vol vs. lol (VDD = 5V, -40°C TO +125°C)

© 1999-2013 Microchip Technology Inc.

### Package Marking Information (Cont'd)

### 40-Lead PDIP

### Example

PIC18C452

-I/JW

0115017

### 28- and 40-Lead JW (CERDIP)

### 44-Lead TQFP

### Example

Example

$\mathbf{v}$

MICROCHIP

### 44-Lead PLCC

### Example

DS39026D-page 278

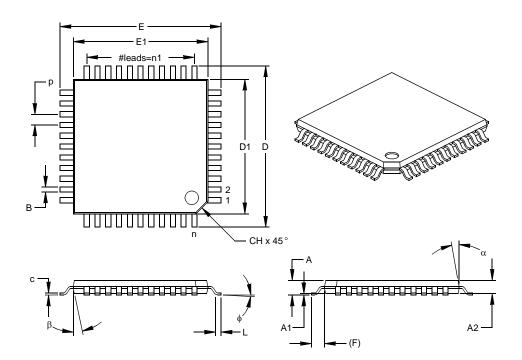

### 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | INCHES |      |      | MILLIMETERS* |       |       |  |

|--------------------------|-------|--------|------|------|--------------|-------|-------|--|

| Dimensi                  | MIN   | NOM    | MAX  | MIN  | NOM          | MAX   |       |  |

| Number of Pins           | n     |        | 44   |      |              | 44    |       |  |

| Pitch                    | р     |        | .031 |      |              | 0.80  |       |  |

| Pins per Side            | n1    |        | 11   |      |              | 11    |       |  |

| Overall Height           | Α     | .039   | .043 | .047 | 1.00         | 1.10  | 1.20  |  |

| Molded Package Thickness | A2    | .037   | .039 | .041 | 0.95         | 1.00  | 1.05  |  |

| Standoff §               | A1    | .002   | .004 | .006 | 0.05         | 0.10  | 0.15  |  |

| Foot Length              | L     | .018   | .024 | .030 | 0.45         | 0.60  | 0.75  |  |

| Footprint (Reference)    | (F)   |        | .039 |      | 1.00         |       |       |  |

| Foot Angle               | ¢     | 0      | 3.5  | 7    | 0            | 3.5   | 7     |  |

| Overall Width            | Е     | .463   | .472 | .482 | 11.75        | 12.00 | 12.25 |  |

| Overall Length           | D     | .463   | .472 | .482 | 11.75        | 12.00 | 12.25 |  |

| Molded Package Width     | E1    | .390   | .394 | .398 | 9.90         | 10.00 | 10.10 |  |

| Molded Package Length    | D1    | .390   | .394 | .398 | 9.90         | 10.00 | 10.10 |  |

| Lead Thickness           | С     | .004   | .006 | .008 | 0.09         | 0.15  | 0.20  |  |

| Lead Width               | В     | .012   | .015 | .017 | 0.30         | 0.38  | 0.44  |  |

| Pin 1 Corner Chamfer     | СН    | .025   | .035 | .045 | 0.64         | 0.89  | 1.14  |  |

| Mold Draft Angle Top     | α     | 5      | 10   | 15   | 5            | 10    | 15    |  |

| Mold Draft Angle Bottom  | β     | 5      | 10   | 15   | 5            | 10    | 15    |  |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-026

Drawing No. C04-076

NOTES: