Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                              |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c442-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

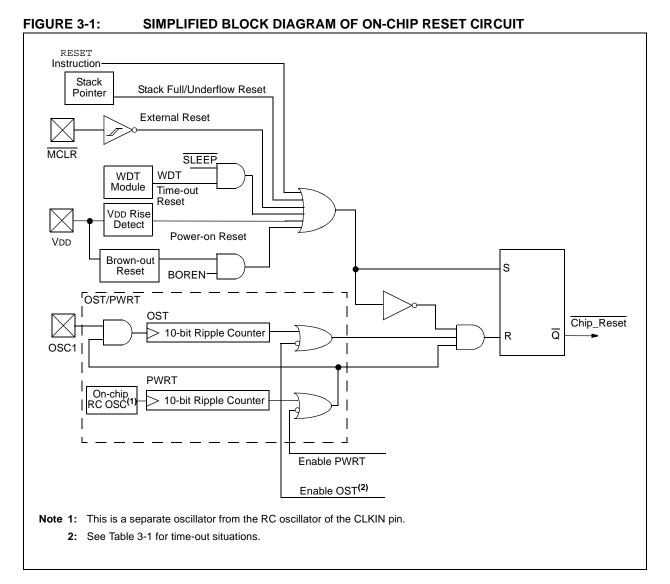

### 3.0 RESET

The PIC18CXX2 differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) Watchdog Timer (WDT) Reset (during normal operation)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

Most registers are unaffected by a RESET. Their status is unknown on POR and unchanged by all other RESETS. The other registers are forced to a "RESET state" on Power-on Reset, MCLR, WDT Reset, Brownout Reset, MCLR Reset during SLEEP, and by the RESET instruction. Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR, are set or cleared differently in different RESET situations, as indicated in Table 3-2. These bits are used in software to determine the nature of the RESET. See Table 3-3 for a full description of the RESET states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The Enhanced MCU devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

MCLR pin is not driven low by any internal RESETS, including WDT.

#### 3.1 Power-on Reset (POR)

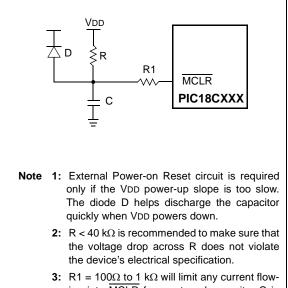

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR circuitry, just tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 3-2.

When the device starts normal operation (i.e., exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

FIGURE 3-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

ing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 3.2 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (parameter #33) only on power-up from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameter #33 for details.

#### 3.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 3.4 PLL Lock Time-out

With the PLL enabled, the time-out sequence following a Power-on Reset is different from other oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator startup time-out (OST).

#### 3.5 Brown-out Reset (BOR)

A configuration bit, BOREN, can disable (if clear/ programmed), or enable (if set) the Brown-out Reset circuitry. If VDD falls below parameter D005 for greater than parameter #35, the brown-out situation will reset the chip. A RESET may not occur if VDD falls below parameter D005 for less than parameter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer will then be invoked and will keep the chip in RESET an additional time delay (parameter #33). If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute the additional time delay.

#### 3.6 Time-out Sequence

On power-up, the time-out sequence is as follows: First, PWRT time-out is invoked after the POR time delay has expired. Then, OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 3-3, Figure 3-4, Figure 3-5, Figure 3-6 and Figure 3-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC18CXXX device operating in parallel.

Table 3-2 shows the RESET conditions for some Special Function Registers, while Table 3-3 shows the RESET conditions for all the registers.

| Register                | Applicable Devices |     |     | ces | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |  |

|-------------------------|--------------------|-----|-----|-----|------------------------------------|---------------------------------------------------------------|---------------------------------|--|--|--|

| TRISE                   | 242                | 442 | 252 | 452 | 0000 -111                          | 0000 -111                                                     | uuuu -uuu                       |  |  |  |

| TRISD                   | 242                | 442 | 252 | 452 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |  |  |

| TRISC                   | 242                | 442 | 252 | 452 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |  |  |

| TRISB                   | 242                | 442 | 252 | 452 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |  |  |

| TRISA <sup>(5, 7)</sup> | 242                | 442 | 252 | 452 | -111 1111 <b>(5)</b>               | -111 1111 <b>(5)</b>                                          | -uuu uuuu <b>(5)</b>            |  |  |  |

| LATE                    | 242                | 442 | 252 | 452 | xxx                                | uuu                                                           | uuu                             |  |  |  |

| LATD                    | 242                | 442 | 252 | 452 | xxxx xxxx                          | սսսս սսսս                                                     | uuuu uuuu                       |  |  |  |

| LATC                    | 242                | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |

| LATB                    | 242                | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |

| LATA <sup>(5, 7)</sup>  | 242                | 442 | 252 | 452 | -xxx xxxx(5)                       | -uuu uuuu <b>(5)</b>                                          | -uuu uuuu <b>(5)</b>            |  |  |  |

| PORTE                   | 242                | 442 | 252 | 452 | 000                                | 000                                                           | uuu                             |  |  |  |

| PORTD                   | 242                | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |

| PORTC                   | 242                | 442 | 252 | 452 | XXXX XXXX                          | սսսս սսսս                                                     | uuuu uuuu                       |  |  |  |

| PORTB                   | 242                | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |

| PORTA <sup>(5, 7)</sup> | 242                | 442 | 252 | 452 | -x0x 0000 <b>(5)</b>               | -u0u 0000 <b>(5)</b>                                          | -uuu uuuu <sup>(5)</sup>        |  |  |  |

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 3-2 for RESET value for specific condition.

5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

**6:** The long write enable is only reset on a POR or  $\overline{MCLR}$  Reset.

7: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read as '0'.

#### $\ensuremath{\textcircled{}^{\circ}}$ 1999-2013 Microchip Technology Inc.

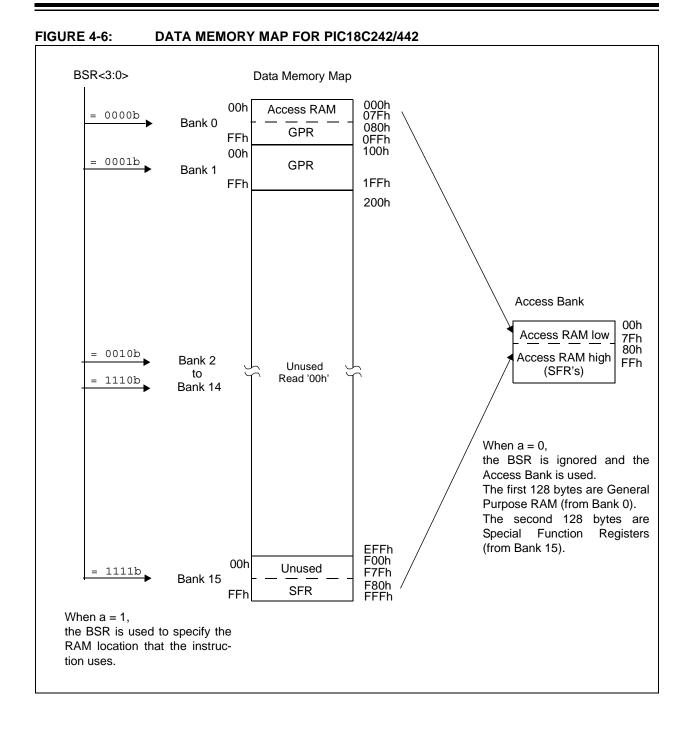

#### 4.10 Access Bank

The Access Bank is an architectural enhancement, which is very useful for C compiler code optimization. The techniques used by the C compiler may also be useful for programs written in assembly.

This data memory region can be used for:

- Intermediate computational values

- · Local variables of subroutines

- Faster context saving/switching of variables

- Common variables

- Faster evaluation/control of SFRs (no banking)

The Access Bank is comprised of the upper 128 bytes in Bank 15 (SFRs) and the lower 128 bytes in Bank 0. These two sections will be referred to as Access RAM High and Access RAM Low, respectively. Figure 4-6 and Figure 4-7 indicate the Access RAM areas.

A bit in the instruction word specifies if the operation is to occur in the bank specified by the BSR register or in the Access Bank. This bit is denoted by the 'a' bit (for access bit).

When forced in the Access Bank (a = '0'), the last address in Access RAM Low is followed by the first address in Access RAM High. Access RAM High maps the Special Function registers, so that these registers can be accessed without any software overhead. This is useful for testing status flags and modifying control bits.

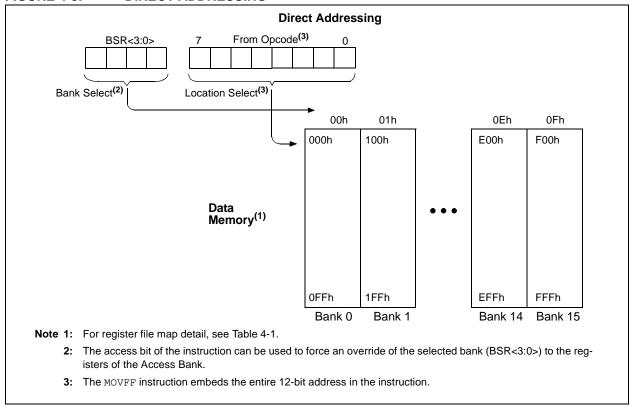

#### 4.11 Bank Select Register (BSR)

The need for a large general purpose memory space dictates a RAM banking scheme. The data memory is partitioned into sixteen banks. When using direct addressing, the BSR should be configured for the desired bank.

BSR<3:0> holds the upper 4 bits of the 12-bit RAM address. The BSR<7:4> bits will always read '0's, and writes will have no effect.

A MOVLB instruction has been provided in the instruction set to assist in selecting banks.

If the currently selected bank is not implemented, any read will return all '0's and all writes are ignored. The STATUS register bits will be set/cleared as appropriate for the instruction performed.

Each Bank extends up to FFh (256 bytes). All data memory is implemented as static RAM.

A MOVFF instruction ignores the BSR, since the 12-bit addresses are embedded into the instruction word.

Section 4.12 provides a description of indirect addressing, which allows linear addressing of the entire RAM space.

#### FIGURE 4-8: DIRECT ADDRESSING

| Name                    | Bit# | Buffer                | Function                                                                                                                                           |

|-------------------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT0                | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input1. Internal software programmable weak pull-up.                                                        |

| RB1/INT1                | bit1 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input2. Internal software programmable weak pull-up.                                                        |

| RB2/INT2                | bit2 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input3. Internal software programmable weak pull-up.                                                        |

| RB3/CCP2 <sup>(3)</sup> | bit3 | TTL/ST <sup>(4)</sup> | Input/output pin. Capture2 input/Compare2 output/PWM output when CCP2MX configuration bit is enabled. Internal software programmable weak pull-up. |

| RB4                     | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                          |

| RB5                     | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                          |

| RB6                     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock.                                |

| RB7                     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data.                                 |

#### TABLE 8-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: A device configuration bit selects which I/O pin the CCP2 pin is multiplexed on.

4: This buffer is a Schmitt Trigger input when configured as the CCP2 input.

| TABLE 8-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |  |

|------------|--------------------------------------------|--|

|            |                                            |  |

| Name    | Bit 7                     | Bit 6         | Bit 5       | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|---------------------------|---------------|-------------|---------|--------|--------|--------|--------|-------------------------|---------------------------------|

| PORTB   | RB7                       | RB6           | RB5         | RB4     | RB3    | RB2    | RB1    | RB0    | xxxx xxxx               | uuuu uuuu                       |

| LATB    | LATB Data Output Register |               |             |         |        |        |        |        |                         |                                 |

| TRISB   | PORTB                     | Data Directio | on Register |         |        |        |        |        | 1111 1111               | 1111 1111                       |

| INTCON  | GIE/<br>GIEH              | PEIE/<br>GIEL | TMR0IE      | INTOIE  | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 000x               | 0000 000u                       |

| INTCON2 | RBPU                      | INTEDG0       | INTEDG1     | INTEDG2 | —      | TMR0IP | —      | RBIP   | 1111 -1-1               | 1111 -1-1                       |

| INTCON3 | INT2IP                    | INT1IP        | —           | INT2IE  | INT1IE | —      | INT2IF | INT1IF | 11-0 0-00               | 11-0 0-00                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

NOTES:

#### 14.3.7 SLEEP OPERATION

In Master mode, all module clocks are halted, and the transmission/reception will remain in that state until the device wakes from SLEEP. After the device returns to normal mode, the module will continue to transmit/ receive data.

In Slave mode, the SPI transmit/receive shift register operates asynchronously to the device. This allows the device to be placed in SLEEP mode, and data to be shifted into the SPI transmit/receive shift register. When all 8-bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device from SLEEP.

#### 14.3.8 EFFECTS OF A RESET

A RESET disables the MSSP module and terminates the current transfer.

#### 14.3.9 BUS MODE COMPATIBILITY

Table 14-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| TABLE 14-1: | <b>SPI BUS MODES</b> |

|-------------|----------------------|

|-------------|----------------------|

| Standard SPI Mode | Control Bits State |     |  |  |

|-------------------|--------------------|-----|--|--|

| Terminology       | СКР                | CKE |  |  |

| 0, 0              | 0                  | 1   |  |  |

| 0, 1              | 0                  | 0   |  |  |

| 1, 0              | 1                  | 1   |  |  |

| 1, 1              | 1                  | 0   |  |  |

There is also a SMP bit which controls when the data is sampled.

| Name    | Bit 7                         | Bit 6         | Bit 5       | Bit 4      | Bit 3        | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------------------------------|---------------|-------------|------------|--------------|--------|---------|---------|-------------------------|---------------------------------|

| INTCON  | GIE/GIEH                      | PEIE/<br>GIEL | TMR0IE      | INTOIE     | RBIE         | TMR0IF | INTOIF  | RBIF    | 0000 000x               | 0000 000u                       |

| PIR1    | PSPIF <sup>(1)</sup>          | ADIF          | RCIF        | TXIF       | SSPIF        | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000               | 0000 0000                       |

| PIE1    | PSPIE <sup>(1)</sup>          | ADIE          | RCIE        | TXIE       | SSPIE        | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000               | 0000 0000                       |

| IPR1    | PSPIP <sup>(1)</sup>          | ADIP          | RCIP        | TXIP       | SSPIP        | CCP1IP | TMR2IP  | TMR1IP  | 0000 0000               | 0000 0000                       |

| TRISC   | PORTC Dat                     | ta Directior  | Register    |            |              |        |         |         | 1111 1111               | 1111 1111                       |

| SSPBUF  | Synchronou                    | is Serial Po  | ort Receive | Buffer/Tra | nsmit Regist | er     |         |         | xxxx xxxx               | uuuu uuuu                       |

| SSPCON  | WCOL                          | SSPOV         | SSPEN       | CKP        | SSPM3        | SSPM2  | SSPM1   | SSPM0   | 0000 0000               | 0000 0000                       |

| TRISA   | PORTA Data Direction Register |               |             |            |              |        | 11 1111 | 11 1111 |                         |                                 |

| SSPSTAT | SMP                           | CKE           | D/A         | Р          | S            | R/W    | UA      | BF      | 0000 0000               | 0000 0000                       |

.

#### TABLE 14-2: REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode. **Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

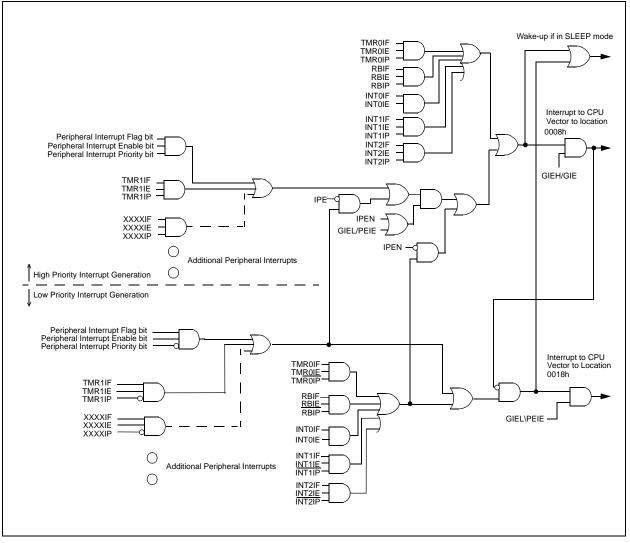

#### 14.4.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all 0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> is set). Following a START bit detect, 8-bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware. If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-bit address mode, then the second half of the address is not necessary, the UA bit will not be set, and the slave will begin receiving data after the Acknowledge (Figure 14-12).

#### 14.4.3 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle, with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt, if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

- Acknowledge Transmit

- Repeated START

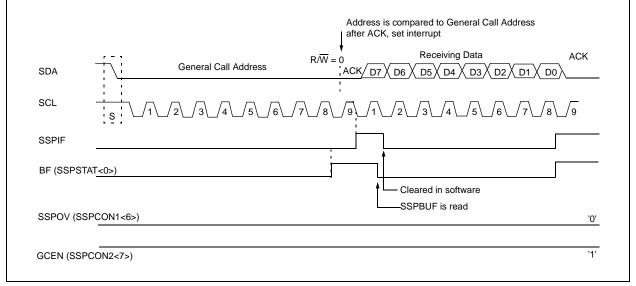

#### 14.4.5 BAUD RATE GENERATOR

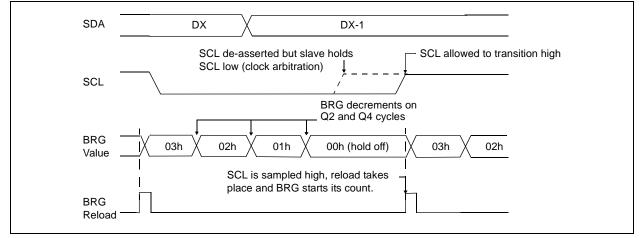

In I<sup>2</sup>C Master mode, the reload value for the BRG is located in the lower 7 bits of the SSPADD register (Figure 14-14). When the BRG is loaded with this value, the BRG counts down to 0 and stops until another reload has taken place. The BRG count is dec-

remented twice per instruction cycle (Tcr) on the Q2 and Q4 clocks. In  $I^2C$  Master mode, the BRG is reloaded automatically. If Clock Arbitration is taking place, for instance, the BRG will be reloaded when the SCL pin is sampled high (Figure 14-15).

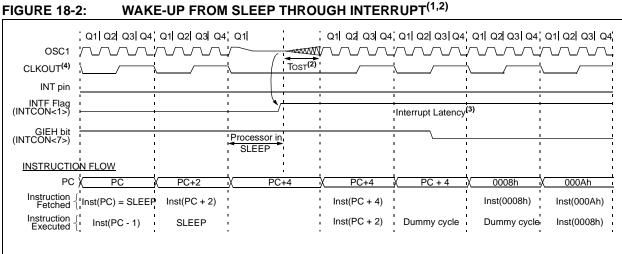

Note 1: XT, HS or LP oscillator mode assumed.

2: GIE = '1' assumed. In this case, after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

3: TOST = 1024TOSC (drawing not to scale) This delay will not occur for RC and EC osc modes.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 18.4 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: Microchip Technology does not recommend code protecting windowed devices.

#### 18.5 ID Locations

Five memory locations (200000h - 200004h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are accessible during normal execution through the TBLRD instruction or during program/verify. The ID locations can be read when the device is code protected.

### 18.6 In-Circuit Serial Programming

PIC18CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

#### TABLE 19-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| a               | RAM access bit                                                                                                                               |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                  |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                 |

| bbb             | Bit address within an 8-bit file register (0 to 7)                                                                                           |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                   |

| d               | Destination select bit;                                                                                                                      |

|                 | d = 0: store result in WREG,                                                                                                                 |

| dt.             | d = 1: store result in file register f.                                                                                                      |

| dest            | Destination either the WREG register or the specified register file location<br>8-bit Register file address (0x00 to 0xFF)                   |

| f               |                                                                                                                                              |

| fs              | 12-bit Register file address (0x000 to 0xFFF). This is the source address.                                                                   |

| fd              | 12-bit Register file address (0x000 to 0xFFF). This is the destination address.                                                              |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value)                                                     |

| label           |                                                                                                                                              |

| mm              | The mode of the TBLPTR register for the Table Read and Table Write instructions<br>Only used with Table Read and Table Write instructions:   |

| *               | No Change to register (such as TBLPTR with Table reads and writes)                                                                           |

|                 |                                                                                                                                              |

| *+              | Post-Increment register (such as TBLPTR with Table reads and writes)                                                                         |

|                 | Post-Decrement register (such as TBLPTR with Table reads and writes)<br>Pre-Increment register (such as TBLPTR with Table reads and writes)  |

| +*              |                                                                                                                                              |

| n               | The relative address (2's complement number) for relative branch instructions, or the direct address for Call/Branch and Return instructions |

| PRODH           | Product of Multiply high byte                                                                                                                |

| PRODL           | Product of Multiply low byte                                                                                                                 |

| S               | Fast Call/Return mode select bit.                                                                                                            |

|                 | s = 0: do not update into/from shadow registers                                                                                              |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                       |

| u               | Unused or Unchanged                                                                                                                          |

| WREG            | Working register (accumulator)                                                                                                               |

| x               | Don't care (0 or 1)                                                                                                                          |

|                 | The assembler will generate code with $x = 0$ . It is the recommended form of use for compatibility with all Microchip software tools.       |

| TBLPTR          | 21-bit Table Pointer (points to a Program Memory location)                                                                                   |

| TABLAT          | 8-bit Table Latch                                                                                                                            |

| TOS             | Top-of-Stack                                                                                                                                 |

| PC              | Program Counter                                                                                                                              |

| PCL             | Program Counter Low Byte                                                                                                                     |

| PCH             | Program Counter High Byte                                                                                                                    |

| PCLATH          | Program Counter High Byte Latch                                                                                                              |

| PCLATU          | Program Counter Upper Byte Latch                                                                                                             |

| GIE             | Global Interrupt Enable bit                                                                                                                  |

|                 | Watchdog Timer                                                                                                                               |

| WDT<br>TO       | Time-out bit                                                                                                                                 |

| PD              | Power-down bit                                                                                                                               |

| C, DC, Z, OV, N | ALU status bits Carry, Digit Carry, Zero, Overflow, Negative                                                                                 |

| []              | Optional                                                                                                                                     |

|                 | Contents                                                                                                                                     |

| ( )             |                                                                                                                                              |

| $\rightarrow$   | Assigned to                                                                                                                                  |

| < >             | Register bit field In the set of                                                                                                             |

| e               |                                                                                                                                              |

| italics         | User defined term (font is courier)                                                                                                          |

f [,a]

| MO\         | /LW            | Move lite           | Move literal to WREG                           |      |     |            |  |  |

|-------------|----------------|---------------------|------------------------------------------------|------|-----|------------|--|--|

| Synt        | ax:            | [ label ]           | MOVLW                                          | / k  |     |            |  |  |

| Ope         | rands:         | $0 \le k \le 2\xi$  | 55                                             |      |     |            |  |  |

| Ope         | ration:        | $k \rightarrow WRE$ | G                                              |      |     |            |  |  |

| Statu       | us Affected:   | None                |                                                |      |     |            |  |  |

| Enco        | oding:         | 0000                | 1110                                           | kkk. | k   | kkkk       |  |  |

| Desc        | cription:      | The eight<br>WREG.  | The eight-bit literal 'k' is loaded into WREG. |      |     |            |  |  |

| Wor         | ds:            | 1                   | 1                                              |      |     |            |  |  |

| Cycl        | es:            | 1                   |                                                |      |     |            |  |  |

| QC          | ycle Activity: |                     |                                                |      |     |            |  |  |

|             | Q1             | Q2                  | Q3                                             | 3    | C   | 24         |  |  |

|             | Decode         | Read<br>literal 'k' | Proce                                          |      |     | e to<br>EG |  |  |

|             |                | INCIDI N            | Dala                                           | a    | VVN | 10         |  |  |

| <u>Exar</u> | <u>mple</u> :  | MOVLW               | 0x5A                                           |      |     |            |  |  |

Operation:  $(\mathsf{WREG}) \to \mathsf{f}$ Status Affected: None Encoding: 0110 ffff ffff 111a Description: Move data from WREG to register 'f'. Location 'f' can be anywhere in the 256 byte bank. If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' = 1, then the bank will be selected as per the BSR value (default). Words: 1 Cycles: 1 Q Cycle Activity: Q1 Q2 Q3 Q4 Decode Read Process Write register 'f' Data register 'f' Example:

Move WREG to f

[label] MOVWF

$0 \leq f \leq 255$ a ∈ [0,1]

MOVWF REG, 0 **Before Instruction** WREG 0x4F = REG = 0xFF

After Instruction WREG 0x4F = REG 0x4F=

MOVWF

Syntax:

Operands:

After Instruction WREG = 0x5A

| RRNCF                   | Rotate Right f (no carry)                                                                                                                                                                                                                                                                  | SETF                         |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Syntax:                 | [ label ] RRNCF f [,d [,a]                                                                                                                                                                                                                                                                 | Syntax:                      |

| Operands:               | $0 \le f \le 255$<br>$d \in [0,1]$                                                                                                                                                                                                                                                         | Operands:                    |

|                         | a ∈ [0,1]                                                                                                                                                                                                                                                                                  | Operation:                   |

| Operation:              | $(f < n >) \rightarrow dest < n - 1 >,$<br>$(f < 0 >) \rightarrow dest < 7 >$                                                                                                                                                                                                              | Status Affected<br>Encoding: |

| Status Affecte          | ed: N,Z                                                                                                                                                                                                                                                                                    | -                            |

| Encoding:               | 0100 00da ffff ffff                                                                                                                                                                                                                                                                        | Description:                 |

| Description:            | The contents of register 'f' are<br>rotated one bit to the right. If 'd' is 0,<br>the result is placed in WREG. If 'd'<br>is 1, the result is placed back in<br>register 'f' (default). If 'a' is 0, the<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' is 1, then | Words:<br>Cycles:            |

|                         | the bank will be selected as per the                                                                                                                                                                                                                                                       | Q Cycle Activit              |

|                         | BSR value (default).                                                                                                                                                                                                                                                                       | Q1                           |

|                         | register f                                                                                                                                                                                                                                                                                 | Decode                       |

| Words:                  | 1                                                                                                                                                                                                                                                                                          |                              |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                          | Example:                     |

| Q Cycle Activ           | vity:                                                                                                                                                                                                                                                                                      | Before Inst                  |

| Q1                      | Q2 Q3 Q4                                                                                                                                                                                                                                                                                   | REG                          |

| Decode                  | e Read Process Write to<br>register 'f' Data destination                                                                                                                                                                                                                                   | After Instru<br>REG          |

| Example 1:<br>Before In | RRNCF REG, 1, 0                                                                                                                                                                                                                                                                            |                              |

| REG                     | = 1101 0111                                                                                                                                                                                                                                                                                |                              |

| After Inst              |                                                                                                                                                                                                                                                                                            |                              |

| REG                     | = 1110 1011                                                                                                                                                                                                                                                                                |                              |

| Example 2:              | RRNCF REG, 0, 0                                                                                                                                                                                                                                                                            |                              |

| Before In               | struction                                                                                                                                                                                                                                                                                  |                              |

|                         | ; = ?<br>= 1101 0111                                                                                                                                                                                                                                                                       |                              |

| After Inst              |                                                                                                                                                                                                                                                                                            |                              |

| WREG                    |                                                                                                                                                                                                                                                                                            |                              |

| Synta  | ix:                              | [ <i>label</i> ] SE                                                           | TFf[,                                                           | a]                                                       |                                  |  |  |  |

|--------|----------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|----------------------------------|--|--|--|

| pera   | ands:                            | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                      | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$ |                                                          |                                  |  |  |  |

| pera   | ation:                           | $FFh\tof$                                                                     |                                                                 |                                                          |                                  |  |  |  |

| status | s Affected:                      | None                                                                          |                                                                 |                                                          |                                  |  |  |  |

| nco    | ding:                            | 0110                                                                          | 100a                                                            | ffff                                                     | ffff                             |  |  |  |

| )esci  | ription:                         | The conte<br>ter are se<br>Access Ba<br>riding the<br>the bank v<br>BSR value | t to FFh<br>ank will<br>BSR val<br>will be se                   | . If 'a' is 0<br>be select<br>ue. If 'a' i<br>elected as | ), the<br>ed, over-<br>s 1, then |  |  |  |

| Vord   | s:                               | 1                                                                             |                                                                 |                                                          |                                  |  |  |  |

| ycle   | s:                               | 1                                                                             |                                                                 |                                                          |                                  |  |  |  |

| Q Cy   | cle Activity:                    |                                                                               |                                                                 |                                                          |                                  |  |  |  |

|        | Q1                               | Q2                                                                            | Q                                                               | 3                                                        | Q4                               |  |  |  |

|        | Decode                           | Read<br>register 'f'                                                          | Proce<br>Data                                                   |                                                          | Write<br>gister 'f'              |  |  |  |

|        |                                  |                                                                               |                                                                 |                                                          |                                  |  |  |  |

| xam    | <u>iple</u> :                    | SETF                                                                          | RE                                                              | G,1                                                      |                                  |  |  |  |

| E      | Before Instruction<br>REG = 0x5A |                                                                               |                                                                 |                                                          |                                  |  |  |  |

| A      | After Instruction                |                                                                               |                                                                 |                                                          |                                  |  |  |  |

0xFF

=

Set f

© 1999-2013 Microchip Technology Inc.

| SLEEP                                       | Enter SL                             | Enter SLEEP mode             |             | SUBFWB                          | Subtract f from WREG with borro |                                      |                  |  |

|---------------------------------------------|--------------------------------------|------------------------------|-------------|---------------------------------|---------------------------------|--------------------------------------|------------------|--|

| Syntax:                                     | [ label ]                            | SLEEP                        |             | Syntax:                         | [ label ]                       | [ <i>label</i> ] SUBFWB f[,d[,a]     |                  |  |

| Operands:                                   | None                                 |                              |             | Operands:                       | $0 \le f \le 25$                | -                                    |                  |  |

| Operation: $00h \rightarrow WDT$ ,          |                                      |                              | d ∈ [0,1]   |                                 |                                 |                                      |                  |  |

| $0 \rightarrow \underline{WDT}$ postscaler, |                                      |                              | a ∈ [0,1]   |                                 |                                 |                                      |                  |  |

|                                             | $1 \rightarrow TO, 0 \rightarrow PD$ |                              |             | Operation:                      |                                 | $-(f) - (\overline{C}) -$            | → dest           |  |

| Otatua Affaata                              |                                      |                              |             | Status Affected: N,OV, C, DC, Z |                                 |                                      |                  |  |

| Status Affecte                              |                                      |                              |             | Encoding:                       | Encoding: 0101 01da fi          |                                      |                  |  |

| Encoding:                                   | 0000                                 | 0000 000                     |             | Description:                    |                                 | Subtract register 'f' and carry flag |                  |  |

| Description:                                | -                                    | er-down statu                |             |                                 |                                 | from WREG                            |                  |  |

|                                             |                                      | The time-out<br>et. Watchdog |             |                                 |                                 | thod). If 'd' is<br>WREG. If 'd'     |                  |  |

|                                             |                                      | caler are clea               |             |                                 | is stored i                     | in register 'f' (                    | default). If 'a' |  |

|                                             | The proc                             | cessor is put i              | nto SLEEP   |                                 |                                 | cess Bank w                          |                  |  |

|                                             | mode wi                              | th the oscillat              | or stopped. |                                 |                                 | g the BSR va<br>bank will be s       |                  |  |

| Nords:                                      | 1                                    |                              |             |                                 |                                 | value (defau                         |                  |  |

| Cycles:                                     | 1                                    |                              |             | Words:                          | 1                               |                                      |                  |  |

| Q Cycle Activ                               | ity:                                 |                              |             | Cycles:                         | 1                               |                                      |                  |  |

| Q1                                          | Q2                                   | Q3                           | Q4          | Q Cycle Activity                |                                 |                                      |                  |  |

| Decode                                      | No                                   | Process                      | Go to       | Q1                              | Q2                              | Q3                                   | Q4               |  |

|                                             | operation                            | Data                         | sleep       | Decode                          | Read                            | Process                              | Write to         |  |

| Example:                                    | SLEEP                                |                              |             |                                 | register 'f'                    | Data                                 | destination      |  |

| Before In:                                  | struction                            |                              |             | Example 1:                      | SUBFWB                          | REG, 1,                              | 0                |  |

| TO :                                        | = ?                                  |                              |             | Before Instru                   | uction                          |                                      |                  |  |

| PD :                                        | -                                    |                              |             | REG                             | = 3                             |                                      |                  |  |

| After Instr<br>TO                           |                                      |                              |             | WREG<br>C                       | = 2<br>= 1                      |                                      |                  |  |

| PD :                                        |                                      |                              |             | After Instruc                   |                                 |                                      |                  |  |

| f If WDT cau                                | ises wake-up, t                      | his bit is clea              | red.        | REG                             | = FF                            |                                      |                  |  |

|                                             |                                      |                              |             | WREG                            | = 2                             |                                      |                  |  |

|                                             |                                      |                              |             | C<br>Z                          | = 0<br>= 0                      |                                      |                  |  |

|                                             |                                      |                              |             | Ν                               | = 1                             | ; result :                           | is negativ       |  |

|                                             |                                      |                              |             | Example 2:                      | SUBFWB                          | REG, 0,                              | 0                |  |

|                                             |                                      |                              |             | Before Instru                   | uction                          |                                      |                  |  |

|                                             |                                      |                              |             | REG                             | = 2                             |                                      |                  |  |

|                                             |                                      |                              |             | WREG<br>C                       | = 5<br>= 1                      |                                      |                  |  |

|                                             |                                      |                              |             | After Instruc                   | tion                            |                                      |                  |  |

|                                             |                                      |                              |             | REG                             | = 2                             |                                      |                  |  |

|                                             |                                      |                              |             | WREG<br>C                       | = 3<br>= 1                      |                                      |                  |  |

|                                             |                                      |                              |             | Z                               | = 1<br>= 0                      |                                      |                  |  |

|                                             |                                      |                              |             | Ν                               | = 0                             | ; result :                           | is positiv       |  |

|                                             |                                      |                              |             | Example 3:                      | SUBFWB                          | REG, 1,                              | 0                |  |

|                                             |                                      |                              |             | Before Instr                    |                                 |                                      |                  |  |

|                                             |                                      |                              |             | REG<br>WREG                     | = 1<br>= 2                      |                                      |                  |  |

|                                             |                                      |                              |             | WREG<br>C                       | = 2<br>= 0                      |                                      |                  |  |

|                                             |                                      |                              |             | After Instruc                   | tion                            |                                      |                  |  |

|                                             |                                      |                              |             |                                 |                                 |                                      |                  |  |

|                                             |                                      |                              |             | REG                             | = 0                             |                                      |                  |  |

|                                             |                                      |                              |             | WREG                            | = 2                             |                                      |                  |  |

|                                             |                                      |                              |             |                                 |                                 | ; result :                           | is zero          |  |

|                   |        |                                                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +40^{\circ}C$ |       |       |                                                       |  |  |

|-------------------|--------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|-------|-------------------------------------------------------|--|--|

| Param.<br>No. Sym |        | Characteristic                                        | Min                                                                                                                 | Max   | Units | Conditions                                            |  |  |

|                   |        | Internal Program Memory<br>Programming Specs (Note 1) |                                                                                                                     |       |       |                                                       |  |  |

| D110              | Vpp    | Voltage on MCLR/VPP pin                               | 12.75                                                                                                               | 13.25 | V     | (Note 2)                                              |  |  |

| D111              | Vddp   | Supply voltage during<br>programming                  | 4.75                                                                                                                | 5.25  | V     |                                                       |  |  |

| D112              | IPP    | Current into MCLR/VPP pin                             | —                                                                                                                   | 50    | mA    |                                                       |  |  |

| D113              | IDDP   | Supply current during<br>programming                  | —                                                                                                                   | 30    | mA    |                                                       |  |  |

| D114              | TPROG  | Programming pulse width                               | 50                                                                                                                  | 1000  | μS    | Terminated via internal/external interrupt or a RESET |  |  |

| D115              | TERASE | EPROM erase time                                      |                                                                                                                     |       |       |                                                       |  |  |

|                   |        | Device operation $\leq$ 3V                            | 60                                                                                                                  | —     | min.  |                                                       |  |  |

|                   |        | Device operation $\ge 3V$                             | 30                                                                                                                  | —     | min.  |                                                       |  |  |

#### TABLE 21-2: EPROM PROGRAMMING REQUIREMENTS

**Note 1:** These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in the PIC18CXXX Programming Specifications (Literature Number DS39028).

2: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

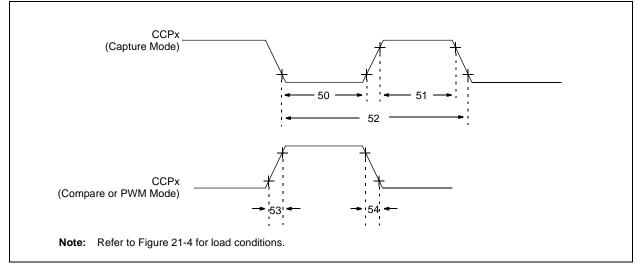

#### FIGURE 21-10: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

### TABLE 21-9: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param.<br>No. | Symbol                | CI                       | naracteristi | с           | Min                   | Мах | Units | Conditions                        |

|---------------|-----------------------|--------------------------|--------------|-------------|-----------------------|-----|-------|-----------------------------------|

| 50 TccL       |                       | CCPx input low No Presca |              | ler         | 0.5Tcy + 20           | —   | ns    |                                   |

|               |                       | time                     | With         | PIC18CXXX   | 10                    | _   | ns    |                                   |

|               |                       | Prescaler                | PIC18LCXXX   | 20          | —                     | ns  |       |                                   |

| 51 TccH       | CCPx input No Presca  |                          | ler          | 0.5Tcy + 20 | _                     | ns  |       |                                   |

|               | high time             | With<br>Prescaler        | PIC18CXXX    | 10          | —                     | ns  |       |                                   |

|               |                       |                          | PIC18LCXXX   | 20          | _                     | ns  |       |                                   |

| 52            | TccP                  | CCPx input period        |              |             | <u>3Tcy + 40</u><br>N | —   | ns    | N = prescale<br>value (1,4 or 16) |

| 53 TccR       | CCPx output fall time |                          | PIC18CXXX    | _           | 25                    | ns  |       |                                   |

|               | PIC18LCXXX            |                          |              | _           | 50                    | ns  |       |                                   |

| 54            | TccF                  |                          |              | PIC18CXXX   | _                     | 25  | ns    |                                   |

|               |                       |                          |              | PIC18LCXXX  |                       | 50  | ns    |                                   |

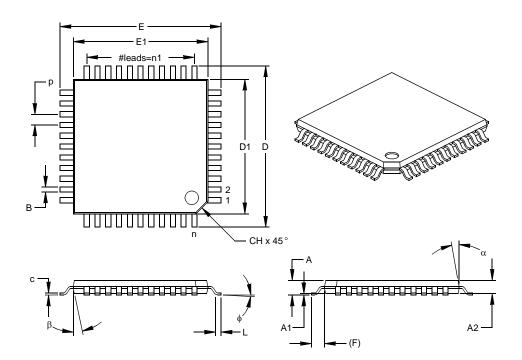

#### 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     |      | INCHES |      | Μ     | ILLIMETERS | *     |

|--------------------------|-----------|------|--------|------|-------|------------|-------|

| Dimensi                  | on Limits | MIN  | NOM    | MAX  | MIN   | NOM        | MAX   |

| Number of Pins           | n         |      | 44     |      |       | 44         |       |

| Pitch                    | р         |      | .031   |      |       | 0.80       |       |

| Pins per Side            | n1        |      | 11     |      |       | 11         |       |

| Overall Height           | Α         | .039 | .043   | .047 | 1.00  | 1.10       | 1.20  |

| Molded Package Thickness | A2        | .037 | .039   | .041 | 0.95  | 1.00       | 1.05  |

| Standoff §               | A1        | .002 | .004   | .006 | 0.05  | 0.10       | 0.15  |

| Foot Length              | L         | .018 | .024   | .030 | 0.45  | 0.60       | 0.75  |

| Footprint (Reference)    | (F)       |      | .039   |      | 1.00  |            |       |

| Foot Angle               | ¢         | 0    | 3.5    | 7    | 0     | 3.5        | 7     |

| Overall Width            | Е         | .463 | .472   | .482 | 11.75 | 12.00      | 12.25 |

| Overall Length           | D         | .463 | .472   | .482 | 11.75 | 12.00      | 12.25 |

| Molded Package Width     | E1        | .390 | .394   | .398 | 9.90  | 10.00      | 10.10 |

| Molded Package Length    | D1        | .390 | .394   | .398 | 9.90  | 10.00      | 10.10 |

| Lead Thickness           | С         | .004 | .006   | .008 | 0.09  | 0.15       | 0.20  |

| Lead Width               | В         | .012 | .015   | .017 | 0.30  | 0.38       | 0.44  |

| Pin 1 Corner Chamfer     | СН        | .025 | .035   | .045 | 0.64  | 0.89       | 1.14  |

| Mold Draft Angle Top     | α         | 5    | 10     | 15   | 5     | 10         | 15    |

| Mold Draft Angle Bottom  | β         | 5    | 10     | 15   | 5     | 10         | 15    |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-026

Drawing No. C04-076

### APPENDIX A: REVISION HISTORY

#### Revision A (July 1999)

Original data sheet for PIC18CXX2 family.

#### **Revision B (March 2001)**

Added DC and AC characteristics graphs (Section 22.0).

#### **Revision C (January 2013)**

Added a note to each package outline drawing.

#### TABLE 1: DEVICE DIFFERENCES

### APPENDIX B: DEVICE DIFFERENCES

The differences between the devices listed in this data sheet are shown in Table 1.

| Feature                   | PIC18C242                              | PIC18C252                              | PIC18C442                                             | PIC18C452                                             |

|---------------------------|----------------------------------------|----------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| Program Memory (Kbytes)   | 16                                     | 32                                     | 16                                                    | 32                                                    |

| Data Memory (Bytes)       | 512                                    | 1536                                   | 512                                                   | 1536                                                  |

| A/D Channels              | 5                                      | 5                                      | 8                                                     | 8                                                     |

| Parallel Slave Port (PSP) | No                                     | No                                     | Yes                                                   | Yes                                                   |

| Package Types             | 28-pin DIP<br>28-pin SOIC<br>28-pin JW | 28-pin DIP<br>28-pin SOIC<br>28-pin JW | 40-pin DIP<br>44-pin PLCC<br>44-pin TQFP<br>40-pin JW | 40-pin DIP<br>44-pin PLCC<br>44-pin TQFP<br>40-pin JW |