Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                             |

| Number of I/O              | 33                                                                     |

| Program Memory Size        | 16KB (8K x 16)                                                         |

| Program Memory Type        | EPROM, UV                                                              |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | External                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

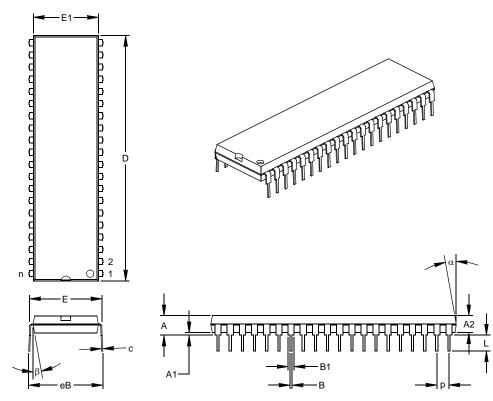

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 40-CDIP (0.600", 15.24mm) Window                                       |

| Supplier Device Package    | 40-Cerdip                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c442-jw |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                | Pi  | n Numt  | per  | D'          | Duffer         |                                                             |

|--------------------------------|-----|---------|------|-------------|----------------|-------------------------------------------------------------|

| Pin Name                       | DIP | PLCC    | TQFP | Pin<br>Type | Buffer<br>Type | Description                                                 |

|                                |     | 1 200   | 14.1 |             |                | PORTC is a bi-directional I/O port.                         |

| RC0/T1OSO/T1CKI                | 15  | 16      | 32   |             |                |                                                             |

| RC0                            |     |         |      | I/O         | ST             | Digital I/O.                                                |

| T1OSO                          |     |         |      | 0           | _              | Timer1 oscillator output.                                   |

| T1CKI                          |     |         |      | Ι           | ST             | Timer1/Timer3 external clock input.                         |

| RC1/T1OSI/CCP2                 | 16  | 18      | 35   |             |                |                                                             |

| RC1                            |     |         |      | I/O         | ST             | Digital I/O.                                                |

| T1OSI                          |     |         |      |             | CMOS           | Timer1 oscillator input.                                    |

| CCP2                           | 47  | 40      |      | I/O         | ST             | Capture2 input, Compare2 output, PWM2 output.               |

| RC2/CCP1<br>RC2                | 17  | 19      | 36   | I/O         | ST             | Digital I/O                                                 |

| CCP1                           |     |         |      | 1/O<br>1/O  | ST             | Digital I/O.<br>Capture1 input/Compare1 output/PWM1 output. |

| RC3/SCK/SCL                    | 18  | 20      | 37   | "0          | 01             |                                                             |

| RC3                            | 10  | 20      | 57   | I/O         | ST             | Digital I/O.                                                |

| SCK                            |     |         |      | I/O         | ST             | Synchronous serial clock input/output for                   |

|                                |     |         |      |             |                | SPI mode.                                                   |

| SCL                            |     |         |      | I/O         | ST             | Synchronous serial clock input/output for                   |

|                                |     |         |      |             |                | I <sup>2</sup> C mode.                                      |

| RC4/SDI/SDA                    | 23  | 25      | 42   |             |                |                                                             |

| RC4                            |     |         |      | I/O         | ST             | Digital I/O.                                                |

| SDI<br>SDA                     |     |         |      | I<br>I/O    | ST<br>ST       | SPI Data In.<br>I <sup>2</sup> C Data I/O.                  |

|                                | 24  | 20      | 43   | 1/0         | 31             | T C Data 1/O.                                               |

| RC5/SDO<br>RC5                 | 24  | 26      | 43   | I/O         | ST             | Digital I/O.                                                |

| SDO                            |     |         |      | 0           | _              | SPI Data Out.                                               |

| RC6/TX/CK                      | 25  | 27      | 44   | -           |                |                                                             |

| RC6                            | 20  |         | ••   | I/O         | ST             | Digital I/O.                                                |

| ТХ                             |     |         |      | 0           | _              | USART Asynchronous Transmit.                                |

| СК                             |     |         |      | I/O         | ST             | USART Synchronous Clock (see related RX/DT).                |

| RC7/RX/DT                      | 26  | 29      | 1    |             |                |                                                             |

| RC7                            |     |         |      | I/O         | ST             | Digital I/O.                                                |

| RX                             |     |         |      |             | ST             | USART Asynchronous Receive.                                 |

|                                |     | 41.1. 1 |      | I/O         | ST             | USART Synchronous Data (see related TX/CK).                 |

| Legend: TTL = TTL<br>ST = Schn |     |         |      |             |                | OS = CMOS compatible input or output                        |

#### PIC18C4X2 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-3:**

ST = Schmitt Trigger input with CMOS levels I = Input

O = Output

P = Power

OD = Open Drain (no P diode to VDD)

| Oscillator                         | Power-up                  | (2)                | Brown-out <sup>(2)</sup>  | Wake-up from                  |

|------------------------------------|---------------------------|--------------------|---------------------------|-------------------------------|

| Configuration                      | PWRTE = 0                 | PWRTE = 0PWRTE = 1 |                           | SLEEP or<br>Oscillator Switch |

| HS with PLL enabled <sup>(1)</sup> | 72 ms + 1024Tosc<br>+ 2ms | 1024Tosc<br>+ 2 ms | 72 ms + 1024Tosc<br>+ 2ms | 1024Tosc + 2 ms               |

| HS, XT, LP                         | 72 ms + 1024Tosc          | 1024Tosc           | 72 ms + 1024Tosc          | 1024Tosc                      |

| EC                                 | 72 ms                     | _                  | 72 ms                     | —                             |

| External RC                        | 72 ms                     |                    | 72 ms                     | —                             |

**Note 1:** 2 ms is the nominal time required for the 4x PLL to lock.

**2:** 72 ms is the nominal Power-up Timer delay.

#### REGISTER 3-1: RCON REGISTER BITS AND POSITIONS

| R/W-0 | R/W-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-0 | R/W-0 |

|-------|-------|-----|-------|-------|-------|-------|-------|

| IPEN  | LWRT  | —   | RI    | TO    | PD    | POR   | BOR   |

| bit 7 |       |     |       |       |       |       | bit 0 |

**Note:** See Register 4-3 on page 53 for bit definitions.

## TABLE 3-2:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

| Condition                                     | Program<br>Counter    | RCON<br>Register | RI | то | PD | POR | BOR | STKFUL | STKUNF |

|-----------------------------------------------|-----------------------|------------------|----|----|----|-----|-----|--------|--------|

| Power-on Reset                                | 0000h                 | 00-1 1100        | 1  | 1  | 1  | 0   | 0   | u      | u      |

| MCLR Reset during normal operation            | 0000h                 | 00-u uuuu        | u  | u  | u  | u   | u   | u      | u      |

| Software Reset during normal operation        | 0000h                 | 0u-0 uuuu        | 0  | u  | u  | u   | u   | u      | u      |

| Stack Full Reset during normal operation      | 0000h                 | 0u-u uull        | u  | u  | u  | u   | u   | u      | 1      |

| Stack Underflow Reset during normal operation | 0000h                 | 0u-u uull        | u  | u  | u  | u   | u   | 1      | u      |

| MCLR Reset during SLEEP                       | 0000h                 | 00-u 10uu        | u  | 1  | 0  | u   | u   | u      | u      |

| WDT Reset                                     | 0000h                 | 0u-u 01uu        | 1  | 0  | 1  | u   | u   | u      | u      |

| WDT Wake-up                                   | PC + 2                | uu-u 00uu        | u  | 0  | 0  | u   | u   | u      | u      |

| Brown-out Reset                               | 0000h                 | 0u-1 11u0        | 1  | 1  | 1  | 1   | 0   | u      | u      |

| Interrupt wake-up from SLEEP                  | PC + 2 <sup>(1)</sup> | uu-u 00uu        | u  | 1  | 0  | u   | u   | u      | u      |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (0x000008h or 0x000018h).

## 4.3 Fast Register Stack

A "fast interrupt return" option is available for interrupts. A Fast Register Stack is provided for the STATUS, WREG and BSR registers and are only one in depth. The stack is not readable or writable and is loaded with the current value of the corresponding register when the processor vectors for an interrupt. The values in the registers are then loaded back into the working registers, if the FAST RETURN instruction is used to return from the interrupt.

A low or high priority interrupt source will push values into the stack registers. If both low and high priority interrupts are enabled, the stack registers cannot be used reliably for low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten.

If high priority interrupts are not disabled during low priority interrupts, users must save the key registers in software during a low priority interrupt.

If no interrupts are used, the fast register stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a FAST CALL instruction must be executed.

Example 4-1 shows a source code example that uses the fast register stack.

## EXAMPLE 4-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|-----------------|---------------------------------------------------------|

| SUB1            |                                                         |

| RETURN FAST     | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

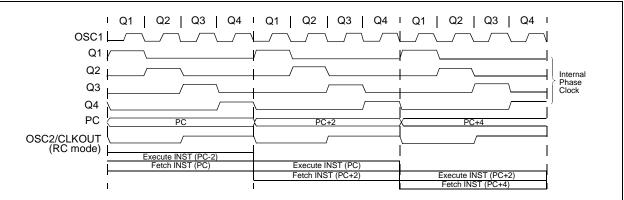

## FIGURE 4-4: CLOCK/INSTRUCTION CYCLE

4.4 PCL, PCLATH and PCLATU

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21-bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCH register. The Upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCU register may be performed through the PCLATU register.

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the LSB of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

The contents of PCLATH and PCLATU will be transferred to the program counter by an operation that writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see Section 4.8.1).

## 4.5 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 4-4.

## 5.1.2 TABLAT - TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch is used to hold 8-bit data during data transfers between program memory and data memory.

#### 5.1.3 TBLPTR - TABLE POINTER REGISTER

The Table Pointer (TBLPTR) addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers (Table Pointer Upper Byte, High Byte and Low Byte). These three registers (TBLPTRU:TBLPTRH:TBLPTRL) join to form a 22-bit wide pointer. The lower 21-bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the Device ID, the User ID and the Configuration bits.

The Table Pointer, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways, based on the table operation. These operations are shown in Table 5-1. These operations on the TBLPTR only affect the lower 21-bits.

#### TABLE 5-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

## 5.2 Internal Program Memory Read/ Writes

#### 5.2.1 TABLE READ OVERVIEW (TBLRD)

The TBLRD instructions are used to read data from program memory to data memory.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TAB-LAT. In addition, TBLPTR can be modified automatically for the next Table Read operation.

Table Reads from program memory are performed one byte at a time. The instruction will load TABLAT with the one byte from program memory pointed to by TBLPTR.

#### 5.2.2 INTERNAL PROGRAM MEMORY WRITE BLOCK SIZE

The internal program memory of PIC18CXXX devices is written in blocks. For PIC18CXX2 devices, the write block size is 2 bytes. Consequently, Table Write operations to internal program memory are performed in pairs, one byte at a time. When a Table Write occurs to an even program memory address (TBLPTR<0> = 0), the contents of TABLAT are transferred to an internal holding register. This is performed as a short write and the program memory block is not actually programmed at this time. The holding register is not accessible by the user.

When a Table Write occurs to an odd program memory address (TBLPTR<0>=1), a long write is started. During the long write, the contents of TABLAT are written to the high byte of the program memory block and the contents of the holding register are transferred to the low byte of the program memory block.

Figure 5-3 shows the holding register and the program memory write blocks.

If a single byte is to be programmed, the low (even) byte of the destination program word should be read using TBLRD\*, modified or changed, if required, and written back to the same address using TBLWT\*+. The high (odd) byte should be read using TBLRD\*, modified or changed if required, and written back to the same address using TBLWT. A write to the odd address will cause a long write to begin. This process ensures that existing data in either byte will not be changed unless desired.

## 7.1 INTCON Registers

The INTCON Registers are readable and writable registers, which contains various enable, priority, and flag bits.

## REGISTER 7-1: INTCON REGISTER

| R/W-0                    | R/W-0                                         | R/W-0         | R/W-0        | R/W-0          | R/W-0      | R/W-0         | R/W-> |

|--------------------------|-----------------------------------------------|---------------|--------------|----------------|------------|---------------|-------|

| GIE/GIEH                 | PEIE/GIEL                                     | TMR0IE        | INT0IE       | RBIE           | TMR0IF     | INTOIF        | RBIF  |

| bit 7                    |                                               |               |              |                |            |               | bit   |

| GIE/GIEH: O<br>When IPEN | Global Interrup<br>= 0:                       | t Enable bit  |              |                |            |               |       |

| 1 = Enables              | all unmasked<br>all interrupts                | interrupts    |              |                |            |               |       |

| 1 = Enables              | all high priorit                              |               |              |                |            |               |       |

|                          | Peripheral Inte                               |               | e bit        |                |            |               |       |

|                          | all unmasked<br>all peripheral<br><u>= 1:</u> |               | terrupts     |                |            |               |       |

|                          | all low priority<br>all low priority          |               |              |                |            |               |       |

| TMROIE: TM               | IR0 Overflow I                                | nterrupt Ena  | ble bit      |                |            |               |       |

|                          | the TMR0 ove<br>the TMR0 ove                  |               | •            |                |            |               |       |

| INTOIE: INTO             | DExternal Inte                                | rrupt Enable  | bit          |                |            |               |       |

|                          | the INT0 extention the INT0 extent            |               |              |                |            |               |       |

| RBIE: RB P               | ort Change Int                                | errupt Enabl  | e bit        |                |            |               |       |

|                          | the RB port cl<br>the RB port c               |               |              |                |            |               |       |

| TMR0IF: TM               | IR0 Overflow I                                | nterrupt Flag | g bit        |                |            |               |       |

|                          | gister has ove<br>gister did not              | •             | st be cleare | ed in softwa   | re)        |               |       |

| INTOIF: INTO             | External Inte                                 | rrupt Flag bi | t            |                |            |               |       |

|                          | 0 external inte<br>0 external inte            | •             | •            | cleared in     | software)  |               |       |

| RBIF: RB Po              | ort Change Int                                | errupt Flag b | oit          |                |            |               |       |

|                          | one of the RB7<br>the RB7:RB4                 |               | 0            | ·              | cleared in | software)     |       |

| Legend:                  |                                               |               |              |                |            |               |       |

| R = Readabl              |                                               | W = Writal    |              | •              |            | t, read as '( |       |

| - n = Value a            | t POR reset                                   | '1' = Bit is  | set          | '0' = Bit is o | cleared    | x = Bit is ur | known |

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit, or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### **REGISTER 7-3:** INTCON3 REGISTER

bit

bit

bit bit

bit

bit bit

bit

| R/W-1                      | R/W-1                                              | U-0                       | R/W-0      | R/W-0        | U-0      | R/W-0        | R/W-0   |

|----------------------------|----------------------------------------------------|---------------------------|------------|--------------|----------|--------------|---------|

| INT2IP                     | INT1IP                                             | —                         | INT2IE     | INT1IE       | —        | INT2IF       | INT1IF  |

| bit 7                      |                                                    |                           |            |              |          |              | bit     |

| INT2IP: IN                 | T2 External Ir                                     | nterrupt Prio             | rity bit   |              |          |              |         |

| 1 = High pr<br>0 = Low pri | •                                                  |                           |            |              |          |              |         |

| INT1IP: IN                 | T1 External Ir                                     | nterrupt Prio             | rity bit   |              |          |              |         |

| 1 = High pr<br>0 = Low pri | iority                                             | ·                         |            |              |          |              |         |

| Unimplem                   | ented: Read                                        | as '0'                    |            |              |          |              |         |

| INT2IE: IN                 | T2 External Ir                                     | nterrupt Ena              | ble bit    |              |          |              |         |

|                            | s the INT2 ex<br>s the INT2 ex                     |                           |            |              |          |              |         |

| INT1IE: IN                 | T1 External Ir                                     | nterrupt Ena              | ble bit    |              |          |              |         |

|                            | s the INT1 ex<br>s the INT1 ex                     |                           |            |              |          |              |         |

| Unimplem                   | ented: Read                                        | as '0'                    |            |              |          |              |         |

| INT2IF: IN                 | T2 External Ir                                     | nterrupt Flag             | bit        |              |          |              |         |

| (must b                    | Γ2 external in<br>e cleared in s<br>Γ2 external in | software)                 |            |              |          |              |         |

| INT1IF: IN                 | T1 External Ir                                     | terrupt Flag              | bit        |              |          |              |         |

| 1 = The IN<br>(must b      | Γ1 external in<br>e cleared in s<br>Γ1 external in | terrupt occu<br>software) | rred       |              |          |              |         |

| Legend:                    |                                                    |                           |            |              |          |              |         |

| R = Reada                  | ble bit                                            | W = Wr                    | itable bit | U = Unimp    | lemented | bit, read as | '0'     |

|                            | at POR reset                                       | t '1' = Bit               | is set     | '0' = Bit is | cleared  | x = Bit is ι | Inknown |

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit, or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

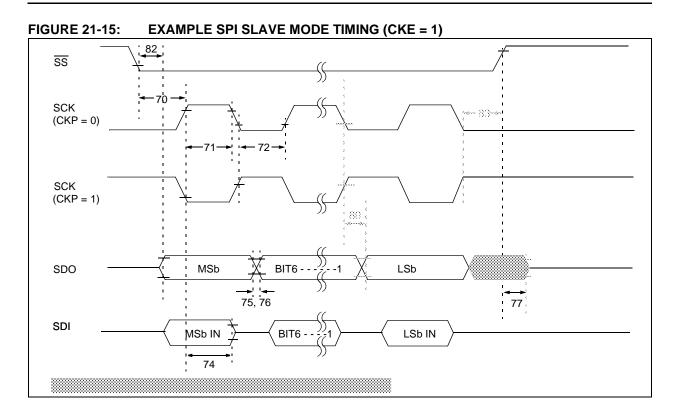

## 14.3 SPI Mode

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL/LVOIN

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) - RA5/SS/AN4

#### 14.3.1 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

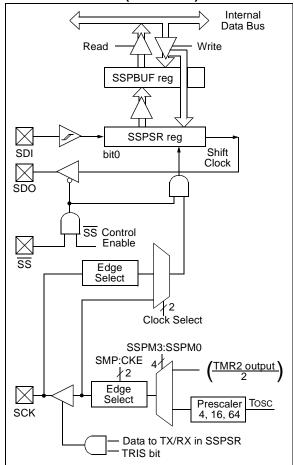

Figure 14-1 shows the block diagram of the MSSP module, when in SPI mode.

## FIGURE 14-1:

#### MSSP BLOCK DIAGRAM (SPI MODE)

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR. until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF, are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit, WCOL (SSPCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

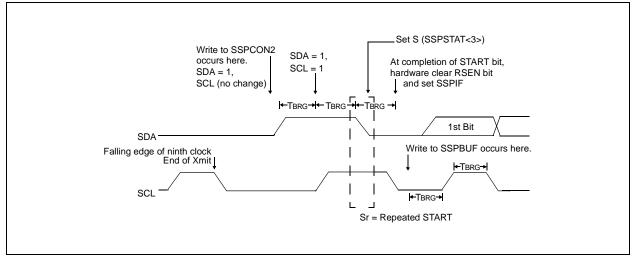

## 14.4.7 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the  $I^2C$ logic module is in the idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (T<sub>BRG</sub>). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG, while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the baud rate generator will not be reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- 2: A bus collision during the Repeated START condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode), or eight bits of data (7-bit mode).

## 14.4.7.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated START sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated START condition is complete.

## FIGURE 14-17: REPEAT START CONDITION WAVEFORM

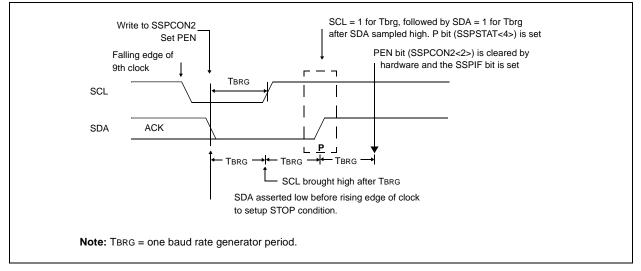

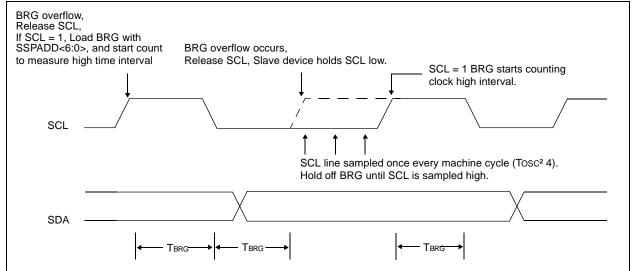

## 14.4.12 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit, or Repeated START/STOP condition, de-asserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 14-22).

## 14.4.13 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs, wake the processor from SLEEP (if the MSSP interrupt is enabled).

#### 14.4.14 EFFECT OF A RESET

A RESET disables the MSSP module and terminates the current transfer.

#### REGISTER 18-3: CONFIGURATION REGISTER 2 HIGH (CONFIG2H: BYTE ADDRESS 300003h)

|    | U-0                                                                                                              | U-0                                                                                    | U-0                                                  | U-0                                             | R/P-1                               | R/P-1        | R/P-1                   | R/P-1             |

|----|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------|-------------------------------------|--------------|-------------------------|-------------------|

|    | —                                                                                                                | _                                                                                      | —                                                    | —                                               | WDTPS2                              | WDTPS1       | WDTPS0                  | WDTEN             |

|    | bit 7                                                                                                            |                                                                                        |                                                      |                                                 |                                     |              |                         | bit 0             |

| 4  | Unimplen                                                                                                         | n <b>ented:</b> Rea                                                                    | d as '0'                                             |                                                 |                                     |              |                         |                   |

| 1  |                                                                                                                  |                                                                                        | /atchdog Tin                                         | ner Postsca                                     | le Select bits                      | ;            |                         |                   |

|    | 111 = 1:1                                                                                                        |                                                                                        |                                                      |                                                 |                                     |              |                         |                   |

|    | 110 = 1:2<br>101 = 1:4                                                                                           |                                                                                        |                                                      |                                                 |                                     |              |                         |                   |

|    | 101 = 1.4<br>100 = 1.8                                                                                           |                                                                                        |                                                      |                                                 |                                     |              |                         |                   |

|    | 011 = 1:10                                                                                                       |                                                                                        |                                                      |                                                 |                                     |              |                         |                   |

|    | 010 = 1:32                                                                                                       | 2                                                                                      |                                                      |                                                 |                                     |              |                         |                   |

|    | 001 = 1:64                                                                                                       | 1                                                                                      |                                                      |                                                 |                                     |              |                         |                   |

|    | 001 - 1.0                                                                                                        | 4                                                                                      |                                                      |                                                 |                                     |              |                         |                   |

|    | 001 = 1.04<br>000 = 1.12                                                                                         |                                                                                        |                                                      |                                                 |                                     |              |                         |                   |

|    | 000 = 1:12<br>WDTEN: \                                                                                           | 28<br>Watchdog Ti                                                                      | mer Enable                                           | bit                                             |                                     |              |                         |                   |

|    | 000 = 1:12<br>WDTEN: V<br>1 = WDT e                                                                              | 28<br>Watchdog Ti<br>enabled                                                           |                                                      |                                                 |                                     |              |                         |                   |

|    | 000 = 1:12<br>WDTEN: V<br>1 = WDT e                                                                              | 28<br>Watchdog Ti                                                                      |                                                      |                                                 | /DTEN bit)                          |              |                         |                   |

|    | 000 = 1:12<br>WDTEN: V<br>1 = WDT e                                                                              | 28<br>Watchdog Ti<br>enabled                                                           |                                                      |                                                 | /DTEN bit)                          |              |                         |                   |

|    | 000 = 1:12<br>WDTEN: V<br>1 = WDT 0<br>0 = WDT 0                                                                 | 28<br>Watchdog Ti<br>enabled<br>disabled (coi                                          | ntrol is place                                       |                                                 |                                     | mplemented   | d bit, read a           | s '0'             |

|    | 000 = 1:12<br><b>WDTEN:</b> V<br>1 = WDT (<br>0 = WDT (<br>Legend:<br>R = Reada                                  | 28<br>Watchdog Ti<br>enabled<br>disabled (coi                                          | ntrol is place<br>P = Progr                          | d on the SW                                     | it U = Uni                          | •            | d bit, read a           |                   |

|    | 000 = 1:12<br><b>WDTEN:</b> V<br>1 = WDT (<br>0 = WDT (<br>Legend:<br>R = Reada                                  | 28<br>Watchdog Ti<br>enabled<br>disabled (coi<br>able bit                              | ntrol is place<br>P = Progr                          | d on the SW                                     | it U = Uni                          | •            |                         |                   |

| ł: | 000 = 1:12<br><b>WDTEN:</b> V<br>1 = WDT e<br>0 = WDT e<br>Legend:<br>R = Reada<br>- n = Value                   | 28<br>Watchdog Ti<br>enabled<br>disabled (cor<br>able bit<br>e when devic              | ntrol is place<br>P = Progr<br>ce is unprogr         | d on the SW<br>rammable b<br>ammed              | it U = Uni                          | changed fror | m programm              | ned state         |

| ŀ: | 000 = 1:12<br><b>WDTEN:</b> V<br>1 = WDT e<br>0 = WDT e<br>Legend:<br>R = Reada<br>- n = Value                   | 28<br>Watchdog Ti<br>enabled<br>disabled (cor<br>able bit<br>e when devic              | ntrol is place<br>P = Progr<br>ce is unprogr         | d on the SW<br>rammable b<br>ammed              | it U = Uni<br>u = Unc               | changed fror | m programm              | ned state         |

| :  | 000 = 1:12<br><b>WDTEN:</b> V<br>1 = WDT 6<br>0 = WDT 6<br>Legend:<br>R = Reada<br>- n = Value<br><b>CONFIGU</b> | 28<br>Watchdog Ti<br>enabled<br>disabled (cor<br>able bit<br>e when devic<br>JRATION R | P = Progr<br>P = Progr<br>se is unprogr<br>EGISTER 2 | d on the SW<br>rammable b<br>ammed<br>2 LOW (CC | it U = Uni<br>u = Unc<br>DNFIG2L: B | changed from | m programm<br>RESS 3000 | ned state<br>02h) |

- bit 7-4 Unimplemented: Read as '0'

- bit 3-2 **BORV1:BORV0:** Brown-out Reset Voltage bits

- 11 = VBOR set to 2.5V10 = VBOR set to 2.7V

- 01 = VBOR set to 4.2V

- 00 = VBOR set to 4.5V

- bit 1 BOREN: Brown-out Reset Enable bit<sup>(1)</sup>

- 1 = Brown-out Reset enabled

- 0 = Brown-out Reset disabled

- **Note:** Enabling Brown-out Reset <u>automatically</u> enables the Power-up Timer (PWRT), regardless of the value of bit PWRTEN. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.

- bit 0 **PWRTEN:** Power-up Timer Enable bit<sup>(1)</sup>

- 1 = PWRT disabled

- 0 = PWRT enabled

- **Note:** Enabling Brown-out Reset automatically enables the Power-up Timer (PWRT), regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.

| Legend:                 |                      |                                     |

|-------------------------|----------------------|-------------------------------------|

| R = Readable bit        | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when device | e is unprogrammed    | u = Unchanged from programmed state |

REGISTER

## 18.2 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO/RA6 pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the RCON register will be cleared upon a WDT time-out.

The Watchdog Timer is enabled/disabled by a device configuration bit. If the WDT is enabled, software execution may not disable this function. When the WDTEN configuration bit is cleared, the SWDTEN bit enables/ disables the operation of the WDT. The WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT postscaler may be assigned using the configuration bits.

**Note:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

**Note:** When a CLRWDT instruction is executed and the postscaler is assigned to the WDT, the postscaler count will be cleared, but the postscaler assignment is not changed.

## 18.2.1 CONTROL REGISTER

Register 18-7 shows the WDTCON register. This is a readable and writable register, which contains a control bit that allows software to override the WDT enable configuration bit, only when the configuration bit has disabled the WDT.

## **REGISTER 18-7: WDTCON REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

|       | —   | —   | —   | —   | —   | _   | SWDTEN |

| bit 7 |     |     |     |     |     |     | bit 0  |

#### bit 7-1 Unimplemented: Read as '0'

- bit 0 SWDTEN: Software Controlled Watchdog Timer Enable bit

- 1 = Watchdog Timer is on

- Watchdog Timer is turned off if the WDTEN configuration bit in the configuration register = '0'

| Legend:                            |                          |

|------------------------------------|--------------------------|

| R = Readable bit                   | W = Writable bit         |

| U = Unimplemented bit, read as '0' | - n = Value at POR Reset |

# PIC18CXX2

| BCF                                                                                       | Bit Clear f                                                                                                                                                                                            |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                                   | [ <i>label</i> ] BCF f,b[,a]                                                                                                                                                                           |  |  |  |  |  |

| Operands:                                                                                 | 0 ≤ f ≤ 255<br>0 ≤ b ≤ 7<br>a ∈ [0,1]                                                                                                                                                                  |  |  |  |  |  |

| Operation:                                                                                | $0 \rightarrow f < b >$                                                                                                                                                                                |  |  |  |  |  |

| Status Affected:                                                                          | None                                                                                                                                                                                                   |  |  |  |  |  |

| Encoding:                                                                                 | 1001 bbba ffff ffff                                                                                                                                                                                    |  |  |  |  |  |

| Description:                                                                              | Bit 'b' in register 'f' is cleared. If 'a'<br>is 0, the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default). |  |  |  |  |  |

| Words:                                                                                    | 1                                                                                                                                                                                                      |  |  |  |  |  |

| Cycles:                                                                                   | 1                                                                                                                                                                                                      |  |  |  |  |  |

| Q Cycle Activity                                                                          | :                                                                                                                                                                                                      |  |  |  |  |  |

| Q1                                                                                        | Q2 Q3 Q4                                                                                                                                                                                               |  |  |  |  |  |

| Decode                                                                                    | Read         Process         Write           register 'f'         Data         register 'f'                                                                                                            |  |  |  |  |  |

| Example: BCF FLAG_REG, 7, 0<br>Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction |                                                                                                                                                                                                        |  |  |  |  |  |

| /                                                                                         | After Instruction<br>FLAG_REG = 0x47                                                                                                                                                                   |  |  |  |  |  |

| BN                          | Branch if                                                         | Negative                                                                                  |                                                              |  |  |  |

|-----------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|

| Syntax:                     | [ <i>label</i> ] B                                                | [ <i>label</i> ] BN n                                                                     |                                                              |  |  |  |

| Operands:                   | -128 ≤ n ≤                                                        | 127                                                                                       |                                                              |  |  |  |

| Operation:                  | •                                                                 | if negative bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                                  |                                                              |  |  |  |

| Status Affected             | : None                                                            |                                                                                           |                                                              |  |  |  |

| Encoding:                   | 1110                                                              | 0110 nn:                                                                                  | nn nnnn                                                      |  |  |  |

|                             | The 2's co<br>added to t<br>have incre<br>instruction<br>PC+2+2n. | vill branch.<br>Implement n<br>he PC. Sincemented to fe<br>the new ad<br>This instruction | e the PC w<br>etch the new<br>Idress will b<br>ction is ther |  |  |  |

| Words:                      | 1                                                                 |                                                                                           |                                                              |  |  |  |

| Cycles:                     | 1(2)                                                              |                                                                                           |                                                              |  |  |  |

| Q Cycle Activit<br>If Jump: | ty:                                                               |                                                                                           |                                                              |  |  |  |

| Q1                          | Q2                                                                | Q3                                                                                        | Q4                                                           |  |  |  |

| Decode                      | Read literal<br>'n'                                               | Process<br>Data                                                                           | Write to PC                                                  |  |  |  |

| No                          | No                                                                | No                                                                                        | No                                                           |  |  |  |

| operation                   | operation                                                         | operation                                                                                 | operation                                                    |  |  |  |

| If No Jump:                 |                                                                   |                                                                                           |                                                              |  |  |  |

| Q1                          | Q2                                                                | Q3                                                                                        | Q4                                                           |  |  |  |

| Decode                      | Read literal<br>'n'                                               | Process<br>Data                                                                           | No<br>operation                                              |  |  |  |

| L                           | •                                                                 |                                                                                           |                                                              |  |  |  |

| Example:                    | HERE                                                              | BN Jump                                                                                   |                                                              |  |  |  |

| Before Inst                 | truction                                                          |                                                                                           |                                                              |  |  |  |

| DC                          | -                                                                 | drees (UFD                                                                                | - )                                                          |  |  |  |

| PC       |                | =        | address       | (HERE)   |

|----------|----------------|----------|---------------|----------|

| After In | struction      |          |               |          |

| If       | Negative<br>PC | = =      | 1;<br>address | (ປາມຫາວ) |

| If       | Negative<br>PC | e =<br>= | 0;            | (HERE+2) |

| тзт                                                                                                                         | TSTFSZ Test f, skip if 0 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                |    |                |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------|--|--|--|

| Synt                                                                                                                        | ax:                      | [label] T                                                                                      | STFSZ f[,                                                                                                                                                                                                                                                                                                                                      | a] |                |  |  |  |

| Ope                                                                                                                         | rands:                   |                                                                                                | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                                                                            |    |                |  |  |  |

|                                                                                                                             |                          | a ∈ [0,1]                                                                                      | a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                      |    |                |  |  |  |

| Ope                                                                                                                         | ration:                  | skip if f = 0                                                                                  | )                                                                                                                                                                                                                                                                                                                                              |    |                |  |  |  |

| Statu                                                                                                                       | us Affected:             | None                                                                                           | None                                                                                                                                                                                                                                                                                                                                           |    |                |  |  |  |

| Enco                                                                                                                        | oding:                   | 0110                                                                                           | 011a ff                                                                                                                                                                                                                                                                                                                                        | ff | ffff           |  |  |  |

| Desc                                                                                                                        | cription:                | fetched du<br>tion execu<br>NOP is exe<br>cycle instr<br>Access Ba<br>riding the<br>then the b | If 'f' = 0, the next instruction,<br>fetched during the current instruc-<br>tion execution, is discarded and a<br>NOP is executed, making this a two-<br>cycle instruction. If 'a' is 0, the<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' is 1,<br>then the bank will be selected as<br>per the BSR value (default). |    |                |  |  |  |

| Words: 1                                                                                                                    |                          |                                                                                                |                                                                                                                                                                                                                                                                                                                                                |    |                |  |  |  |

| Cycl                                                                                                                        | es:                      |                                                                                                | 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction.                                                                                                                                                                                                                                                                        |    |                |  |  |  |

| QC                                                                                                                          | ycle Activity:           |                                                                                                |                                                                                                                                                                                                                                                                                                                                                |    |                |  |  |  |

|                                                                                                                             | Q1                       | Q2                                                                                             | Q3                                                                                                                                                                                                                                                                                                                                             |    | Q4             |  |  |  |

|                                                                                                                             | Decode                   | Read                                                                                           | Process                                                                                                                                                                                                                                                                                                                                        |    | No             |  |  |  |

| lf sk                                                                                                                       | rin:                     | register 'f'                                                                                   | Data                                                                                                                                                                                                                                                                                                                                           | op | peration       |  |  |  |

| 11 51                                                                                                                       | ωρ.<br>Q1                | Q2                                                                                             | Q3                                                                                                                                                                                                                                                                                                                                             |    | Q4             |  |  |  |

| 1                                                                                                                           | No                       | No                                                                                             | No                                                                                                                                                                                                                                                                                                                                             |    | No             |  |  |  |

|                                                                                                                             | operation                | operation                                                                                      | operation                                                                                                                                                                                                                                                                                                                                      | op | peration       |  |  |  |

| lf sk                                                                                                                       | ip and follow            | ed by 2-wor                                                                                    | d instructior                                                                                                                                                                                                                                                                                                                                  | :  |                |  |  |  |

| 1                                                                                                                           | Q1                       | Q2                                                                                             | Q3                                                                                                                                                                                                                                                                                                                                             | 1  | Q4             |  |  |  |

|                                                                                                                             | No                       | No                                                                                             | No                                                                                                                                                                                                                                                                                                                                             |    | No             |  |  |  |

|                                                                                                                             | operation<br>No          | operation<br>No                                                                                | operation<br>No                                                                                                                                                                                                                                                                                                                                | ot | beration<br>No |  |  |  |

|                                                                                                                             | operation                | operation                                                                                      | operation                                                                                                                                                                                                                                                                                                                                      | op | peration       |  |  |  |

| Example: HERE TSTFSZ CNT, 1<br>NZERO :<br>ZERO :                                                                            |                          |                                                                                                |                                                                                                                                                                                                                                                                                                                                                |    |                |  |  |  |

| Before Instruction<br>PC = Address(HERE)                                                                                    |                          |                                                                                                |                                                                                                                                                                                                                                                                                                                                                |    |                |  |  |  |

|                                                                                                                             | After Instruct           | ion                                                                                            |                                                                                                                                                                                                                                                                                                                                                |    |                |  |  |  |

| After Instruction<br>If CNT = $0 \times 00$ ,<br>PC = Address (ZERO)<br>If CNT $\neq 0 \times 00$ ,<br>PC = Address (NZERO) |                          |                                                                                                |                                                                                                                                                                                                                                                                                                                                                |    |                |  |  |  |

| XOR               | RLW          | Exclusiv            | Exclusive OR literal with WREG                                                                 |                   |                  |  |  |  |  |

|-------------------|--------------|---------------------|------------------------------------------------------------------------------------------------|-------------------|------------------|--|--|--|--|

| Synt              | ax:          | [ <i>label</i> ] ]  | [label] XORLW k                                                                                |                   |                  |  |  |  |  |

| Ope               | rands:       | $0 \le k \le 2$     | 55                                                                                             |                   |                  |  |  |  |  |

| Ope               | ration:      | (WREG)              | .XOR. k                                                                                        | $\rightarrow$ WRE | G                |  |  |  |  |

| Statu             | us Affected: | d: N,Z              |                                                                                                |                   |                  |  |  |  |  |

| Enco              | oding:       | 0000                | 0000 1010 kkkk kkkk                                                                            |                   |                  |  |  |  |  |

| Des               | cription:    | XORed v             | The contents of WREG are<br>XORed with the 8-bit literal 'k'.<br>The result is placed in WREG. |                   |                  |  |  |  |  |

| Wor               | ds:          | 1                   |                                                                                                |                   |                  |  |  |  |  |

| Cycl              | es:          | 1                   | 1                                                                                              |                   |                  |  |  |  |  |

| Q Cycle Activity: |              |                     |                                                                                                |                   |                  |  |  |  |  |

|                   | Q1           | Q2                  | Q3                                                                                             |                   | Q4               |  |  |  |  |

|                   | Decode       | Read<br>literal 'k' | Proce:<br>Data                                                                                 |                   | Vrite to<br>VREG |  |  |  |  |

|                   |              |                     |                                                                                                |                   |                  |  |  |  |  |

Example:

XORLW 0xAF

Before Instruction WREG = 0xB5 After Instruction WREG = 0x1A

|               |        |                                                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +40^{\circ}C$ |                        |      |                                                       |       |              |  |  |

|---------------|--------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------|------|-------------------------------------------------------|-------|--------------|--|--|