Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

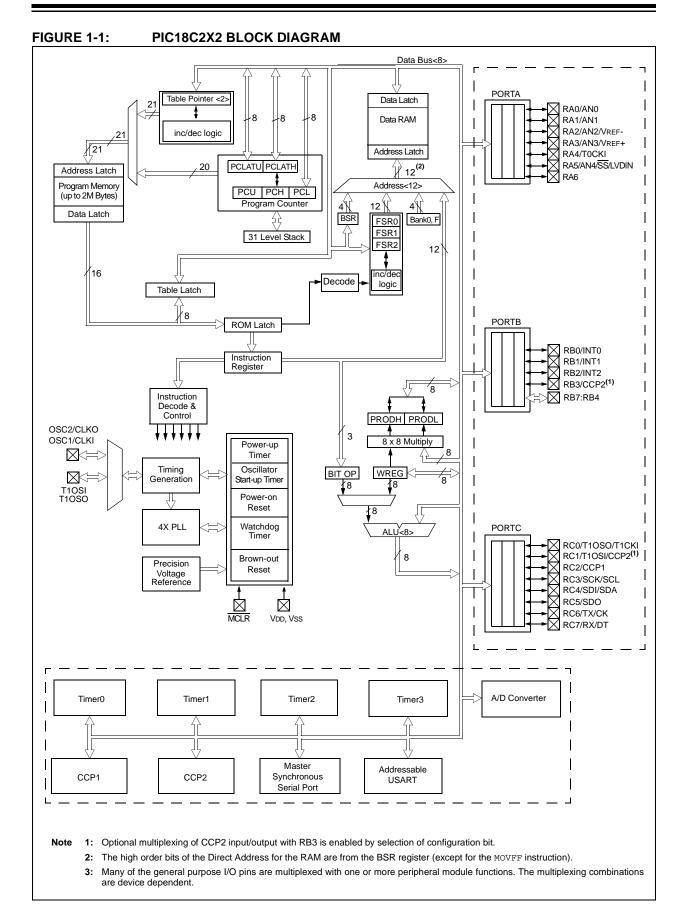

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

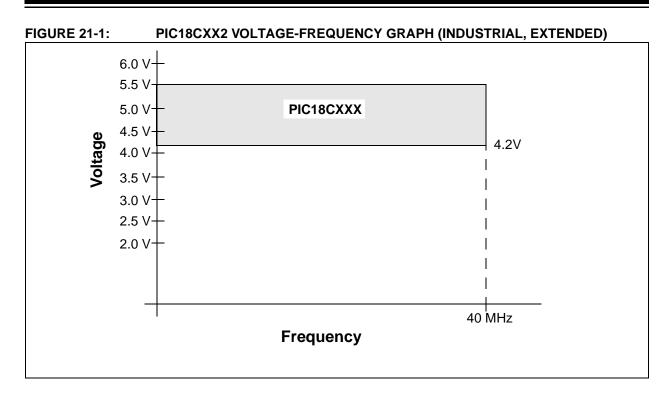

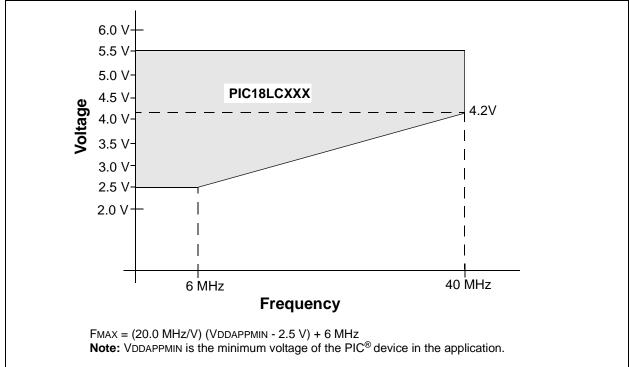

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

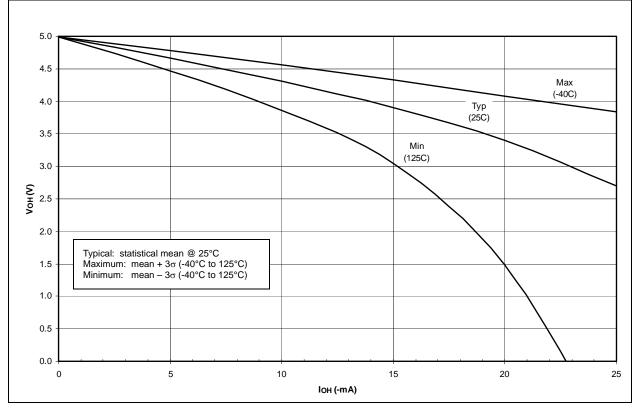

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c442t-e-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register | Арр | Applicable Devices |     | Applicable Devices Power-on Reset,<br>Brown-out Reset RESET Instruction<br>Stack Resets |           | WDT Reset<br>RESET Instruction | Wake-up via WDT<br>or Interrupt |  |

|----------|-----|--------------------|-----|-----------------------------------------------------------------------------------------|-----------|--------------------------------|---------------------------------|--|

| TOSU     | 242 | 442                | 252 | 452                                                                                     | 0 0000    | 0 0000                         | 0 uuuu <b>(3)</b>               |  |

| TOSH     | 242 | 442                | 252 | 452                                                                                     | 0000 0000 | 0000 0000                      | uuuu uuuu <b>(3)</b>            |  |

| TOSL     | 242 | 442                | 252 | 452                                                                                     | 0000 0000 | 0000 0000                      | uuuu uuuu <b>(3)</b>            |  |

| STKPTR   | 242 | 442                | 252 | 452                                                                                     | 00-0 0000 | 00-0 0000                      | uu-u uuuu <b>(3)</b>            |  |

| PCLATU   | 242 | 442                | 252 | 452                                                                                     | 0 0000    | 0 0000                         | u uuuu                          |  |

| PCLATH   | 242 | 442                | 252 | 452                                                                                     | 0000 0000 | 0000 0000                      | uuuu uuuu                       |  |

| PCL      | 242 | 442                | 252 | 452                                                                                     | 0000 0000 | 0000 0000                      | PC + 2 <sup>(2)</sup>           |  |

| TBLPTRU  | 242 | 442                | 252 | 452                                                                                     | 00 0000   | 00 0000                        | uu uuuu                         |  |

| TBLPTRH  | 242 | 442                | 252 | 452                                                                                     | 0000 0000 | 0000 0000                      | սսսս սսսս                       |  |

| TBLPTRL  | 242 | 442                | 252 | 452                                                                                     | 0000 0000 | 0000 0000                      | uuuu uuuu                       |  |

| TABLAT   | 242 | 442                | 252 | 452                                                                                     | 0000 0000 | 0000 0000                      | uuuu uuuu                       |  |

| PRODH    | 242 | 442                | 252 | 452                                                                                     | xxxx xxxx | uuuu uuuu                      | uuuu uuuu                       |  |

| PRODL    | 242 | 442                | 252 | 452                                                                                     | xxxx xxxx | uuuu uuuu                      | uuuu uuuu                       |  |

| INTCON   | 242 | 442                | 252 | 452                                                                                     | 0000 000x | 0000 000u                      | uuuu uuuu <b>(1)</b>            |  |

| INTCON2  | 242 | 442                | 252 | 452                                                                                     | 1111 -1-1 | 1111 -1-1                      | uuuu -u-u <b>(1)</b>            |  |

| INTCON3  | 242 | 442                | 252 | 452                                                                                     | 11-0 0-00 | 11-0 0-00                      | uu-u u-uu <b>(1)</b>            |  |

| INDF0    | 242 | 442                | 252 | 452                                                                                     | N/A       | N/A                            | N/A                             |  |

| POSTINC0 | 242 | 442                | 252 | 452                                                                                     | N/A       | N/A                            | N/A                             |  |

| POSTDEC0 | 242 | 442                | 252 | 452                                                                                     | N/A       | N/A                            | N/A                             |  |

| PREINC0  | 242 | 442                | 252 | 452                                                                                     | N/A       | N/A                            | N/A                             |  |

| PLUSW0   | 242 | 442                | 252 | 452                                                                                     | N/A       | N/A                            | N/A                             |  |

| FSR0H    | 242 | 442                | 252 | 452                                                                                     | 0000      | 0000                           | uuuu                            |  |

| FSR0L    | 242 | 442                | 252 | 452                                                                                     | XXXX XXXX | uuuu uuuu                      | սսսս սսսս                       |  |

| WREG     | 242 | 442                | 252 | 452                                                                                     | XXXX XXXX | uuuu uuuu                      | սսսս սսսս                       |  |

| INDF1    | 242 | 442                | 252 | 452                                                                                     | N/A       | N/A                            | N/A                             |  |

| POSTINC1 | 242 | 442                | 252 | 452                                                                                     | N/A       | N/A                            | N/A                             |  |

| POSTDEC1 | 242 | 442                | 252 | 452                                                                                     | N/A       | N/A                            | N/A                             |  |

| PREINC1  | 242 | 442                | 252 | 452                                                                                     | N/A       | N/A                            | N/A                             |  |

| PLUSW1   | 242 | 442                | 252 | 452                                                                                     | N/A       | N/A                            | N/A                             |  |

#### TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

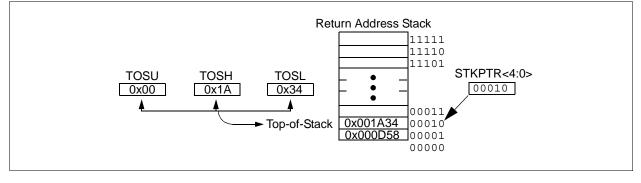

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 3-2 for RESET value for specific condition.

- 5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

- 6: The long write enable is only reset on a POR or MCLR Reset.

- 7: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read as '0'.

### REGISTER 4-1: STKPTR REGISTER

|                      | R/C-0                             | R/C-0          | U-0           | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|-----------------------------------|----------------|---------------|-----------|-------|-------|-------|-------|

|                      | STKFUL                            | STKUNF         | —             | SP4       | SP3   | SP2   | SP1   | SP0   |

|                      | bit 7                             |                |               |           |       |       |       | bit 0 |

|                      |                                   |                |               |           |       |       |       |       |

| bit 7 <sup>(1)</sup> | STKFUL: S                         | Stack Full Fla | ag bit        |           |       |       |       |       |

|                      | 1 = Stack b                       | ecame full c   | or overflowed | d         |       |       |       |       |

|                      | 0 = Stack h                       | as not beco    | me full or ov | verflowed |       |       |       |       |

| bit 6 <sup>(1)</sup> | STKUNF: S                         | Stack Underf   | low Flag bit  |           |       |       |       |       |

|                      | 1 = Stack u                       | inderflow oc   | curred        |           |       |       |       |       |

|                      | 0 = Stack underflow did not occur |                |               |           |       |       |       |       |

| bit 5                | Unimplemented: Read as '0'        |                |               |           |       |       |       |       |

| bit 4-0              | SP4:SP0: S                        | Stack Pointe   | r Location b  | its       |       |       |       |       |

|                      |                                   |                |               |           |       |       |       |       |

|                      |                                   |                |               |           |       |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### FIGURE 4-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

### 4.2.3 PUSH AND POP INSTRUCTIONS

Since the Top-of-Stack (TOS) is readable and writable, the ability to push values onto the stack and pull values off the stack, without disturbing normal program execution, is a desirable option. To push the current PC value onto the stack, a PUSH instruction can be executed. This will increment the stack pointer and load the current PC value onto the stack. TOSU, TOSH and TOSL can then be modified to place a return address on the stack.

The ability to pull the TOS value off of the stack and replace it with the value that was previously pushed onto the stack, without disturbing normal execution, is achieved by using the POP instruction. The POP instruction discards the current TOS by decrementing the stack pointer. The previous value pushed onto the stack then becomes the TOS value.

### 4.2.4 STACK FULL/UNDERFLOW RESETS

These resets are enabled by programming the STVREN configuration bit. When the STVREN bit is disabled, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a device RESET. When the STVREN bit is enabled, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device RESET. The STKFUL or STKUNF bits are only cleared by the user software or a POR Reset.

#### 4.10 Access Bank

The Access Bank is an architectural enhancement, which is very useful for C compiler code optimization. The techniques used by the C compiler may also be useful for programs written in assembly.

This data memory region can be used for:

- Intermediate computational values

- · Local variables of subroutines

- Faster context saving/switching of variables

- Common variables

- Faster evaluation/control of SFRs (no banking)

The Access Bank is comprised of the upper 128 bytes in Bank 15 (SFRs) and the lower 128 bytes in Bank 0. These two sections will be referred to as Access RAM High and Access RAM Low, respectively. Figure 4-6 and Figure 4-7 indicate the Access RAM areas.

A bit in the instruction word specifies if the operation is to occur in the bank specified by the BSR register or in the Access Bank. This bit is denoted by the 'a' bit (for access bit).

When forced in the Access Bank (a = '0'), the last address in Access RAM Low is followed by the first address in Access RAM High. Access RAM High maps the Special Function registers, so that these registers can be accessed without any software overhead. This is useful for testing status flags and modifying control bits.

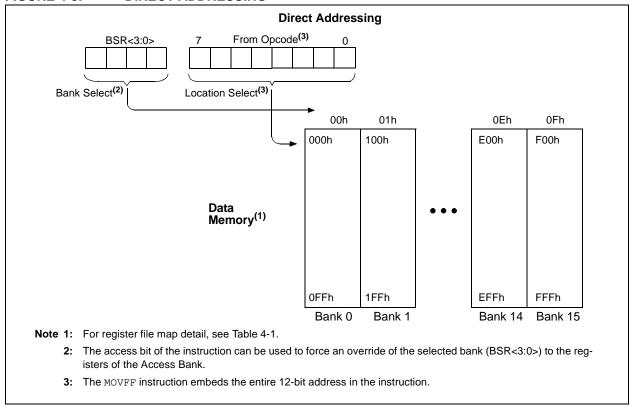

#### 4.11 Bank Select Register (BSR)

The need for a large general purpose memory space dictates a RAM banking scheme. The data memory is partitioned into sixteen banks. When using direct addressing, the BSR should be configured for the desired bank.

BSR<3:0> holds the upper 4 bits of the 12-bit RAM address. The BSR<7:4> bits will always read '0's, and writes will have no effect.

A MOVLB instruction has been provided in the instruction set to assist in selecting banks.

If the currently selected bank is not implemented, any read will return all '0's and all writes are ignored. The STATUS register bits will be set/cleared as appropriate for the instruction performed.

Each Bank extends up to FFh (256 bytes). All data memory is implemented as static RAM.

A MOVFF instruction ignores the BSR, since the 12-bit addresses are embedded into the instruction word.

Section 4.12 provides a description of indirect addressing, which allows linear addressing of the entire RAM space.

#### FIGURE 4-8: DIRECT ADDRESSING

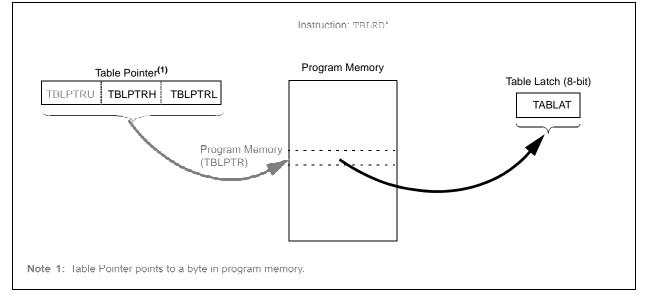

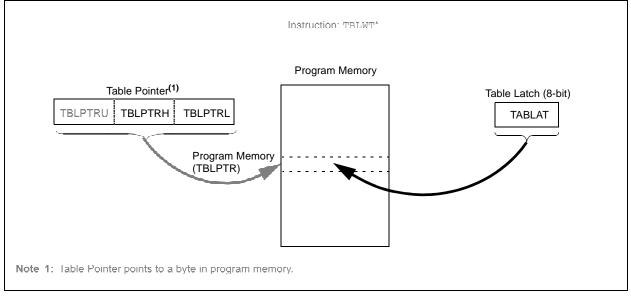

### 5.0 TABLE READS/TABLE WRITES

Enhanced devices have two memory spaces: the program memory space and the data memory space. The program memory space is 16-bits wide, while the data memory space is 8 bits wide. Table Reads and Table Writes have been provided to move data between these two memory spaces through an 8-bit register (TABLAT).

The operations that allow the processor to move data between the data and program memory spaces are:

- Table Read (TBLRD)

- Table Write (TBLWT)

Table Read operations retrieve data from program memory and place it into the data memory space. Figure 5-1 shows the operation of a Table Read with program and data memory.

Table Write operations store data from the data memory space into program memory. Figure 5-2 shows the operation of a Table Write with program and data memory.

Table operations work with byte entities. A table block containing data is not required to be word aligned, so a table block can start and end at any byte address. If a Table Write is being used to write an executable program to program memory, program instructions will need to be word aligned.

### FIGURE 5-2: TABLE WRITE OPERATION

### FIGURE 5-1: TABLE READ OPERATION

### 5.1 Control Registers

Several control registers are used in conjunction with the  ${\tt TBLRD}$  and  ${\tt TBLWT}$  instructions. These include the:

- TBLPTR registers

- TABLAT register

- RCON register

#### 5.1.1 RCON REGISTER

The LWRT bit specifies the operation of Table Writes to internal memory when the VPP voltage is applied to the MCLR pin. When the LWRT bit is set, the controller continues to execute user code, but long Table Writes are allowed (for programming internal program memory) from user mode. The LWRT bit can be cleared only by performing either a POR or MCLR Reset.

#### REGISTER 5-1: RCON REGISTER (ADDRESS: FD0h)

| R/W-0 | R/W-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-0 | R/W-0 |

|-------|-------|-----|-------|-------|-------|-------|-------|

| IPEN  | LWRT  | —   | RI    | TO    | PD    | POR   | BOR   |

| bit 7 |       |     |       |       |       |       | bit 0 |

|  | bit 7 | <b>IPEN:</b> | Interrupt | Prioritv | Enable bit |

|--|-------|--------------|-----------|----------|------------|

|--|-------|--------------|-----------|----------|------------|

- 1 = Enable priority levels on interrupts

- 0 = Disable priority levels on interrupts (16CXXX compatibility mode)

- bit 6 LWRT: Long Write Enable bit

- 1 = Enable TBLWT to internal program memory

- 0 = Disable TBLWT to internal program memory.

- Note:Only cleared on a POR or MCLR Reset.This bit has no effect on TBLWTs to external program memory.

- bit 5 Unimplemented: Read as '0'

- bit 4 RI: RESET Instruction Flag bit

- 1 = No RESET instruction occurred

- 0 = A RESET instruction occurred

- bit 3 TO: Time-out bit

- 1 = After power-up, CLRWDT instruction, or SLEEP instruction

- 0 = A WDT time-out occurred

- bit 2 **PD:** Power-down bit

- 1 = After power-up or by the CLRWDT instruction

- 0 = By execution of the SLEEP instruction

- bit 1 POR: Power-on Reset Status bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 BOR: Brown-out Reset Status bit

- 1 = No Brown-out Reset or POR Reset occurred

- 0 = A Brown-out Reset or POR Reset occurred

- (must be set in software after a Brown-out Reset occurs)

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### TABLE 8-1: PORTA FUNCTIONS

| Name             | Bit# | Buffer | Function                                                                                                     |

|------------------|------|--------|--------------------------------------------------------------------------------------------------------------|

| RA0/AN0          | bit0 | TTL    | Input/output or analog input.                                                                                |

| RA1/AN1          | bit1 | TTL    | Input/output or analog input.                                                                                |

| RA2/AN2/VREF-    | bit2 | TTL    | Input/output or analog input or VREF                                                                         |

| RA3/AN3/VREF+    | bit3 | TTL    | Input/output or analog input or VREF+.                                                                       |

| RA4/T0CKI        | bit4 | ST     | Input/output or external clock input for Timer0.<br>Output is open drain type.                               |

| RA5/SS/AN4/LVDIN | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input, or low voltage detect input. |

| OSC2/CLKO/RA6    | bit6 | TTL    | OSC2 or clock output or I/O pin.                                                                             |

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 8-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7 | Bit 6   | Bit 5                          | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0   | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|-------|---------|--------------------------------|-------|-------|-------|-------|---------|-------------------------|---------------------------------|

| PORTA  | —     | RA6     | RA5                            | RA4   | RA3   | RA2   | RA1   | RA0     | 0x 0000                 | 0u 0000                         |

| LATA   |       | Latch A | _atch A Data Output Registeruu |       |       |       |       |         | uu uuuu                 |                                 |

| TRISA  |       | PORTA   | PORTA Data Direction Register1 |       |       |       |       | 11 1111 | 11 1111                 |                                 |

| ADCON1 | ADFM  | ADCS2   | —                              | —     | PCFG3 | PCFG2 | PCFG1 | PCFG0   | 0- 0000                 | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

$\ensuremath{\textcircled{}^\circ}$  1999-2013 Microchip Technology Inc.

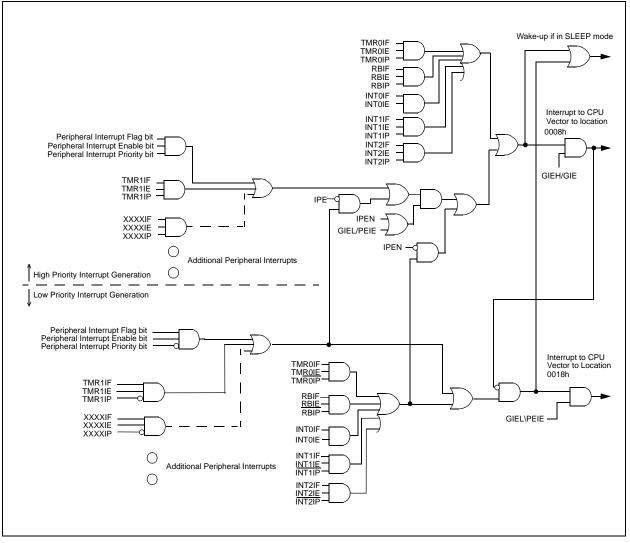

### 8.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bi-directional port. The corresponding Data Direction Register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

| Note: | On a Power-on Reset, these pins are con- |

|-------|------------------------------------------|

|       | figured as digital inputs.               |

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register reads and writes the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 8-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings. The pin override value is not loaded into the TRIS register. This allows read-modify-write of the TRIS register, without concern due to peripheral overrides.

RC1 is normally configured by the configuration bit CCP2MX as the default peripheral pin for the CCP2 module (default/erased state, CCP2MX = '1').

| EXAMPLE 0-3: INITIALIZING PURIC | XAMPLE 8-3: | INITIALIZING PORTC |

|---------------------------------|-------------|--------------------|

|---------------------------------|-------------|--------------------|

| CLRF  | PORTC | ; Initialize PORTC by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATC  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0xCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISC | ; Set RC<3:0> as inputs |

|       |       | ; RC<5:4> as outputs    |

|       |       | ; RC<7:6> as inputs     |

|       |       |                         |

### FIGURE 8-7: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

**3:** Peripheral Output Enable is only active if peripheral select is active.

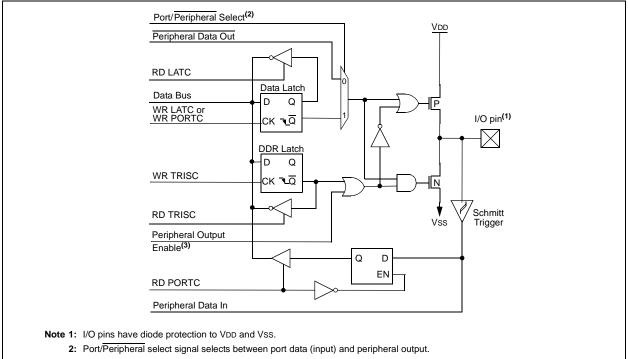

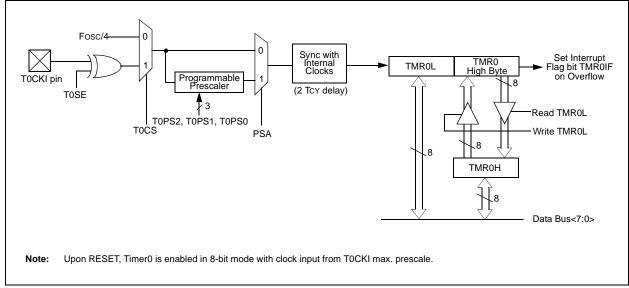

### FIGURE 9-1: TIMER0 BLOCK DIAGRAM IN 8-BIT MODE

NOTES:

### REGISTER 18-5: CONFIGURATION REGISTER 3 HIGH (CONFIG3H: BYTE ADDRESS 300005h)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/P-1  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| —     | —   |     | —   | —   | —   |     | CCP2MX |

| bit 7 |     |     |     |     |     |     | bit 0  |

bit 7-1 Unimplemented: Read as '0'

bit 0 CCP2MX: CCP2 Mux bit

- 1 = CCP2 input/output is multiplexed with RC1

- 0 = CCP2 input/output is multiplexed with RB3

| Legend:               |                      |                                     |

|-----------------------|----------------------|-------------------------------------|

| R = Readable bit      | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when devi | ce is unprogrammed   | u = Unchanged from programmed state |

#### REGISTER 18-6: CONFIGURATION REGISTER 4 LOW (CONFIG4L: BYTE ADDRESS 300006h)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/P-1    | R/P-1  |

|-------|-----|-----|-----|-----|-----|----------|--------|

|       | _   | _   |     | _   |     | Reserved | STVREN |

| bit 7 |     |     |     |     |     |          | bit 0  |

- bit 7-2 Unimplemented: Read as '0'

- bit 1 Reserved: Maintain this bit set

- bit 0 STVREN: Stack Full/Underflow Reset Enable bit

- 1 = Stack Full/Underflow will cause RESET

- 0 = Stack Full/Underflow will not cause RESET

| Legend:              |                      |                                     |

|----------------------|----------------------|-------------------------------------|

| R = Readable bit     | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when dev | ice is unprogrammed  | u = Unchanged from programmed state |

| MOVFF                                                | Move f to                                                                                                                                                                                                                                                                       | o f          |              |                                        |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|----------------------------------------|

| Syntax:                                              | [label]                                                                                                                                                                                                                                                                         | MOVFF        | $f_s, f_d$   |                                        |

| Operands:                                            | $\begin{array}{l} 0 \leq f_s \leq 4 \\ 0 \leq f_d \leq 4 \end{array}$                                                                                                                                                                                                           |              |              |                                        |

| Operation:                                           | $(f_{S}) \to f_{d}$                                                                                                                                                                                                                                                             |              |              |                                        |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                            |              |              |                                        |

| Encoding:<br>1st word (source)<br>2nd word (destin.) | 1100<br>1111                                                                                                                                                                                                                                                                    | ffff<br>ffff | ffff<br>ffff | ffff <sub>s</sub><br>ffff <sub>d</sub> |

| Description:                                         | The contents of source register ${}^{'}f_{s}{}^{'}$ are moved to destination register ${}^{'}f_{d}{}^{'}$ . Location of source ${}^{'}f_{s}{}^{'}$ can be anywhere in the 4096 byte data space (000h to FFFh), and location of destination ${}^{'}f_{d}{}^{'}$ can also be any- |              |              |                                        |

where from 000h to FFFh. Either source or destination can be WREG (a useful special situation). MOVFF is particularly useful for transferring a data memory location to a peripheral register (such as the transmit buffer or an I/O port).

The MOVFF instruction cannot use the PCL, TOSU, TOSH or TOSL as the destination register.

Words:

Cycles:

Q Cycle Activity:

Q1

| Q1     | Q2                                  | Q3              | Q4                              |

|--------|-------------------------------------|-----------------|---------------------------------|

| Decode | Read<br>register 'f'<br>(src)       | Process<br>Data | No<br>operation                 |

| Decode | No<br>operation<br>No dummy<br>read | No<br>operation | Write<br>register 'f'<br>(dest) |

#### Example:

MOVFF REG1, REG2

#### **Before Instruction**

| REG1<br>REG2      | =<br>= | 0x33<br>0x11 |

|-------------------|--------|--------------|

| After Instruction |        |              |

| REG1              | =      | 0x33,        |

| REG2              | =      | 0x33         |

2

2 (3)

| MO\         | /LB              | Move lite           | ral to lo                                                            | w nibble | e in BSR                    |  |  |

|-------------|------------------|---------------------|----------------------------------------------------------------------|----------|-----------------------------|--|--|

| Synt        | ax:              | [ label ]           | MOVLB                                                                | k        |                             |  |  |

| Ope         | rands:           | $0 \le k \le 25$    | 55                                                                   |          |                             |  |  |

| Ope         | ration:          | $k \to BSR$         |                                                                      |          |                             |  |  |

| Statu       | us Affected:     | None                |                                                                      |          |                             |  |  |

| Enco        | oding:           | 0000                | 0001                                                                 | kkkk     | kkkk                        |  |  |

| Desc        | cription:        |                     | The 8-bit literal 'k' is loaded into the Bank Select Register (BSR). |          |                             |  |  |

| Wor         | ds:              | 1                   |                                                                      |          |                             |  |  |

| Cycl        | es:              | 1                   |                                                                      |          |                             |  |  |

| QC          | ycle Activity    |                     |                                                                      |          |                             |  |  |

|             | Q1               | Q2                  | Q3                                                                   |          | Q4                          |  |  |

| Decode F    |                  | Read literal<br>'k' | Proce<br>Data                                                        |          | Write<br>eral 'k' to<br>BSR |  |  |

| <u>Exar</u> | Example: MOVLB 5 |                     |                                                                      |          |                             |  |  |

| Before Instruction |   |      |

|--------------------|---|------|

| BSR register       | = | 0x02 |

| After Instruction  |   |      |

| BSR register       | = | 0x05 |

| RRNCF                   | Rotate Right f (no carry)                                                                                                                                                                                                                                                                  | SETF                         |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Syntax:                 | [ label ] RRNCF f [,d [,a]                                                                                                                                                                                                                                                                 | Syntax:                      |

| Operands:               | $0 \le f \le 255$<br>$d \in [0,1]$                                                                                                                                                                                                                                                         | Operands:                    |

|                         | a ∈ [0,1]                                                                                                                                                                                                                                                                                  | Operation:                   |

| Operation:              | $(f < n >) \rightarrow dest < n - 1 >,$<br>$(f < 0 >) \rightarrow dest < 7 >$                                                                                                                                                                                                              | Status Affected<br>Encoding: |

| Status Affecte          | ed: N,Z                                                                                                                                                                                                                                                                                    | -                            |

| Encoding:               | 0100 00da ffff ffff                                                                                                                                                                                                                                                                        | Description:                 |

| Description:            | The contents of register 'f' are<br>rotated one bit to the right. If 'd' is 0,<br>the result is placed in WREG. If 'd'<br>is 1, the result is placed back in<br>register 'f' (default). If 'a' is 0, the<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' is 1, then | Words:<br>Cycles:            |

|                         | the bank will be selected as per the                                                                                                                                                                                                                                                       | Q Cycle Activit              |

|                         | BSR value (default).                                                                                                                                                                                                                                                                       | Q1                           |

|                         | register f                                                                                                                                                                                                                                                                                 | Decode                       |

| Words:                  | 1                                                                                                                                                                                                                                                                                          |                              |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                          | Example:                     |

| Q Cycle Activ           | vity:                                                                                                                                                                                                                                                                                      | Before Inst                  |

| Q1                      | Q2 Q3 Q4                                                                                                                                                                                                                                                                                   | REG                          |

| Decode                  | e Read Process Write to<br>register 'f' Data destination                                                                                                                                                                                                                                   | After Instru<br>REG          |

| Example 1:<br>Before In | RRNCF REG, 1, 0                                                                                                                                                                                                                                                                            |                              |

| REG                     | = 1101 0111                                                                                                                                                                                                                                                                                |                              |

| After Inst              |                                                                                                                                                                                                                                                                                            |                              |

| REG                     | = 1110 1011                                                                                                                                                                                                                                                                                |                              |

| Example 2:              | RRNCF REG, 0, 0                                                                                                                                                                                                                                                                            |                              |

| Before In               | struction                                                                                                                                                                                                                                                                                  |                              |

|                         | ; = ?<br>= 1101 0111                                                                                                                                                                                                                                                                       |                              |

| After Inst              |                                                                                                                                                                                                                                                                                            |                              |

| WREG                    |                                                                                                                                                                                                                                                                                            |                              |

| yntax: [label] SETF f [,a] |                                  |                                                                               |                                                                 |                                                          |                                  |  |  |

|----------------------------|----------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|----------------------------------|--|--|

| pera                       | ands:                            | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                      | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$ |                                                          |                                  |  |  |

| pera                       | ation:                           | $FFh\tof$                                                                     |                                                                 |                                                          |                                  |  |  |

| status                     | s Affected:                      | None                                                                          |                                                                 |                                                          |                                  |  |  |

| nco                        | ding:                            | 0110                                                                          | 100a                                                            | ffff                                                     | ffff                             |  |  |

| )esci                      | ription:                         | The conte<br>ter are se<br>Access Ba<br>riding the<br>the bank v<br>BSR value | t to FFh<br>ank will<br>BSR val<br>will be se                   | . If 'a' is 0<br>be select<br>ue. If 'a' i<br>elected as | ), the<br>ed, over-<br>s 1, then |  |  |

| Vord                       | s:                               | 1                                                                             | 1                                                               |                                                          |                                  |  |  |

| ycle                       | s:                               | 1                                                                             |                                                                 |                                                          |                                  |  |  |

| Q Cy                       | cle Activity:                    |                                                                               |                                                                 |                                                          |                                  |  |  |

|                            | Q1                               | Q2                                                                            | Q                                                               | 3                                                        | Q4                               |  |  |

|                            | Decode                           | Read<br>register 'f'                                                          | Proce<br>Data                                                   |                                                          | Write<br>gister 'f'              |  |  |

|                            |                                  |                                                                               |                                                                 |                                                          |                                  |  |  |

| xam                        | <u>iple</u> :                    | SETF                                                                          | RE                                                              | G,1                                                      |                                  |  |  |

| E                          | Before Instruction<br>REG = 0x5A |                                                                               |                                                                 |                                                          |                                  |  |  |

| A                          | After Instruction                |                                                                               |                                                                 |                                                          |                                  |  |  |

0xFF

=

Set f

© 1999-2013 Microchip Technology Inc.

| SUB         | SUBWFB Subtract WREG from f with Borrow |                                                                                           |                                                                                                                                                                   |                                                                                                                                 |  |  |

|-------------|-----------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| Synt        | ax:                                     | [ label ]                                                                                 | SUBWFB f                                                                                                                                                          | [,d [,a]                                                                                                                        |  |  |

| Ope         | rands:                                  | $0 \leq f \leq 2$                                                                         | $0 \le f \le 255$                                                                                                                                                 |                                                                                                                                 |  |  |

|             |                                         | d ∈ [0,1]                                                                                 |                                                                                                                                                                   |                                                                                                                                 |  |  |

| ~           |                                         | a ∈ [0,1]                                                                                 |                                                                                                                                                                   |                                                                                                                                 |  |  |

|             | ration:                                 | ., .                                                                                      | $(\overline{C}) \rightarrow (\overline{C}) \rightarrow$                                                                                                           | dest                                                                                                                            |  |  |

|             | us Affected:                            | N,OV, C                                                                                   |                                                                                                                                                                   |                                                                                                                                 |  |  |

| Enco        | oding:                                  | 0101                                                                                      | 10da ff                                                                                                                                                           | ff ffff                                                                                                                         |  |  |

| Des         | cription:                               | (borrow)<br>ment me<br>stored in<br>is stored<br>If 'a' is 0,<br>selected<br>'a' is 1, th | WREG and the<br>from register of<br>thod). If 'd' is (<br>WREG. If 'd' is<br>back in register<br>the Access B<br>overriding the<br>nen the bank we<br>BSR value ( | f' (2's comple-<br>), the result is<br>s 1, the result<br>er 'f' (default).<br>ank will be<br>BSR value. If<br>vill be selected |  |  |

| Wor         | ds:                                     | 1                                                                                         |                                                                                                                                                                   |                                                                                                                                 |  |  |

| Cycl        | es:                                     | 1                                                                                         |                                                                                                                                                                   |                                                                                                                                 |  |  |

| QC          | cycle Activity:                         |                                                                                           |                                                                                                                                                                   |                                                                                                                                 |  |  |

|             | Q1                                      | Q2                                                                                        | Q3                                                                                                                                                                | Q4                                                                                                                              |  |  |

|             | Decode                                  | Read<br>register 'f'                                                                      | Process<br>Data                                                                                                                                                   | Write to destination                                                                                                            |  |  |

| Exar        | <u>mple 1</u> :                         | SUBWFB                                                                                    | REG, 1, 0                                                                                                                                                         |                                                                                                                                 |  |  |

|             | Before Instru                           | iction                                                                                    |                                                                                                                                                                   |                                                                                                                                 |  |  |

|             | REG                                     | = 0x19                                                                                    |                                                                                                                                                                   |                                                                                                                                 |  |  |

|             | WREG<br>C                               | $= 0 \times 0 D$<br>= 1                                                                   | 0x0D (0000 1101)<br>1                                                                                                                                             |                                                                                                                                 |  |  |

|             | After Instruct                          |                                                                                           |                                                                                                                                                                   |                                                                                                                                 |  |  |

|             | REG<br>WREG                             | $= 0 \times 0 C$<br>$= 0 \times 0 D$                                                      | (0000 101 (0000 110                                                                                                                                               |                                                                                                                                 |  |  |

|             | С                                       | = 1                                                                                       | (0000 110                                                                                                                                                         | 1)                                                                                                                              |  |  |

|             | Z<br>N                                  | = 0<br>= 0                                                                                | ; result i                                                                                                                                                        | s positive                                                                                                                      |  |  |

| <u>Exar</u> | <u>mple 2</u> :                         | SUBWFB                                                                                    | REG, 0, 0                                                                                                                                                         | -                                                                                                                               |  |  |

|             | Before Instru                           | iction                                                                                    |                                                                                                                                                                   |                                                                                                                                 |  |  |

|             | REG<br>WREG                             | = 0x1B<br>= 0x1A                                                                          | (0001 10<br>(0001 10                                                                                                                                              |                                                                                                                                 |  |  |

|             | C                                       | $=$ 0 $\times$ 1 $A$                                                                      | (0001 10                                                                                                                                                          | 107                                                                                                                             |  |  |

|             | After Instruct                          |                                                                                           |                                                                                                                                                                   |                                                                                                                                 |  |  |

|             | REG<br>WREG                             | = 0x1B $= 0x00$                                                                           | (0001 101                                                                                                                                                         | 11)                                                                                                                             |  |  |

|             | C                                       | = 1                                                                                       |                                                                                                                                                                   |                                                                                                                                 |  |  |

|             | Z<br>N                                  | = 1 = 0                                                                                   | ; result i                                                                                                                                                        | s zero                                                                                                                          |  |  |

| <u>Exar</u> | <u>mple 3:</u>                          | SUBWFB                                                                                    | REG, 1, 0                                                                                                                                                         |                                                                                                                                 |  |  |

|             | Before Instru                           | iction                                                                                    |                                                                                                                                                                   |                                                                                                                                 |  |  |

|             | REG                                     | = 0x03                                                                                    | (0000 001                                                                                                                                                         |                                                                                                                                 |  |  |

|             | WREG<br>C                               | = 0x0E<br>= 1                                                                             | (0000 110                                                                                                                                                         | ) _ )                                                                                                                           |  |  |

|             | After Instruct                          | tion                                                                                      |                                                                                                                                                                   |                                                                                                                                 |  |  |

|             | REG                                     | = 0xF5                                                                                    | (1111 010<br>; [2's com]                                                                                                                                          |                                                                                                                                 |  |  |

|             | WREG                                    | = 0x0E                                                                                    | (0000 110                                                                                                                                                         |                                                                                                                                 |  |  |

|             | C<br>Z                                  | = 0<br>= 0                                                                                |                                                                                                                                                                   |                                                                                                                                 |  |  |

|             | N                                       | = 1                                                                                       | ; result i                                                                                                                                                        | s negative                                                                                                                      |  |  |

| SWAPF                                                                                           | Swap f                                                                                                 |                                                                                                                                                                                                                                                                                                                                                   |   |                       |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------|--|--|

| Syntax:                                                                                         | [label] SWAPF f[,d[,a]                                                                                 |                                                                                                                                                                                                                                                                                                                                                   |   |                       |  |  |

| Operands:                                                                                       | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                    |                                                                                                                                                                                                                                                                                                                                                   |   |                       |  |  |

| Operation:                                                                                      | · · ·                                                                                                  | $(f<3:0>) \rightarrow dest<7:4>,$<br>$(f<7:4>) \rightarrow dest<3:0>$                                                                                                                                                                                                                                                                             |   |                       |  |  |

| Status Affected:                                                                                | None                                                                                                   |                                                                                                                                                                                                                                                                                                                                                   |   |                       |  |  |

| Encoding:                                                                                       | 0011                                                                                                   | 0011 10da ffff ffff                                                                                                                                                                                                                                                                                                                               |   |                       |  |  |

| Description:                                                                                    | ister 'f' are<br>result is pl<br>the result<br>(default). I<br>Bank will t<br>the BSR v<br>bank will b | The upper and lower nibbles of reg-<br>ister 'f' are exchanged. If 'd' is 0, the<br>result is placed in WREG. If 'd' is 1,<br>the result is placed in register 'f'<br>(default). If 'a' is 0, the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' is 1, then the<br>bank will be selected as per the<br>BSR value (default). |   |                       |  |  |

| Words:                                                                                          | 1                                                                                                      | ,                                                                                                                                                                                                                                                                                                                                                 | , |                       |  |  |

| Cycles:                                                                                         | 1                                                                                                      |                                                                                                                                                                                                                                                                                                                                                   |   |                       |  |  |

| Q Cycle Activity:                                                                               |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                   |   |                       |  |  |

| Q1                                                                                              | Q2                                                                                                     | Q3                                                                                                                                                                                                                                                                                                                                                |   | Q4                    |  |  |

| Decode                                                                                          | Read<br>register 'f'                                                                                   | Proces<br>Data                                                                                                                                                                                                                                                                                                                                    | - | Vrite to<br>stination |  |  |

| Example: SWAPF REG, 1, 0<br>Before Instruction<br>REG = 0x53<br>After Instruction<br>REG = 0x35 |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                   |   |                       |  |  |

| TBL               | RD                                 | Table Read                                                          | d                                                                        |                                         |                |  |  |

|-------------------|------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------|----------------|--|--|

| Synt              | ax:                                | [ label ]                                                           | TBLRD (                                                                  | *; *+; *-; +                            | -*)            |  |  |

| Ope               | rands:                             | None                                                                |                                                                          |                                         |                |  |  |

| Ope               | ration:                            | if TBLRD *,                                                         | ,                                                                        |                                         |                |  |  |

|                   |                                    |                                                                     |                                                                          | $PTR)) \rightarrow $                    | TABLAT;        |  |  |

|                   |                                    | if TBLRD *-                                                         | R - No Ch<br>+                                                           | iange;                                  |                |  |  |

|                   |                                    |                                                                     |                                                                          | $PTR)) \rightarrow $                    | TABLAT;        |  |  |

|                   |                                    |                                                                     |                                                                          | TBLPTR;                                 |                |  |  |

|                   |                                    | if TBLRD *-<br>(Prog M                                              |                                                                          | $PTR)) \rightarrow $                    | TABI AT'       |  |  |

|                   |                                    |                                                                     |                                                                          | TBLPTR;                                 | 17 (BE) (1,    |  |  |