Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

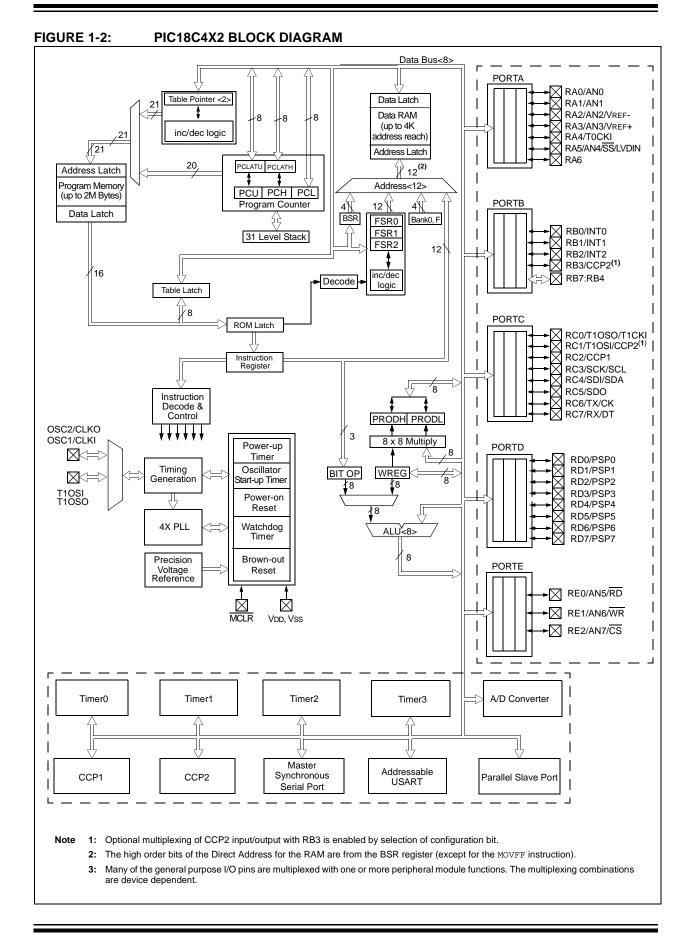

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c442t-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 4-2: REGISTER FILE SUMMARY**

| File Name | Bit 7        | Bit 6                             | Bit 5                | Bit 4         | Bit 3          | Bit 2          | Bit 1           | Bit 0         | Value on<br>POR,<br>BOR | Details<br>on page: |

|-----------|--------------|-----------------------------------|----------------------|---------------|----------------|----------------|-----------------|---------------|-------------------------|---------------------|

| TOSU      | _            | _                                 | _                    | Top-of-Stack  | Upper Byte (T  | OS<20:16>)     |                 |               | 0 0000                  | 37                  |

| TOSH      | Top-of-Stacl | k High Byte (T                    | OS<15:8>)            |               |                |                |                 |               | 0000 0000               | 37                  |

| TOSL      | Top-of-Stac  | k Low Byte (TC                    | )<br>S<7:0>)         |               |                |                |                 |               | 0000 0000               | 37                  |

| STKPTR    | STKFUL       | STKUNF                            | _                    | Return Stack  | Pointer        |                |                 |               | 00-0 0000               | 38                  |

| PCLATU    | _            | _                                 | _                    | Holding Regi  | ster for PC<20 | ):16>          |                 |               | 0 0000                  | 39                  |

| PCLATH    | Holding Reg  | gister for PC<1                   | 5:8>                 |               |                |                |                 |               | 0000 0000               | 39                  |

| PCL       | PC Low Byt   | e (PC<7:0>)                       |                      |               |                |                |                 |               | 0000 0000               | 39                  |

| TBLPTRU   | _            | _                                 | bit21 <sup>(2)</sup> | Program Mer   | nory Table Po  | inter Upper By | te (TBLPTR<     | 20:16>)       | 0 0000                  | 57                  |

| TBLPTRH   | Program Me   | emory Table Po                    | pinter High By       | te (TBLPTR<1  | 5:8>)          |                |                 |               | 0000 0000               | 57                  |

| TBLPTRL   | Program Me   | emory Table Po                    | pinter Low Byt       | te (TBLPTR<7: | 0>)            |                |                 |               | 0000 0000               | 57                  |

| TABLAT    | Program Me   | emory Table La                    | atch                 |               |                |                |                 |               | 0000 0000               | 57                  |

| PRODH     | Product Reg  | gister High Byt                   | е                    |               |                |                |                 |               | XXXX XXXX               | 61                  |

| PRODL     | Product Reg  | gister Low Byte                   | 9                    |               |                |                |                 |               | XXXX XXXX               | 61                  |

| INTCON    | GIE/GIEH     | PEIE/GIEL                         | TMR0IE               | <b>INTOIE</b> | RBIE           | TMR0IF         | <b>INT0IF</b>   | RBIF          | 0000 000x               | 65                  |

| INTCON2   | RBPU         | INTEDG0                           | INTEDG1              | INTEDG2       | _              | TMR0IP         | _               | RBIP          | 1111 -1-1               | 66                  |

| INTCON3   | INT2IP       | INT1IP                            | _                    | INT2IE        | INT1IE         | _              | INT2IF          | INT1IF        | 11-0 0-00               | 67                  |

| INDF0     | Uses conter  | nts of FSR0 to                    | address data         | memory - valu | e of FSR0 not  | changed (not   | a physical rec  | gister)       | N/A                     | 50                  |

| POSTINC0  | Uses conter  | nts of FSR0 to                    | address data         | memory - valu | e of FSR0 pos  | t-incremented  | (not a physic   | al register)  | N/A                     | 50                  |

| POSTDEC0  | Uses conter  | nts of FSR0 to                    | address data         | memory - valu | e of FSR0 pos  | t-decremented  | d (not a physic | cal register) | N/A                     | 50                  |

| PREINC0   | Uses conter  | nts of FSR0 to                    | address data         | memory - valu | e of FSR0 pre- | -incremented   | not a physica   | I register)   | N/A                     | 50                  |

| PLUSW0    |              | nts of FSR0 to<br>R0 offset by va |                      | memory - valu | e of FSR0 pre- | -incremented   | not a physica   | l register) - | N/A                     | 50                  |

| FSR0H     | _            | _                                 | _                    | _             | Indirect Data  | Memory Add     | ress Pointer (  | ) High Byte   | 0000                    | 50                  |

| FSR0L     | Indirect Dat | a Memory Add                      | ress Pointer 0       | Low Byte      |                |                |                 |               | XXXX XXXX               | 50                  |

| WREG      | Working Re   | gister                            |                      |               |                |                |                 |               | xxxx xxxx               |                     |

| INDF1     | Uses conter  | nts of FSR1 to                    | address data         | memory - valu | e of FSR1 not  | changed (not   | a physical reg  | gister)       | N/A                     | 50                  |

| POSTINC1  | Uses conter  | nts of FSR1 to                    | address data         | memory - valu | e of FSR1 pos  | t-incremented  | (not a physic   | al register)  | N/A                     | 50                  |

| POSTDEC1  | Uses conter  | nts of FSR1 to                    | address data         | memory - valu | e of FSR1 pos  | t-decremented  | d (not a physic | cal register) | N/A                     | 50                  |

| PREINC1   | Uses conter  | nts of FSR1 to                    | address data         | memory - valu | e of FSR1 pre- | -incremented   | not a physica   | I register)   | N/A                     | 50                  |

| PLUSW1    |              | nts of FSR1 to<br>R1 offset by va |                      | memory - valu | e of FSR1 pre  | -incremented   | not a physica   | l register) - | N/A                     | 50                  |

| FSR1H     | _            | _                                 | _                    | —             | Indirect Data  | a Memory Add   | ress Pointer 1  | High Byte     | 0000                    | 50                  |

| FSR1L     | Indirect Dat | a Memory Add                      | ress Pointer 1       | Low Byte      |                |                |                 |               | xxxx xxxx               | 50                  |

| BSR       | _            | _                                 | _                    | —             | Bank Select    | Register       |                 |               | 0000                    | 49                  |

| INDF2     | Uses conter  | nts of FSR2 to                    | address data         | memory - valu | e of FSR2 not  | changed (not   | a physical reg  | gister)       | N/A                     | 50                  |

| POSTINC2  | Uses conter  | nts of FSR2 to                    | address data         | memory - valu | e of FSR2 pos  | t-incremented  | (not a physic   | al register)  | N/A                     | 50                  |

| POSTDEC2  | Uses conter  | nts of FSR2 to                    | address data         | memory - valu | e of FSR2 pos  | t-decremented  | d (not a physic | cal register) | N/A                     | 50                  |

| PREINC2   | Uses conter  | nts of FSR2 to                    | address data         | memory - valu | e of FSR2 pre- | -incremented   | not a physica   | l register)   | N/A                     | 50                  |

| PLUSW2    |              | nts of FSR2 to<br>R2 offset by va |                      | memory - valu | e of FSR2 pre  | -incremented   | not a physica   | l register) - | N/A                     | 50                  |

| FSR2H     | _            | _                                 | _                    | _             | Indirect Data  | Memory Add     | ress Pointer 2  | 2 High Byte   | 0000                    | 50                  |

| FSR2L     | Indirect Dat | a Memory Add                      | ress Pointer 2       | 2 Low Byte    |                |                |                 |               | xxxx xxxx               | 50                  |

| STATUS    | _            | —                                 | _                    | Ν             | OV             | Z              | DC              | С             | x xxxx                  | 52                  |

| TMR0H     | Timer0 Reg   | ister High Byte                   |                      |               |                |                |                 |               | 0000 0000               | 95                  |

| TMR0L     | Timer0 Reg   | ister Low Byte                    |                      |               |                |                |                 |               | xxxx xxxx               | 95                  |

| T0CON     | TMR0ON       | T08BIT                            | TOCS                 | TOSE          | PSA            | T0PS2          | T0PS1           | T0PS0         | 1111 1111               | 93                  |

| OSCCON    | —            | —                                 | —                    | —             | —              | —              | —               | SCS           | 0                       | 20                  |

| LVDCON    | _            | _                                 | IRVST                | LVDEN         | LVDL3          | LVDL2          | LVDL1           | LVDL0         | 00 0101                 | 175                 |

Legend: x = unknown, u = unchanged, - = unimplemented, g = value depends on condition

Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO oscillator mode only, and read '0' in all other oscillator modes.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

#### 4.10 Access Bank

The Access Bank is an architectural enhancement, which is very useful for C compiler code optimization. The techniques used by the C compiler may also be useful for programs written in assembly.

This data memory region can be used for:

- Intermediate computational values

- · Local variables of subroutines

- Faster context saving/switching of variables

- Common variables

- Faster evaluation/control of SFRs (no banking)

The Access Bank is comprised of the upper 128 bytes in Bank 15 (SFRs) and the lower 128 bytes in Bank 0. These two sections will be referred to as Access RAM High and Access RAM Low, respectively. Figure 4-6 and Figure 4-7 indicate the Access RAM areas.

A bit in the instruction word specifies if the operation is to occur in the bank specified by the BSR register or in the Access Bank. This bit is denoted by the 'a' bit (for access bit).

When forced in the Access Bank (a = '0'), the last address in Access RAM Low is followed by the first address in Access RAM High. Access RAM High maps the Special Function registers, so that these registers can be accessed without any software overhead. This is useful for testing status flags and modifying control bits.

#### 4.11 Bank Select Register (BSR)

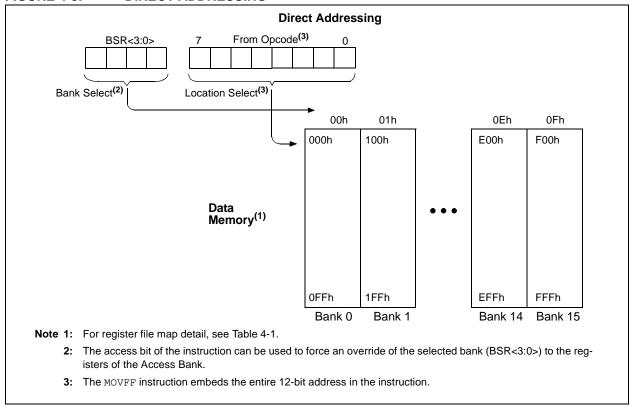

The need for a large general purpose memory space dictates a RAM banking scheme. The data memory is partitioned into sixteen banks. When using direct addressing, the BSR should be configured for the desired bank.

BSR<3:0> holds the upper 4 bits of the 12-bit RAM address. The BSR<7:4> bits will always read '0's, and writes will have no effect.

A MOVLB instruction has been provided in the instruction set to assist in selecting banks.

If the currently selected bank is not implemented, any read will return all '0's and all writes are ignored. The STATUS register bits will be set/cleared as appropriate for the instruction performed.

Each Bank extends up to FFh (256 bytes). All data memory is implemented as static RAM.

A MOVFF instruction ignores the BSR, since the 12-bit addresses are embedded into the instruction word.

Section 4.12 provides a description of indirect addressing, which allows linear addressing of the entire RAM space.

#### FIGURE 4-8: DIRECT ADDRESSING

### 4.12 Indirect Addressing, INDF and FSR Registers

Indirect addressing is a mode of addressing data memory, where the data memory address in the instruction is not fixed. An FSR register is used as a pointer to the data memory location that is to be read or written. Since this pointer is in RAM, the contents can be modified by the program. This can be useful for data tables in the data memory and for software stacks. Figure 4-9 shows the operation of indirect addressing. This shows the moving of the value to the data memory address, specified by the value of the FSR register.

Indirect addressing is possible by using one of the INDF registers. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = '0'), will read 00h. Writing to the INDF register indirectly, results in a no operation. The FSR register contains a 12-bit address, which is shown in Figure 4-10.

The INDFn register is not a physical register. Addressing INDFn actually addresses the register whose address is contained in the FSRn register (FSRn is a pointer). This is indirect addressing.

Example 4-4 shows a simple use of indirect addressing to clear the RAM in Bank1 (locations 100h-1FFh) in a minimum number of instructions.

#### EXAMPLE 4-4: HOW TO CLEAR RAM (BANK1) USING INDIRECT ADDRESSING

| FSR0, 0x100<br>POSTINC0 | ;<br>; Clear INDF register<br>; & inc pointer               |

|-------------------------|-------------------------------------------------------------|

| FSROH, 1<br>NEXT        | ; All done w/ Bank1?<br>; NO, clear next<br>; YES, continue |

There are three indirect addressing registers. To address the entire data memory space (4096 bytes), these registers are 12-bit wide. To store the 12-bits of addressing information, two 8-bit registers are required. These indirect addressing registers are:

- 1. FSR0: composed of FSR0H:FSR0L

- 2. FSR1: composed of FSR1H:FSR1L

- 3. FSR2: composed of FSR2H:FSR2L

In addition, there are registers INDF0, INDF1 and INDF2, which are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data.

If an instruction writes a value to INDF0, the value will be written to the address pointed to by FSR0H:FSR0L. A read from INDF1 reads the data from the address pointed to by FSR1H:FSR1L. INDFn can be used in code anywhere an operand can be used. If INDF0, INDF1 or INDF2 are read indirectly via an FSR, all '0's are read (zero bit is set). Similarly, if INDF0, INDF1 or INDF2 are written to indirectly, the operation will be equivalent to a NOP instruction and the STATUS bits are not affected.

#### 4.12.1 INDIRECT ADDRESSING OPERATION

Each FSR register has an INDF register associated with it, plus four additional register addresses. Performing an operation on one of these five registers determines how the FSR will be modified during indirect addressing.

When data access is done to one of the five INDFn locations, the address selected will configure the FSRn register to:

- Do nothing to FSRn after an indirect access (no change) INDFn

- Auto-decrement FSRn after an indirect access (post-decrement) POSTDECn

- Auto-increment FSRn after an indirect access (post-increment) POSTINCn

- Auto-increment FSRn before an indirect access (pre-increment) PREINCn

- Use the value in the WREG register as an offset to FSRn. Do not modify the value of the WREG or the FSRn register after an indirect access (no change) - PLUSWn

When using the auto-increment or auto-decrement features, the effect on the FSR is not reflected in the STATUS register. For example, if the indirect address causes the FSR to equal '0', the Z bit will not be set.

Incrementing or decrementing an FSR affects all 12 bits. That is, when FSRnL overflows from an increment, FSRnH will be incremented automatically.

Adding these features allows the FSRn to be used as a stack pointer, in addition to its uses for table operations in data memory.

Each FSR has an address associated with it that performs an indexed indirect access. When a data access to this INDFn location (PLUSWn) occurs, the FSRn is configured to add the signed value in the WREG register and the value in FSR to form the address before an indirect access. The FSR value is not changed.

If an FSR register contains a value that points to one of the INDFn, an indirect read will read 00h (zero bit is set), while an indirect write will be equivalent to a NOP (STATUS bits are not affected).

### 4.13 STATUS Register

The STATUS register, shown in Register 4-2, contains the arithmetic status of the ALU. The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, then the write to these five bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the STATUS register as destination may be different than intended. For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits from the STATUS register. For other instructions not affecting any status bits, see Table 19-2.

| Note: | The C and DC bits operate as a borrow and      |

|-------|------------------------------------------------|

|       | digit borrow bit respectively, in subtraction. |

#### REGISTER 4-2: STATUS REGISTER

| U-0   | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | N     | OV    | Z     | DC    | С     |

| bit 7 |     |     |       |       |       |       | bit 0 |

#### bit 7-5 Unimplemented: Read as '0'

bit 4 N: Negative bit

This bit is used for signed arithmetic (2's complement). It indicates whether the result was negative, (ALU MSB = 1).

- 1 = Result was negative

- 0 = Result was positive

| bit 3 <b>OV:</b> Overflow bit |

|-------------------------------|

|-------------------------------|

This bit is used for signed arithmetic (2's complement). It indicates an overflow of the 7-bit magnitude, which causes the sign bit (bit7) to change state.

- 1 = Overflow occurred for signed arithmetic (in this arithmetic operation)

- 0 = No overflow occurred

bit 2 Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

#### bit 1 DC: Digit carry/borrow bit

For ADDWF, ADDLW, SUBLW, and SUBWF instructions

1 = A carry-out from the 4th low order bit of the result occurred

- 0 = No carry-out from the 4th low order bit of the result

- **Note:** For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the bit 4 or bit 3 of the source register.

#### bit 0 **C:** Carry/borrow bit

For ADDWF, ADDLW, SUBLW, and SUBWF instructions

- 1 = A carry-out from the Most Significant bit of the result occurred

- 0 = No carry-out from the Most Significant bit of the result occurred

- **Note:** For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 7.5 RCON Register

The RCON register contains the bit which is used to enable prioritized interrupts (IPEN).

- n = Value at POR reset

#### REGISTER 7-10: RCON REGISTER

|       | R/W-0       | R/W-0                               | U-0           | R/W-1      | R-1           | R-1       | R/W-0          | R/W-0 |

|-------|-------------|-------------------------------------|---------------|------------|---------------|-----------|----------------|-------|

|       | IPEN        | LWRT                                |               | RI         | TO            | PD        | POR            | BOR   |

|       | bit 7       |                                     |               |            |               |           |                | bit 0 |

|       |             |                                     |               |            |               |           |                |       |

| bit 7 | IPEN: Inte  | rrupt Priority                      | Enable bit    |            |               |           |                |       |

|       |             | e priority leve<br>le priority leve |               |            | ( compatibili | ty mode)  |                |       |

| bit 6 | LWRT: Lor   | ng Write Enal                       | ble bit       |            |               |           |                |       |

|       | For details | of bit operati                      | ion, see Regi | ster 4-3   |               |           |                |       |

| bit 5 | Unimplem    | nented: Read                        | l as '0'      |            |               |           |                |       |

| bit 4 | RI: RESET   | Instruction F                       | lag bit       |            |               |           |                |       |

|       | For details | of bit operat                       | ion, see Regi | ster 4-3   |               |           |                |       |

| bit 3 | TO: Watch   | idog Time-ou                        | t Flag bit    |            |               |           |                |       |

|       | For details | of bit operation                    | ion, see Regi | ster 4-3   |               |           |                |       |

| bit 2 | PD: Power   | r-down Detec                        | tion Flag bit |            |               |           |                |       |

|       | For details | of bit operat                       | ion, see Regi | ster 4-3   |               |           |                |       |

| bit 1 | POR: Pow    | er-on Reset                         | Status bit    |            |               |           |                |       |

|       | For details | of bit operat                       | ion, see Regi | ster 4-3   |               |           |                |       |

| bit 0 | BOR: Brow   | wn-out Reset                        | Status bit    |            |               |           |                |       |

|       | For details | of bit operat                       | ion, see Regi | ster 4-3   |               |           |                |       |

|       | Logondi     |                                     |               |            |               |           |                | ]     |

|       | Legend:     |                                     |               |            |               |           |                | 01    |

|       | R = Reada   | adie dit                            | vv = vvr      | itable bit | U = Unimp     | plemented | bit, read as ' | U     |

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

#### TABLE 8-1: PORTA FUNCTIONS

| Name             | Bit# | Buffer | Function                                                                                                     |

|------------------|------|--------|--------------------------------------------------------------------------------------------------------------|

| RA0/AN0          | bit0 | TTL    | Input/output or analog input.                                                                                |

| RA1/AN1          | bit1 | TTL    | Input/output or analog input.                                                                                |

| RA2/AN2/VREF-    | bit2 | TTL    | Input/output or analog input or VREF                                                                         |

| RA3/AN3/VREF+    | bit3 | TTL    | Input/output or analog input or VREF+.                                                                       |

| RA4/T0CKI        | bit4 | ST     | Input/output or external clock input for Timer0.<br>Output is open drain type.                               |

| RA5/SS/AN4/LVDIN | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input, or low voltage detect input. |

| OSC2/CLKO/RA6    | bit6 | TTL    | OSC2 or clock output or I/O pin.                                                                             |

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 8-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7 | Bit 6   | Bit 5     | Bit 4     | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|-------|---------|-----------|-----------|--------|-------|-------|-------|-------------------------|---------------------------------|

| PORTA  | —     | RA6     | RA5       | RA4       | RA3    | RA2   | RA1   | RA0   | 0x 0000                 | 0u 0000                         |

| LATA   |       | Latch A | Data Outp | out Regis | ster   |       |       |       | xx xxxx                 | uu uuuu                         |

| TRISA  |       | PORTA   | Data Dire | ction Reg | gister |       |       |       | 11 1111                 | 11 1111                         |

| ADCON1 | ADFM  | ADCS2   | —         | —         | PCFG3  | PCFG2 | PCFG1 | PCFG0 | 0- 0000                 | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

$\ensuremath{\textcircled{}^\circ}$  1999-2013 Microchip Technology Inc.

#### TABLE 8-7:PORTD FUNCTIONS

| Name     | Bit# | Buffer Type           | Function                                           |

|----------|------|-----------------------|----------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0. |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1. |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2. |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3. |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4. |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5. |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6. |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7. |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 8-8: SUMMARY OF REGISTERS ASSOCIATED WITH POR |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Name  | Bit 7  | Bit 6                         | Bit 5     | Bit 4                               | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|-------|--------|-------------------------------|-----------|-------------------------------------|-------|-------|-------|-------|-------------------------|---------------------------------|

| PORTD | RD7    | RD6                           | RD5       | RD4                                 | RD3   | RD2   | RD1   | RD0   | xxxx xxxx               | uuuu uuuu                       |

| LATD  | LATD D | Data Out                      | put Regis | ster                                |       |       |       |       | xxxx xxxx               | uuuu uuuu                       |

| TRISD | PORTE  | PORTD Data Direction Register |           |                                     |       |       |       |       | 1111 1111               | 1111 1111                       |

| TRISE | IBF    | OBF                           | IBOV      | PSPMODE — PORTE Data Direction bits |       |       |       |       | 0000 -111               | 0000 -111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

### 9.0 TIMER0 MODULE

The Timer0 module has the following features:

- Software selectable as an 8-bit or 16-bit timer/ counter

- Readable and writable

- Dedicated 8-bit software programmable prescaler

- · Clock source selectable to be external or internal

- Interrupt-on-overflow from FFh to 00h in 8-bit mode and FFFFh to 0000h in 16-bit mode

- Edge select for external clock

| REGISTER 9-1: | T0CON: TIMER0 CONTROL REGISTER |

|---------------|--------------------------------|

| R 9-1:  | : T0CON: TIMER0 CONTROL REGISTER                                                                                                                            |                                                                                                                                                                   |                                   |                                       |              |          |              |       |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------|--------------|----------|--------------|-------|--|--|--|

|         | R/W-1                                                                                                                                                       | R/W-1                                                                                                                                                             | R/W-1                             | R/W-1                                 | R/W-1        | R/W-1    | R/W-1        | R/W-1 |  |  |  |

|         | TMR0ON                                                                                                                                                      | T08BIT                                                                                                                                                            | TOCS                              | TOSE                                  | PSA          | T0PS2    | T0PS1        | T0PS0 |  |  |  |

|         | bit 7                                                                                                                                                       |                                                                                                                                                                   |                                   | · · · · · · · · · · · · · · · · · · · |              |          |              | bit 0 |  |  |  |

| bit 7   | TMR0ON: <sup>-</sup><br>1 = Enables<br>0 = Stops T                                                                                                          |                                                                                                                                                                   | Control bit                       |                                       |              |          |              |       |  |  |  |

| bit 6   | <b>T08BIT</b> : Timer0 8-bit/16-bit Control bit<br>1 = Timer0 is configured as an 8-bit timer/counter<br>0 = Timer0 is configured as a 16-bit timer/counter |                                                                                                                                                                   |                                   |                                       |              |          |              |       |  |  |  |

| bit 5   | 1 = Transiti                                                                                                                                                | <b>TOCS</b> : Timer0 Clock Source Select bit<br>1 = Transition on T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT)                                      |                                   |                                       |              |          |              |       |  |  |  |

| bit 4   | 1 = Increme                                                                                                                                                 | er0 Source Ed<br>ent on high-to-<br>ent on low-to-l                                                                                                               | -low transitic                    | n on TOCKI p                          |              |          |              |       |  |  |  |

| bit 3   | 1 = TImer0                                                                                                                                                  | 0 Prescaler A<br>prescaler is N<br>prescaler is a                                                                                                                 | IOT assigne                       | d. Timer0 clo                         |              |          |              |       |  |  |  |

| bit 2:0 | 111 = 1:256<br>110 = 1:128<br>101 = 1:64<br>100 = 1:32<br>011 = 1:16<br>010 = 1:8<br>001 = 1:4                                                              | <b>PSO</b> : Timer0 P<br>6 prescale valu<br>8 prescale valu<br>prescale valu<br>prescale valu<br>prescale valu<br>prescale valu<br>prescale valu<br>prescale valu | ue<br>ue<br>e<br>e<br>e<br>e<br>e | ect bits                              |              |          |              |       |  |  |  |

|         | Legend:<br>R = Readal                                                                                                                                       | ble bit                                                                                                                                                           | W = Wri                           | table bit                             | U = Unima    | lemented | bit, read as | ʻ0'   |  |  |  |

|         |                                                                                                                                                             | at POR reset                                                                                                                                                      | '1' = Bit                         | is set                                | '0' = Bit is |          | x = Bit is u |       |  |  |  |

Figure 9-1 shows a simplified block diagram of the Timer0 module in 8-bit mode and Figure 9-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

The T0CON register (Register 9-1) is a readable and writable register that controls all the aspects of Timer0, including the prescale selection.

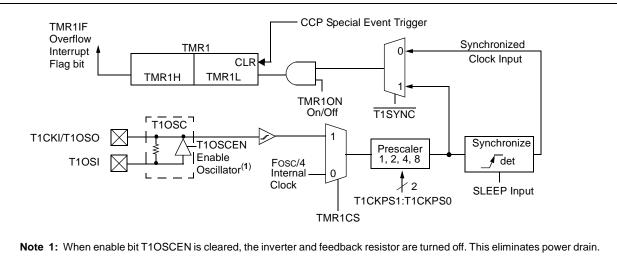

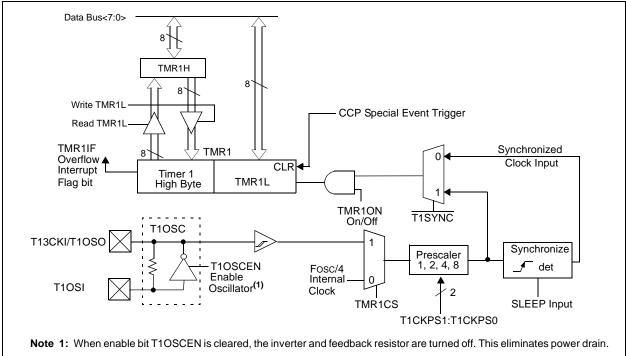

### 10.1 Timer1 Operation

Timer1 can operate in one of these modes:

- As a timer

- As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

When TMR1CS = 0, Timer1 increments every instruction cycle. When TMR1CS = 1, Timer1 increments on every rising edge of the external clock input or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer1 also has an internal "RESET input". This RESET can be generated by the CCP module (Section 13.0).

#### FIGURE 10-2: TIMER1 BLOCK DIAGRAM: 16-BIT READ/WRITE MODE

### FIGURE 10-1: TIMER1 BLOCK DIAGRAM

NOTES:

| TABLE 15-5: | BAUD RATES FOR ASYNCHRONOUS MODE (B | 3RGH = 1) |

|-------------|-------------------------------------|-----------|

|-------------|-------------------------------------|-----------|

| BAUD<br>RATE<br>(K) | Fosc = 40 MHz         |            |                             | F                     | DSC = 20   | MHz                         | F                     | osc = 16   | MHz                         | F                     | SC = 10 MHz           %         SPBRG value (decimal)           +0.16         64           -1.36         32           +1.7         15 |    |

|---------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|----|

|                     | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) |                                                                                                                                       |    |

| 9.6                 | 9.77                  | -1.70      | 255                         | 9.615                 | +0.16      | 129                         | 9.615                 | +0.16      | 103                         | 9.615                 | +0.16                                                                                                                                 | 64 |

| 19.2                | 19.23                 | -0.16      | 129                         | 19.230                | +0.16      | 64                          | 19.230                | +0.16      | 51                          | 18.939                | -1.36                                                                                                                                 | 32 |

| 38.4                | 38.46                 | -0.16      | 64                          | 37.878                | -1.36      | 32                          | 38.461                | +0.16      | 25                          | 39.062                | +1.7                                                                                                                                  | 15 |

| 57.6                | 58.14                 | -0.93      | 42                          | 56.818                | -1.36      | 21                          | 58.823                | +2.12      | 16                          | 56.818                | -1.36                                                                                                                                 | 10 |

| 115.2               | 113.64                | +1.38      | 21                          | 113.63                | -1.36      | 10                          | 111.11                | -3.55      | 8                           | 125                   | +8.51                                                                                                                                 | 4  |

| 250                 | 250.00                | 0          | 9                           | 250                   | 0          | 4                           | 250                   | 0          | 3                           | NA                    | _                                                                                                                                     | _  |

| 625                 | 625.00                | 0          | 3                           | 625                   | 0          | 1                           | NA                    | _          | _                           | 625                   | 0                                                                                                                                     | 0  |

| 1250                | 1250.00               | 0          | 1                           | 1250                  | 0          | 0                           | NA                    | _          | _                           | NA                    | _                                                                                                                                     | _  |

| BAUD        | Fosc = 7.16MHz        |            |                             | Fos                   | SC = 5.06  | 8 MHz                       | F                     | osc = 4 I  | MHz                         | Fosc                  | = 3.5795   | 645 MHz                     |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 9.6         | 9.520                 | -0.83      | 46                          | 9.6                   | 0          | 32                          | NA                    | _          | _                           | 9.727                 | +1.32      | 22                          |

| 19.2        | 19.454                | +1.32      | 22                          | 18.645                | -2.94      | 16                          | 1.202                 | +0.17      | 207                         | 18.643                | -2.90      | 11                          |

| 38.4        | 37.286                | -2.90      | 11                          | 39.6                  | +3.12      | 7                           | 2.403                 | +0.13      | 103                         | 37.286                | -2.90      | 5                           |

| 57.6        | 55.930                | -2.90      | 7                           | 52.8                  | -8.33      | 5                           | 9.615                 | +0.16      | 25                          | 55.930                | -2.90      | 3                           |

| 115.2       | 111.860               | -2.90      | 3                           | 105.6                 | -8.33      | 2                           | 19.231                | +0.16      | 12                          | 111.86                | -2.90      | 1                           |

| 250         | NA                    | _          | _                           | NA                    | _          | _                           | NA                    | _          | _                           | 223.72                | -10.51     | 0                           |

| 625         | NA                    | _          | _                           |

| 1250        | NA                    | —          | —                           |

| BAUD        | F                               | osc = 1 | MHz                         | Fosc = 32.768 kHz     |            |                             |  |

|-------------|---------------------------------|---------|-----------------------------|-----------------------|------------|-----------------------------|--|

| RATE<br>(K) | Actual %<br>Rate %<br>(K) Error |         | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 9.6         | 8.928                           | -6.99   | 6                           | NA                    | _          | _                           |  |

| 19.2        | 20.833                          | +8.51   | 2                           | NA                    | —          | —                           |  |

| 38.4        | 31.25                           | -18.61  | 1                           | NA                    | —          | —                           |  |

| 57.6        | 62.5                            | +8.51   | 0                           | NA                    | —          | _                           |  |

| 115.2       | NA                              | —       | _                           | NA                    | —          | _                           |  |

| 250         | NA                              | —       | _                           | NA                    | —          | _                           |  |

| 625         | NA                              | —       | —                           | NA                    | —          | —                           |  |

| 1250        | NA                              | —       |                             | NA                    | —          | —                           |  |

The value that is in the ADRESH/ADRESL registers is not modified for a Power-on Reset. The ADRESH/ ADRESL registers will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 16.1. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- · Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear ADIF bit

- Set ADIE bit

- · Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared

OR

- Waiting for the A/D interrupt

- 6. Read A/D Result registers (ADRESH/ADRESL); clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

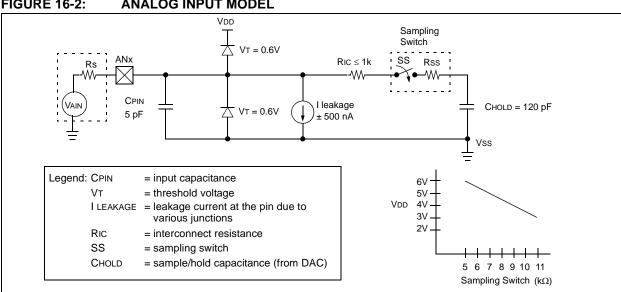

#### **FIGURE 16-2:** ANALOG INPUT MODEL

#### 16.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 16-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

When the conversion is started, the hold-Note: ing capacitor is disconnected from the input pin.

| ADDWFC                                           | ADDWFC ADD WREG and Carry bit to f                                                                                                                                                                                                                                                          |                 |           |                   |  |  |  |  |  |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|-------------------|--|--|--|--|--|--|

| Syntax:                                          | [ label ] Al                                                                                                                                                                                                                                                                                | DWFC            | f [,d [,a | a]                |  |  |  |  |  |  |

| Operands:                                        | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                       | 5               |           |                   |  |  |  |  |  |  |

| Operation: $(WREG) + (f) + (C) \rightarrow dest$ |                                                                                                                                                                                                                                                                                             |                 |           |                   |  |  |  |  |  |  |

| Status Affected:                                 | N,OV, C, [                                                                                                                                                                                                                                                                                  | DC, Z           |           |                   |  |  |  |  |  |  |

| Encoding:                                        | 0010                                                                                                                                                                                                                                                                                        | 00da            | ffff      | ffff              |  |  |  |  |  |  |

| Words:                                           | Description: Add WREG, the Carry Flag and data<br>memory location 'f'. If 'd' is 0, the<br>result is placed in WREG. If 'd' is 1,<br>the result is placed in data memory<br>location 'f'. If 'a' is 0, the Access<br>Bank will be selected. If 'a' is 1, the<br>BSR will not be overridden. |                 |           |                   |  |  |  |  |  |  |

|                                                  | 1                                                                                                                                                                                                                                                                                           |                 |           |                   |  |  |  |  |  |  |

| Cycles:<br>Q Cycle Activity<br>Q1                |                                                                                                                                                                                                                                                                                             | Q3              |           | Q4                |  |  |  |  |  |  |

| Decode                                           | Read<br>register 'f'                                                                                                                                                                                                                                                                        | Process<br>Data |           | ite to<br>ination |  |  |  |  |  |  |

| Example: ADDWFC REG, 0, 1<br>Before Instruction  |                                                                                                                                                                                                                                                                                             |                 |           |                   |  |  |  |  |  |  |

| ANDLW            | AND liter                            | AND literal with WREG |                    |                  |  |  |  |

|------------------|--------------------------------------|-----------------------|--------------------|------------------|--|--|--|

| Syntax:          | [label] A                            | NDLW                  | k                  |                  |  |  |  |

| Operands:        | $0 \le k \le 25$                     | 5                     |                    |                  |  |  |  |

| Operation:       | (WREG).                              | AND. k -              | $\rightarrow$ WREC | 3                |  |  |  |

| Status Affected: | N,Z                                  |                       |                    |                  |  |  |  |

| Encoding:        | 0000                                 | 1011                  | kkkk               | kkkk             |  |  |  |

| Description:     | The conte<br>with the 8<br>placed in | -bit litera           |                    |                  |  |  |  |

| Words:           | 1                                    |                       |                    |                  |  |  |  |

| Cycles:          | 1                                    | 1                     |                    |                  |  |  |  |

| Q Cycle Activit  | y:                                   |                       |                    |                  |  |  |  |

| Q1               | Q2                                   | Q3                    |                    | Q4               |  |  |  |

| Decode           | Read literal<br>'k'                  | Proce:<br>Data        |                    | /rite to<br>VREG |  |  |  |

| Example:         | ANDLW                                | 0x5F                  |                    |                  |  |  |  |

| Carry     | bit=  | 1    |

|-----------|-------|------|

| REG       | =     | 0x02 |

| WREG      | =     | 0x4D |

| or Inetru | otion |      |

## After Instruction

| Carry | bit= | 0    |

|-------|------|------|

| REG   | =    | 0x02 |

| WREG  | =    | 0x50 |

**Before Instruction** WREG = 0xA3

#### After Instruction

WREG =  $0 \times 03$

address (HERE)

address (Jump)

0; address (HERE+2)

| BTG   |                          | Bit Toggl                                                                                                                                                                                                           | e f             |                       | ВС           | v                              | Branch if                                                                                                                                                                                                      | Branch if Overflow                                       |             |  |  |

|-------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|--------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------|--|--|

| Synt  | ax:                      | [label] B                                                                                                                                                                                                           | STG f,b[,a]     |                       | Sy           | ntax:                          | [ <i>label</i> ] B                                                                                                                                                                                             | [ <i>label</i> ] BOV n                                   |             |  |  |

| Oper  | rands:                   | 0 ≤ f ≤ 25                                                                                                                                                                                                          | 5               |                       | Ор           | Operands: $-128 \le n \le 127$ |                                                                                                                                                                                                                |                                                          |             |  |  |

|       |                          | 0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                                                                              |                 |                       | Ор           | eration:                       |                                                                                                                                                                                                                | if overflow bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC |             |  |  |

| Oper  | ration:                  | $(\overline{f} < b >) \rightarrow 1$                                                                                                                                                                                | f <b></b>       |                       | Sta          | atus Affected:                 | None                                                                                                                                                                                                           | None                                                     |             |  |  |

| Statu | us Affected:             | None                                                                                                                                                                                                                | None            |                       |              | coding:                        | 1110                                                                                                                                                                                                           | 0100 nn                                                  | nn nnnn     |  |  |

| Enco  | oding:                   | 0111                                                                                                                                                                                                                | bbba f          | fff ffff              |              | scription:                     | If the Ove                                                                                                                                                                                                     | rflow bit is '1                                          | , then the  |  |  |

| Desc  | cription:                | Bit 'b' in data memory location 'f' is<br>inverted. If 'a' is 0, the Access Bank<br>will be selected, overriding the BSR<br>value. If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default). |                 |                       |              |                                | program will branch.<br>The 2's complement number '2n' i<br>added to the PC. Since the PC wi<br>have incremented to fetch the nex<br>instruction, the new address will be<br>PC+2+2n. This instruction is then |                                                          |             |  |  |

| Word  | ds:                      | 1                                                                                                                                                                                                                   |                 |                       |              |                                | a two-cycl                                                                                                                                                                                                     | e instruction                                            |             |  |  |

| Cycl  | es:                      | 1                                                                                                                                                                                                                   | 1               |                       |              | ords:                          | 1                                                                                                                                                                                                              |                                                          |             |  |  |

| QC    | vcle Activity            |                                                                                                                                                                                                                     |                 |                       | Су           | cles:                          | 1(2)                                                                                                                                                                                                           |                                                          |             |  |  |

|       | Q1                       | Q2                                                                                                                                                                                                                  | Q3              | Q4                    |              | Cycle Activity                 | <i>r</i> :                                                                                                                                                                                                     |                                                          |             |  |  |

|       | Decode                   | Read<br>register 'f'                                                                                                                                                                                                | Process<br>Data | Write<br>register 'f' | lf -         | Jump:<br>Q1                    | Q2                                                                                                                                                                                                             | Q3                                                       | Q4          |  |  |

| Exar  | nole:                    |                                                                                                                                                                                                                     | PORTC, 4,       |                       |              | Decode                         | Read literal<br>'n'                                                                                                                                                                                            | Process<br>Data                                          | Write to PC |  |  |

|       | Before Instru            |                                                                                                                                                                                                                     |                 | •                     |              | No                             | No                                                                                                                                                                                                             | No                                                       | No          |  |  |

|       | PORTC                    |                                                                                                                                                                                                                     | 0101 [0x75]     |                       | 14           | operation                      | operation                                                                                                                                                                                                      | operation                                                | operation   |  |  |

|       | After Instruc            | tion:                                                                                                                                                                                                               |                 |                       | If           | No Jump:                       | 00                                                                                                                                                                                                             | 00                                                       | 04          |  |  |

|       | PORTC = 0110 0101 [0x65] |                                                                                                                                                                                                                     |                 |                       | Q1<br>Decode | Q2<br>Read literal             | Q3<br>Process                                                                                                                                                                                                  | Q4<br>No                                                 |             |  |  |

|       |                          |                                                                                                                                                                                                                     |                 |                       |              | Decode                         | 'n'                                                                                                                                                                                                            | Data                                                     | operation   |  |  |

|       |                          |                                                                                                                                                                                                                     |                 |                       | <u>Ex</u>    | ample:                         | HERE                                                                                                                                                                                                           | BOV Jump                                                 |             |  |  |

**Before Instruction** PC

After Instruction If Overflow=

=

PC =

If Overflow= PC =

1;

| GOT   | GOTO Unconditional Branch               |                                                                                |                                           |                           |                     |                                        |

|-------|-----------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------|---------------------------|---------------------|----------------------------------------|

| Synt  | ax:                                     | [ label ]                                                                      | GOTO                                      | k                         |                     |                                        |

| Ope   | rands:                                  | $0 \le k \le 10$                                                               | )48575                                    |                           |                     |                                        |

| Ope   | ration:                                 | $k \rightarrow PC < 2$                                                         | 20:1>                                     |                           |                     |                                        |

| Statu | us Affected:                            | None                                                                           |                                           |                           |                     |                                        |

| 1st v | oding:<br>vord (k<7:0>)<br>word(k<19:8> | .) 1110                                                                        | 1111<br>k <sub>19</sub> kkk               | k <sub>7</sub> ki<br>kkk  |                     | kkkk <sub>0</sub><br>kkkk <sub>8</sub> |

| Deso  | cription:                               | GOTO allo<br>branch ar<br>2 Mbyte r<br>value 'k' i<br>GOTO is a<br>instruction | nywhere<br>nemory<br>s loaded<br>Ilways a | within<br>range<br>I into | n en<br>. Th<br>PC< | tire<br>ne 20-bit<br><20:1>.           |

| Wore  | ds:                                     | 2                                                                              |                                           |                           |                     |                                        |

| Cycl  | es:                                     | 2                                                                              |                                           |                           |                     |                                        |

| QC    | ycle Activity:                          |                                                                                |                                           |                           |                     |                                        |

|       | Q1                                      | Q2                                                                             | Q                                         | 3                         |                     | Q4                                     |

|       | Decode                                  | Read literal<br>'k'<7:0>,                                                      | No<br>operat                              |                           |                     | ad literal<br><19:8>,                  |

| Decode    | Read literal<br>'k'<7:0>, | No<br>operation | Read literal<br>'k'<19:8>,<br>Write to PC |

|-----------|---------------------------|-----------------|-------------------------------------------|

| No        | No                        | No              | No                                        |

| operation | operation                 | operation       | operation                                 |

Example: GOTO THERE

After Instruction

PC = Address (THERE)

| INCF                      | Incremen                                                                                                                                                                                                                                                                                        | t f          |           |    |                                             |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|----|---------------------------------------------|

| Syntax:                   | [ label ]                                                                                                                                                                                                                                                                                       | INCF         | f [,d [,a | a] |                                             |

| Operands:                 | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                             | 5            |           |    |                                             |