Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                              |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 32KB (16K x 16)                                                         |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1.5K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c452-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 1.0 DEVICE OVERVIEW

This document contains device specific information for the following four devices:

- 1. PIC18C242

- 2. PIC18C252

- 3. PIC18C442

- 4. PIC18C452

These devices come in 28-pin and 40-pin packages. The 28-pin devices do not have a Parallel Slave Port (PSP) implemented and the number of Analog-to-Digital (A/D) converter input channels is reduced to 5. An overview of features is shown in Table 1-1.

# The following two figures are device block diagrams sorted by pin count: 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-2 and Table 1-3, respectively.

| Features                           | PIC18C242                                                                        | PIC18C252                                                                        | PIC18C442                                                                        | PIC18C452                                                                        |

|------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Operating Frequency                | DC - 40 MHz                                                                      |

| Program Memory (Bytes)             | 16K                                                                              | 32K                                                                              | 16K                                                                              | 32K                                                                              |

| Program Memory (Instructions)      | 8192                                                                             | 16384                                                                            | 8192                                                                             | 16384                                                                            |

| Data Memory (Bytes)                | 512                                                                              | 1536                                                                             | 512                                                                              | 1536                                                                             |

| Interrupt Sources                  | 16                                                                               | 16                                                                               | 17                                                                               | 17                                                                               |

| I/O Ports                          | Ports A, B, C                                                                    | Ports A, B, C                                                                    | Ports A, B, C, D, E                                                              | Ports A, B, C, D, E                                                              |

| Timers                             | 4                                                                                | 4                                                                                | 4                                                                                | 4                                                                                |

| Capture/Compare/PWM Modules        | 2                                                                                | 2                                                                                | 2                                                                                | 2                                                                                |

| Serial Communications              | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    |

| Parallel Communications            | —                                                                                | —                                                                                | PSP                                                                              | PSP                                                                              |

| 10-bit Analog-to-Digital Module    | 5 input channels                                                                 | 5 input channels                                                                 | 8 input channels                                                                 | 8 input channels                                                                 |

| RESETS (and Delays)                | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST) |

| Programmable Low Voltage<br>Detect | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |

| Programmable Brown-out Reset       | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |

| Instruction Set                    | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  |

| Packages                           | 28-pin DIP<br>28-pin SOIC<br>28-pin JW                                           | 28-pin DIP<br>28-pin SOIC<br>28-pin JW                                           | 40-pin DIP<br>44-pin PLCC<br>44-pin TQFP<br>40-pin JW                            | 40-pin DIP<br>44-pin PLCC<br>44-pin TQFP<br>40-pin JW                            |

#### TABLE 1-1: DEVICE FEATURES

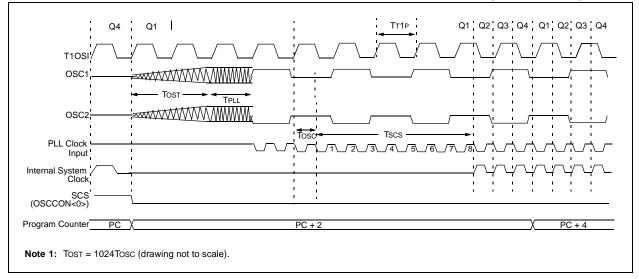

If the main oscillator is configured for HS-PLL mode, an oscillator start-up time (Tost) plus an additional PLL time-out (TPLL) will occur. The PLL time-out is typically 2 ms and allows the PLL to lock to the main oscillator

frequency. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for HS-PLL mode, is shown in Figure 2-10.

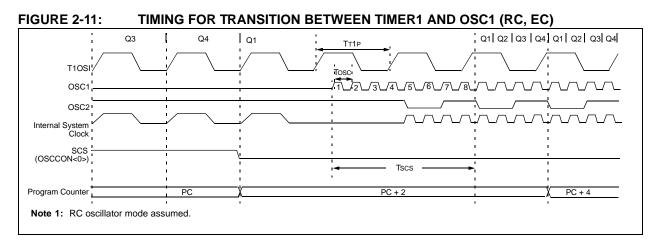

If the main oscillator is configured in the RC, RCIO, EC or ECIO modes, there is no oscillator start-up time-out. Operation will resume after eight cycles of the main oscillator have been counted. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for RC, RCIO, EC and ECIO modes, is shown in Figure 2-11.

| Register | Applicable Devices |     | Power-on Reset,<br>Brown-out Reset | MCLR<br>WDT I<br>RESET In<br>Stack F | Reset<br>struction | Wake-up via WDT<br>or Interrupt |      |      |                 |

|----------|--------------------|-----|------------------------------------|--------------------------------------|--------------------|---------------------------------|------|------|-----------------|

| ADRESH   | 242                | 442 | 252                                | 452                                  | xxxx xxxx          | uuuu                            | uuuu | uuuu | uuuu            |

| ADRESL   | 242                | 442 | 252                                | 452                                  | xxxx xxxx          | uuuu                            | uuuu | uuuu | uuuu            |

| ADCON0   | 242                | 442 | 252                                | 452                                  | 0000 0000          | 0000                            | 0000 | uuuu | uuuu            |

| ADCON1   | 242                | 442 | 252                                | 452                                  | 0- 0000            | 0 -                             | 0000 | u-   | uuuu            |

| CCPR1H   | 242                | 442 | 252                                | 452                                  | xxxx xxxx          | uuuu                            | uuuu | uuuu | uuuu            |

| CCPR1L   | 242                | 442 | 252                                | 452                                  | xxxx xxxx          | uuuu                            | uuuu | uuuu | uuuu            |

| CCP1CON  | 242                | 442 | 252                                | 452                                  | 00 0000            | 0 0                             | 0000 | uu   | uuuu            |

| CCPR2H   | 242                | 442 | 252                                | 452                                  | xxxx xxxx          | uuuu                            | uuuu | uuuu | uuuu            |

| CCPR2L   | 242                | 442 | 252                                | 452                                  | xxxx xxxx          | uuuu                            | uuuu | uuuu | uuuu            |

| CCP2CON  | 242                | 442 | 252                                | 452                                  | 00 0000            | 0 0                             | 0000 | uu   | uuuu            |

| TMR3H    | 242                | 442 | 252                                | 452                                  | xxxx xxxx          | uuuu                            | uuuu | uuuu | uuuu            |

| TMR3L    | 242                | 442 | 252                                | 452                                  | xxxx xxxx          | uuuu                            | uuuu | uuuu | uuuu            |

| T3CON    | 242                | 442 | 252                                | 452                                  | 0000 0000          | uuuu                            | uuuu | uuuu | uuuu            |

| SPBRG    | 242                | 442 | 252                                | 452                                  | xxxx xxxx          | uuuu                            | uuuu | uuuu | uuuu            |

| RCREG    | 242                | 442 | 252                                | 452                                  | xxxx xxxx          | uuuu                            | uuuu | uuuu | uuuu            |

| TXREG    | 242                | 442 | 252                                | 452                                  | xxxx xxxx          | uuuu                            | uuuu | uuuu | uuuu            |

| TXSTA    | 242                | 442 | 252                                | 452                                  | 0000 -01x          | 0000                            | -01u | uuuu | -uuu            |

| RCSTA    | 242                | 442 | 252                                | 452                                  | 0000 000x          | 0000                            | 000u | uuuu | uuuu            |

| IPR2     | 242                | 442 | 252                                | 452                                  | 1111               |                                 | 1111 |      | uuuu            |

| PIR2     | 242                | 442 | 252                                | 452                                  | 0000               |                                 | 0000 |      | սսսս <b>(1)</b> |

| PIE2     | 242                | 442 | 252                                | 452                                  | 0000               |                                 | 0000 |      | uuuu            |

| IPR1     | 242                | 442 | 252                                | 452                                  | 1111 1111          | 1111                            | 1111 | uuuu | uuuu            |

|          | 242                | 442 | 252                                | 452                                  | -111 1111          | -111                            | 1111 |      | uuuu            |

| PIR1     | 242                | 442 | 252                                | 452                                  | 0000 0000          | 0000                            | 0000 | uuuu | սսսս <b>(1)</b> |

|          | 242                | 442 | 252                                | 452                                  | -000 0000          | -000                            | 0000 | -uuu | սսսս <b>(1)</b> |

| PIE1     | 242                | 442 | 252                                | 452                                  | 0000 0000          | 0000                            | 0000 | uuuu | uuuu            |

|          | 242                | 442 | 252                                | 452                                  | -000 0000          | -000                            | 0000 | -uuu | uuuu            |

#### TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for RESET value for specific condition.

- 5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

- **6:** The long write enable is only reset on a POR or  $\overline{\text{MCLR}}$  Reset.

- 7: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read as '0'.

| TABLE 4-2: | REGISTER FILE SUMMARY (CONTINUED) |

|------------|-----------------------------------|

|------------|-----------------------------------|

| File Name | Bit 7       | Bit 6                         | Bit 5                      | Bit 4          | Bit 3         | Bit 2                         | Bit 1        | Bit 0   | Value on<br>POR,<br>BOR | Details<br>on page: |  |

|-----------|-------------|-------------------------------|----------------------------|----------------|---------------|-------------------------------|--------------|---------|-------------------------|---------------------|--|

| WDTCON    | -           | —                             | —                          | —              | —             | -                             | _            | SWDTE   | 0                       | 183                 |  |

| RCON      | IPEN        | LWRT                          | —                          | RI             | TO            | PD                            | POR          | BOR     | 0q-1 11qq               | 53, 56,<br>74       |  |

| TMR1H     | Timer1 Reg  | ister High Byte               |                            | XXXX XXXX      | 97            |                               |              |         |                         |                     |  |

| TMR1L     | Timer1 Reg  | Timer1 Register Low Byte      |                            |                |               |                               |              |         |                         |                     |  |

| T1CON     | RD16        | _                             | T1CKPS1                    | T1CKPS0        | T1OSCEN       | T1SYNC                        | TMR1CS       | TMR10N  | 0-00 0000               | 97                  |  |

| TMR2      | Timer2 Reg  | ister                         |                            |                |               |                               |              |         | 0000 0000               | 101                 |  |

| PR2       | Timer2 Peri | od Register                   |                            |                |               |                               |              |         | 1111 1111               | 102                 |  |

| T2CON     |             | TOUTPS3                       | TOUTPS2                    | TOUTPS1        | TOUTPS0       | TMR2ON                        | T2CKPS1      | T2CKPS0 | -000 0000               | 101                 |  |

| SSPBUF    | SSP Receiv  | /e Buffer/Trans               | smit Register              |                |               |                               |              |         | xxxx xxxx               | 121                 |  |

| SSPADD    | SSP Addres  | ss Register in I              | I <sup>2</sup> C Slave Mod | le. SSP Baud F | Rate Reload R | egister in I <sup>2</sup> C I | Master Mode. |         | 0000 0000               | 128                 |  |

| SSPSTAT   | SMP         | CKE                           | D/A                        | Р              | S             | R/W                           | UA           | BF      | 0000 0000               | 116                 |  |

| SSPCON1   | WCOL        | SSPOV                         | SSPEN                      | CKP            | SSPM3         | SSPM2                         | SSPM1        | SSPM0   | 0000 0000               | 118                 |  |

| SSPCON2   | GCEN        | ACKSTAT                       | ACKDT                      | ACKEN          | RCEN          | PEN                           | RSEN         | SEN     | 0000 0000               | 120                 |  |

| ADRESH    | A/D Result  | A/D Result Register High Byte |                            |                |               |                               |              |         |                         |                     |  |

| ADRESL    | A/D Result  | Register Low E                | Byte                       |                |               |                               |              |         | xxxx xxxx               | 171,172             |  |

| ADCON0    | ADCS1       | ADCS0                         | CHS2                       | CHS1           | CHS0          | GO/DONE                       | _            | ADON    | 0000 00-0               | 165                 |  |

| ADCON1    | ADFM        | ADCS2                         | _                          | _              | PCFG3         | PCFG2                         | PCFG1        | PCFG0   | 00 0000                 | 166                 |  |

| CCPR1H    | Capture/Co  | mpare/PWM R                   | Register1 High             | Byte           |               |                               |              |         | xxxx xxxx               | 111, 113            |  |

| CCPR1L    | Capture/Co  | mpare/PWM R                   | Register1 Low              | Byte           |               |                               |              |         | xxxx xxxx               | 111, 113            |  |

| CCP1CON   | _           | _                             | DC1B1                      | DC1B0          | CCP1M3        | CCP1M2                        | CCP1M1       | CCP1M0  | 00 0000                 | 107                 |  |

| CCPR2H    | Capture/Co  | mpare/PWM R                   | Register2 High             | Byte           |               |                               |              |         | xxxx xxxx               | 111, 113            |  |

| CCPR2L    | Capture/Co  | mpare/PWM R                   | Register2 Low              | Byte           |               |                               |              |         | xxxx xxxx               | 111, 113            |  |

| CCP2CON   | _           | _                             | DC2B1                      | DC2B0          | CCP2M3        | CCP2M2                        | CCP2M1       | CCP2M0  | 00 0000                 | 107                 |  |

| TMR3H     | Timer3 Reg  | ister High Byte               | 9                          |                |               |                               |              |         | xxxx xxxx               | 103                 |  |

| TMR3L     | Timer3 Reg  | ister Low Byte                |                            |                |               |                               |              |         | xxxx xxxx               | 103                 |  |

| T3CON     | RD16        | T3CCP2                        | T3CKPS1                    | T3CKPS0        | T3CCP1        | T3SYNC                        | TMR3CS       | TMR3ON  | 0000 0000               | 103                 |  |

| SPBRG     | USART1 Ba   | aud Rate Gene                 | erator                     |                |               |                               |              |         | 0000 0000               | 151                 |  |

| RCREG     | USART1 Re   | eceive Registe                | r                          |                |               |                               |              |         | 0000 0000               | 158, 161,<br>163    |  |

| TXREG     | USART1 Tr   | ansmit Registe                | er                         |                |               |                               |              |         | 0000 0000               | 156, 159,<br>162    |  |

| TXSTA     | CSRC        | TX9                           | TXEN                       | SYNC           | —             | BRGH                          | TRMT         | TX9D    | 0000 -010               | 149                 |  |

| RCSTA     | SPEN        | RX9                           | SREN                       | CREN           | ADDEN         | FERR                          | OERR         | RX9D    | 0000 000x               | 150                 |  |

Legend: x = unknown, u = unchanged, - = unimplemented, g = value depends on condition

Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO oscillator mode only, and read '0' in all other oscillator modes.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

#### **REGISTER FILE SUMMARY (CONTINUED) TABLE 4-2:**

| File Name | Bit 7                                     | Bit 6                                                | Bit 5                                                | Bit 4           | Bit 3          | Bit 2                     | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Details<br>on page: |

|-----------|-------------------------------------------|------------------------------------------------------|------------------------------------------------------|-----------------|----------------|---------------------------|--------|--------|-------------------------|---------------------|

| IPR2      | _                                         | _                                                    | _                                                    | —               | 1111           | 73                        |        |        |                         |                     |

| PIR2      | —                                         | —                                                    | _                                                    | —               | 0000           | 69                        |        |        |                         |                     |

| PIE2      | _                                         | _                                                    | _                                                    | _               | 0000           | 71                        |        |        |                         |                     |

| IPR1      | PSPIP                                     | ADIP                                                 | RCIP                                                 | TXIP            | SSPIP          | CCP1IP                    | TMR2IP | TMR1IP | 1111 1111               | 72                  |

| PIR1      | PSPIF                                     | ADIF                                                 | RCIF                                                 | TXIF            | SSPIF          | CCP1IF                    | TMR2IF | TMR1IF | 0000 0000               | 68                  |

| PIE1      | PSPIE                                     | ADIE                                                 | RCIE                                                 | TXIE            | SSPIE          | CCP1IE                    | TMR2IE | TMR1IE | 0000 0000               | 70                  |

| TRISE     | IBF                                       | IBF OBF IBOV PSPMODE — Data Direction bits for PORTE |                                                      |                 |                |                           |        |        |                         |                     |

| TRISD     | Data Directi                              | Data Direction Control Register for PORTD            |                                                      |                 |                |                           |        |        |                         |                     |

| TRISC     | Data Direction Control Register for PORTC |                                                      |                                                      |                 |                |                           |        |        |                         | 83                  |

| TRISB     | Data Direction Control Register for PORTB |                                                      |                                                      |                 |                |                           |        |        |                         | 80                  |

| TRISA     | _                                         | TRISA6 <sup>(1)</sup>                                | Data Directi                                         | on Control Reg  | ister for PORT | A                         |        |        | -111 1111               | 77                  |

| LATE      | -                                         | —                                                    | — — Read PORTE Data Latch,<br>Write PORTE Data Latch |                 |                |                           |        |        |                         | 87                  |

| LATD      | Read PORT                                 | D Data Latch,                                        | Write PORTE                                          | Data Latch      | •              |                           |        |        | xxxx xxxx               | 85                  |

| LATC      | Read PORT                                 | C Data Latch,                                        | Write PORTO                                          | C Data Latch    |                |                           |        |        | xxxx xxxx               | 83                  |

| LATB      | Read PORT                                 | B Data Latch,                                        | Write PORTE                                          | B Data Latch    |                |                           |        |        | xxxx xxxx               | 80                  |

| LATA      | _                                         | LATA6 <sup>(1)</sup>                                 | Read PORT                                            | A Data Latch, V | Write PORTA    | Data Latch <sup>(1)</sup> |        |        | -xxx xxxx               | 77                  |

| PORTE     | Read PORT                                 | E pins, Write                                        | PORTE Data                                           | Latch           |                |                           |        |        | 000                     | 87                  |

| PORTD     | Read PORT                                 | D pins, Write                                        | PORTD Data                                           | Latch           |                |                           |        |        | xxxx xxxx               | 85                  |

| PORTC     | Read PORT                                 | C pins, Write                                        | PORTC Data                                           | Latch           |                |                           |        |        | xxxx xxxx               | 83                  |

| PORTB     | Read PORT                                 | B pins, Write                                        | PORTB Data                                           | Latch           |                |                           |        |        | xxxx xxxx               | 80                  |

| PORTA     | —                                         | RA6 <sup>(1)</sup>                                   | Read PORT                                            | A pins, Write P | ORTA Data La   | atch <sup>(1)</sup>       |        |        | -x0x 0000               | 77                  |

Legend: x = unknown, u = unchanged, - = unimplemented, g = value depends on condition

Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO oscillator mode only, and read '0' in all other oscillator modes.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

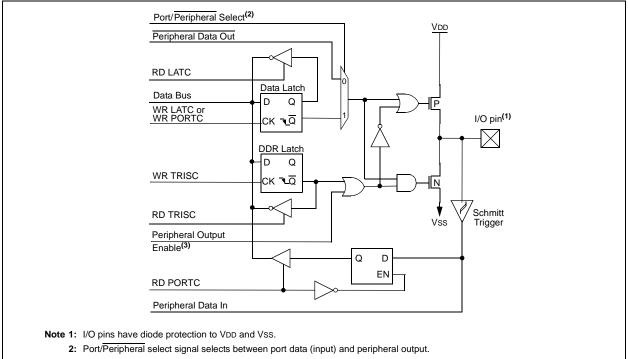

#### 8.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bi-directional port. The corresponding Data Direction Register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

| Note: | On a Power-on Reset, these pins are con- |

|-------|------------------------------------------|

|       | figured as digital inputs.               |

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register reads and writes the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 8-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings. The pin override value is not loaded into the TRIS register. This allows read-modify-write of the TRIS register, without concern due to peripheral overrides.

RC1 is normally configured by the configuration bit CCP2MX as the default peripheral pin for the CCP2 module (default/erased state, CCP2MX = '1').

| EXAMPLE 0-3: INITIALIZING PURIC | XAMPLE 8-3: | INITIALIZING PORTC |

|---------------------------------|-------------|--------------------|

|---------------------------------|-------------|--------------------|

| CLRF  | PORTC | ; Initialize PORTC by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATC  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0xCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISC | ; Set RC<3:0> as inputs |

|       |       | ; RC<5:4> as outputs    |

|       |       | ; RC<7:6> as inputs     |

|       |       |                         |

#### FIGURE 8-7: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

**3:** Peripheral Output Enable is only active if peripheral select is active.

#### 13.3 Capture Mode

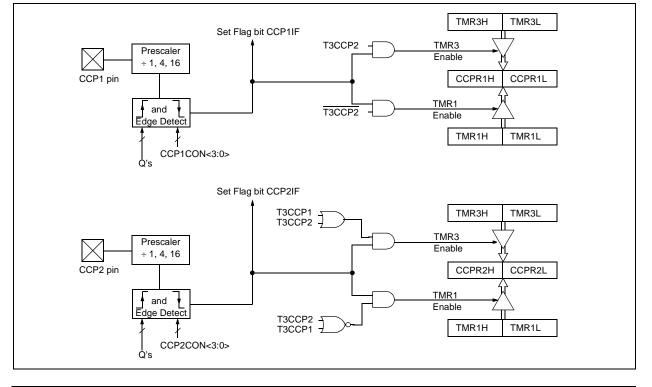

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on pin RC2/CCP1. An event is defined as:

- · every falling edge

- every rising edge

- every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 13.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-                |

|-------|---------------------------------------------------------|

|       | put, a write to the port can cause a capture condition. |

|       | oonalion.                                               |

#### 13.3.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (either Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each CCP module is selected in the T3CON register.

#### 13.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 13.3.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 13-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 13-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON, F  | ; | Turn CCP module off |

|-------|-------------|---|---------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the  |

|       |             | ; | new prescaler mode  |

|       |             | ; | value and CCP ON    |

| MOVWF | CCP1CON     | ; | Load CCP1CON with   |

|       |             | ; | this value          |

|       |             |   |                     |

#### FIGURE 13-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

NOTES:

#### 14.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2).

#### REGISTER 14-1: SSPSTAT: MSSP STATUS REGISTER

- n = Value at POR

'1' = Bit is set

|       | R/W-0                                              | R/W-0                                                                                      | R-0                      | R-0            | R-0             | R-0             | R-0            | R-0      |  |  |  |  |

|-------|----------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------|----------------|-----------------|-----------------|----------------|----------|--|--|--|--|

|       | SMP                                                | CKE                                                                                        | D/A                      | Р              | S               | R/W             | UA             | BF       |  |  |  |  |

|       | bit 7                                              | 1                                                                                          | 1                        |                |                 |                 |                | bit 0    |  |  |  |  |

| bit 7 | SMP: Sam                                           | nlo hit                                                                                    |                          |                |                 |                 |                |          |  |  |  |  |

|       | SPI Master                                         | •                                                                                          |                          |                |                 |                 |                |          |  |  |  |  |

|       |                                                    |                                                                                            | l at end of da           | ata outout tii | me              |                 |                |          |  |  |  |  |

|       | -                                                  |                                                                                            | l at middle o            |                |                 |                 |                |          |  |  |  |  |

|       |                                                    | SPI Slave mode:                                                                            |                          |                |                 |                 |                |          |  |  |  |  |

|       | SMP must be cleared when SPI is used in Slave mode |                                                                                            |                          |                |                 |                 |                |          |  |  |  |  |

|       |                                                    | In J <sup>2</sup> C Master or Slave mode:                                                  |                          |                |                 |                 |                |          |  |  |  |  |

|       |                                                    | <ol> <li>Slew rate control disabled for standard speed mode (100 kHz and 1 MHz)</li> </ol> |                          |                |                 |                 |                |          |  |  |  |  |

|       | 0 = Slew r                                         | ate control e                                                                              | enabled for h            | nigh speed r   | node (400 kl    | Hz)             |                |          |  |  |  |  |

| bit 6 | CKE: SPI (                                         | Clock Edge                                                                                 | Select bit               |                |                 |                 |                |          |  |  |  |  |

|       | <u>CKP = 0:</u>                                    |                                                                                            |                          |                |                 |                 |                |          |  |  |  |  |

|       | 1 = Data tra                                       | ansmitted or                                                                               | n rising edge            | e of SCK       |                 |                 |                |          |  |  |  |  |

|       | 0 = Data tra                                       | ansmitted or                                                                               | n falling edg            | e of SCK       |                 |                 |                |          |  |  |  |  |

|       | <u>CKP = 1:</u>                                    |                                                                                            |                          |                |                 |                 |                |          |  |  |  |  |

|       |                                                    |                                                                                            | n falling edg            |                |                 |                 |                |          |  |  |  |  |

|       |                                                    |                                                                                            | n rising edge            |                |                 |                 |                |          |  |  |  |  |

| bit 5 |                                                    |                                                                                            | (I <sup>2</sup> C mode o |                |                 |                 |                |          |  |  |  |  |

|       |                                                    |                                                                                            | •                        |                | smitted was     |                 |                |          |  |  |  |  |

|       | 0 = Indicate                                       | es that the la                                                                             | ast byte rece            | eived or tran  | smitted was     | address         |                |          |  |  |  |  |

| bit 4 | P: STOP b                                          |                                                                                            |                          |                |                 |                 |                |          |  |  |  |  |

|       | •                                                  | •                                                                                          |                          |                |                 |                 | SSPEN is c     | leared.) |  |  |  |  |

|       |                                                    |                                                                                            |                          |                | ed last (this b | oit is '0' on R | ESET)          |          |  |  |  |  |

|       | 0 = STOP                                           | bit was not c                                                                              | letected last            |                |                 |                 |                |          |  |  |  |  |

|       | Legend:                                            |                                                                                            |                          |                |                 |                 |                |          |  |  |  |  |

|       | R = Reada                                          | ble bit                                                                                    | W = Writab               | le bit         | U = Unimpl      | emented bit     | t, read as '0' |          |  |  |  |  |

|       |                                                    |                                                                                            |                          |                | 2 Simp          |                 | ,              |          |  |  |  |  |

'0' = Bit is cleared

x = Bit is unknown

### 15.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

In order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter:

- bit SPEN (RCSTA<7>) must be set (= 1), and

- bits TRISC<7:6> must be cleared (= 0).

Register 15-1 shows the Transmit Status and Control Register (TXSTA) and Register 15-2 shows the Receive Status and Control Register (RCSTA).

#### REGISTER 15-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

|       | R/W-0                                                                         | R/W-0                                               | R/W-0          | R/W-0       | U-0          | R/W-0       | R-1            | R/W-0 |

|-------|-------------------------------------------------------------------------------|-----------------------------------------------------|----------------|-------------|--------------|-------------|----------------|-------|

|       | CSRC                                                                          | TX9                                                 | TXEN           | SYNC        |              | BRGH        | TRMT           | TX9D  |

|       | bit 7                                                                         |                                                     |                |             |              |             |                | bit 0 |

| bit 7 | Asynchron<br>Don't care<br>Synchrono<br>1 = Master                            |                                                     | generated in   | •           | BRG)         |             |                |       |

| bit 6 | 1 = Selects                                                                   | Transmit Enal<br>s 9-bit transmi<br>s 8-bit transmi | ission         |             |              |             |                |       |

| bit 5 | 1 = Transm                                                                    | nsmit Enable<br>nit enabled<br>nit disabled         | bit            |             |              |             |                |       |

|       | Note:                                                                         | SREN/CREN                                           | l overrides T  | XEN in SYN  | C mode.      |             |                |       |

| bit 4 | 1 = Synchr                                                                    | ART Mode Se<br>onous mode<br>nronous mode           |                |             |              |             |                |       |

| bit 3 | Unimplem                                                                      | ented: Read                                         | as '0'         |             |              |             |                |       |

| bit 2 | BRGH: Hig<br>Asynchron<br>1 = High sp<br>0 = Low sp<br>Synchrono<br>Unused in | beed<br>beed<br><u>us mode:</u>                     | Select bit     |             |              |             |                |       |

| bit 1 | <b>TRMT</b> : Trai<br>1 = TSR er<br>0 = TSR fu                                |                                                     | egister Status | s bit       |              |             |                |       |

| bit 0 | <b>TX9D:</b> 9th                                                              | bit of transmit                                     | t data. Can b  | e Address/D | ata bit or a | parity bit. |                |       |

|       | Legend:                                                                       |                                                     |                |             |              |             |                |       |

|       | R = Reada                                                                     | ble bit                                             | W = Wri        | table bit   | U = Unimp    | lemented b  | oit, read as ' | 0'    |

|                  | - 3                      |                  |                      |                    |  |

|------------------|--------------------------|------------------|----------------------|--------------------|--|

| R = Readable bit |                          | W = Writable bit | U = Unimplemented    | bit, read as '0'   |  |

|                  | - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

The value that is in the ADRESH/ADRESL registers is not modified for a Power-on Reset. The ADRESH/ ADRESL registers will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 16.1. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- · Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear ADIF bit

- Set ADIE bit

- · Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared

OR

- Waiting for the A/D interrupt

- 6. Read A/D Result registers (ADRESH/ADRESL); clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

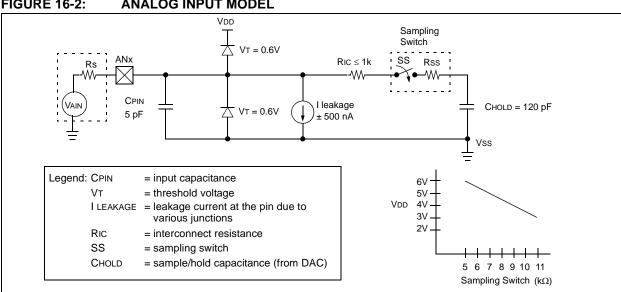

#### **FIGURE 16-2:** ANALOG INPUT MODEL

#### 16.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 16-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

When the conversion is started, the hold-Note: ing capacitor is disconnected from the input pin.

#### 17.2.1 REFERENCE VOLTAGE SET POINT

The Internal Reference Voltage of the LVD module may be used by other internal circuitry (the Programmable Brown-out Reset). If these circuits are disabled (lower current consumption), the reference voltage circuit requires a time to become stable before a low voltage condition can be reliably detected. This time is invariant of system clock speed. This start-up time is specified in electrical specification parameter #36. The low voltage interrupt flag will not be enabled until a stable reference voltage is reached. Refer to the waveform in Figure 17-4.

#### 17.2.2 CURRENT CONSUMPTION

When the module is enabled, the LVD comparator and voltage divider are enabled and will consume static current. The voltage divider can be tapped from multiple places in the resistor array. Total current consumption, when enabled, is specified in electrical specification parameter #D022B.

#### 17.3 Operation During SLEEP

When enabled, the LVD circuitry continues to operate during SLEEP. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from SLEEP. Device execution will continue from the interrupt vector address, if interrupts have been globally enabled.

#### 17.4 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the LVD module to be turned off.

| BRA                | A Contraction of the second seco | Unconditi                         | ional Branc                  | h                                                 | BSF       |                                | Bit Set f            |                                                                                                                                                                      |                       |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------|---------------------------------------------------|-----------|--------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|

| Synt               | tax:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | [ <i>label</i> ] BRA n            |                              | Syntax                                            | x:        | [ <i>label</i> ] B             | [label] BSF f,b[,a]  |                                                                                                                                                                      |                       |  |  |

| Operands:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -1024 ≤ n                         | $-1024 \le n \le 1023$       |                                                   |           | Operands:                      |                      | $0 \le f \le 255$                                                                                                                                                    |                       |  |  |

| Ope                | ration:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $(PC) + 2 + 2n \to PC$            |                              |                                                   |           |                                | $0 \le b \le 7$      |                                                                                                                                                                      |                       |  |  |

| State              | us Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | None                              |                              |                                                   | Onoro     | tion                           |                      | a ∈ [0,1]                                                                                                                                                            |                       |  |  |

| Enco               | oding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1101 Onnn nnnn nnnn               |                              |                                                   | -         | Operation:<br>Status Affected: |                      | $1 \rightarrow f < b >$                                                                                                                                              |                       |  |  |

| Des                | cription:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Add the 2'                        | s compleme                   | nt number                                         |           |                                |                      | None                                                                                                                                                                 |                       |  |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '2n' to the PC. Since the PC will |                              |                                                   | Encoding: |                                | 1000                 | bbba ffi                                                                                                                                                             |                       |  |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | instruction                       | , the new ad<br>This instruc | etch the next<br>dress will be<br>ction is a two- |           | Description:                   |                      | Bit 'b' in register 'f' is set. If 'a' is 0<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' = 1, then<br>the bank will be selected as per the |                       |  |  |

| Wor                | ds:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                 |                              |                                                   |           |                                | BSR value            | <b>)</b> .                                                                                                                                                           |                       |  |  |