Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                              |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 32KB (16K x 16)                                                         |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1.5K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c452-i-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

NOTES:

### 7.6 INT0 Interrupt

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge triggered: either rising, if the corresponding INTEDGx bit is set in the INTCON2 register, or falling, if the INTEDGx bit is clear. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit INTxF is set. This interrupt can be disabled by clearing the corresponding enable bit INTxE. Flag bit INTxF must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt. All external interrupts (INT0, INT1 and INT2) can wake-up the processor from SLEEP, if bit INTxE was set prior to going into SLEEP. If the global interrupt enable bit GIE set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high priority interrupt source.

### 7.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF. In 16-bit mode, an overflow (FFFFh  $\rightarrow$  0000h) in the TMR0H:TMR0L registers will set flag bit TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit TOIE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit TMR0IP (INTCON2<2>). See Section 8.0 for further details on the Timer0 module.

## 7.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB Interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

## 7.9 Context Saving During Interrupts

During an interrupt, the return PC value is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see Section 4.3), the user may need to save the WREG, STATUS and BSR registers in software. Depending on the user's application, other registers may also need to be saved. Example 7-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| MOVWF  | W_TEMP              | ; W_TEMP is in virtual bank    |

|--------|---------------------|--------------------------------|

| MOVFF  | STATUS, STATUS_TEMP | ; STATUS_TEMP located anywhere |

| MOVFF  | BSR, BSR_TEMP       | ; BSR located anywhere         |

| ;      |                     |                                |

| ; USER | ISR CODE            |                                |

| ;      |                     |                                |

| MOVFF  | BSR_TEMP, BSR       | ; Restore BSR                  |

| MOVF   | W_TEMP, W           | ; Restore WREG                 |

| MOVFF  | STATUS TEMP, STATUS | ; Restore STATUS               |

|        | —                   |                                |

|        |                     |                                |

NOTES:

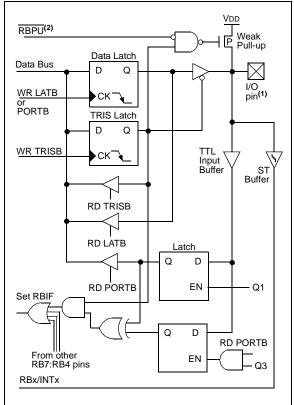

### 8.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

| Note: | On a Power-on Reset, these pins are con- |

|-------|------------------------------------------|

|       | figured as digital inputs.               |

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register reads and writes the latched output value for PORTB.

#### EXAMPLE 8-2: INITIALIZING PORTB

| CLRF  | PORTB | ; Initialize PORTB by<br>; clearing output |

|-------|-------|--------------------------------------------|

| CLRF  | LATB  | ; data latches<br>; Alternate method       |

| -     |       | ; to clear output                          |

| MOTTL | 007   | ; data latches                             |

| MOVLW | UXCF  | ; Value used to<br>; initialize data       |

|       |       | ; direction                                |

| MOVWF | TRISB | ; Set RB<3:0> as inputs                    |

|       |       | ; RB<5:4> as outputs                       |

|       |       | ; RB<7:6> as inputs                        |

|       |       |                                            |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overrightarrow{\text{RBPU}}$  (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins, RB7:RB4, have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF instruction). This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB3 can be configured by the configuration bit CCP2MX as the alternate peripheral pin for the CCP2 module (CCP2MX = (0)).

Note 1: I/O pins have diode protection to VDD and VSS.

2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (INTCON2<7>).

| Name            | Bit# | Buffer Type | Function                                                                                                                                    |

|-----------------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                                                                       |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin, Timer1 oscillator input, or Capture2 input/<br>Compare2 output/PWM output when CCP2MX configuration bit is disabled. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/<br>PWM1 output.                                                                    |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.                                                       |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or Data I/O ( $I^2$ C mode).                                                                     |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port Data output.                                                                               |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin, Addressable USART Asynchronous Transmit, or Addressable USART Synchronous Clock.                                     |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin, Addressable USART Asynchronous Receive, or Addressable USART Synchronous Data.                                       |

### TABLE 8-5: PORTC FUNCTIONS

Legend: ST = Schmitt Trigger input

### TABLE 8-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7                          | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|-------|--------------------------------|-----------|------------|-------|-------|-------|-------|-------|-------------------------|---------------------------------|

| PORTC | RC7                            | RC6       | RC5        | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx               | uuuu uuuu                       |

| LATC  | LATC LATC Data Output Register |           |            |       |       |       |       |       | xxxx xxxx               | uuuu uuuu                       |

| TRISC | PORTC                          | Data Dire | ection Reg | ister |       |       |       |       | 1111 1111               | 1111 1111                       |

Legend: x = unknown, u = unchanged

# 11.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match of PR2

- SSP module optional use of TMR2 output to generate clock shift

Timer2 has a control register shown in Register 11-1. Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption. Figure 11-1 is a simplified block diagram of the Timer2 module. Register 11-1 shows the Timer2 control register. The prescaler and postscaler selection of Timer2 are controlled by this register.

## 11.1 Timer2 Operation

Timer2 can be used as the PWM time-base for the PWM mode of the CCP module. The TMR2 register is readable and writable, and is cleared on any device RESET. The input clock (Fosc/4) has a prescale option of 1:1, 1:4, or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>). The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- a write to the T2CON register

- any device RESET (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

### REGISTER 11-1: T2CON: TIMER2 CONTROL REGISTER

|         | U-0      | R/W-0                         | R/W-0                | R/W-0         | R/W-0          | R/W-0      | R/W-0          | R/W-0   |

|---------|----------|-------------------------------|----------------------|---------------|----------------|------------|----------------|---------|

|         | —        | TOUTPS3                       | TOUTPS2              | TOUTPS1       | TOUTPS0        | TMR2ON     | T2CKPS1        | T2CKPS0 |

|         | bit 7    |                               |                      |               |                |            |                | bit 0   |

|         |          |                               |                      |               |                |            |                |         |

| bit 7   | Unimple  | emented: Re                   | ead as '0'           |               |                |            |                |         |

| bit 6-3 | TOUTPS   | S3:TOUTPS                     | <b>0</b> : Timer2 Ou | itput Postsca | le Select bits |            |                |         |

|         | 0000 =   | 1:1 Postscal                  | е                    |               |                |            |                |         |

|         | 0001 =   | 1:2 Postscal                  | e                    |               |                |            |                |         |

|         | •        |                               |                      |               |                |            |                |         |

|         | •        |                               |                      |               |                |            |                |         |

|         | •        | 1:16 Postsca                  |                      |               |                |            |                |         |

|         |          |                               |                      |               |                |            |                |         |

| bit 2   |          | N: Timer2 O                   | n bit                |               |                |            |                |         |

|         | 1 = Time |                               |                      |               |                |            |                |         |

|         |          | er2 is off                    |                      |               |                |            |                |         |

| bit 1-0 |          |                               | : Timer2 Clo         | ck Prescale   | Select bits    |            |                |         |

|         |          | escaler is 1                  |                      |               |                |            |                |         |

|         |          | escaler is 4<br>escaler is 16 |                      |               |                |            |                |         |

|         | 1X = FIG |                               |                      |               |                |            |                |         |

|         | Levend   |                               |                      |               |                |            |                |         |

|         | Legend:  |                               |                      |               |                |            |                |         |

|         | R = Rea  | dable bit                     | W =                  | Writable bit  |                | •          | l bit, read as | ʻ0'     |

|         | - n = Va | ue at POR r                   | eset '1' =           | Bit is set    | '0' = Bit      | is cleared | x = Bit is u   | unknown |

|         |          |                               |                      |               |                |            |                |         |

#### 13.5.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

### TABLE 13-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F       | 0x1F       | 0x17       |

| Maximum Resolution (bits)  | 14       | 12       | 10        | 8          | 7          | 6.58       |

#### TABLE 13-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Name    | Bit 7                | Bit 6                               | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | PC   | ie on<br>)R,<br>)R | all o | ie on<br>other<br>SETS |

|---------|----------------------|-------------------------------------|-------------|---------|---------|--------|---------|---------|------|--------------------|-------|------------------------|

| INTCON  | GIE/<br>GIEH         | PEIE/<br>GIEL                       | TMR0IE      | INTOIE  | RBIE    | TMR0IF | INTOIF  | RBIF    | 0000 | 000x               | 0000  | 000u                   |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                                | RCIF        | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 | 0000               | 0000  | 0000                   |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                                | RCIE        | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 | 0000               | 0000  | 0000                   |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP                                | RCIP        | TXIP    | SSPIP   | CCP1IP | TMR2IP  | TMR1IP  | 0000 | 0000               | 0000  | 0000                   |

| TRISC   | PORTC Da             | ata Direction                       | Register    |         |         |        |         |         | 1111 | 1111               | 1111  | 1111                   |

| TMR2    | Timer2 Mo            | dule Registe                        | er          |         |         |        |         |         | 0000 | 0000               | 0000  | 0000                   |

| PR2     | Timer2 Mo            | dule Period                         | Register    |         |         |        |         |         | 1111 | 1111               | 1111  | 1111                   |

| T2CON   | _                    | TOUTPS3                             | TOUTPS2     | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000               | -000  | 0000                   |

| CCPR1L  | Capture/Co           | ompare/PWI                          | M Register1 | (LSB)   |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                   |

| CCPR1H  | Capture/Co           | ompare/PWI                          | M Register1 | (MSB)   |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                   |

| CCP1CON | _                    | _                                   | DC1B1       | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00   | 0000               | 00    | 0000                   |

| CCPR2L  | Capture/Co           | Capture/Compare/PWM Register2 (LSB) |             |         |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                   |

| CCPR2H  | Capture/Co           | pture/Compare/PWM Register2 (MSB)   |             |         |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                   |

| CCP2CON |                      |                                     | DC2B1       | DC2B0   | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00   | 0000               | 00    | 0000                   |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

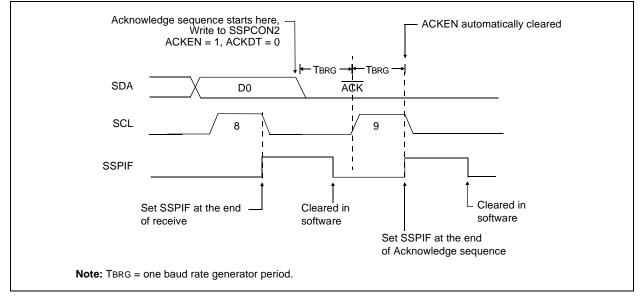

### 14.4.10 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit is presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The baud rate generator then counts for one rollover period (TBRG) and the SCL pin is de-asserted (pulled high). When the SCL pin is sampled high (clock arbitration), the baud rate generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off and the MSSP module then goes into IDLE mode (Figure 14-20).

### 14.4.10.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

### 14.4.11 STOP CONDITION TIMING

A STOP bit is asserted on the SDA pin at the end of a receive/transmit by setting the STOP sequence enable bit, PEN (SSPCON2<2>). At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the baud rate generator is reloaded and counts down to 0. When the baud rate generator times out, the SCL pin will be brought high, and one TBRG (baud rate generator rollover count) later, the SDA pin will be de-asserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 14-21).

### 14.4.11.1 WCOL Status Flag

If the user writes the SSPBUF when a STOP sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

## FIGURE 14-20: ACKNOWLEDGE SEQUENCE WAVEFORM

| BCF                                                                                       | Bit Clear f                                                                                                                                                                                            |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                                   | [ <i>label</i> ] BCF f,b[,a]                                                                                                                                                                           |  |  |  |  |  |  |

| Operands:                                                                                 | 0 ≤ f ≤ 255<br>0 ≤ b ≤ 7<br>a ∈ [0,1]                                                                                                                                                                  |  |  |  |  |  |  |

| Operation:                                                                                | $0 \rightarrow f < b >$                                                                                                                                                                                |  |  |  |  |  |  |

| Status Affected:                                                                          | None                                                                                                                                                                                                   |  |  |  |  |  |  |

| Encoding:                                                                                 | 1001 bbba ffff ffff                                                                                                                                                                                    |  |  |  |  |  |  |

| Description:                                                                              | Bit 'b' in register 'f' is cleared. If 'a'<br>is 0, the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default). |  |  |  |  |  |  |

| Words:                                                                                    | 1                                                                                                                                                                                                      |  |  |  |  |  |  |

| Cycles:                                                                                   | 1                                                                                                                                                                                                      |  |  |  |  |  |  |

| Q Cycle Activity                                                                          | :                                                                                                                                                                                                      |  |  |  |  |  |  |

| Q1                                                                                        | Q2 Q3 Q4                                                                                                                                                                                               |  |  |  |  |  |  |

| Decode                                                                                    | Read         Process         Write           register 'f'         Data         register 'f'                                                                                                            |  |  |  |  |  |  |

| Example: BCF FLAG_REG, 7, 0<br>Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction |                                                                                                                                                                                                        |  |  |  |  |  |  |

| /                                                                                         | EG = 0x47                                                                                                                                                                                              |  |  |  |  |  |  |

| BN                           | Branch if                                                            | Negative                                                                                      |                                                              |  |  |  |  |  |

|------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|

| Syntax:                      | [ <i>label</i> ] B                                                   | [ <i>label</i> ] BN n                                                                         |                                                              |  |  |  |  |  |

| Operands:                    | -128 ≤ n ≤                                                           | 127                                                                                           |                                                              |  |  |  |  |  |

| Operation:                   | •                                                                    | if negative bit is '1' (PC) + 2 + 2n $\rightarrow$ PC                                         |                                                              |  |  |  |  |  |

| Status Affected:             | None                                                                 |                                                                                               |                                                              |  |  |  |  |  |

| Encoding:                    | 1110                                                                 | 0110 nn                                                                                       | nn nnnn                                                      |  |  |  |  |  |

|                              | The 2's co<br>added to the<br>have incre-<br>instruction<br>PC+2+2n. | vill branch.<br>Implement n<br>he PC. Since<br>mented to fe<br>the new ad<br>This instruction | e the PC wi<br>etch the new<br>dress will b<br>ction is ther |  |  |  |  |  |

| Words:                       | 1                                                                    |                                                                                               |                                                              |  |  |  |  |  |

| Cycles:                      | 1(2)                                                                 |                                                                                               |                                                              |  |  |  |  |  |

| Q Cycle Activity<br>If Jump: | <u>/:</u>                                                            |                                                                                               |                                                              |  |  |  |  |  |

| Q1                           | Q2                                                                   | Q3                                                                                            | Q4                                                           |  |  |  |  |  |

| Decode                       | Read literal<br>'n'                                                  | Process<br>Data                                                                               | Write to PC                                                  |  |  |  |  |  |

| No                           | No                                                                   | No                                                                                            | No                                                           |  |  |  |  |  |

| operation                    | operation                                                            | operation                                                                                     | operation                                                    |  |  |  |  |  |

| If No Jump:                  |                                                                      |                                                                                               | •                                                            |  |  |  |  |  |

| Q1                           | Q2                                                                   | Q3                                                                                            | Q4                                                           |  |  |  |  |  |

| Decode                       | Read literal<br>'n'                                                  | Process<br>Data                                                                               | No<br>operation                                              |  |  |  |  |  |

| L                            |                                                                      | 2414                                                                                          | - speration                                                  |  |  |  |  |  |

| Example:                     | HERE                                                                 | BN Jump                                                                                       |                                                              |  |  |  |  |  |

| Before Instr                 | uction                                                               |                                                                                               |                                                              |  |  |  |  |  |

| PC                           | - ad                                                                 | dress (HER                                                                                    | F)                                                           |  |  |  |  |  |

| PC       | =                                        | address       | (HERE)             |

|----------|------------------------------------------|---------------|--------------------|

| After In | struction                                |               |                    |

|          | Negative =<br>PC =<br>Negative =<br>PC = | address<br>0; | (Jump)<br>(HERE+2) |

| IORLW Inclusive OR literal with WREG |       |                     |                                                                                                    |      |                  |      |  |  |

|--------------------------------------|-------|---------------------|----------------------------------------------------------------------------------------------------|------|------------------|------|--|--|

| Syntax:                              |       | [ label ]           | IORLW                                                                                              | k    |                  |      |  |  |

| Operands:                            |       | $0 \le k \le 2\xi$  | $0 \le k \le 255$                                                                                  |      |                  |      |  |  |

| Operation:                           |       | (WREG)              | .OR. k –                                                                                           | → WR | EG               |      |  |  |

| Status Affecte                       | ed:   | N,Z                 |                                                                                                    |      |                  |      |  |  |

| Encoding:                            |       | 0000                | 1001                                                                                               | kkk  | k                | kkkk |  |  |

| Description:                         |       | with the e          | The contents of WREG are OR'ed<br>with the eight-bit literal 'k'. The<br>result is placed in WREG. |      |                  |      |  |  |

| Words:                               |       | 1                   |                                                                                                    |      |                  |      |  |  |

| Cycles:                              |       | 1                   |                                                                                                    |      |                  |      |  |  |

| Q Cycle Acti                         | vity: |                     |                                                                                                    |      |                  |      |  |  |

| Q1                                   |       | Q2                  | Q3                                                                                                 | 3    |                  | Q4   |  |  |

| Decode                               | е     | Read<br>literal 'k' | Proce<br>Data                                                                                      |      | Write to<br>WREG |      |  |  |

| Example:<br>Before Instruc           |       |                     | 0x35                                                                                               |      |                  |      |  |  |

| After Ins                            |       | 011911              |                                                                                                    |      |                  |      |  |  |

WREG = 0xBF

| IORWF                              | Inclusive OR WREG with f                                         |                                   |                    |                            |  |  |

|------------------------------------|------------------------------------------------------------------|-----------------------------------|--------------------|----------------------------|--|--|

| Syntax:                            | [ label ]                                                        | IORWF                             | f [,c              | d [,a]                     |  |  |

| Operands:                          | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$              | 5                                 |                    |                            |  |  |

| Operation:                         | (WREG) .                                                         | OR. (f) -                         | $\rightarrow$ des  | t                          |  |  |

| Status Affected:                   | N,Z                                                              |                                   |                    |                            |  |  |

| Encoding:                          | 0001                                                             | 00da                              | fff                | f fff:                     |  |  |

|                                    | WREG. If<br>placed bac<br>If 'a' is 0, t<br>selected, c          | ck in reg<br>he Acce<br>overridir | gister '<br>ess Ba | f' (default<br>ink will be |  |  |

|                                    | lf 'a' = 1, t<br>selected a<br>(default).                        |                                   |                    |                            |  |  |

| Words:                             | selected a                                                       |                                   |                    |                            |  |  |

| Words:<br>Cycles:                  | selected a (default).                                            |                                   |                    |                            |  |  |

|                                    | selected a<br>(default).<br>1                                    |                                   |                    |                            |  |  |

| Cycles:                            | selected a<br>(default).<br>1                                    |                                   | e BSF              |                            |  |  |

| Cycles:<br>Q Cycle Activity:       | selected a<br>(default).<br>1<br>1                               | is per th                         | e BSF              | R value                    |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1 | selected a<br>(default).<br>1<br>1<br>Q2<br>Read<br>register 'f' | Q3<br>Proce                       | e BSF              | ₹ value<br>Q4<br>Write to  |  |  |

| Before Instruction       |          |      |  |  |  |  |

|--------------------------|----------|------|--|--|--|--|

| RESULT                   | =        | 0x13 |  |  |  |  |

| WREG                     | =        | 0x91 |  |  |  |  |

| After Instruction        |          |      |  |  |  |  |

| After Instruct           | ion      |      |  |  |  |  |

| After Instruct<br>RESULT | ion<br>= | 0x13 |  |  |  |  |

| RRNCF                   | Rotate Right f (no carry)                                                                                                                                                                                                                                                                  | SETF                         |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Syntax:                 | [ label ] RRNCF f [,d [,a]                                                                                                                                                                                                                                                                 | Syntax:                      |

| Operands:               | $0 \le f \le 255$<br>$d \in [0,1]$                                                                                                                                                                                                                                                         | Operands:                    |

|                         | a ∈ [0,1]                                                                                                                                                                                                                                                                                  | Operation:                   |

| Operation:              | $(f < n >) \rightarrow dest < n - 1 >,$<br>$(f < 0 >) \rightarrow dest < 7 >$                                                                                                                                                                                                              | Status Affected<br>Encoding: |

| Status Affecte          | ed: N,Z                                                                                                                                                                                                                                                                                    | -                            |

| Encoding:               | 0100 00da ffff ffff                                                                                                                                                                                                                                                                        | Description:                 |

| Description:            | The contents of register 'f' are<br>rotated one bit to the right. If 'd' is 0,<br>the result is placed in WREG. If 'd'<br>is 1, the result is placed back in<br>register 'f' (default). If 'a' is 0, the<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' is 1, then | Words:<br>Cycles:            |

|                         | the bank will be selected as per the                                                                                                                                                                                                                                                       | Q Cycle Activit              |

|                         | BSR value (default).                                                                                                                                                                                                                                                                       | Q1                           |

|                         | register f                                                                                                                                                                                                                                                                                 | Decode                       |

| Words:                  | 1                                                                                                                                                                                                                                                                                          |                              |

| Cycles:                 | 1                                                                                                                                                                                                                                                                                          | Example:                     |

| Q Cycle Activ           | vity:                                                                                                                                                                                                                                                                                      | Before Inst                  |

| Q1                      | Q2 Q3 Q4                                                                                                                                                                                                                                                                                   | REG                          |

| Decode                  | e Read Process Write to<br>register 'f' Data destination                                                                                                                                                                                                                                   | After Instru<br>REG          |

| Example 1:<br>Before In | RRNCF REG, 1, 0                                                                                                                                                                                                                                                                            |                              |

| REG                     | = 1101 0111                                                                                                                                                                                                                                                                                |                              |

| After Inst              |                                                                                                                                                                                                                                                                                            |                              |

| REG                     | = 1110 1011                                                                                                                                                                                                                                                                                |                              |

| Example 2:              | RRNCF REG, 0, 0                                                                                                                                                                                                                                                                            |                              |

| Before In               | struction                                                                                                                                                                                                                                                                                  |                              |

|                         | ; = ?<br>= 1101 0111                                                                                                                                                                                                                                                                       |                              |

| After Inst              |                                                                                                                                                                                                                                                                                            |                              |

| WREG                    |                                                                                                                                                                                                                                                                                            |                              |

| Synta  | ix:                              | [ <i>label</i> ] SE                                                           | TFf[,                                                           | a]                                                       |                                  |  |  |  |

|--------|----------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|----------------------------------|--|--|--|

| pera   | ands:                            | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                      | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$ |                                                          |                                  |  |  |  |

| pera   | ation:                           | $FFh\tof$                                                                     |                                                                 |                                                          |                                  |  |  |  |

| status | s Affected:                      | None                                                                          |                                                                 |                                                          |                                  |  |  |  |

| nco    | ding:                            | 0110                                                                          | 100a                                                            | ffff                                                     | ffff                             |  |  |  |

| )esci  | ription:                         | The conte<br>ter are se<br>Access Ba<br>riding the<br>the bank v<br>BSR value | t to FFh<br>ank will<br>BSR val<br>will be se                   | . If 'a' is 0<br>be select<br>ue. If 'a' i<br>elected as | ), the<br>ed, over-<br>s 1, then |  |  |  |

| Vord   | s:                               | 1                                                                             |                                                                 |                                                          |                                  |  |  |  |

| ycle   | s:                               | 1                                                                             |                                                                 |                                                          |                                  |  |  |  |

| Q Cy   | cle Activity:                    |                                                                               |                                                                 |                                                          |                                  |  |  |  |

|        | Q1                               | Q2                                                                            | Q                                                               | 3                                                        | Q4                               |  |  |  |

|        | Decode                           | Read<br>register 'f'                                                          | Proce<br>Data                                                   |                                                          | Write<br>gister 'f'              |  |  |  |

|        |                                  |                                                                               |                                                                 |                                                          |                                  |  |  |  |

| xam    | <u>iple</u> :                    | SETF                                                                          | RE                                                              | G,1                                                      |                                  |  |  |  |

| E      | Before Instruction<br>REG = 0x5A |                                                                               |                                                                 |                                                          |                                  |  |  |  |

| A      | After Instruct                   | ion                                                                           |                                                                 |                                                          |                                  |  |  |  |

0xFF

=

Set f

© 1999-2013 Microchip Technology Inc.

| SUBLW                   | Subtract WREG from literal           | SUBWF             | Subtract WREG from f                                                            |

|-------------------------|--------------------------------------|-------------------|---------------------------------------------------------------------------------|

| Syntax:                 | [ <i>label</i> ] SUBLW k             | Syntax:           | [ <i>label</i> ] SUBWF f[,d[,a]                                                 |

| Operands:               | $0 \le k \le 255$                    | Operands:         | $0 \le f \le 255$                                                               |

| Operation:              | $k - (WREG) \rightarrow WREG$        |                   | d ∈ [0,1]                                                                       |

| Status Affected:        | N,OV, C, DC, Z                       |                   | a ∈ [0,1]                                                                       |

| Encoding:               | 0000 1000 kkkk kkkk                  | Operation:        | (f) – (WREG) $\rightarrow$ dest                                                 |

| Description:            | WREG is subtracted from the          | Status Affected:  | N,OV, C, DC, Z                                                                  |

|                         | eight-bit literal 'k'. The result is | Encoding:         | 0101 11da ffff ffff                                                             |

|                         | placed in WREG.                      | Description:      | Subtract WREG from register 'f'<br>(2's complement method). If 'd' is           |

| Words:                  | 1                                    |                   | 0, the result is stored in WREG. If                                             |

| Cycles:                 | 1                                    |                   | 'd' is 1, the result is stored back in register 'f' (default). If 'a' is 0, the |

| Q Cycle Activity:<br>Q1 | Q2 Q3 Q4                             |                   | Access Bank will be selected,                                                   |

| Decode                  | Read Process Write to                |                   | overriding the BSR value. If 'a' is 1, then the bank will be selected           |

|                         | literal 'k' Data WREG                |                   | as per the BSR value (default).                                                 |

| Example 1:              | SUBLW 0x02                           | Words:            | 1                                                                               |

| Before Instruc          | ction                                | Cycles:           | 1                                                                               |

|                         | = 1                                  | Q Cycle Activity: |                                                                                 |

| د<br>After Instructi    | = ?                                  | Q1                | Q2 Q3 Q4                                                                        |

|                         | = 1                                  | Decode            | Read Process Write to                                                           |

| С                       | = 1 ; result is positive             |                   | register 'f' Data destination                                                   |

|                         | = 0<br>= 0                           | Example 1:        | SUBWF REG, 1, 0                                                                 |

| European la Or          |                                      | Before Instru     |                                                                                 |

| Example 2:              | SUBLW 0x02                           | REG<br>WREG       | = 3<br>= 2                                                                      |

| Before Instruc          |                                      | C                 | = ?                                                                             |

|                         | = 2<br>= ?                           | After Instruct    | ion<br>= 1                                                                      |

| After Instruction       | on                                   | WREG              | = 2                                                                             |

|                         | = 0                                  | C<br>Z            | = 1 ; result is positive<br>= 0                                                 |

| Z                       | = 1 ; result is zero<br>= 1          | N                 | = 0                                                                             |

|                         | = 0                                  | Example 2:        | SUBWF REG, 0, 0                                                                 |

| Example 3:              | SUBLW 0x02                           | Before Instru     |                                                                                 |

| Before Instruc          |                                      | REG<br>WREG       | = 2<br>= 2                                                                      |

|                         | = 3<br>= ?                           | C                 | = ?                                                                             |

| After Instruction       | on                                   | After Instruct    |                                                                                 |

|                         | = FF ; (2's complement)              | REG<br>WREG       | = 2<br>= 0                                                                      |

| -                       | = 0 ; result is negative<br>= 0      | C                 | = 1 ; result is zero                                                            |

| Ν                       | = 1                                  | Z<br>N            | = 1<br>= 0                                                                      |

|                         |                                      | Example 3:        | SUBWF REG, 1, 0                                                                 |

|                         |                                      | Before Instru     | ction                                                                           |

|                         |                                      | REG               | = 1                                                                             |

|                         |                                      | WREG<br>C         | = 2<br>= ?                                                                      |

|                         |                                      | After Instruct    | ion                                                                             |

|                         |                                      | REG               | = FFh ;(2's complement)                                                         |

|                         |                                      | WREG<br>C         | = 2<br>= 0 ; result is negative                                                 |

|                         |                                      | Z<br>N            | = 0<br>= 1                                                                      |

|                         |                                      |                   |                                                                                 |

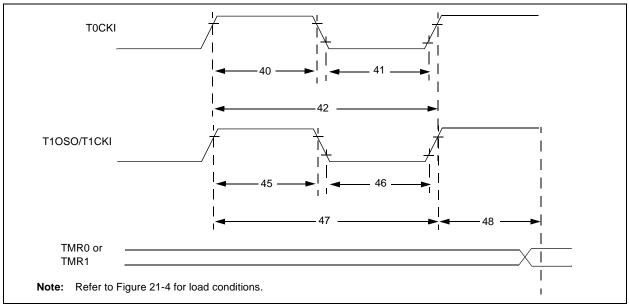

FIGURE 21-9: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 21-8: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

|-------------|-----------------------------------------------|

| Param<br>No. | Symbol    |                          | Characteris                 | tic             | Min                                          | Max   | Units | Conditions                               |

|--------------|-----------|--------------------------|-----------------------------|-----------------|----------------------------------------------|-------|-------|------------------------------------------|

| 40 Tt0H      |           | T0CKI H                  | ligh Pulse Width            | No Prescaler    | 0.5Tcy + 20                                  |       | ns    |                                          |

|              |           |                          |                             | With Prescaler  | 10                                           | _     | ns    |                                          |

| 41           | Tt0L      | T0CKI L                  | ow Pulse Width              | No Prescaler    | 0.5Tcy + 20                                  | _     | ns    |                                          |

|              |           |                          |                             | With Prescaler  | 10                                           |       | ns    |                                          |

| 42           | Tt0P      | T0CKI P                  | Period                      | No Prescaler    | Tcy + 10                                     |       | ns    |                                          |

|              |           |                          |                             | With Prescaler  | Greater of:<br>20 ns or <u>TcY + 40</u><br>N |       | ns    | N = prescale<br>value<br>(1, 2, 4,, 256) |

| 45           | Tt1H      | T1CKI                    | Synchronous, no             | o prescaler     | 0.5Tcy + 20                                  | _     | ns    |                                          |

|              |           | High                     | Synchronous,                | PIC18CXXX       | 10                                           | _     | ns    |                                          |

|              |           | Time                     | with prescaler              | PIC18LCXXX      | 25                                           | _     | ns    |                                          |

|              |           |                          | Asynchronous                | PIC18CXXX       | 30                                           | _     | ns    |                                          |

|              |           |                          |                             | PIC18LCXXX      | 40                                           | _     | ns    |                                          |

| 46           | Tt1L      | T1CKI                    | Synchronous, no             | prescaler       | 0.5Tcy + 20                                  | _     | ns    |                                          |

|              |           | Low                      | Synchronous,                | PIC18CXXX       | 15                                           | _     | ns    |                                          |

|              |           | Time                     | with prescaler              | PIC18LCXXX      | 30                                           | _     | ns    |                                          |

|              |           |                          | Asynchronous                | PIC18CXXX       | 30                                           | _     | ns    |                                          |

|              |           |                          |                             | PIC18LCXXX      | 40                                           | _     | ns    |                                          |

| 47           | Tt1P      | T1CKI<br>input<br>period | Synchronous                 |                 | Greater of:<br>20 ns or <u>Tcy + 40</u><br>N |       | ns    | N = prescale<br>value<br>(1, 2, 4, 8)    |

|              |           |                          | Asynchronous                | Asynchronous    |                                              |       | ns    |                                          |

|              | Ft1       | T1CKI o                  | scillator input free        | luency range    | DC                                           | 50    | kHz   |                                          |

| 48           | Tcke2tmrl | Delay fro                | om external T1CK<br>crement | I clock edge to | 2Tosc                                        | 7Tosc |       |                                          |

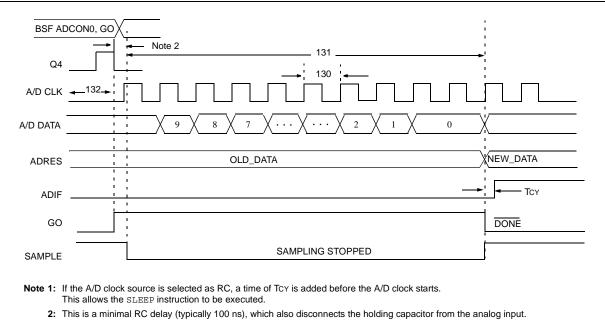

### TABLE 21-22: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Symbol | Characteristic                              |                             | Min | Max               | Units                                                                                                             | Conditions                                                                                                                                                             |

|--------------|--------|---------------------------------------------|-----------------------------|-----|-------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD    | A/D clock period                            | PIC18CXXX                   | 1.6 | 20 <sup>(5)</sup> | μS                                                                                                                | Tosc based, VREF $\geq 3.0V$                                                                                                                                           |

|              |        |                                             | PIC18LCXXX                  | 3.0 | 20 <sup>(5)</sup> | μS                                                                                                                | Tosc based, VREF full range                                                                                                                                            |

|              |        |                                             | PIC18CXXX                   | 2.0 | 6.0               | μS                                                                                                                | A/D RC mode                                                                                                                                                            |

|              |        |                                             | PIC18LCXXX                  | 3.0 | 9.0               | μS                                                                                                                | A/D RC mode                                                                                                                                                            |

| 131          | TCNV   | Conversion time<br>(not including acquisiti | 11                          | 12  | TAD               |                                                                                                                   |                                                                                                                                                                        |

| 132          | TACQ   | Acquisition time (Note                      | 15<br>10                    |     | μs<br>μs          | $\begin{array}{l} -40^{\circ}C \leq Temp \leq 125^{\circ}C \\ 0^{\circ}C \leq Temp \leq 125^{\circ}C \end{array}$ |                                                                                                                                                                        |

| 135          | Tswc   | Switching Time from c                       | onvert $\rightarrow$ sample | —   | (Note 4)          |                                                                                                                   |                                                                                                                                                                        |

| 136          | Тамр   | Amplifier settling time                     | (Note 2)                    | 1   | _                 | μs                                                                                                                | This may be used if the<br>"new" input voltage has not<br>changed by more than 1 LSb<br>(i.e., 5 mV @ 5.12V) from<br>the last sampled voltage (as<br>stated on CHOLD). |

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 16.0 for minimum conditions, when input voltage has changed more than 1 LSb.

**3:** The time for the holding capacitor to acquire the "New" input voltage, when the voltage changes full scale after the conversion (AVDD to AVSS, or AVSS to AVDD). The source impedance (*Rs*) on the input channels is  $50 \Omega$ .

4: On the next Q4 cycle of the device clock.

5: The time of the A/D clock period is dependent on the device frequency and the TAD clock divider.

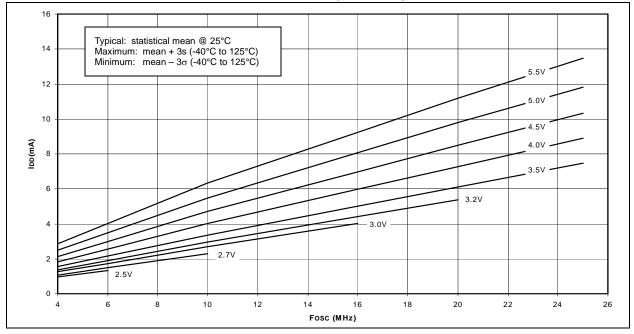

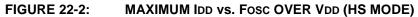

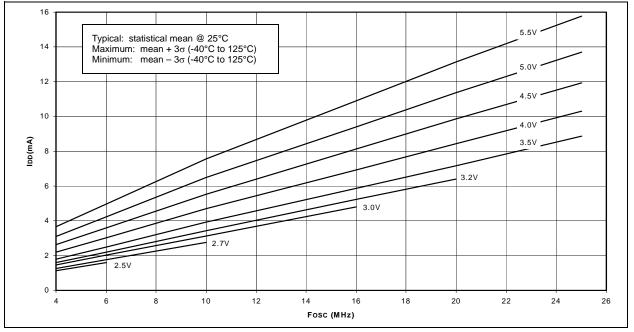

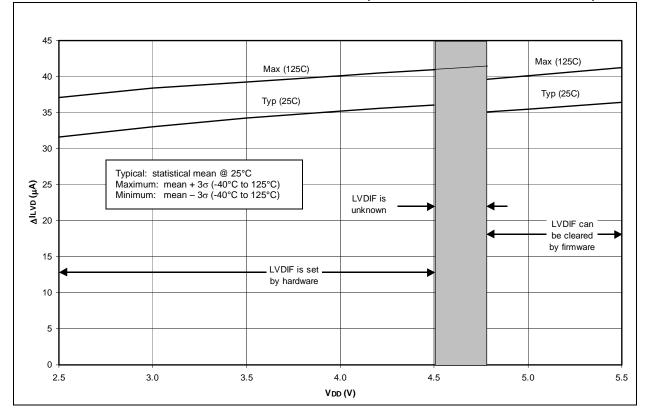

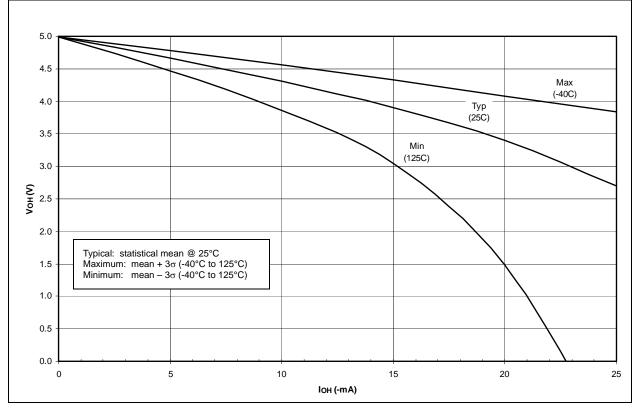

# 22.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at 25°C. 'Max' or 'min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

FIGURE 22-1: TYPICAL IDD vs. Fosc OVER VDD (HS MODE)

© 1999-2013 Microchip Technology Inc.

### FIGURE 22-19: △ILVD vs. VDD OVER TEMPERATURE (LVD ENABLED, VLVD = 4.5V - 4.78V)

# Package Marking Information (Cont'd)

### 40-Lead PDIP

### Example

PIC18C452

-I/JW

0115017

### 28- and 40-Lead JW (CERDIP)

# 44-Lead TQFP

### Example

Example

$\mathbf{v}$

MICROCHIP

#### 44-Lead PLCC

#### Example

DS39026D-page 278

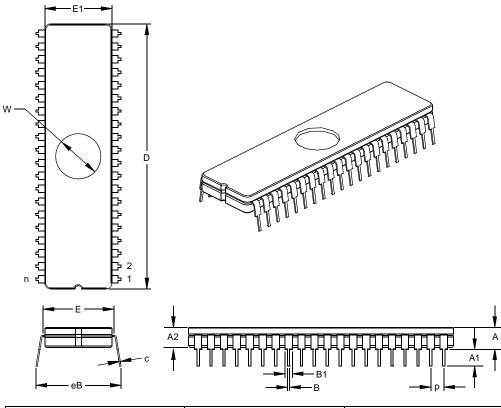

### 40-Lead Ceramic Dual In-line with Window (JW) - 600 mil (CERDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units | INCHES* |       |       | MILLIMETERS |       |       |  |

|----------------------------|-------|---------|-------|-------|-------------|-------|-------|--|

| Dimension                  | MIN   | NOM     | MAX   | MIN   | NOM         | MAX   |       |  |

| Number of Pins             | n     |         | 40    |       |             | 40    |       |  |

| Pitch                      | р     |         | .100  |       |             | 2.54  |       |  |

| Top to Seating Plane       | Α     | .185    | .205  | .225  | 4.70        | 5.21  | 5.72  |  |

| Ceramic Package Height     | A2    | .155    | .160  | .165  | 3.94        | 4.06  | 4.19  |  |

| Standoff                   | A1    | .030    | .045  | .060  | 0.76        | 1.14  | 1.52  |  |

| Shoulder to Shoulder Width | E     | .595    | .600  | .625  | 15.11       | 15.24 | 15.88 |  |

| Ceramic Pkg. Width         | E1    | .514    | .520  | .526  | 13.06       | 13.21 | 13.36 |  |

| Overall Length             | D     | 2.040   | 2.050 | 2.060 | 51.82       | 52.07 | 52.32 |  |

| Tip to Seating Plane       | L     | .135    | .140  | .145  | 3.43        | 3.56  | 3.68  |  |

| Lead Thickness             | С     | .008    | .011  | .014  | 0.20        | 0.28  | 0.36  |  |

| Upper Lead Width           | B1    | .050    | .053  | .055  | 1.27        | 1.33  | 1.40  |  |

| Lower Lead Width           | В     | .016    | .020  | .023  | 0.41        | 0.51  | 0.58  |  |

| Overall Row Spacing §      | eB    | .610    | .660  | .710  | 15.49       | 16.76 | 18.03 |  |

| Window Diameter            | W     | .340    | .350  | .360  | 8.64        | 8.89  | 9.14  |  |

Significant Characteristic JEDEC Equivalent: MO-103 Drawing No. C04-014

| Code Examples                         |          |

|---------------------------------------|----------|

| 16 x 16 Signed Multiply Routine       | 62       |

| 16 x 16 Unsigned Multiply Routine     | 62       |

| 8 x 8 Signed Multiply Routine         |          |

| 8 x 8 Unsigned Multiply Routine       | 61       |

| Changing Between Capture Prescalers   | 109      |

| Fast Register Stack                   |          |

| Initializing PORTA                    | 77       |

| Initializing PORTB                    |          |

| Initializing PORTC                    |          |

| Initializing PORTD                    |          |

| Initializing PORTE                    |          |

| Loading the SSPBUF Register           | 122      |

| Saving STATUS, WREG and BSR Registers |          |

| in RAM                                | 75       |

| Code Protection                       | 179, 186 |

| COMF                                  | 204      |

| Compare (CCP Module)                  | 110      |

| Associated Registers                  | 111      |

| Block Diagram                         | 110      |

| CCP Pin Configuration                 | 110      |

| CCPR1H:CCPR1L Registers               | 110      |

| Software Interrupt                    | 110      |

| Special Event Trigger                 | 110, 171 |

| Timer1 Mode Selection                 | 110      |

| Configuration Bits                    | 179      |

| Context Saving During Interrupts      | 75       |

| Example Code                          | 75       |