Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c452t-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.7 Effects of SLEEP Mode on the On-chip Oscillator

When the device executes a SLEEP instruction, the on-chip clocks and oscillator are turned off and the device is held at the beginning of an instruction cycle (Q1 state). With the oscillator off, the OSC1 and OSC2 signals will stop oscillating. Since all the transistor

switching currents have been removed, SLEEP mode achieves the lowest current consumption of the device (only leakage currents). Enabling any on-chip feature that will operate during SLEEP will increase the current consumed during SLEEP. The user can wake from SLEEP through external RESET, Watchdog Timer Reset, or through an interrupt.

## TABLE 2-3:OSC1 AND OSC2 PIN STATES IN SLEEP MODE

| OSC Mode       | OSC1 Pin                                                  | OSC2 Pin                                                  |  |  |

|----------------|-----------------------------------------------------------|-----------------------------------------------------------|--|--|

| RC             | Floating, external resistor should pull high              | At logic low                                              |  |  |

| RCIO           | Floating, external resistor should pull high              | Configured as PORTA, bit 6                                |  |  |

| ECIO           | Floating                                                  | Configured as PORTA, bit 6                                |  |  |

| EC             | Floating                                                  | At logic low                                              |  |  |

| LP, XT, and HS | Feedback inverter disabled, at<br>quiescent voltage level | Feedback inverter disabled, at<br>quiescent voltage level |  |  |

**Note:** See Table 3-1, in Section 3.0 RESET, for time-outs due to SLEEP and MCLR Reset.

## 2.8 Power-up Delays

Power up delays are controlled by two timers, so that no external RESET circuitry is required for most applications. The delays ensure that the device is kept in RESET until the device power supply and clock are stable. For additional information on RESET operation, see the "RESET" section.

The first timer is the Power-up Timer (PWRT), which optionally provides a fixed delay of 72 ms (nominal) on power-up only (POR and BOR). The second timer is the Oscillator Start-up Timer, OST, intended to keep the chip in RESET until the crystal oscillator is stable.

With the PLL enabled (HS/PLL oscillator mode), the time-out sequence following a Power-on Reset is different from other oscillator modes. The time-out sequence is as follows: First, the PWRT time-out is invoked after a POR time delay has expired. Then, the Oscillator Start-up Timer (OST) is invoked. However, this is still not a sufficient amount of time to allow the PLL to lock at high frequencies. The PWRT timer is used to provide an additional fixed 2ms (nominal) time-out to allow the PLL ample time to lock to the incoming clock frequency.

NOTES:

## 4.2 Return Address Stack

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC (Program Counter) is pushed onto the stack when a CALL or RCALL instruction is executed, or an interrupt is acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the call or return instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit stack pointer, with the stack pointer initialized to 00000b after all RESETS. There is no RAM associated with stack pointer 00000b. This is only a RESET value. During a CALL type instruction causing a push onto the stack, the stack pointer is first incremented and the RAM location pointed to by the stack pointer is written with the contents of the PC. During a RETURN type instruction causing a pop from the stack, the contents of the RAM location pointed to by the STKPTR is transferred to the PC and then the stack pointer is decremented.

The stack space is not part of either program or data space. The stack pointer is readable and writable, and the address on the top of the stack is readable and writable through SFR registers. Data can also be pushed to, or popped from, the stack, using the top-of-stack SFRs. Status bits indicate if the stack pointer is at, or beyond the 31 levels provided.

## 4.2.1 TOP-OF-STACK ACCESS

The top of the stack is readable and writable. Three register locations, TOSU, TOSH and TOSL hold the contents of the stack location pointed to by the STKPTR register. This allows users to implement a software stack, if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU, TOSH and TOSL registers. These values can be placed on a user defined software stack. At return time, the software can replace the TOSU, TOSH and TOSL and do a return.

The user must disable the global interrupt enable bits during this time to prevent inadvertent stack operations.

## 4.2.2 RETURN STACK POINTER (STKPTR)

The STKPTR register contains the stack pointer value, the STKFUL (stack full) status bit, and the STKUNF (stack underflow) status bits. Register 4-1 shows the STKPTR register. The value of the stack pointer can be 0 through 31. The stack pointer increments when values are pushed onto the stack and decrements when values are popped off the stack. At RESET, the stack pointer value will be 0. The user may read and write the stack pointer value. This feature can be used by a Real Time Operating System for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit can only be cleared in software or by a POR.

The action that takes place when the stack becomes full, depends on the state of the STVREN (Stack Overflow Reset Enable) configuration bit. Refer to Section 18.0 for a description of the device configuration bits. If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit, and reset the device. The STKFUL bit will remain set and the stack pointer will be set to 0.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the stack pointer will increment to 31. Any additional pushes will not overwrite the 31st push and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the stack pointer remains at 0. The STKUNF bit will remain set until cleared in software or a POR occurs.

**Note:** Returning a value of zero to the PC on an underflow, has the effect of vectoring the program to the RESET vector, where the stack conditions can be verified and appropriate actions can be taken.

| FFFh | TOSU                    | FDFh | INDF2 <sup>(3)</sup>    | FBFh | CCPR1H   | F9Fh | IPR1                 |

|------|-------------------------|------|-------------------------|------|----------|------|----------------------|

| FFEh | TOSH                    | FDEh | POSTINC2(3)             | FBEh | CCPR1L   | F9Eh | PIR1                 |

| FFDh | TOSL                    | FDDh | POSTDEC2 <sup>(3)</sup> | FBDh | CCP1CON  | F9Dh | PIE1                 |

| FFCh | STKPTR                  | FDCh | PREINC2 <sup>(3)</sup>  | FBCh | CCPR2H   | F9Ch |                      |

| FFBh | PCLATU                  | FDBh | PLUSW2 <sup>(3)</sup>   | FBBh | CCPR2L   | F9Bh |                      |

| FFAh | PCLATH                  | FDAh | FSR2H                   | FBAh | CCP2CON  | F9Ah |                      |

| FF9h | PCL                     | FD9h | FSR2L                   | FB9h | —        | F99h | _                    |

| FF8h | TBLPTRU                 | FD8h | STATUS                  | FB8h | —        | F98h | —                    |

| FF7h | TBLPTRH                 | FD7h | TMR0H                   | FB7h | —        | F97h |                      |

| FF6h | TBLPTRL                 | FD6h | TMR0L                   | FB6h | —        | F96h | TRISE <sup>(2)</sup> |

| FF5h | TABLAT                  | FD5h | T0CON                   | FB5h | —        | F95h | TRISD <sup>(2)</sup> |

| FF4h | PRODH                   | FD4h |                         | FB4h | —        | F94h | TRISC                |

| FF3h | PRODL                   | FD3h | OSCCON                  | FB3h | TMR3H    | F93h | TRISB                |

| FF2h | INTCON                  | FD2h | LVDCON                  | FB2h | TMR3L    | F92h | TRISA                |

| FF1h | INTCON2                 | FD1h | WDTCON                  | FB1h | T3CON    | F91h |                      |

| FF0h | INTCON3                 | FD0h | RCON                    | FB0h | <u> </u> | F90h |                      |

| FEFh | INDF0 <sup>(3)</sup>    | FCFh | TMR1H                   | FAFh | SPBRG    | F8Fh |                      |

| FEEh | POSTINC0 <sup>(3)</sup> | FCEh | TMR1L                   | FAEh | RCREG    | F8Eh |                      |

| FEDh | POSTDEC0 <sup>(3)</sup> | FCDh | T1CON                   | FADh | TXREG    | F8Dh | LATE <sup>(2)</sup>  |

| FECh | PREINC0 <sup>(3)</sup>  | FCCh | TMR2                    | FACh | TXSTA    | F8Ch | LATD <sup>(2)</sup>  |

| FEBh | PLUSW0 <sup>(3)</sup>   | FCBh | PR2                     | FABh | RCSTA    | F8Bh | LATC                 |

| FEAh | FSR0H                   | FCAh | T2CON                   | FAAh | —        | F8Ah | LATB                 |

| FE9h | FSR0L                   | FC9h | SSPBUF                  | FA9h | —        | F89h | LATA                 |

| FE8h | WREG                    | FC8h | SSPADD                  | FA8h | —        | F88h |                      |

| FE7h | INDF1 <sup>(3)</sup>    | FC7h | SSPSTAT                 | FA7h | —        | F87h |                      |

| FE6h | POSTINC1 <sup>(3)</sup> | FC6h | SSPCON1                 | FA6h | —        | F86h |                      |

| FE5h | POSTDEC1 <sup>(3)</sup> | FC5h | SSPCON2                 | FA5h | —        | F85h |                      |

| FE4h | PREINC1 <sup>(3)</sup>  | FC4h | ADRESH                  | FA4h | —        | F84h | PORTE <sup>(2)</sup> |

| FE3h | PLUSW1 <sup>(3)</sup>   | FC3h | ADRESL                  | FA3h | —        | F83h | PORTD <sup>(2)</sup> |

| FE2h | FSR1H                   | FC2h | ADCON0                  | FA2h | IPR2     | F82h | PORTC                |

| FE1h | FSR1L                   | FC1h | ADCON1                  | FA1h | PIR2     | F81h | PORTB                |

| FE0h | BSR                     | FC0h | _                       | FA0h | PIE2     | F80h | PORTA                |

#### SPECIAL FUNCTION REGISTER MAP **TABLE 4-1:**

Note 1: Unimplemented registers are read as '0'.2: This register is not available on PIC18C2X2 devices.

**3:** This is not a physical register.

## 5.0 TABLE READS/TABLE WRITES

Enhanced devices have two memory spaces: the program memory space and the data memory space. The program memory space is 16-bits wide, while the data memory space is 8 bits wide. Table Reads and Table Writes have been provided to move data between these two memory spaces through an 8-bit register (TABLAT).

The operations that allow the processor to move data between the data and program memory spaces are:

- Table Read (TBLRD)

- Table Write (TBLWT)

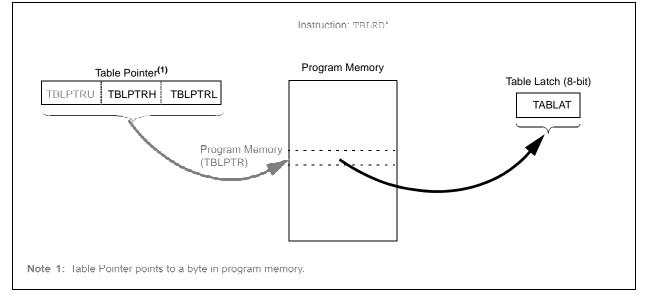

Table Read operations retrieve data from program memory and place it into the data memory space. Figure 5-1 shows the operation of a Table Read with program and data memory.

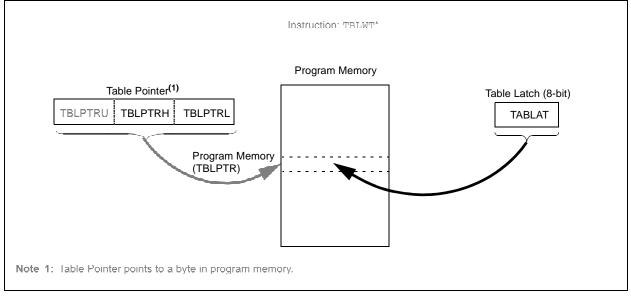

Table Write operations store data from the data memory space into program memory. Figure 5-2 shows the operation of a Table Write with program and data memory.

Table operations work with byte entities. A table block containing data is not required to be word aligned, so a table block can start and end at any byte address. If a Table Write is being used to write an executable program to program memory, program instructions will need to be word aligned.

## FIGURE 5-2: TABLE WRITE OPERATION

## FIGURE 5-1: TABLE READ OPERATION

NOTES:

## 11.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match of PR2

- SSP module optional use of TMR2 output to generate clock shift

Timer2 has a control register shown in Register 11-1. Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption. Figure 11-1 is a simplified block diagram of the Timer2 module. Register 11-1 shows the Timer2 control register. The prescaler and postscaler selection of Timer2 are controlled by this register.

## 11.1 Timer2 Operation

Timer2 can be used as the PWM time-base for the PWM mode of the CCP module. The TMR2 register is readable and writable, and is cleared on any device RESET. The input clock (Fosc/4) has a prescale option of 1:1, 1:4, or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>). The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- a write to the T2CON register

- any device RESET (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

## REGISTER 11-1: T2CON: TIMER2 CONTROL REGISTER

|         | U-0      | R/W-0                         | R/W-0                | R/W-0         | R/W-0          | R/W-0      | R/W-0          | R/W-0   |

|---------|----------|-------------------------------|----------------------|---------------|----------------|------------|----------------|---------|

|         | —        | TOUTPS3                       | TOUTPS2              | TOUTPS1       | TOUTPS0        | TMR2ON     | T2CKPS1        | T2CKPS0 |

|         | bit 7    |                               |                      |               |                |            |                | bit 0   |

|         |          |                               |                      |               |                |            |                |         |

| bit 7   | Unimple  | emented: Re                   | ead as '0'           |               |                |            |                |         |

| bit 6-3 | TOUTPS   | S3:TOUTPS                     | <b>0</b> : Timer2 Ou | itput Postsca | le Select bits |            |                |         |

|         | 0000 =   | 1:1 Postscal                  | e                    |               |                |            |                |         |

|         | 0001 =   | 1:2 Postscal                  | e                    |               |                |            |                |         |

|         | •        |                               |                      |               |                |            |                |         |

|         | •        |                               |                      |               |                |            |                |         |

|         | •        | 1:16 Postsca                  |                      |               |                |            |                |         |

|         |          |                               |                      |               |                |            |                |         |

| bit 2   |          | N: Timer2 O                   | n bit                |               |                |            |                |         |

|         | 1 = Time |                               |                      |               |                |            |                |         |

|         |          | er2 is off                    |                      |               |                |            |                |         |

| bit 1-0 |          |                               | : Timer2 Clo         | ck Prescale   | Select bits    |            |                |         |

|         |          | escaler is 1                  |                      |               |                |            |                |         |

|         |          | escaler is 4<br>escaler is 16 |                      |               |                |            |                |         |

|         | TX = HG  |                               |                      |               |                |            |                |         |

|         | Laward   |                               |                      |               |                |            |                |         |

|         | Legend:  |                               |                      |               |                |            |                |         |

|         | R = Rea  | dable bit                     | W =                  | Writable bit  |                | •          | l bit, read as | ʻ0'     |

|         | - n = Va | ue at POR r                   | eset '1' =           | Bit is set    | '0' = Bit      | is cleared | x = Bit is u   | unknown |

|         |          |                               |                      |               |                |            |                |         |

## 13.5.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

## TABLE 13-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F       | 0x1F       | 0x17       |

| Maximum Resolution (bits)  | 14       | 12       | 10        | 8          | 7          | 6.58       |

### TABLE 13-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Name    | Bit 7                | Bit 6         | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | PC   | ie on<br>)R,<br>)R | all o | ie on<br>other<br>SETS |

|---------|----------------------|---------------|-------------|---------|---------|--------|---------|---------|------|--------------------|-------|------------------------|

| INTCON  | GIE/<br>GIEH         | PEIE/<br>GIEL | TMR0IE      | INTOIE  | RBIE    | TMR0IF | INTOIF  | RBIF    | 0000 | 000x               | 0000  | 000u                   |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF          | RCIF        | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 | 0000               | 0000  | 0000                   |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE          | RCIE        | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 | 0000               | 0000  | 0000                   |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP          | RCIP        | TXIP    | SSPIP   | CCP1IP | TMR2IP  | TMR1IP  | 0000 | 0000               | 0000  | 0000                   |

| TRISC   | PORTC Da             | ata Direction | Register    |         |         |        |         |         | 1111 | 1111               | 1111  | 1111                   |

| TMR2    | Timer2 Mo            | dule Registe  | er          |         |         |        |         |         | 0000 | 0000               | 0000  | 0000                   |

| PR2     | Timer2 Mo            | dule Period   | Register    |         |         |        |         |         | 1111 | 1111               | 1111  | 1111                   |

| T2CON   | _                    | TOUTPS3       | TOUTPS2     | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000               | -000  | 0000                   |

| CCPR1L  | Capture/Co           | ompare/PWI    | M Register1 | (LSB)   |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                   |

| CCPR1H  | Capture/Co           | ompare/PWI    | M Register1 | (MSB)   |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                   |

| CCP1CON | _                    | _             | DC1B1       | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00   | 0000               | 00    | 0000                   |

| CCPR2L  | Capture/Co           | ompare/PWI    | M Register2 | (LSB)   |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                   |

| CCPR2H  | Capture/Co           | ompare/PWI    | M Register2 | (MSB)   |         |        |         |         | xxxx | xxxx               | uuuu  | uuuu                   |

| CCP2CON |                      |               | DC2B1       | DC2B0   | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00   | 0000               | 00    | 0000                   |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

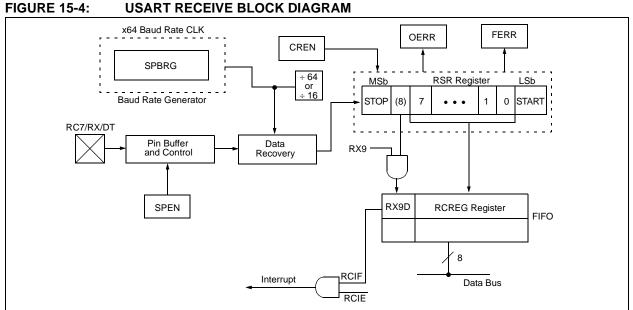

#### USART ASYNCHRONOUS 15.2.2 RECEIVER

The receiver block diagram is shown in Figure 15-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate, or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- Initialize the SPBRG register for the appropriate 1. baud rate. If a high speed baud rate is desired, set bit BRGH (Section 15.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- Enable the reception by setting bit CREN. 5.

- 6. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the 8. RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

### SETTING UP 9-BIT MODE WITH 15.2.3 ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address **Detect Enable:**

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is required, set the BRGH bit.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- If interrupts are required, set the RCEN bit and 3. select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- Set the ADDEN bit to enable address detect. 5.

- Enable reception by setting the CREN bit.

- The RCIF bit will be set when reception is com-7. plete. The interrupt will be acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

## 16.4 A/D Conversions

Figure 16-3 shows the operation of the A/D converter after the GO bit has been set. Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, acquisition on the selected channel is automatically started.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

## 16.5 Use of the CCP2 Trigger

An A/D conversion can be started by the "special event trigger" of the CCP2 module. This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/ DONE bit will be set, starting the A/D conversion and the Timer1 (or Timer3) counter will be reset to zero. Timer1 (or Timer3) is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH/ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 (or Timer3) counter.

|       | TAD TAD1   | l        |        |        |        | TAD6     |         |          |                    |    |    |  |

|-------|------------|----------|--------|--------|--------|----------|---------|----------|--------------------|----|----|--|

| TT    | <b>b</b> 9 | b8       | b7     | b6     | b5     | b4       | b3      | b2       | b1                 | b0 | b0 |  |

|       | Conver     | sion St  | arts   |        |        |          |         |          |                    |    |    |  |

| Hole  | ding capa  | citor is | discon | nected | trom a | inalog i | nput (t | ypically | <sup>,</sup> 100 n | s) |    |  |

| Set C | GO bit     |          |        | Ţ      |        |          |         |          |                    |    |    |  |

## FIGURE 16-3: A/D CONVERSION TAD CYCLES

| Name   | Bit 7                | Bit 6         | Bit 5        | Bit 4      | Bit 3 | Bit 2       | Bit 1         | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>RESETS |

|--------|----------------------|---------------|--------------|------------|-------|-------------|---------------|--------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH         | PEIE/<br>GIEL | TMR0IE       | INTOIE     | RBIE  | TMR0IF      | INT0IF        | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF          | RCIF         | TXIF       | SSPIF | CCP1IF      | TMR2IF        | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE          | RCIE         | TXIE       | SSPIE | CCP1IE      | TMR2IE        | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP          | RCIP         | TXIP       | SSPIP | CCP1IP      | TMR2IP        | TMR1IP | 0000 0000            | 0000 0000                       |

| PIR2   | _                    |               | _            | _          | BCLIF | LVDIF       | TMR3IF        | CCP2IF | 0000                 | 0000                            |

| PIE2   | _                    |               | —            | _          | BCLIE | LVDIE       | TMR3IE        | CCP2IE | 0000                 | 0000                            |

| IPR2   | _                    | _             | _            | —          | BCLIP | LVDIP       | TMR3IP        | CCP2IP | 0000                 | 0000                            |

| ADRESH | A/D Result           | t Register    |              |            |       |             |               |        | xxxx xxxx            | uuuu uuuu                       |

| ADRESL | A/D Result           | t Register    |              |            |       |             |               |        | xxxx xxxx            | uuuu uuuu                       |

| ADCON0 | ADCS1                | ADCS0         | CHS2         | CHS1       | CHS0  | GO/<br>DONE | —             | ADON   | 0000 00-0            | 0000 00-0                       |

| ADCON1 | ADFM                 | ADCS2         | _            | _          | PCFG3 | PCFG2       | PCFG1         | PCFG0  | 000                  | 000                             |

| PORTA  | _                    | RA6           | RA5          | RA4        | RA3   | RA2         | RA1           | RA0    | 0x 0000              | 0u 0000                         |

| TRISA  | —                    | PORTA D       | ata Directio | n Register |       |             |               |        | 11 1111              | 11 1111                         |

| PORTE  | _                    | —             | _            | —          | _     | RE2         | RE1           | RE0    | 000                  | 000                             |

| LATE   | —                    | _             | _            | —          | —     | LATE2       | LATE1         | LATE0  | xxx                  | uuu                             |

| TRISE  | IBF                  | OBF           | IBOV         | PSPMODE    |       | PORTE Da    | ata Directior | n bits | 0000 -111            | 0000 -111                       |

## TABLE 16-3: SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

NOTES:

## **19.1** Instruction Set

| ADD          | DLW                    | ADD litera                               | al to WRE             | G   |                  |  |  |  |  |  |

|--------------|------------------------|------------------------------------------|-----------------------|-----|------------------|--|--|--|--|--|

| Synt         | tax:                   | [ <i>label</i> ] A                       | DDLW I                | (   |                  |  |  |  |  |  |

| Ope          | rands:                 | $0 \le k \le 25$                         | 5                     |     |                  |  |  |  |  |  |

| Ope          | ration:                | (WREG) +                                 | $- k \rightarrow WRE$ | G   |                  |  |  |  |  |  |

| State        | us Affected:           | N,OV, C, [                               | DC, Z                 |     |                  |  |  |  |  |  |

| Enco         | oding:                 | 0000                                     | 1111 }                | kkk | kkkk             |  |  |  |  |  |

| Description: |                        | The conte<br>to the 8-bit<br>placed in V | t literal 'k' a       |     |                  |  |  |  |  |  |

| Words:       |                        | 1                                        | 1                     |     |                  |  |  |  |  |  |

| Cycles:      |                        | 1                                        | 1                     |     |                  |  |  |  |  |  |

| QC           | Cycle Activity:        |                                          |                       |     |                  |  |  |  |  |  |

|              | Q1                     | Q2                                       | Q3                    |     | Q4               |  |  |  |  |  |

|              | Decode                 | Read<br>literal 'k'                      | Process<br>Data       | -   | /rite to<br>VREG |  |  |  |  |  |

| <u>Exa</u>   | mple:<br>Before Instru | iction                                   | )x15                  |     |                  |  |  |  |  |  |

|              | WREG =                 |                                          |                       |     |                  |  |  |  |  |  |

|              | After Instruct         |                                          |                       |     |                  |  |  |  |  |  |

|              | WREG =                 | 0x25                                     |                       |     |                  |  |  |  |  |  |

|              |                        |                                          |                       |     |                  |  |  |  |  |  |

| ADDWF            | ADD WR                                                  | EG to f                                                                                                                                                                                                                              |       |      |                       |  |  |  |  |

|------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----------------------|--|--|--|--|

| Syntax:          | [ label ] A                                             | DDWF                                                                                                                                                                                                                                 | f [,d | d[,a | ] f [,d [,a]          |  |  |  |  |

| Operands:        | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                   | 5                                                                                                                                                                                                                                    |       |      |                       |  |  |  |  |

| Operation:       | (WREG) -                                                | (WREG) + (f) $\rightarrow$ dest                                                                                                                                                                                                      |       |      |                       |  |  |  |  |

| Status Affected: | N,OV, C,                                                | DC, Z                                                                                                                                                                                                                                |       |      |                       |  |  |  |  |

| Encoding:        | 0010                                                    | 01da                                                                                                                                                                                                                                 | fff   | f    | ffff                  |  |  |  |  |

| Description:     | the result<br>is 1, the re<br>ister 'f' (de<br>Access B | Add WREG to register 'f'. If 'd' is 0,<br>the result is stored in WREG. If 'd'<br>is 1, the result is stored back in reg-<br>ister 'f' (default). If 'a' is 0, the<br>Access Bank will be selected. If 'a'<br>is 1, the BSR is used. |       |      |                       |  |  |  |  |

| Words:           | 1                                                       |                                                                                                                                                                                                                                      |       |      |                       |  |  |  |  |

| Cycles:          | 1                                                       |                                                                                                                                                                                                                                      |       |      |                       |  |  |  |  |

| Q Cycle Activity |                                                         |                                                                                                                                                                                                                                      |       |      |                       |  |  |  |  |

| Q1               | Q2                                                      | Q3                                                                                                                                                                                                                                   | 3     |      | Q4                    |  |  |  |  |

| Decode           | Read<br>register 'f'                                    | Proce<br>Data                                                                                                                                                                                                                        |       |      | /rite to<br>stination |  |  |  |  |

| Example:         | ADDWF                                                   | REG,                                                                                                                                                                                                                                 | 0, 0  |      |                       |  |  |  |  |

| Before Instru    | uction                                                  |                                                                                                                                                                                                                                      |       |      |                       |  |  |  |  |

| WREG<br>REG      | = 0x17<br>= 0xC2                                        |                                                                                                                                                                                                                                      |       |      |                       |  |  |  |  |

| After Instruc    | tion                                                    |                                                                                                                                                                                                                                      |       |      |                       |  |  |  |  |

| WDEC             | - 0~09                                                  |                                                                                                                                                                                                                                      |       |      |                       |  |  |  |  |

| WREG | = | 0xD9 |

|------|---|------|

| REG  | = | 0xC2 |

| SLEEP             | Enter SL                             | EEP mode                     |             | SUBFWB           | Subtract          | f from WRE                           | G with borro     |  |  |

|-------------------|--------------------------------------|------------------------------|-------------|------------------|-------------------|--------------------------------------|------------------|--|--|

| Syntax:           | [ label ]                            | SLEEP                        |             | Syntax:          | [ label ]         | SUBFWB                               | f [,d [,a]       |  |  |

| Operands:         | None                                 |                              |             | Operands:        | $0 \le f \le 25$  | -                                    |                  |  |  |

| Operation:        | $00h \rightarrow W$                  | /DT,                         |             |                  | d ∈ [0,1]         |                                      |                  |  |  |

|                   |                                      | T postscaler,                |             |                  | a ∈ [0,1]         |                                      |                  |  |  |

|                   | $1 \rightarrow TO, 0 \rightarrow PD$ |                              |             | Operation:       |                   | $-(f) - (\overline{C}) -$            | → dest           |  |  |

|                   |                                      |                              |             | Status Affected: | N,OV, C,          | DC, Z                                |                  |  |  |

| Status Affected:  | TO, PD                               |                              |             | Encoding:        | 0101              | 0101 01da ffff ffff                  |                  |  |  |

| Encoding:         | 0000                                 | 0000 000                     |             | Description:     |                   | Subtract register 'f' and carry flag |                  |  |  |

| Description:      |                                      | er-down statu                |             |                  |                   | from WREG                            |                  |  |  |

|                   |                                      | The time-out<br>et. Watchdog |             |                  |                   | thod). If 'd' is<br>WREG. If 'd'     |                  |  |  |

|                   |                                      | caler are clea               |             |                  | is stored i       | in register 'f' (                    | default). If 'a' |  |  |

|                   | The proc                             | essor is put i               | nto SLEEP   |                  |                   | cess Bank w                          |                  |  |  |

|                   | mode wit                             | th the oscillat              | or stopped. |                  |                   | g the BSR va<br>bank will be s       |                  |  |  |

| Nords:            | 1                                    |                              |             |                  |                   | value (defau                         |                  |  |  |

| Cycles:           | 1                                    |                              |             | Words:           | 1                 |                                      |                  |  |  |

| Q Cycle Activity  | <i>/</i> :                           |                              |             | Cycles:          | 1                 |                                      |                  |  |  |

| Q1                | Q2                                   | Q3                           | Q4          | Q Cycle Activity |                   |                                      |                  |  |  |

| Decode            | No                                   | Process                      | Go to       | Q1               | Q2                | Q3                                   | Q4               |  |  |

|                   | operation                            | Data                         | sleep       | Decode           | Read              | Process                              | Write to         |  |  |

| Example:          | SLEEP                                |                              |             |                  | register 'f'      | Data                                 | destination      |  |  |

| Before Instr      | uction                               |                              |             | Example 1:       | SUBFWB            | REG, 1,                              | 0                |  |  |

| $\overline{TO} =$ | ?                                    |                              |             | Before Instru    | uction            |                                      |                  |  |  |

| PD =              | ?                                    |                              |             | REG              | = 3               |                                      |                  |  |  |

| After Instruc     | 1 †                                  |                              |             | WREG<br>C        | = 2<br>= 1        |                                      |                  |  |  |

| $\frac{10}{PD} =$ | 0                                    |                              |             | After Instruc    |                   |                                      |                  |  |  |

| f If WDT cause    | es wake-up, tl                       | his bit is clea              | red.        | REG              | = FF              |                                      |                  |  |  |

|                   |                                      |                              |             | WREG             | = 2               |                                      |                  |  |  |

|                   |                                      |                              |             | C<br>Z           | = 0<br>= 0        |                                      |                  |  |  |

|                   |                                      |                              |             | Ν                | = 1               | ; result :                           | is negativ       |  |  |

|                   |                                      |                              |             | Example 2:       | SUBFWB            | REG, 0,                              | 0                |  |  |

|                   |                                      |                              |             | Before Instru    | uction            |                                      |                  |  |  |

|                   |                                      |                              |             | REG              | = 2               |                                      |                  |  |  |

|                   |                                      |                              |             | WREG<br>C        | = 5<br>= 1        |                                      |                  |  |  |

|                   |                                      |                              |             | After Instruc    | tion              |                                      |                  |  |  |

|                   |                                      |                              |             | REG              | = 2               |                                      |                  |  |  |

|                   |                                      |                              |             | WREG<br>C        | = 3<br>= 1        |                                      |                  |  |  |

|                   |                                      |                              |             | Z                | = 1<br>= 0        |                                      |                  |  |  |

|                   |                                      |                              |             | Ν                | = 0               | ; result :                           | is positiv       |  |  |

|                   |                                      |                              |             | Example 3:       | SUBFWB            | REG, 1,                              | 0                |  |  |

|                   |                                      |                              |             | Before Instru    |                   |                                      |                  |  |  |

|                   |                                      |                              |             | REG              | = 1               |                                      |                  |  |  |

|                   |                                      |                              |             | WREG<br>C        | = 2<br>= 0        |                                      |                  |  |  |

|                   |                                      |                              |             | After Instruc    | tion              |                                      |                  |  |  |

|                   |                                      |                              |             | REG              | = 0               |                                      |                  |  |  |

|                   |                                      |                              |             |                  |                   |                                      |                  |  |  |

|                   |                                      |                              |             | WREG             | = 2               |                                      |                  |  |  |

|                   |                                      |                              |             | WREG<br>C<br>Z   | = 2<br>= 1<br>= 1 | ; result :                           | is zero          |  |  |

## 20.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD for PIC16F87X

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

## 20.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- A project manager

- Customizable toolbar and key mapping

- A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the costeffective simulator to a full-featured emulator with minimal retraining.

## 20.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

## 20.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

## 21.1 DC Characteristics

| PIC18LCXX2<br>(Industrial)          |        |                                                                     |                                                      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |       |                                           |  |  |  |  |

|-------------------------------------|--------|---------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------------------------|--|--|--|--|

| PIC18CXX2<br>(Industrial, Extended) |        |                                                                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                                                                                                    |      |       |                                           |  |  |  |  |

| Param<br>No.                        | Symbol | Characteristic                                                      | Min                                                  | Тур                                                                                                                                | Max  | Units | Conditions                                |  |  |  |  |

|                                     | Vdd    | Supply Voltage                                                      |                                                      |                                                                                                                                    |      |       |                                           |  |  |  |  |

| D001                                |        | PIC18LCXX2                                                          | 2.5                                                  | _                                                                                                                                  | 5.5  | V     | HS, XT, RC and LP osc mode                |  |  |  |  |

| D001                                |        | PIC18CXX2                                                           | 4.2                                                  | —                                                                                                                                  | 5.5  | V     |                                           |  |  |  |  |

| D002                                | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                        | 1.5                                                  | —                                                                                                                                  | -    | V     |                                           |  |  |  |  |

| D003                                | VPOR   | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    |                                                      | —                                                                                                                                  | 0.7  | V     | See section on Power-on Reset for details |  |  |  |  |

| D004                                | Svdd   | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.05                                                 | —                                                                                                                                  |      | V/ms  | See section on Power-on Reset for details |  |  |  |  |

|                                     | VBOR   | Brown-out Reset Voltage                                             |                                                      |                                                                                                                                    |      |       |                                           |  |  |  |  |

| D005                                |        | PIC18LCXX2                                                          |                                                      |                                                                                                                                    |      |       |                                           |  |  |  |  |

|                                     |        | BORV1:BORV0 = 11                                                    | 2.5                                                  | _                                                                                                                                  | 2.66 | V     |                                           |  |  |  |  |

|                                     |        | BORV1:BORV0 = 10                                                    | 2.7                                                  |                                                                                                                                    | 2.86 | V     |                                           |  |  |  |  |

|                                     |        | BORV1:BORV0 = 01                                                    | 4.2                                                  |                                                                                                                                    | 4.46 | V     |                                           |  |  |  |  |

|                                     |        | BORV1:BORV0 = 00                                                    | 4.5                                                  | —                                                                                                                                  | 4.78 | V     |                                           |  |  |  |  |

| D005                                |        | PIC18CXX2                                                           |                                                      |                                                                                                                                    |      |       |                                           |  |  |  |  |

|                                     |        | BORV1:BORV0 = 1x                                                    | N.A.                                                 | —                                                                                                                                  | N.A. | V     | Not in operating voltage range of device  |  |  |  |  |

|                                     |        | BORV1:BORV0 = 01                                                    | 4.2                                                  | —                                                                                                                                  | 4.46 | V     |                                           |  |  |  |  |

|                                     |        | BORV1:BORV0 = 00                                                    | 4.5                                                  | —                                                                                                                                  | 4.78 | V     |                                           |  |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode, or during a device RESET, without losing RAM data.

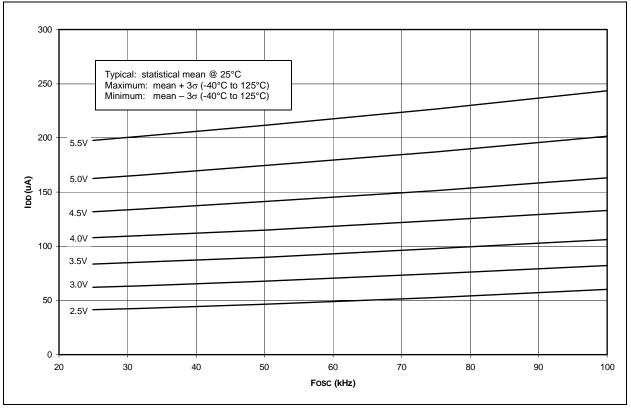

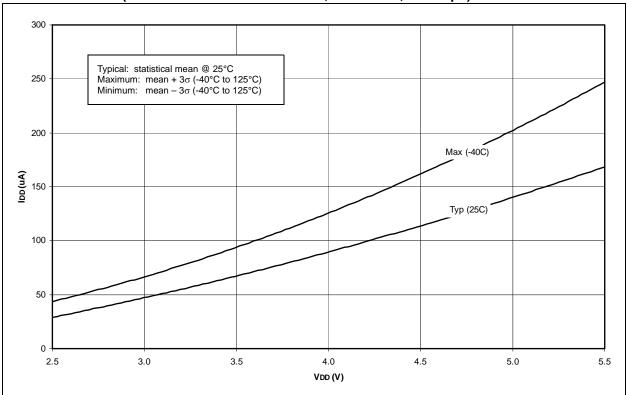

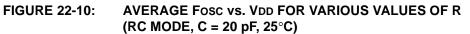

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss, and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR,...).

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

## 21.2 DC Characteristics: PIC18CXX2 (Industrial, Extended) PIC18LCXX2 (Industrial) (Continued)

| DC CHARACTERISTICS |        |                                            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |       |                                               |  |

|--------------------|--------|--------------------------------------------|------------------------------------------------------|-----|-------|-----------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                             | Min                                                  | Max | Units | Conditions                                    |  |

|                    | Vol    | Output Low Voltage                         |                                                      |     |       |                                               |  |

| D080               |        | I/O ports                                  | —                                                    | 0.6 | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C   |  |

| D080A              |        |                                            | —                                                    | 0.6 | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C  |  |

| D083               |        | OSC2/CLKOUT<br>(RC mode)                   | —                                                    | 0.6 | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C   |  |

| D083A              |        |                                            | —                                                    | 0.6 | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C  |  |

|                    | Vон    | Output High Voltage <sup>(3)</sup>         |                                                      |     |       |                                               |  |

| D090               |        | I/O ports                                  | Vdd - 0.7                                            | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С  |  |

| D090A              |        |                                            | Vdd - 0.7                                            | —   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С |  |

| D092               |        | OSC2/CLKOUT<br>(RC mode)                   | Vdd - 0.7                                            | —   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С  |  |

| D092A              |        |                                            | Vdd - 0.7                                            | —   | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С |  |

| D150               | Vod    | Open Drain High Voltage                    | _                                                    | 8.5 | V     | RA4 pin                                       |  |

|                    |        | Capacitive Loading Specs<br>on Output Pins |                                                      |     |       |                                               |  |

| D101               | Сю     | All I/O pins and OSC2<br>(in RC mode)      | —                                                    | 50  | pF    | To meet the AC Timing<br>Specifications       |  |

| D102               | Св     | SCL, SDA                                   | —                                                    | 400 | pF    | In I <sup>2</sup> C mode                      |  |

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC MCU be driven with an external clock while in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

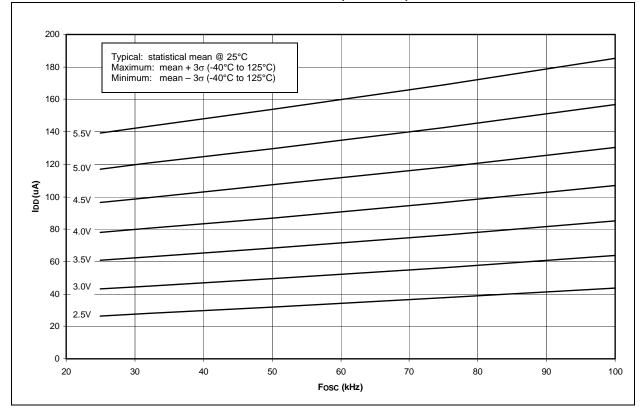

## FIGURE 22-7: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

FIGURE 22-9: TYPICAL AND MAXIMUM IDD vs. VDD (TIMER1 AS MAIN OSCILLATOR, 32.768 kHz, C = 47 pF)

© 1999-2013 Microchip Technology Inc.