### Microchip Technology - PIC18LC242-I/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lc242-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-2: PIC18C2X2 PINOUT I/O DESCRIPTIONS

| Dia Mara          | Pin N | umber      | Pin      | Buffer       | Description                                                                                                                                                     |

|-------------------|-------|------------|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name          | DIP   | SOIC       | Туре     | Туре         | Description                                                                                                                                                     |

| MCLR/VPP<br>MCLR  | 1     | 1          |          | ST           | Master clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active low                                                   |

|                   |       |            | '        | 31           | RESET to the device.                                                                                                                                            |

| VPP               |       |            | Р        |              | Programming voltage input.                                                                                                                                      |

| NC                | —     | —          | —        | _            | These pins should be left unconnected.                                                                                                                          |

| OSC1/CLKI<br>OSC1 | 9     | 9          | I        | ST           | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. CMOS otherwise |

| CLKI              |       |            | I        | CMOS         | External clock source input. Always associated with<br>pin function OSC1. (See related OSC1/CLKIN,<br>OSC2/CLKOUT pins.)                                        |

| OSC2/CLKO/RA6     | 10    | 10         |          |              | Oscillator crystal or clock output.                                                                                                                             |

| OSC2              |       |            | 0        | —            | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.                                                                         |

| CLKO              |       |            | 0        | _            | In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate.                                                |

| RA6               |       |            | I/O      | TTL          | General Purpose I/O pin.                                                                                                                                        |

| INAU              |       |            | 1/0      | 116          | PORTA is a bi-directional I/O port.                                                                                                                             |

|                   |       |            |          |              | PORTA is a di-directional i/O port.                                                                                                                             |

| RA0/AN0           | 2     | 2          |          | <b>TT</b> I  |                                                                                                                                                                 |

| RA0<br>AN0        |       |            | I/O      | TTL          | Digital I/O.<br>Analog input 0.                                                                                                                                 |

| -                 |       |            | 1        | Analog       | Analog input 0.                                                                                                                                                 |

| RA1/AN1           | 3     | 3          |          | <b>TT</b> I  | Disting 1/0                                                                                                                                                     |

| RA1               |       |            | I/O      | TTL          | Digital I/O.                                                                                                                                                    |

| AN1               |       |            | 1        | Analog       | Analog input 1.                                                                                                                                                 |

| RA2/AN2/VREF-     | 4     | 4          | 1/0      |              |                                                                                                                                                                 |

| RA2               |       |            | I/O      | TTL          | Digital I/O.                                                                                                                                                    |

| AN2<br>Vref-      |       |            |          | Analog       | Analog input 2.                                                                                                                                                 |

|                   | _     | _          | 1        | Analog       | A/D Reference Voltage (Low) input.                                                                                                                              |

| RA3/AN3/VREF+     | 5     | 5          |          | <b>TT</b> 1  |                                                                                                                                                                 |

| RA3               |       |            | I/O      | TTL          | Digital I/O.                                                                                                                                                    |

| AN3<br>Vref+      |       |            |          | Analog       | Analog input 3.<br>A/D Reference Voltage (High) input.                                                                                                          |

|                   |       |            | 1        | Analog       | AVD Relefence voltage (Fligh) linput.                                                                                                                           |

| RA4/T0CKI         | 6     | 6          | I/O      | ST/OD        | Digital I/O. Open drain when configured as output.                                                                                                              |

| RA4<br>T0CKI      |       |            | 1/0      | ST           | Timer0 external clock input.                                                                                                                                    |

|                   | -     | -          | 1        | 31           |                                                                                                                                                                 |

| RA5/AN4/SS/LVDIN  | 7     | 7          |          | <b>TT</b> 1  |                                                                                                                                                                 |

| RA5               |       |            | I/O      | TTL          | Digital I/O.                                                                                                                                                    |

| AN4<br>SS         |       |            |          | Analog<br>ST | Analog input 4.<br>SPI Slave Select input.                                                                                                                      |

| LVDIN             |       |            |          | Analog       | Low Voltage Detect Input.                                                                                                                                       |

|                   |       |            | '        | Analog       | - · ·                                                                                                                                                           |

| RA6               |       | elle ta di |          |              | See the OSC2/CLKO/RA6 pin.                                                                                                                                      |

| Legend: TTL = TTL |       |            |          |              | CMOS = CMOS compatible input or output                                                                                                                          |

| ST = Schm         |       | yer inpu   | i with C | INIO2 IEVEI  |                                                                                                                                                                 |

| O = Output        | L     |            |          |              | P = Power                                                                                                                                                       |

OD = Open Drain (no P diode to VDD)

|                                | Pin Number |        |      | D'          | Duffer         |                                                             |  |  |

|--------------------------------|------------|--------|------|-------------|----------------|-------------------------------------------------------------|--|--|

| Pin Name                       | DIP        | PLCC   | TQFP | Pin<br>Type | Buffer<br>Type | Description                                                 |  |  |

|                                |            | 1 200  | 14.1 |             |                | PORTC is a bi-directional I/O port.                         |  |  |

| RC0/T1OSO/T1CKI                | 15         | 16     | 32   |             |                |                                                             |  |  |

| RC0                            |            |        |      | I/O         | ST             | Digital I/O.                                                |  |  |

| T1OSO                          |            |        |      | 0           | _              | Timer1 oscillator output.                                   |  |  |

| T1CKI                          |            |        |      | Ι           | ST             | Timer1/Timer3 external clock input.                         |  |  |

| RC1/T1OSI/CCP2                 | 16         | 18     | 35   |             |                |                                                             |  |  |

| RC1                            |            |        |      | I/O         | ST             | Digital I/O.                                                |  |  |

| T1OSI                          |            |        |      |             | CMOS           | Timer1 oscillator input.                                    |  |  |

| CCP2                           | 47         | 40     |      | I/O         | ST             | Capture2 input, Compare2 output, PWM2 output.               |  |  |

| RC2/CCP1<br>RC2                | 17         | 19     | 36   | I/O         | ST             | Digital I/O                                                 |  |  |

| CCP1                           |            |        |      | 1/O<br>1/O  | ST             | Digital I/O.<br>Capture1 input/Compare1 output/PWM1 output. |  |  |

| RC3/SCK/SCL                    | 18         | 20     | 37   | "0          | 01             |                                                             |  |  |

| RC3                            | 10         | 20     | 57   | I/O         | ST             | Digital I/O.                                                |  |  |

| SCK                            |            |        |      | I/O         | ST             | Synchronous serial clock input/output for                   |  |  |

|                                |            |        |      |             |                | SPI mode.                                                   |  |  |

| SCL                            |            |        |      | I/O         | ST             | Synchronous serial clock input/output for                   |  |  |

|                                |            |        |      |             |                | I <sup>2</sup> C mode.                                      |  |  |

| RC4/SDI/SDA                    | 23         | 25     | 42   |             |                |                                                             |  |  |

| RC4                            |            |        |      | I/O         | ST             | Digital I/O.                                                |  |  |

| SDI<br>SDA                     |            |        |      | I<br>I/O    | ST<br>ST       | SPI Data In.<br>I <sup>2</sup> C Data I/O.                  |  |  |

|                                | 24         | 20     | 43   | 1/0         | 31             | T C Data 1/O.                                               |  |  |

| RC5/SDO<br>RC5                 | 24         | 26     | 43   | I/O         | ST             | Digital I/O.                                                |  |  |

| SDO                            |            |        |      | 0           | _              | SPI Data Out.                                               |  |  |

| RC6/TX/CK                      | 25         | 27     | 44   | -           |                |                                                             |  |  |

| RC6                            | 20         |        | ••   | I/O         | ST             | Digital I/O.                                                |  |  |

| ТХ                             |            |        |      | 0           | _              | USART Asynchronous Transmit.                                |  |  |

| СК                             |            |        |      | I/O         | ST             | USART Synchronous Clock (see related RX/DT).                |  |  |

| RC7/RX/DT                      | 26         | 29     | 1    |             |                |                                                             |  |  |

| RC7                            |            |        |      | I/O         | ST             | Digital I/O.                                                |  |  |

| RX                             |            |        |      |             | ST             | USART Asynchronous Receive.                                 |  |  |

|                                |            | 41-1-1 |      | I/O         | ST             | USART Synchronous Data (see related TX/CK).                 |  |  |

| Legend: TTL = TTL<br>ST = Schn |            |        |      |             |                | OS = CMOS compatible input or output                        |  |  |

#### PIC18C4X2 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-3:**

ST = Schmitt Trigger input with CMOS levels I = Input

O = Output

P = Power

OD = Open Drain (no P diode to VDD)

#### 2.7 Effects of SLEEP Mode on the On-chip Oscillator

When the device executes a SLEEP instruction, the on-chip clocks and oscillator are turned off and the device is held at the beginning of an instruction cycle (Q1 state). With the oscillator off, the OSC1 and OSC2 signals will stop oscillating. Since all the transistor

switching currents have been removed, SLEEP mode achieves the lowest current consumption of the device (only leakage currents). Enabling any on-chip feature that will operate during SLEEP will increase the current consumed during SLEEP. The user can wake from SLEEP through external RESET, Watchdog Timer Reset, or through an interrupt.

#### TABLE 2-3:OSC1 AND OSC2 PIN STATES IN SLEEP MODE

| OSC Mode       | OSC1 Pin                                                  | OSC2 Pin                                                  |  |  |

|----------------|-----------------------------------------------------------|-----------------------------------------------------------|--|--|

| RC             | Floating, external resistor should pull high              | At logic low                                              |  |  |

| RCIO           | Floating, external resistor should pull high              | Configured as PORTA, bit 6                                |  |  |

| ECIO           | Floating                                                  | Configured as PORTA, bit 6                                |  |  |

| EC             | Floating                                                  | At logic low                                              |  |  |

| LP, XT, and HS | Feedback inverter disabled, at<br>quiescent voltage level | Feedback inverter disabled, at<br>quiescent voltage level |  |  |

**Note:** See Table 3-1, in Section 3.0 RESET, for time-outs due to SLEEP and MCLR Reset.

#### 2.8 Power-up Delays

Power up delays are controlled by two timers, so that no external RESET circuitry is required for most applications. The delays ensure that the device is kept in RESET until the device power supply and clock are stable. For additional information on RESET operation, see the "RESET" section.

The first timer is the Power-up Timer (PWRT), which optionally provides a fixed delay of 72 ms (nominal) on power-up only (POR and BOR). The second timer is the Oscillator Start-up Timer, OST, intended to keep the chip in RESET until the crystal oscillator is stable.

With the PLL enabled (HS/PLL oscillator mode), the time-out sequence following a Power-on Reset is different from other oscillator modes. The time-out sequence is as follows: First, the PWRT time-out is invoked after a POR time delay has expired. Then, the Oscillator Start-up Timer (OST) is invoked. However, this is still not a sufficient amount of time to allow the PLL to lock at high frequencies. The PWRT timer is used to provide an additional fixed 2ms (nominal) time-out to allow the PLL ample time to lock to the incoming clock frequency.

| ABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                    |     |                                    |                                                               |                                   |           |           |  |  |

|-------------------------------------------------------------------|--------------------|-----|------------------------------------|---------------------------------------------------------------|-----------------------------------|-----------|-----------|--|--|

| Register                                                          | Applicable Devices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>n or Interrupt |           |           |  |  |

| FSR1H                                                             | 242                | 442 | 252                                | 452                                                           | 0000                              | 0000      | uuuu      |  |  |

| FSR1L                                                             | 242                | 442 | 252                                | 452                                                           | xxxx xxxx                         | uuuu uuuu | uuuu uuuu |  |  |

| BSR                                                               | 242                | 442 | 252                                | 452                                                           | 0000                              | 0000      | uuuu      |  |  |

| INDF2                                                             | 242                | 442 | 252                                | 452                                                           | N/A                               | N/A       | N/A       |  |  |

| POSTINC2                                                          | 242                | 442 | 252                                | 452                                                           | N/A                               | N/A       | N/A       |  |  |

| POSTDEC2                                                          | 242                | 442 | 252                                | 452                                                           | N/A                               | N/A       | N/A       |  |  |

| PREINC2                                                           | 242                | 442 | 252                                | 452                                                           | N/A                               | N/A       | N/A       |  |  |

| PLUSW2                                                            | 242                | 442 | 252                                | 452                                                           | N/A                               | N/A       | N/A       |  |  |

| FSR2H                                                             | 242                | 442 | 252                                | 452                                                           | 0000                              | 0000      | uuuu      |  |  |

| FSR2L                                                             | 242                | 442 | 252                                | 452                                                           | xxxx xxxx                         | սսսս սսսս | uuuu uuuu |  |  |

| STATUS                                                            | 242                | 442 | 252                                | 452                                                           | x xxxx                            | u uuuu    | u uuuu    |  |  |

| TMR0H                                                             | 242                | 442 | 252                                | 452                                                           | xxxx xxxx                         | սսսս սսսս | uuuu uuuu |  |  |

| TMR0L                                                             | 242                | 442 | 252                                | 452                                                           | xxxx xxxx                         | uuuu uuuu | uuuu uuuu |  |  |

| T0CON                                                             | 242                | 442 | 252                                | 452                                                           | 1111 1111                         | 1111 1111 | uuuu uuuu |  |  |

| OSCCON                                                            | 242                | 442 | 252                                | 452                                                           | 0                                 | 0         | u         |  |  |

| LVDCON                                                            | 242                | 442 | 252                                | 452                                                           | 00 0101                           | 00 0101   | uu uuuu   |  |  |

| WDTCON                                                            | 242                | 442 | 252                                | 452                                                           | 0                                 | 0         | u         |  |  |

| RCON <sup>(4, 6)</sup>                                            | 242                | 442 | 252                                | 452                                                           | 00-1 11q0                         | 00-1 qquu | uu-u qquu |  |  |

| TMR1H                                                             | 242                | 442 | 252                                | 452                                                           | xxxx xxxx                         | uuuu uuuu | uuuu uuuu |  |  |

| TMR1L                                                             | 242                | 442 | 252                                | 452                                                           | xxxx xxxx                         | uuuu uuuu | นนนน นนนน |  |  |

| T1CON                                                             | 242                | 442 | 252                                | 452                                                           | 0-00 0000                         | u-uu uuuu | u-uu uuuu |  |  |

| TMR2                                                              | 242                | 442 | 252                                | 452                                                           | xxxx xxxx                         | uuuu uuuu | นนนน นนนน |  |  |

| PR2                                                               | 242                | 442 | 252                                | 452                                                           | 1111 1111                         | 1111 1111 | 1111 1111 |  |  |

| T2CON                                                             | 242                | 442 | 252                                | 452                                                           | -000 0000                         | -000 0000 | -uuu uuuu |  |  |

| SSPBUF                                                            | 242                | 442 | 252                                | 452                                                           | xxxx xxxx                         | uuuu uuuu | นนนน นนนน |  |  |

| SSPADD                                                            | 242                | 442 | 252                                | 452                                                           | 0000 0000                         | 0000 0000 | นนนน นนนน |  |  |

| SSPSTAT                                                           | 242                | 442 | 252                                | 452                                                           | 0000 0000                         | 0000 0000 | սսսս սսսս |  |  |

| SSPCON1                                                           | 242                | 442 | 252                                | 452                                                           | 0000 0000                         | 0000 0000 | นนนน นนนน |  |  |

| SSPCON2                                                           | 242                | 442 | 252                                | 452                                                           | 0000 0000                         | 0000 0000 | uuuu uuuu |  |  |

TABLE 3-3:

INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for RESET value for specific condition.

- 5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

- 6: The long write enable is only reset on a POR or  $\overline{\text{MCLR}}$  Reset.

- 7: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read as '0'.

#### 4.3 Fast Register Stack

A "fast interrupt return" option is available for interrupts. A Fast Register Stack is provided for the STATUS, WREG and BSR registers and are only one in depth. The stack is not readable or writable and is loaded with the current value of the corresponding register when the processor vectors for an interrupt. The values in the registers are then loaded back into the working registers, if the FAST RETURN instruction is used to return from the interrupt.

A low or high priority interrupt source will push values into the stack registers. If both low and high priority interrupts are enabled, the stack registers cannot be used reliably for low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten.

If high priority interrupts are not disabled during low priority interrupts, users must save the key registers in software during a low priority interrupt.

If no interrupts are used, the fast register stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a FAST CALL instruction must be executed.

Example 4-1 shows a source code example that uses the fast register stack.

#### EXAMPLE 4-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|-----------------|---------------------------------------------------------|

| SUB1            |                                                         |

| RETURN FAST     | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

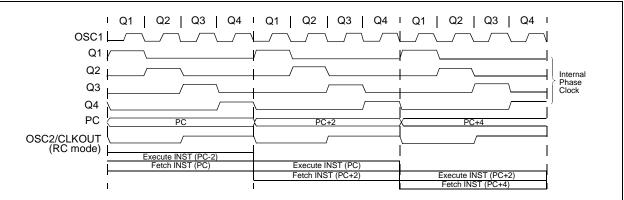

#### FIGURE 4-4: CLOCK/INSTRUCTION CYCLE

4.4 PCL, PCLATH and PCLATU

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21-bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCH register. The Upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCU register may be performed through the PCLATU register.

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the LSB of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

The contents of PCLATH and PCLATU will be transferred to the program counter by an operation that writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see Section 4.8.1).

#### 4.5 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 4-4.

#### EXAMPLE 6-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, | W    |   |                  |

|---|--------|--------|------|---|------------------|

|   | MULWF  | ARG2L  |      | ; | ARG1L * ARG2L -> |

|   |        |        |      | ; | PRODH: PRODL     |

|   | MOVFF  | PRODH, | RES1 | ; |                  |

|   | MOVFF  | PRODL, | RES0 | ; |                  |

| ; |        |        |      |   |                  |

|   | MOVF   | ARG1H, | W    |   |                  |

|   | MULWF  | ARG2H  |      | ; | ARG1H * ARG2H -> |

|   |        |        |      | ; | PRODH: PRODL     |

|   | MOVFF  | PRODH, | RES3 | ; |                  |

|   | MOVFF  | PRODL, | RES2 | ; |                  |

| ; |        |        |      |   |                  |

|   | MOVF   | ARG1L, | W    |   |                  |

|   | MULWF  | ARG2H  |      | ; | ARG1L * ARG2H -> |

|   |        |        |      | ; | PRODH: PRODL     |

|   | MOVF   | PRODL, | W    | ; |                  |

|   | ADDWF  | RES1,  | F    | ; | Add cross        |

|   | MOVF   | PRODH, | W    | ; | products         |

|   | ADDWFC | RES2,  | F    | ; |                  |

|   | CLRF   | WREG,  | F    | ; |                  |

|   | ADDWFC | RES3,  | F    | ; |                  |

| ; |        |        |      |   |                  |

|   | MOVF   | ARG1H, | W    | ; |                  |

|   | MULWF  | ARG2L  |      | ; | ARG1H * ARG2L -> |

|   |        |        |      | ; | PRODH: PRODL     |

|   | MOVF   | PRODL, | W    | ; |                  |

|   | ADDWF  | RES1,  |      | ; | Add cross        |

|   | MOVF   | PRODH, | W    | ; | products         |

|   | ADDWFC | RES2,  | F    | ; |                  |

|   | CLRF   | WREG,  | F    | ; |                  |

|   | ADDWFC | RES3,  | F    | ; |                  |

|   |        |        |      |   |                  |

Example 6-4 shows the sequence to do a 16 x 16 signed multiply. Equation 6-2 shows the algorithm used. The 32-bit result is stored in four registers, RES3:RES0. To account for the sign bits of the arguments, each argument pairs' Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EQUATION 6-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

RES3:RES0

= ARG1H:ARG1L • ARG2H:ARG2L = (ARG1H • ARG2H • 2<sup>16</sup>)+ (ARG1H • ARG2L • 2<sup>8</sup>)+ (ARG1L • ARG2L • 2<sup>8</sup>)+ (ARG1L • ARG2L)+ (-1 • ARG2L

```

(-1 \bullet ARG1H < 7 > \bullet ARG2H: ARG2L \bullet 2^{16})

```

#### EXAMPLE 6-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|    | MOVF    | ARG1L, V            | W    |   |                  |

|----|---------|---------------------|------|---|------------------|

|    | MULWF   | ARG2L               |      | ; | ARG1L * ARG2L -> |

|    |         |                     |      | ; | PRODH: PRODL     |

|    | MOVFF   | PRODH, H            | RES1 | ; |                  |

|    | MOVFF   | PRODL, H            | RESO | ; |                  |

| ;  |         |                     |      |   |                  |

|    | MOVF    | ARG1H, V            | W    |   |                  |

|    | MULWF   | ARG2H               |      | ; | ARG1H * ARG2H -> |

|    |         |                     |      |   | PRODH: PRODL     |

|    | MOVFF   | PRODH, H            | RES3 | ; |                  |

|    | MOVFF   | PRODL, H            |      |   |                  |

| ;  |         | 111022, 1           |      | ' |                  |

| '  | MOVF    | ARG1L, V            | TAT  |   |                  |

|    | MULWF   | ARG11, ARG2H        |      |   | ARG1L * ARG2H -> |

|    | HOLWI   | AICOZII             |      |   | PRODH: PRODL     |

|    | MOVF    | ז זמספת             | TAT  |   | PRODITIPRODE     |

|    | ADDWF   | PRODL, N<br>RES1, N |      | ; | Add cross        |

|    |         |                     |      |   |                  |

|    | MOVF    | PRODH, V            |      |   | products         |

|    | ADDWFC  | RES2, I             |      | ; |                  |

|    | CLRF    | WREG, I             |      | ; |                  |

|    | ADDWFC  | RES3, I             | F.   | ; |                  |

| ;  | MOTE    | 100111              |      |   |                  |

|    | MOVF    | ARG1H, V            | W    | ; |                  |

|    | MULWF   | ARG2L               |      |   | ARG1H * ARG2L -> |

|    |         |                     |      |   | PRODH: PRODL     |

|    | MOVF    | PRODL, V            |      | ; |                  |

|    | ADDWF   | RES1, I             |      |   | Add cross        |

|    | MOVF    | PRODH, V            |      | ; | products         |

|    | ADDWFC  | RES2, F             |      | ; |                  |

|    | CLRF    | WREG, F             |      | ; |                  |

|    | ADDWFC  | RES3, F             |      | ; |                  |

| ;  |         |                     |      |   |                  |

|    | BTFSS   |                     |      | ; | ARG2H:ARG2L neg? |

|    | BRA     | SIGN_ARG            |      | ; | no, check ARG1   |

|    | MOVF    | ARG1L, V            | W    | ; |                  |

|    | SUBWF   | RES2                |      | ; |                  |

|    | MOVF    | ARG1H, V            | W    | ; |                  |

|    | SUBWFB  | RES3                |      |   |                  |

| ;  |         |                     |      |   |                  |

| SI | GN_ARG1 |                     |      |   |                  |

|    | BTFSS   | ARG1H,              |      |   | ARG1H:ARG1L neg? |

|    | BRA     | CONT_COI            | DE   | ; | no, done         |

|    | MOVF    | ARG2L, V            | W    | ; |                  |

|    | SUBWF   | RES2                |      | ; |                  |

|    | MOVF    | ARG2H, V            | W    | ; |                  |

|    | SUBWFB  | RES3                |      |   |                  |

| ;  |         |                     |      |   |                  |

| CO | NT_CODE |                     |      |   |                  |

|    | :       |                     |      |   |                  |

|    |         |                     |      |   |                  |

#### 7.6 INT0 Interrupt

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge triggered: either rising, if the corresponding INTEDGx bit is set in the INTCON2 register, or falling, if the INTEDGx bit is clear. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit INTxF is set. This interrupt can be disabled by clearing the corresponding enable bit INTxE. Flag bit INTxF must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt. All external interrupts (INT0, INT1 and INT2) can wake-up the processor from SLEEP, if bit INTxE was set prior to going into SLEEP. If the global interrupt enable bit GIE set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high priority interrupt source.

#### 7.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF. In 16-bit mode, an overflow (FFFFh  $\rightarrow$  0000h) in the TMR0H:TMR0L registers will set flag bit TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit TOIE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit TMR0IP (INTCON2<2>). See Section 8.0 for further details on the Timer0 module.

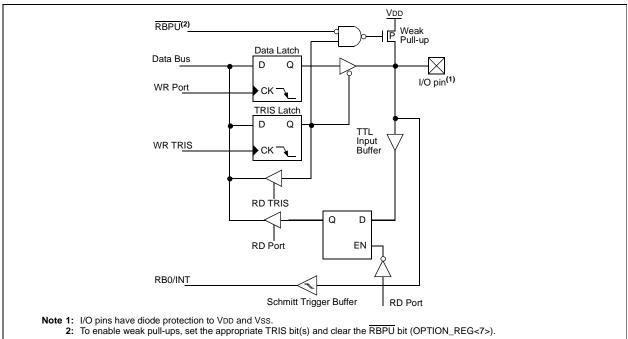

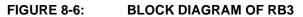

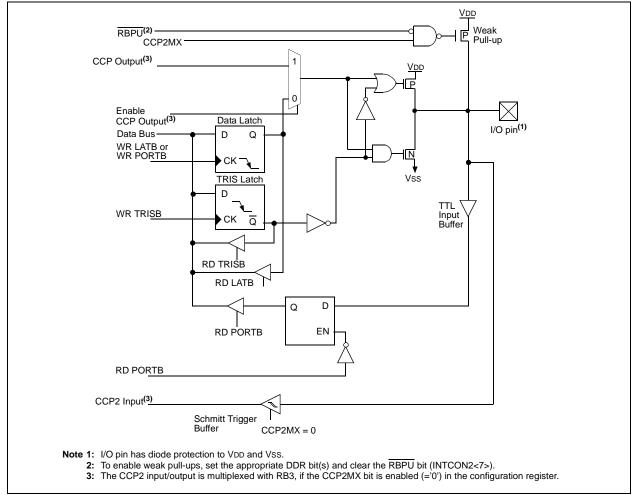

#### 7.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB Interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

### 7.9 Context Saving During Interrupts

During an interrupt, the return PC value is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see Section 4.3), the user may need to save the WREG, STATUS and BSR registers in software. Depending on the user's application, other registers may also need to be saved. Example 7-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| MOVWF  | W_TEMP              | ; W_TEMP is in virtual bank    |

|--------|---------------------|--------------------------------|

| MOVFF  | STATUS, STATUS_TEMP | ; STATUS_TEMP located anywhere |

| MOVFF  | BSR, BSR_TEMP       | ; BSR located anywhere         |

| ;      |                     |                                |

| ; USER | ISR CODE            |                                |

| ;      |                     |                                |

| MOVFF  | BSR_TEMP, BSR       | ; Restore BSR                  |

| MOVF   | W_TEMP, W           | ; Restore WREG                 |

| MOVFF  | STATUS TEMP, STATUS | ; Restore STATUS               |

|        | —                   |                                |

|        |                     |                                |

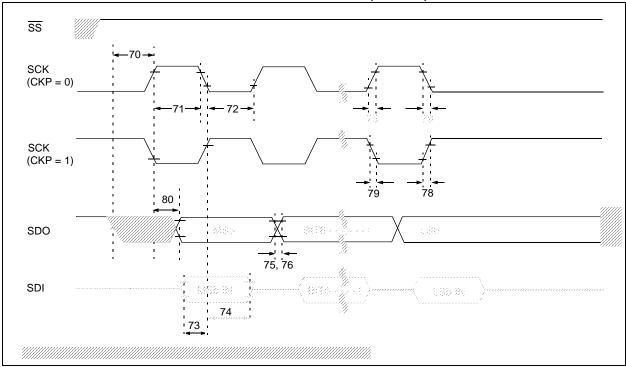

### 14.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2).

#### REGISTER 14-1: SSPSTAT: MSSP STATUS REGISTER

- n = Value at POR

'1' = Bit is set

|       | R/W-0                               | R/W-0                                                                    | R-0                      | R-0            | R-0             | R-0             | R-0            | R-0      |  |  |

|-------|-------------------------------------|--------------------------------------------------------------------------|--------------------------|----------------|-----------------|-----------------|----------------|----------|--|--|

|       | SMP                                 | CKE                                                                      | D/A                      | Р              | S               | R/W             | UA             | BF       |  |  |

|       | bit 7                               | 1                                                                        | 1                        | 1              |                 |                 |                | bit 0    |  |  |

| bit 7 | SMD: Som                            | nlo hit                                                                  |                          |                |                 |                 |                |          |  |  |

|       | SMP: Sample bit<br>SPI Master mode: |                                                                          |                          |                |                 |                 |                |          |  |  |

|       |                                     |                                                                          | l at end of da           | ata outout tii | me              |                 |                |          |  |  |

|       | -                                   |                                                                          | l at middle o            |                |                 |                 |                |          |  |  |

|       | SPI Slave r                         |                                                                          |                          |                |                 |                 |                |          |  |  |

|       |                                     |                                                                          | when SPI is              | used in Slav   | /e mode         |                 |                |          |  |  |

|       |                                     | ter or Slave                                                             |                          |                |                 |                 |                |          |  |  |

|       |                                     |                                                                          |                          | standard sp    | eed mode (1     | 00 kHz and      | 1 MHz)         |          |  |  |

|       | 0 = Slew r                          | ate control e                                                            | enabled for h            | nigh speed r   | node (400 kl    | Hz)             |                |          |  |  |

| bit 6 | CKE: SPI (                          | Clock Edge                                                               | Select bit               |                |                 |                 |                |          |  |  |

|       | <u>CKP = 0:</u>                     |                                                                          |                          |                |                 |                 |                |          |  |  |

|       | 1 = Data tra                        | ansmitted or                                                             | n rising edge            | e of SCK       |                 |                 |                |          |  |  |

|       | 0 = Data tra                        | ansmitted or                                                             | n falling edg            | e of SCK       |                 |                 |                |          |  |  |

|       | <u>CKP = 1:</u>                     |                                                                          |                          |                |                 |                 |                |          |  |  |

|       |                                     |                                                                          | n falling edg            |                |                 |                 |                |          |  |  |

|       |                                     |                                                                          | n rising edge            |                |                 |                 |                |          |  |  |

| bit 5 |                                     |                                                                          | (I <sup>2</sup> C mode o |                |                 |                 |                |          |  |  |

|       |                                     |                                                                          | •                        |                | smitted was     |                 |                |          |  |  |

|       | 0 = Indicate                        | es that the la                                                           | ast byte rece            | eived or tran  | smitted was     | address         |                |          |  |  |

| bit 4 | P: STOP b                           |                                                                          |                          |                |                 |                 |                |          |  |  |

|       | •                                   | •                                                                        |                          |                |                 |                 | SSPEN is c     | leared.) |  |  |

|       |                                     |                                                                          |                          |                | ed last (this b | oit is '0' on R | ESET)          |          |  |  |

|       | 0 = STOP                            | bit was not c                                                            | letected last            |                |                 |                 |                |          |  |  |

|       | Legend:                             |                                                                          |                          |                |                 |                 |                |          |  |  |

|       | R = Reada                           | ble bit                                                                  | W = Writab               | le bit         | U = Unimpl      | emented bit     | t. read as '0' |          |  |  |

|       |                                     | R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$ |                          |                |                 |                 |                |          |  |  |

'0' = Bit is cleared

x = Bit is unknown

### REGISTER 14-1: SSPSTAT: MSSP STATUS REGISTER (CONTINUED)

|       | R/W-0                                                                                                                                                                                     | R/W-0                            | R-0                         | R-0         | R-0            | R-0             | R-0            | R-0          |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------|-------------|----------------|-----------------|----------------|--------------|--|--|--|

|       | SMP                                                                                                                                                                                       | CKE                              | D/Ā                         | Р           | S              | R/W             | UA             | BF           |  |  |  |

|       | bit 7                                                                                                                                                                                     |                                  |                             |             |                |                 |                | bit 0        |  |  |  |

|       |                                                                                                                                                                                           |                                  |                             |             |                |                 |                |              |  |  |  |

| bit 3 | S: START bit                                                                                                                                                                              |                                  |                             |             |                |                 |                |              |  |  |  |

|       | (I <sup>2</sup> C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)<br>1 = Indicates that a START bit has been detected last (this bit is '0' on RESET) |                                  |                             |             |                |                 |                |              |  |  |  |

|       |                                                                                                                                                                                           |                                  | detected las                |             | ied last (this | Dit is 'U' on I | RESEI)         |              |  |  |  |

| bit 2 | R/W: Read                                                                                                                                                                                 | /Write bit inf                   | formation (I <sup>2</sup>   | C mode onl  | y)             |                 |                |              |  |  |  |

|       |                                                                                                                                                                                           |                                  |                             | •           | he last addre  |                 | his bit is onl | y valid from |  |  |  |

|       |                                                                                                                                                                                           |                                  | ne next STA                 | RT bit, STO | P bit, or not  | ACK bit.        |                |              |  |  |  |

|       | In I <sup>2</sup> C Slav                                                                                                                                                                  | <u>e mode:</u>                   |                             |             |                |                 |                |              |  |  |  |

|       | 0 = Write                                                                                                                                                                                 |                                  |                             |             |                |                 |                |              |  |  |  |

|       | In I <sup>2</sup> C Mast                                                                                                                                                                  |                                  |                             |             |                |                 |                |              |  |  |  |

|       |                                                                                                                                                                                           | it is in progr                   |                             |             |                |                 |                |              |  |  |  |

|       |                                                                                                                                                                                           | nit is not in p<br>this bit with | •                           | I. PEN. RCI | EN, or ACKE    | N will indica   | ate if the MS  | SP is in     |  |  |  |

|       | IDLE m                                                                                                                                                                                    |                                  | •=, •••=-                   | .,,         |                |                 |                |              |  |  |  |

| bit 1 | UA: Update                                                                                                                                                                                | e Address b                      | it (10-bit I <sup>2</sup> C | mode only)  |                |                 |                |              |  |  |  |

|       |                                                                                                                                                                                           |                                  |                             |             | address in t   | the SSPADE      | O register     |              |  |  |  |

|       |                                                                                                                                                                                           |                                  | need to be u                | pdated      |                |                 |                |              |  |  |  |

| bit 0 |                                                                                                                                                                                           | Full Status b                    |                             |             |                |                 |                |              |  |  |  |

|       |                                                                                                                                                                                           | <u>PI and I<sup>2</sup>C r</u>   |                             | full        |                |                 |                |              |  |  |  |

|       | <ol> <li>Receive complete, SSPBUF is full</li> <li>Receive not complete, SSPBUF is empty</li> </ol>                                                                                       |                                  |                             |             |                |                 |                |              |  |  |  |

|       |                                                                                                                                                                                           | <sup>2</sup> C mode on           |                             |             |                |                 |                |              |  |  |  |

|       | 1 = Data transmit in progress (does not include the ACK and STOP bits), SSPBUF is full                                                                                                    |                                  |                             |             |                |                 |                |              |  |  |  |

|       | $0 = Data transmit complete (does not include the \overline{ACK} and STOP bits), SSPBUF is empty$                                                                                         |                                  |                             |             |                |                 |                |              |  |  |  |

|       | Legend:                                                                                                                                                                                   |                                  |                             |             |                |                 |                |              |  |  |  |

|       | R = Reada                                                                                                                                                                                 | ble bit                          | W = Writab                  | le bit      | U = Unimpl     | emented bit     | , read as '0'  |              |  |  |  |

|       | - n = Value                                                                                                                                                                               | at POR                           | '1' = Bit is s              | set         | '0' = Bit is c | leared          | x = Bit is ur  | nknown       |  |  |  |

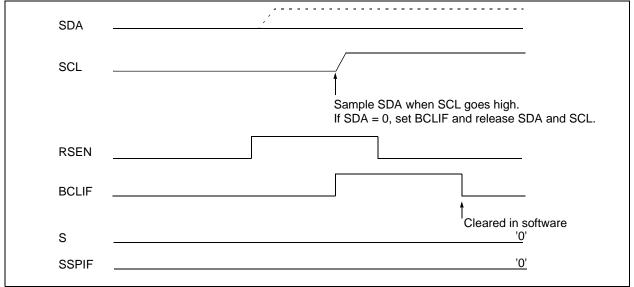

## 14.4.16.2 Bus Collision During a Repeated START Condition

During a Repeated START condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then de-asserted, and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 14-27). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

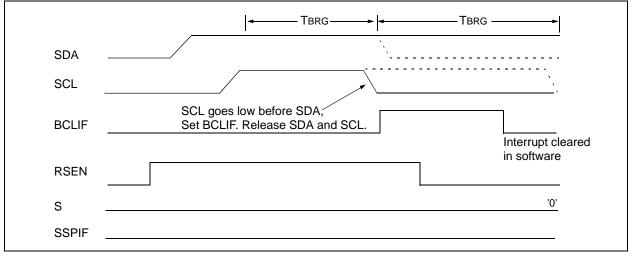

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated START condition, Figure 14-28.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated START condition is complete.

#### FIGURE 14-28: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

| Name   | Bit 7                           | Bit 6         | Bit 5  | Bit 4   | Bit 3 | Bit 2       | Bit 1         | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>RESETS |

|--------|---------------------------------|---------------|--------|---------|-------|-------------|---------------|-----------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH                    | PEIE/<br>GIEL | TMR0IE | INTOIE  | RBIE  | TMR0IF      | INT0IF        | RBIF      | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>            | ADIF          | RCIF   | TXIF    | SSPIF | CCP1IF      | TMR2IF        | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>            | ADIE          | RCIE   | TXIE    | SSPIE | CCP1IE      | TMR2IE        | TMR1IE    | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>            | ADIP          | RCIP   | TXIP    | SSPIP | CCP1IP      | TMR2IP        | TMR1IP    | 0000 0000            | 0000 0000                       |

| PIR2   | _                               |               | _      | _       | BCLIF | LVDIF       | TMR3IF        | CCP2IF    | 0000                 | 0000                            |

| PIE2   | _                               |               | —      | _       | BCLIE | LVDIE       | TMR3IE        | CCP2IE    | 0000                 | 0000                            |

| IPR2   | _                               | _             | _      | —       | BCLIP | LVDIP       | TMR3IP        | CCP2IP    | 0000                 | 0000                            |

| ADRESH | A/D Result Register             |               |        |         |       |             | xxxx xxxx     | uuuu uuuu |                      |                                 |

| ADRESL | A/D Result Register             |               |        |         |       |             | xxxx xxxx     | uuuu uuuu |                      |                                 |

| ADCON0 | ADCS1                           | ADCS0         | CHS2   | CHS1    | CHS0  | GO/<br>DONE | —             | ADON      | 0000 00-0            | 0000 00-0                       |

| ADCON1 | ADFM                            | ADCS2         | _      | _       | PCFG3 | PCFG2       | PCFG1         | PCFG0     | 000                  | 000                             |

| PORTA  | _                               | RA6           | RA5    | RA4     | RA3   | RA2         | RA1           | RA0       | 0x 0000              | 0u 0000                         |

| TRISA  | — PORTA Data Direction Register |               |        |         |       |             | 11 1111       | 11 1111   |                      |                                 |

| PORTE  | _                               | —             | _      | —       | _     | RE2         | RE1           | RE0       | 000                  | 000                             |

| LATE   | —                               | _             | _      | —       | —     | LATE2       | LATE1         | LATE0     | xxx                  | uuu                             |

| TRISE  | IBF                             | OBF           | IBOV   | PSPMODE |       | PORTE Da    | ata Directior | n bits    | 0000 -111            | 0000 -111                       |

#### TABLE 16-3: SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

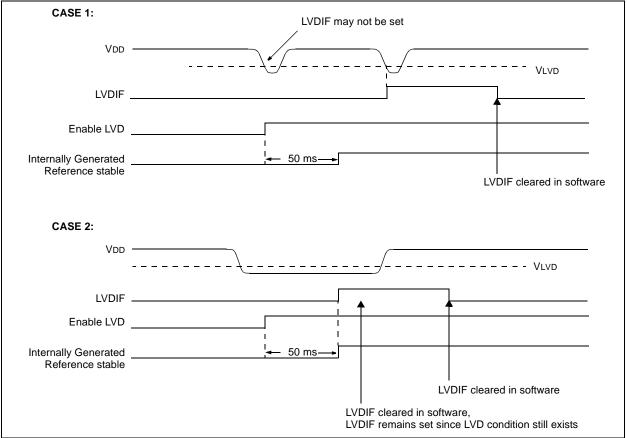

#### 17.2 Operation

Depending on the power source for the device voltage, the voltage normally decreases relatively slowly. This means that the LVD module does not need to be constantly operating. To decrease the current requirements, the LVD circuitry only needs to be enabled for short periods, where the voltage is checked. After doing the check, the LVD module may be disabled.

Each time that the LVD module is enabled, the circuitry requires some time to stabilize. After the circuitry has stabilized, all status flags may be cleared. The module will then indicate the proper state of the system.

The following steps are needed to set up the LVD module:

- Write the value to the LVDL3:LVDL0 bits (LVD-CON register), which selects the desired LVD Trip Point.

- 2. Ensure that LVD interrupts are disabled (the LVDIE bit is cleared, or the GIE bit is cleared).

- 3. Enable the LVD module (set the LVDEN bit in the LVDCON register).

- 4. Wait for the LVD module to stabilize (the IRVST bit to become set).

- 5. Clear the LVD interrupt flag, which may have falsely become set until the LVD module has stabilized (clear the LVDIF bit).

- 6. Enable the LVD interrupt (set the LVDIE and the GIE bits).

Figure 17-4 shows typical waveforms that the LVD module may be used to detect.

#### FIGURE 17-4: LOW VOLTAGE DETECT WAVEFORMS

| COMF              | Complement f                                                                                                                                                                                                                                                                                                                              | CPFSEQ                    | Compare f with WREG,<br>skip if f = WREG                                                                                                                                                                                                                                                                       |                 |                 |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--|

| Syntax:           | [ <i>label</i> ] COMF f[,d[,a]                                                                                                                                                                                                                                                                                                            | Syntax:                   | [label] C                                                                                                                                                                                                                                                                                                      | CPFSEQ f        | ,a]             |  |

| Operands:         |                                                                                                                                                                                                                                                                                                                                           |                           | $0 \le f \le 255$                                                                                                                                                                                                                                                                                              | 5               |                 |  |

|                   | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                    |                           | a ∈ [0,1]                                                                                                                                                                                                                                                                                                      |                 |                 |  |

| Operation:        | $(\overline{f}) \rightarrow dest$                                                                                                                                                                                                                                                                                                         | Operation:                | (f) – (WRE<br>skip if (f) =<br>(unsigned                                                                                                                                                                                                                                                                       |                 |                 |  |

| Status Affected:  | N,Z                                                                                                                                                                                                                                                                                                                                       | Status Affected:          | None                                                                                                                                                                                                                                                                                                           | companson       |                 |  |

| Encoding:         | 0001 11da ffff ffff                                                                                                                                                                                                                                                                                                                       |                           |                                                                                                                                                                                                                                                                                                                | 001a ff         |                 |  |

| Description:      | The contents of register 'f' are com-<br>plemented. If 'd' is 0, the result is<br>stored in WREG. If 'd' is 1, the<br>result is stored back in register 'f'<br>(default). If 'a' is 0, the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' = 1, then the<br>bank will be selected as per the<br>BCR value. (default) | Encoding:<br>Description: | 0110001affffffffCompares the contents of data<br>memory location 'f' to the contents<br>of WREG by performing an<br>unsigned subtraction.instructionIf 'f' = WREG, then the fetched<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>true and a instruction is (for the fetched) |                 |                 |  |

|                   | BSR value (default).                                                                                                                                                                                                                                                                                                                      |                           | two-cycle instruction. If 'a' is 0, the Access Bank will be selected, over-                                                                                                                                                                                                                                    |                 |                 |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                         |                           | riding the BSR value. If 'a' = 1, then                                                                                                                                                                                                                                                                         |                 |                 |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                         |                           |                                                                                                                                                                                                                                                                                                                | vill be selecte | ed as per the   |  |

| Q Cycle Activity: | 00 00 01                                                                                                                                                                                                                                                                                                                                  |                           | BSR value                                                                                                                                                                                                                                                                                                      | e (default).    |                 |  |