Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

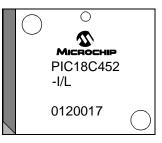

| Detuils                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lc252-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name          | Pin Number |           | Pin  | Buffer | Description                                               |

|-------------------|------------|-----------|------|--------|-----------------------------------------------------------|

| Pin Name          | DIP        | SOIC      | Туре | Туре   | Description                                               |

|                   |            |           |      |        | PORTB is a bi-directional I/O port. PORTB can be software |

|                   |            |           |      |        | programmed for internal weak pull-ups on all inputs.      |

| RB0/INT0          | 21         | 21        |      |        |                                                           |

| RB0               |            |           | I/O  | TTL    | Digital I/O.                                              |

| INT0              |            |           | Ι    | ST     | External Interrupt 0.                                     |

| RB1/INT1          | 22         | 22        |      |        |                                                           |

| RB1               |            |           | I/O  | TTL    |                                                           |

| INT1              |            |           | Ι    | ST     | External Interrupt 1.                                     |

| RB2/INT2          | 23         | 23        |      |        |                                                           |

| RB2               |            |           | I/O  | TTL    | Digital I/O.                                              |

| INT2              |            |           | I    | ST     | External Interrupt 2.                                     |

| RB3/CCP2          | 24         | 24        |      |        |                                                           |

| RB3               |            |           | I/O  | TTL    | Digital I/O.                                              |

| CCP2              |            |           | I/O  | ST     | Capture2 input, Compare2 output, PWM2 output.             |

| RB4               | 25         | 25        | I/O  | TTL    | Digital I/O.                                              |

|                   |            |           |      |        | Interrupt-on-change pin.                                  |

| RB5               | 26         | 26        | I/O  | TTL    | Digital I/O.                                              |

|                   |            |           |      |        | Interrupt-on-change pin.                                  |

| RB6               | 27         | 27        | I/O  | TTL    | Digital I/O.                                              |

|                   |            |           |      |        | Interrupt-on-change pin.                                  |

|                   |            |           | Ι    | ST     | ICSP programming clock.                                   |

| RB7               | 28         | 28        | I/O  | TTL    | Digital I/O.                                              |

|                   |            |           |      |        | Interrupt-on-change pin.                                  |

|                   |            |           | I/O  | ST     | ICSP programming data.                                    |

| Legend: TTL = TTL | compa      | tible inp | ut   |        | CMOS = CMOS compatible input or output                    |

#### PIC18C2X2 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-2:**

ST = Schmitt Trigger input with CMOS levels I = Input O = Output

OD = Open Drain (no P diode to VDD)

P = Power

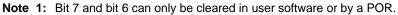

### REGISTER 4-1: STKPTR REGISTER

|                      | R/C-0                                       | R/C-0          | U-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------------------|---------------------------------------------|----------------|--------------|-------|-------|-------|-------|-------|--|--|

|                      | STKFUL                                      | STKUNF         | —            | SP4   | SP3   | SP2   | SP1   | SP0   |  |  |

|                      | bit 7 bit 0                                 |                |              |       |       |       |       |       |  |  |

|                      |                                             |                |              |       |       |       |       |       |  |  |

| bit 7 <sup>(1)</sup> | STKFUL: S                                   | Stack Full Fla | ag bit       |       |       |       |       |       |  |  |

|                      | 1 = Stack became full or overflowed         |                |              |       |       |       |       |       |  |  |

|                      | 0 = Stack has not become full or overflowed |                |              |       |       |       |       |       |  |  |

| bit 6 <sup>(1)</sup> | STKUNF: S                                   | Stack Underf   | low Flag bit |       |       |       |       |       |  |  |

|                      | 1 = Stack u                                 | inderflow oc   | curred       |       |       |       |       |       |  |  |

|                      | 0 = Stack u                                 | inderflow did  | l not occur  |       |       |       |       |       |  |  |

| bit 5                | Unimplemented: Read as '0'                  |                |              |       |       |       |       |       |  |  |

| bit 4-0              | SP4:SP0: S                                  | Stack Pointe   | r Location b | its   |       |       |       |       |  |  |

|                      |                                             |                |              |       |       |       |       |       |  |  |

|                      |                                             |                |              |       |       |       |       |       |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### FIGURE 4-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

### 4.2.3 PUSH AND POP INSTRUCTIONS

Since the Top-of-Stack (TOS) is readable and writable, the ability to push values onto the stack and pull values off the stack, without disturbing normal program execution, is a desirable option. To push the current PC value onto the stack, a PUSH instruction can be executed. This will increment the stack pointer and load the current PC value onto the stack. TOSU, TOSH and TOSL can then be modified to place a return address on the stack.

The ability to pull the TOS value off of the stack and replace it with the value that was previously pushed onto the stack, without disturbing normal execution, is achieved by using the POP instruction. The POP instruction discards the current TOS by decrementing the stack pointer. The previous value pushed onto the stack then becomes the TOS value.

### 4.2.4 STACK FULL/UNDERFLOW RESETS

These resets are enabled by programming the STVREN configuration bit. When the STVREN bit is disabled, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a device RESET. When the STVREN bit is enabled, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device RESET. The STKFUL or STKUNF bits are only cleared by the user software or a POR Reset.

### 4.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. Figure 4-6 and Figure 4-7 show the data memory organization for the PIC18CXX2 devices.

The data memory map is divided into as many as 16 banks that contain 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits for the BSR are not implemented.

The data memory contains Special Function Registers (SFR) and General Purpose Registers (GPR). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratch pad operations in the user's application. The SFRs start at the last location of Bank 15 (0xFFF) and extend downwards. Any remaining space beyond the SFRs in the Bank may be implemented as GPRs. GPRs start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

The entire data memory may be accessed directly, or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSRn) and corresponding Indirect File Operand (INDFn). Each FSR holds a 12-bit address value that can be used to access any location in the Data Memory map without banking.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. Section 4.10 provides a detailed description of the Access RAM.

### 4.9.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly. Indirect addressing operates using the File Select Registers (FSRn) and corresponding Indirect File Operand (INDFn). The operation of indirect addressing is shown in Section 4.12.

Enhanced MCU devices may have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other RESETS.

Data RAM is available for use as GPR registers by all instructions. The top half of bank 15 (0xF80 to 0xFFF) contains SFRs. All other banks of data memory contain GPR registers, starting with bank 0.

### 4.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 4-1 and Table 4-2.

The SFRs can be classified into two sets; those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFRs are typically distributed among the peripherals whose functions they control.

The unused SFR locations will be unimplemented and read as '0's. See Table 4-1 for addresses for the SFRs.

#### **TABLE 4-2: REGISTER FILE SUMMARY**

| File Name | Bit 7                                                                                                                                          | Bit 6                                                                                                                                                                                                                      | Bit 5                | Bit 4         | Bit 3          | Bit 2          | Bit 1           | Bit 0         | Value on<br>POR,<br>BOR | Details<br>on page: |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|----------------|----------------|-----------------|---------------|-------------------------|---------------------|

| TOSU      | _                                                                                                                                              | _                                                                                                                                                                                                                          | _                    | Top-of-Stack  | Upper Byte (T  | OS<20:16>)     |                 |               | 0 0000                  | 37                  |

| TOSH      | Top-of-Stacl                                                                                                                                   | Top-of-Stack High Byte (TOS<15:8>)                                                                                                                                                                                         |                      |               |                |                |                 |               | 0000 0000               | 37                  |

| TOSL      | Top-of-Stac                                                                                                                                    | op-of-Stack Low Byte (TOS<7:0>)                                                                                                                                                                                            |                      |               |                |                |                 |               | 0000 0000               | 37                  |

| STKPTR    | STKFUL                                                                                                                                         | STKUNF                                                                                                                                                                                                                     | _                    | Return Stack  | Pointer        |                |                 |               | 00-0 0000               | 38                  |

| PCLATU    | _                                                                                                                                              | _                                                                                                                                                                                                                          | _                    | Holding Regi  | ster for PC<20 | ):16>          |                 |               | 0 0000                  | 39                  |

| PCLATH    | Holding Reg                                                                                                                                    | olding Register for PC<15:8> 0000 0                                                                                                                                                                                        |                      |               |                |                |                 | 0000 0000     | 39                      |                     |

| PCL       | PC Low Byt                                                                                                                                     | C Low Byte (PC<7:0>) 0000 0000                                                                                                                                                                                             |                      |               |                |                |                 | 0000 0000     | 39                      |                     |

| TBLPTRU   | _                                                                                                                                              | _                                                                                                                                                                                                                          | bit21 <sup>(2)</sup> | Program Mer   | nory Table Po  | inter Upper By | te (TBLPTR<     | 20:16>)       | 0 0000                  | 57                  |

| TBLPTRH   | Program Me                                                                                                                                     | emory Table Po                                                                                                                                                                                                             | pinter High By       | te (TBLPTR<1  | 5:8>)          |                |                 |               | 0000 0000               | 57                  |

| TBLPTRL   | Program Me                                                                                                                                     | emory Table Po                                                                                                                                                                                                             | pinter Low Byt       | te (TBLPTR<7: | 0>)            |                |                 |               | 0000 0000               | 57                  |

| TABLAT    | Program Me                                                                                                                                     | emory Table La                                                                                                                                                                                                             | atch                 |               |                |                |                 |               | 0000 0000               | 57                  |

| PRODH     | Product Reg                                                                                                                                    | gister High Byt                                                                                                                                                                                                            | е                    |               |                |                |                 |               | XXXX XXXX               | 61                  |

| PRODL     | Product Reg                                                                                                                                    | gister Low Byte                                                                                                                                                                                                            | 9                    |               |                |                |                 |               | XXXX XXXX               | 61                  |

| INTCON    | GIE/GIEH                                                                                                                                       | PEIE/GIEL                                                                                                                                                                                                                  | TMR0IE               | <b>INTOIE</b> | RBIE           | TMR0IF         | <b>INT0IF</b>   | RBIF          | 0000 000x               | 65                  |

| INTCON2   | RBPU                                                                                                                                           | INTEDG0                                                                                                                                                                                                                    | INTEDG1              | INTEDG2       | _              | TMR0IP         | _               | RBIP          | 1111 -1-1               | 66                  |

| INTCON3   | INT2IP                                                                                                                                         | INT1IP                                                                                                                                                                                                                     | _                    | INT2IE        | INT1IE         | _              | INT2IF          | INT1IF        | 11-0 0-00               | 67                  |

| INDF0     | Uses conter                                                                                                                                    | nts of FSR0 to                                                                                                                                                                                                             | address data         | memory - valu | e of FSR0 not  | changed (not   | a physical rec  | gister)       | N/A                     | 50                  |

| POSTINC0  | Uses conter                                                                                                                                    | nts of FSR0 to                                                                                                                                                                                                             | address data         | memory - valu | e of FSR0 pos  | t-incremented  | (not a physic   | al register)  | N/A                     | 50                  |

| POSTDEC0  | Uses conter                                                                                                                                    | Uses contents of FSR0 to address data memory - value of FSR0 post-incremented (not a physical register) N/A<br>Uses contents of FSR0 to address data memory - value of FSR0 post-decremented (not a physical register) N/A |                      |               |                |                |                 | N/A           | 50                      |                     |

| PREINC0   | Uses contents of FSR0 to address data memory - value of FSR0 pre-incremented (not a physical register)                                         |                                                                                                                                                                                                                            |                      |               |                | I register)    | N/A             | 50            |                         |                     |

| PLUSW0    | Uses contents of FSR0 to address data memory - value of FSR0 pre-incremented (not a physical register) - value of FSR0 offset by value in WREG |                                                                                                                                                                                                                            |                      |               |                | N/A            | 50              |               |                         |                     |

| FSR0H     | Indirect Data Memory Address Pointer 0 High Byt                                                                                                |                                                                                                                                                                                                                            |                      |               |                | ) High Byte    | 0000            | 50            |                         |                     |

| FSR0L     | Indirect Dat                                                                                                                                   | Indirect Data Memory Address Pointer 0 Low Byte                                                                                                                                                                            |                      |               |                |                |                 |               | XXXX XXXX               | 50                  |

| WREG      | Working Register xxxx xxxx                                                                                                                     |                                                                                                                                                                                                                            |                      |               |                |                |                 |               |                         |                     |

| INDF1     | Uses conter                                                                                                                                    | nts of FSR1 to                                                                                                                                                                                                             | address data         | memory - valu | e of FSR1 not  | changed (not   | a physical reg  | gister)       | N/A                     | 50                  |

| POSTINC1  | Uses conter                                                                                                                                    | nts of FSR1 to                                                                                                                                                                                                             | address data         | memory - valu | e of FSR1 pos  | t-incremented  | (not a physic   | al register)  | N/A                     | 50                  |

| POSTDEC1  | Uses conter                                                                                                                                    | nts of FSR1 to                                                                                                                                                                                                             | address data         | memory - valu | e of FSR1 pos  | t-decremented  | d (not a physic | cal register) | N/A                     | 50                  |

| PREINC1   | Uses conter                                                                                                                                    | nts of FSR1 to                                                                                                                                                                                                             | address data         | memory - valu | e of FSR1 pre- | -incremented   | not a physica   | I register)   | N/A                     | 50                  |

| PLUSW1    |                                                                                                                                                | nts of FSR1 to<br>R1 offset by va                                                                                                                                                                                          |                      | memory - valu | e of FSR1 pre  | -incremented   | not a physica   | l register) - | N/A                     | 50                  |

| FSR1H     | _                                                                                                                                              | _                                                                                                                                                                                                                          | _                    | —             | Indirect Data  | a Memory Add   | ress Pointer 1  | High Byte     | 0000                    | 50                  |

| FSR1L     | Indirect Dat                                                                                                                                   | a Memory Add                                                                                                                                                                                                               | ress Pointer 1       | Low Byte      |                |                |                 |               | xxxx xxxx               | 50                  |

| BSR       | _                                                                                                                                              | _                                                                                                                                                                                                                          | _                    | —             | Bank Select    | Register       |                 |               | 0000                    | 49                  |

| INDF2     | Uses conter                                                                                                                                    | nts of FSR2 to                                                                                                                                                                                                             | address data         | memory - valu | e of FSR2 not  | changed (not   | a physical reg  | gister)       | N/A                     | 50                  |

| POSTINC2  | Uses conter                                                                                                                                    | nts of FSR2 to                                                                                                                                                                                                             | address data         | memory - valu | e of FSR2 pos  | t-incremented  | (not a physic   | al register)  | N/A                     | 50                  |

| POSTDEC2  | Uses conter                                                                                                                                    | nts of FSR2 to                                                                                                                                                                                                             | address data         | memory - valu | e of FSR2 pos  | t-decremented  | d (not a physic | cal register) | N/A                     | 50                  |

| PREINC2   | Uses conter                                                                                                                                    | nts of FSR2 to                                                                                                                                                                                                             | address data         | memory - valu | e of FSR2 pre- | -incremented   | not a physica   | l register)   | N/A                     | 50                  |

| PLUSW2    |                                                                                                                                                | nts of FSR2 to<br>R2 offset by va                                                                                                                                                                                          |                      | memory - valu | e of FSR2 pre  | -incremented   | not a physica   | l register) - | N/A                     | 50                  |

| FSR2H     | _                                                                                                                                              | _                                                                                                                                                                                                                          | _                    | _             | Indirect Data  | Memory Add     | ress Pointer 2  | 2 High Byte   | 0000                    | 50                  |

| FSR2L     | Indirect Dat                                                                                                                                   | a Memory Add                                                                                                                                                                                                               | ress Pointer 2       | 2 Low Byte    |                |                |                 |               | xxxx xxxx               | 50                  |

| STATUS    | _                                                                                                                                              | —                                                                                                                                                                                                                          | _                    | Ν             | OV             | Z              | DC              | С             | x xxxx                  | 52                  |

| TMR0H     | Timer0 Reg                                                                                                                                     | ister High Byte                                                                                                                                                                                                            |                      |               |                |                |                 |               | 0000 0000               | 95                  |

| TMR0L     | Timer0 Reg                                                                                                                                     | ister Low Byte                                                                                                                                                                                                             |                      |               |                |                |                 |               | xxxx xxxx               | 95                  |

| T0CON     | TMR0ON                                                                                                                                         | T08BIT                                                                                                                                                                                                                     | TOCS                 | TOSE          | PSA            | T0PS2          | T0PS1           | T0PS0         | 1111 1111               | 93                  |

| OSCCON    | —                                                                                                                                              | —                                                                                                                                                                                                                          | —                    | —             | —              | —              | —               | SCS           | 0                       | 20                  |

| LVDCON    | _                                                                                                                                              | _                                                                                                                                                                                                                          | IRVST                | LVDEN         | LVDL3          | LVDL2          | LVDL1           | LVDL0         | 00 0101                 | 175                 |

Legend: x = unknown, u = unchanged, - = unimplemented, g = value depends on condition

Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO oscillator mode only, and read '0' in all other oscillator modes.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

### 7.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable Registers (PIE1, PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

### REGISTER 7-6: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (PIE1)

|       | R/W-0                                                      | R/W-0                       | R/W-0         | R/W-0         | R/W-0          | R/W-0      | R/W-0         | R/W-0      |  |

|-------|------------------------------------------------------------|-----------------------------|---------------|---------------|----------------|------------|---------------|------------|--|

|       | PSPIE                                                      | ADIE                        | RCIE          | TXIE          | SSPIE          | CCP1IE     | TMR2IE        | TMR1IE     |  |

|       | bit 7                                                      |                             |               |               |                |            |               | bit 0      |  |

|       |                                                            |                             |               |               |                |            |               |            |  |

| bit 7 | PSPIE: Parallel Slave Port Read/Write Interrupt Enable bit |                             |               |               |                |            |               |            |  |

|       |                                                            | s the PSP re<br>s the PSP r |               |               |                |            |               |            |  |

| bit 6 |                                                            | Converter Ir                |               |               |                |            |               |            |  |

|       |                                                            | s the A/D in                | •             |               |                |            |               |            |  |

|       | 0 = Disable                                                | es the A/D ir               | nterrupt      |               |                |            |               |            |  |

| bit 5 | RCIE: USA                                                  | RT Receive                  | e Interrupt E | nable bit     |                |            |               |            |  |

|       |                                                            | s the USAR                  |               |               |                |            |               |            |  |

| h:+ 4 |                                                            | es the USAF                 |               | •             |                |            |               |            |  |

| bit 4 |                                                            | RT Transmi<br>s the USAR    |               |               |                |            |               |            |  |

|       |                                                            | s the USAR                  |               |               |                |            |               |            |  |

| bit 3 | SSPIE: Ma                                                  | ster Synchr                 | onous Seria   | I Port Interr | upt Enable bit |            |               |            |  |

|       |                                                            | s the MSSP                  |               |               |                |            |               |            |  |

|       |                                                            | es the MSSF                 |               |               |                |            |               |            |  |

| bit 2 |                                                            | CP1 Interru                 |               | it            |                |            |               |            |  |

|       |                                                            | s the CCP1<br>is the CCP1   | -             |               |                |            |               |            |  |

| bit 1 |                                                            | MR2 to PR2                  | •             | rrunt Enable  | - hit          |            |               |            |  |

| bit i |                                                            | s the TMR2                  |               | •             |                |            |               |            |  |

|       |                                                            | es the TMR2                 |               |               |                |            |               |            |  |

| bit 0 | TMR1IE: T                                                  | MR1 Overflo                 | ow Interrupt  | Enable bit    |                |            |               |            |  |

|       |                                                            | s the TMR1                  |               |               |                |            |               |            |  |

|       | 0 = Disables the TMR1 overflow interrupt                   |                             |               |               |                |            |               |            |  |

|       | Legend:                                                    |                             |               |               |                |            |               | ]          |  |

|       | R = Reada                                                  | hla hit                     | \\/ \\        | /ritable bit  | U = Unimple    | omontad hi | it read as "  | <b>ר</b> י |  |

|       | - n = Value                                                |                             |               | Bit is set    | 0 = 0 minipi   |            | x = Bit is ur |            |  |

|       | - n = value                                                | al FUR                      | I = D         | IL IS SEL     | U = DILISC     | lealeu     | x = Dit is uf | INTOWN     |  |

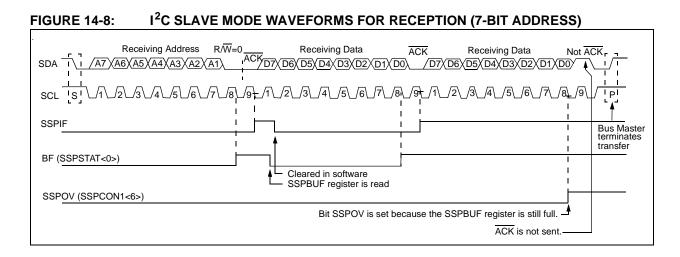

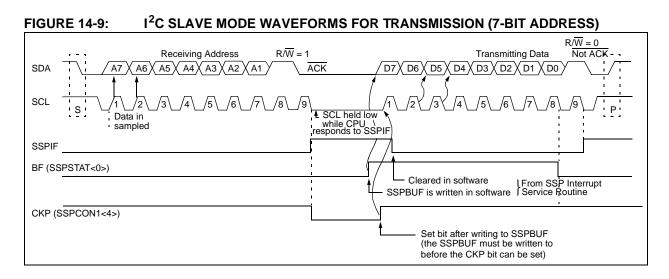

# REGISTER 14-1: SSPSTAT: MSSP STATUS REGISTER (CONTINUED)

|       | R/W-0                                                                                                                                             | R/W-0                            | R-0                         | R-0           | R-0                 | R-0           | R-0            | R-0          |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------|---------------|---------------------|---------------|----------------|--------------|--|

|       | SMP                                                                                                                                               | CKE                              | D/Ā                         | Р             | S                   | R/W           | UA             | BF           |  |

|       | bit 7                                                                                                                                             |                                  |                             |               |                     |               |                | bit 0        |  |

|       |                                                                                                                                                   |                                  |                             |               |                     |               |                |              |  |

| bit 3 | S: START I                                                                                                                                        |                                  |                             |               |                     |               | 000511         |              |  |

|       |                                                                                                                                                   |                                  |                             |               | SSP module          |               |                | cleared.)    |  |

|       | <ul> <li>1 = Indicates that a START bit has been detected last (this bit is '0' on RESET)</li> <li>0 = START bit was not detected last</li> </ul> |                                  |                             |               |                     |               |                |              |  |

| bit 2 | R/W: Read                                                                                                                                         | /Write bit inf                   | formation (I <sup>2</sup>   | C mode onl    | y)                  |               |                |              |  |

|       |                                                                                                                                                   |                                  |                             | •             | he last addre       |               | his bit is onl | y valid from |  |

|       |                                                                                                                                                   |                                  | ne next STA                 | RT bit, STO   | P bit, or not       | ACK bit.      |                |              |  |

|       | In I <sup>2</sup> C Slav                                                                                                                          | <u>e mode:</u>                   |                             |               |                     |               |                |              |  |

|       | 0 = Write                                                                                                                                         |                                  |                             |               |                     |               |                |              |  |

|       | In I <sup>2</sup> C Mast                                                                                                                          |                                  |                             |               |                     |               |                |              |  |

|       |                                                                                                                                                   | it is in progr                   |                             |               |                     |               |                |              |  |

|       |                                                                                                                                                   | nit is not in p<br>this bit with | •                           | I. PEN. RCI   | EN, or ACKE         | N will indica | ate if the MS  | SP is in     |  |

|       | IDLE m                                                                                                                                            |                                  | •=, •••=-                   | .,,           |                     |               |                |              |  |

| bit 1 | UA: Update                                                                                                                                        | e Address b                      | it (10-bit I <sup>2</sup> C | mode only)    |                     |               |                |              |  |

|       |                                                                                                                                                   |                                  |                             |               | address in t        | the SSPADE    | O register     |              |  |

|       |                                                                                                                                                   |                                  | need to be u                | pdated        |                     |               |                |              |  |

| bit 0 |                                                                                                                                                   | Full Status k                    |                             |               |                     |               |                |              |  |

|       |                                                                                                                                                   | <u>PI and I<sup>2</sup>C r</u>   | <u>nodes):</u><br>SSPBUF is | full          |                     |               |                |              |  |

|       |                                                                                                                                                   |                                  | ete, SSPBU                  |               |                     |               |                |              |  |

|       |                                                                                                                                                   | <sup>2</sup> C mode on           |                             |               |                     |               |                |              |  |

|       |                                                                                                                                                   |                                  |                             |               | th <u>e AC</u> K ar |               |                |              |  |

|       | 0 = Data tra                                                                                                                                      | ansmit comp                      | olete (does r               | not include t | he ACK and          | STOP bits),   | SSPBUF is      | empty        |  |

|       | Legend:                                                                                                                                           |                                  |                             |               |                     |               |                |              |  |

|       | R = Reada                                                                                                                                         | ble bit                          | W = Writab                  | le bit        | U = Unimpl          | emented bit   | , read as '0'  |              |  |

|       | - n = Value                                                                                                                                       | at POR                           | '1' = Bit is s              | set           | '0' = Bit is c      | leared        | x = Bit is ur  | nknown       |  |

### REGISTER 14-2: SSPCON1: MSSP CONTROL REGISTER1

|   | R/W-0 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

| ſ | WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

|   | bit 7 |       |       |       |       |       |       | bit 0 |

bit 7 WCOL: Write Collision Detect bit

Master mode:

- 1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started

- $0 = No \ collision$

Slave mode:

- 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

- 0 = No collision

bit 6 **SSPOV:** Receive Overflow Indicator bit

### In SPI mode:

- 1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data to avoid

- In Slave mode, the user must read the SSPBUF, even if only transmitting data to avoid setting overflow.

In Master mode, the overflow bit is not set, since each new reception (and transmission) is initiated by writing to the SSPBUF register (must be cleared in software).

### 0 = No overflow

In I<sup>2</sup>C mode:

- 1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit mode (must be cleared in software).

- 0 = No overflow

bit 5

### SSPEN: Synchronous Serial Port Enable bit

In both modes when enabled, these pins must be properly configured as input or output. In SPI mode:

- 1 = Enables serial port and configures SCK, SDO, SDI, and SS as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

### In I<sup>2</sup>C mode:

- 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented I  | oit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

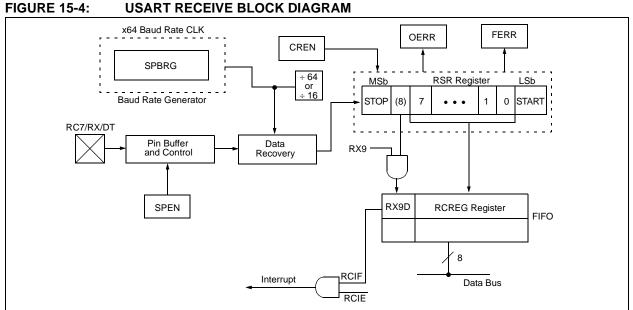

#### USART ASYNCHRONOUS 15.2.2 RECEIVER

The receiver block diagram is shown in Figure 15-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate, or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- Initialize the SPBRG register for the appropriate 1. baud rate. If a high speed baud rate is desired, set bit BRGH (Section 15.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- Enable the reception by setting bit CREN. 5.

- 6. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the 8. RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

#### SETTING UP 9-BIT MODE WITH 15.2.3 ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address **Detect Enable:**

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is required, set the BRGH bit.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- If interrupts are required, set the RCEN bit and 3. select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- Set the ADDEN bit to enable address detect. 5.

- Enable reception by setting the CREN bit.

- The RCIF bit will be set when reception is com-7. plete. The interrupt will be acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

### 15.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

### 15.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

| Name                          | Bit 7                              | Bit 6         | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|-------------------------------|------------------------------------|---------------|--------|--------|-------|--------|-----------|-----------|-------------------------|---------------------------------|

| INTCON                        | GIE/<br>GIEH                       | PEIE/<br>GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INTOIF    | RBIF      | 0000 000x               | 0000 000u                       |

| PIR1                          | PSPIF <sup>(1)</sup>               | ADIF          | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000               | 0000 0000                       |

| PIE1                          | PSPIE <sup>(1)</sup>               | ADIE          | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000               | 0000 0000                       |

| IPR1                          | PSPIP <sup>(1)</sup>               | ADIP          | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP    | TMR1IP    | 0000 0000               | 0000 0000                       |

| RCSTA                         | SPEN                               | RX9           | SREN   | CREN   | ADDEN | FERR   | OERR      | RX9D      | 0000 -00x               | 0000 -00x                       |

| TXREG USART Transmit Register |                                    |               |        |        |       |        | 0000 0000 | 0000 0000 |                         |                                 |

| TXSTA                         | CSRC                               | TX9           | TXEN   | SYNC   | _     | BRGH   | TRMT      | TX9D      | 0000 -010               | 0000 -010                       |

| SPBRG                         | SPBRG Baud Rate Generator Register |               |        |        |       |        |           |           | 0000 0000               | 0000 0000                       |

### TABLE 15-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'.

Shaded cells are not used for Synchronous Slave Transmission.

**Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

### 18.2 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO/RA6 pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the RCON register will be cleared upon a WDT time-out.

The Watchdog Timer is enabled/disabled by a device configuration bit. If the WDT is enabled, software execution may not disable this function. When the WDTEN configuration bit is cleared, the SWDTEN bit enables/ disables the operation of the WDT. The WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT postscaler may be assigned using the configuration bits.

**Note:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

Note: When a CLRWDT instruction is executed and the postscaler is assigned to the WDT, the postscaler count will be cleared, but the postscaler assignment is not changed.

### 18.2.1 CONTROL REGISTER

Register 18-7 shows the WDTCON register. This is a readable and writable register, which contains a control bit that allows software to override the WDT enable configuration bit, only when the configuration bit has disabled the WDT.

### **REGISTER 18-7: WDTCON REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

|       | —   | —   | —   | —   | —   | _   | SWDTEN |

| bit 7 |     |     |     |     |     |     | bit 0  |

### bit 7-1 Unimplemented: Read as '0'

- bit 0 SWDTEN: Software Controlled Watchdog Timer Enable bit

- 1 = Watchdog Timer is on

- Watchdog Timer is turned off if the WDTEN configuration bit in the configuration register = '0'

| Legend:                            |                          |

|------------------------------------|--------------------------|

| R = Readable bit                   | W = Writable bit         |

| U = Unimplemented bit, read as '0' | - n = Value at POR Reset |

| CPFSGT                       | Compare<br>skip if f >                                                                                                           | f with WRE0<br>WREG                                                                                                                                                                                                                                                                                                                                                                                                                          | З,              | CPFSLT                   |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|--|

| Syntax:                      | [label] C                                                                                                                        | PFSGT f[                                                                                                                                                                                                                                                                                                                                                                                                                                     | ,a]             | Syntax:                  |  |

| Operands:                    | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 | Operand                  |  |

| Operation:                   | (f) – (WRE<br>skip if (f) ><br>(unsigned                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | Operatio                 |  |

| Status Affected:             | None                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | Status A                 |  |

| Encoding:                    | 0110                                                                                                                             | 010a fff                                                                                                                                                                                                                                                                                                                                                                                                                                     | f ffff          | Encodin                  |  |

| Description:                 | memory lo<br>of the WR<br>unsigned s<br>If the content<br>fetched ins<br>a NOP is e<br>this a two-<br>0, the Acco<br>selected, o | Compares the contents of data<br>memory location 'f' to the contents<br>of the WREG by performing an<br>unsigned subtraction.<br>If the contents of 'f' are greater than<br>the contents of WREG, then the<br>fetched instruction is discarded and<br>a NOP is executed instead, making<br>this a two-cycle instruction. If 'a' is<br>0, the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be |                 |                          |  |

|                              | (default).                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | Cycles:                  |  |

| Words:                       | 1                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | -                        |  |

| Cycles:<br>Q Cycle Activity: | by                                                                                                                               | cycles if skip<br>a 2-word ins                                                                                                                                                                                                                                                                                                                                                                                                               |                 | Q Cycle                  |  |

| Q1                           | Q2                                                                                                                               | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q4              |                          |  |

| Decode                       | Read<br>register 'f'                                                                                                             | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                              | No<br>operation | lf skip:                 |  |

| If skip:                     |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |                          |  |

| Q1                           | Q2                                                                                                                               | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q4              |                          |  |

| No<br>operation              | No<br>operation                                                                                                                  | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                              | No<br>operation | lf skip a                |  |

| If skip and follow           |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                              | oporation       | ,<br>                    |  |

| Q1                           | Q2                                                                                                                               | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q4              | ор                       |  |