Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lc252t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 DEVICE OVERVIEW

This document contains device specific information for the following four devices:

- 1. PIC18C242

- 2. PIC18C252

- 3. PIC18C442

- 4. PIC18C452

These devices come in 28-pin and 40-pin packages. The 28-pin devices do not have a Parallel Slave Port (PSP) implemented and the number of Analog-to-Digital (A/D) converter input channels is reduced to 5. An overview of features is shown in Table 1-1.

# The following two figures are device block diagrams sorted by pin count: 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-2 and Table 1-3, respectively.

| Features                           | PIC18C242                                                                        | PIC18C252                                                                        | PIC18C442                                                                        | PIC18C452                                                                        |

|------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Operating Frequency                | DC - 40 MHz                                                                      |

| Program Memory (Bytes)             | 16K                                                                              | 32K                                                                              | 16K                                                                              | 32K                                                                              |

| Program Memory (Instructions)      | 8192                                                                             | 16384                                                                            | 8192                                                                             | 16384                                                                            |

| Data Memory (Bytes)                | 512                                                                              | 1536                                                                             | 512                                                                              | 1536                                                                             |

| Interrupt Sources                  | 16                                                                               | 16                                                                               | 17                                                                               | 17                                                                               |

| I/O Ports                          | Ports A, B, C                                                                    | Ports A, B, C                                                                    | Ports A, B, C, D, E                                                              | Ports A, B, C, D, E                                                              |

| Timers                             | 4                                                                                | 4                                                                                | 4                                                                                | 4                                                                                |

| Capture/Compare/PWM Modules        | 2                                                                                | 2                                                                                | 2                                                                                | 2                                                                                |

| Serial Communications              | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    |

| Parallel Communications            | —                                                                                | —                                                                                | PSP                                                                              | PSP                                                                              |

| 10-bit Analog-to-Digital Module    | 5 input channels                                                                 | 5 input channels                                                                 | 8 input channels                                                                 | 8 input channels                                                                 |

| RESETS (and Delays)                | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST) |

| Programmable Low Voltage<br>Detect | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |

| Programmable Brown-out Reset       | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |

| Instruction Set                    | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  |

| Packages                           | 28-pin DIP<br>28-pin SOIC<br>28-pin JW                                           | 28-pin DIP<br>28-pin SOIC<br>28-pin JW                                           | 40-pin DIP<br>44-pin PLCC<br>44-pin TQFP<br>40-pin JW                            | 40-pin DIP<br>44-pin PLCC<br>44-pin TQFP<br>40-pin JW                            |

#### TABLE 1-1: DEVICE FEATURES

#### 2.4 External Clock Input

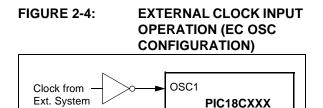

The EC and ECIO oscillator modes require an external clock source to be connected to the OSC1 pin. The feedback device between OSC1 and OSC2 is turned off in these modes to save current. There is no oscillator start-up time required after a Power-on Reset or after a recovery from SLEEP mode.

In the EC oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-4 shows the pin connections for the EC oscillator mode.

Fosc/4 -

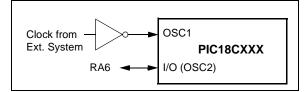

The ECIO oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 2-5 shows the pin connections for the ECIO oscillator mode.

OSC2

#### FIGURE 2-6: PLL BLOCK DIAGRAM

#### FIGURE 2-5:

#### EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

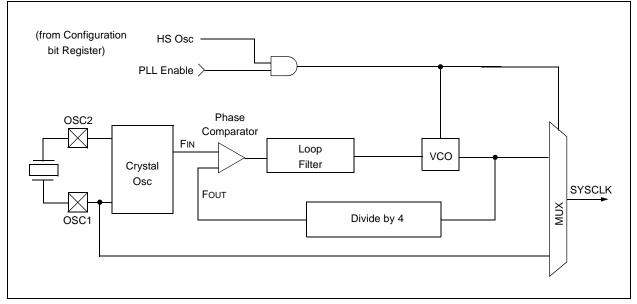

#### 2.5 HS/PLL

A Phase Locked Loop circuit is provided as a programmable option for users that want to multiply the frequency of the incoming crystal oscillator signal by 4. For an input clock frequency of 10 MHz, the internal clock frequency will be multiplied to 40 MHz. This is useful for customers who are concerned with EMI due to high frequency crystals.

The PLL can only be enabled when the oscillator configuration bits are programmed for HS mode. If they are programmed for any other mode, the PLL is not enabled and the system clock will come directly from OSC1.

The PLL is one of the modes of the FOSC<2:0> configuration bits. The oscillator mode is specified during device programming.

A PLL lock timer is used to ensure that the PLL has locked before device execution starts. The PLL lock timer has a time-out that is called TPLL.

## PIC18CXX2

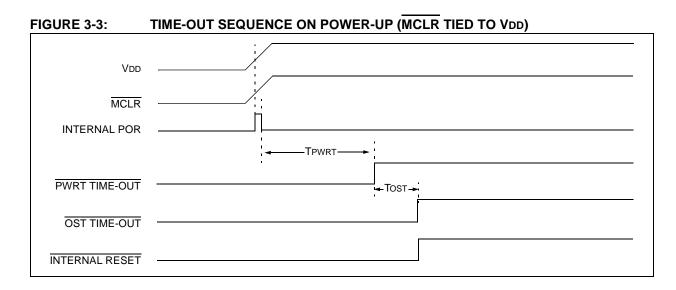

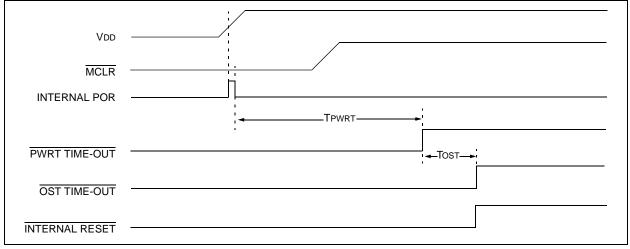

#### FIGURE 3-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

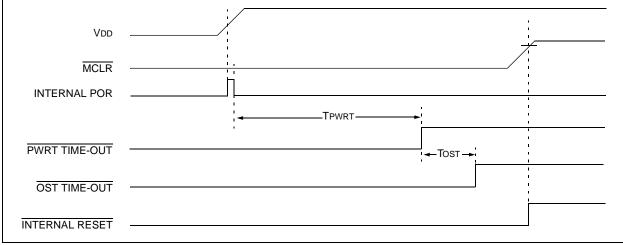

## FIGURE 3-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

#### 5.0 TABLE READS/TABLE WRITES

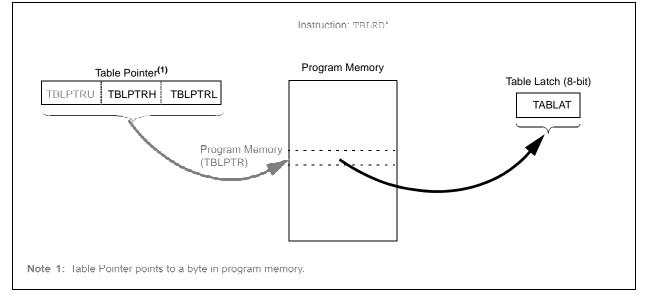

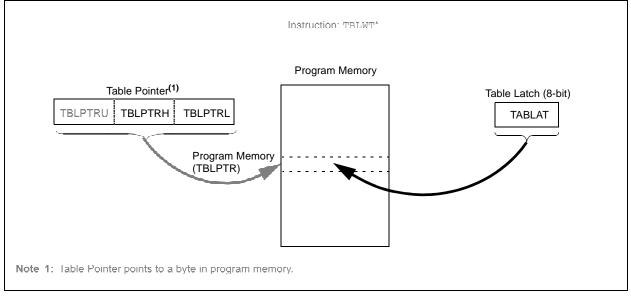

Enhanced devices have two memory spaces: the program memory space and the data memory space. The program memory space is 16-bits wide, while the data memory space is 8 bits wide. Table Reads and Table Writes have been provided to move data between these two memory spaces through an 8-bit register (TABLAT).

The operations that allow the processor to move data between the data and program memory spaces are:

- Table Read (TBLRD)

- Table Write (TBLWT)

Table Read operations retrieve data from program memory and place it into the data memory space. Figure 5-1 shows the operation of a Table Read with program and data memory.

Table Write operations store data from the data memory space into program memory. Figure 5-2 shows the operation of a Table Write with program and data memory.

Table operations work with byte entities. A table block containing data is not required to be word aligned, so a table block can start and end at any byte address. If a Table Write is being used to write an executable program to program memory, program instructions will need to be word aligned.

#### FIGURE 5-2: TABLE WRITE OPERATION

#### FIGURE 5-1: TABLE READ OPERATION

#### 5.1 Control Registers

Several control registers are used in conjunction with the  ${\tt TBLRD}$  and  ${\tt TBLWT}$  instructions. These include the:

- TBLPTR registers

- TABLAT register

- RCON register

#### 5.1.1 RCON REGISTER

The LWRT bit specifies the operation of Table Writes to internal memory when the VPP voltage is applied to the MCLR pin. When the LWRT bit is set, the controller continues to execute user code, but long Table Writes are allowed (for programming internal program memory) from user mode. The LWRT bit can be cleared only by performing either a POR or MCLR Reset.

#### REGISTER 5-1: RCON REGISTER (ADDRESS: FD0h)

| R/W-0 | R/W-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-0 | R/W-0 |

|-------|-------|-----|-------|-------|-------|-------|-------|

| IPEN  | LWRT  | —   | RI    | TO    | PD    | POR   | BOR   |

| bit 7 |       |     |       |       |       |       | bit 0 |

|  | bit 7 | <b>IPEN:</b> | Interrupt | Prioritv | Enable bit |

|--|-------|--------------|-----------|----------|------------|

|--|-------|--------------|-----------|----------|------------|

- 1 = Enable priority levels on interrupts

- 0 = Disable priority levels on interrupts (16CXXX compatibility mode)

- bit 6 LWRT: Long Write Enable bit

- 1 = Enable TBLWT to internal program memory

- 0 = Disable TBLWT to internal program memory.

- Note:Only cleared on a POR or MCLR Reset.This bit has no effect on TBLWTs to external program memory.

- bit 5 Unimplemented: Read as '0'

- bit 4 RI: RESET Instruction Flag bit

- 1 = No RESET instruction occurred

- 0 = A RESET instruction occurred

- bit 3 TO: Time-out bit

- 1 = After power-up, CLRWDT instruction, or SLEEP instruction

- 0 = A WDT time-out occurred

- bit 2 **PD:** Power-down bit

- 1 = After power-up or by the CLRWDT instruction

- 0 = By execution of the SLEEP instruction

- bit 1 POR: Power-on Reset Status bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 BOR: Brown-out Reset Status bit

- 1 = No Brown-out Reset or POR Reset occurred

- 0 = A Brown-out Reset or POR Reset occurred

- (must be set in software after a Brown-out Reset occurs)

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 7.6 INT0 Interrupt

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge triggered: either rising, if the corresponding INTEDGx bit is set in the INTCON2 register, or falling, if the INTEDGx bit is clear. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit INTxF is set. This interrupt can be disabled by clearing the corresponding enable bit INTxE. Flag bit INTxF must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt. All external interrupts (INT0, INT1 and INT2) can wake-up the processor from SLEEP, if bit INTxE was set prior to going into SLEEP. If the global interrupt enable bit GIE set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high priority interrupt source.

#### 7.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF. In 16-bit mode, an overflow (FFFFh  $\rightarrow$  0000h) in the TMR0H:TMR0L registers will set flag bit TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit TOIE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit TMR0IP (INTCON2<2>). See Section 8.0 for further details on the Timer0 module.

#### 7.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB Interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

#### 7.9 Context Saving During Interrupts

During an interrupt, the return PC value is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see Section 4.3), the user may need to save the WREG, STATUS and BSR registers in software. Depending on the user's application, other registers may also need to be saved. Example 7-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| MOVWF  | W_TEMP              | ; W_TEMP is in virtual bank    |

|--------|---------------------|--------------------------------|

| MOVFF  | STATUS, STATUS_TEMP | ; STATUS_TEMP located anywhere |

| MOVFF  | BSR, BSR_TEMP       | ; BSR located anywhere         |

| ;      |                     |                                |

| ; USER | ISR CODE            |                                |

| ;      |                     |                                |

| MOVFF  | BSR_TEMP, BSR       | ; Restore BSR                  |

| MOVF   | W_TEMP, W           | ; Restore WREG                 |

| MOVFF  | STATUS TEMP, STATUS | ; Restore STATUS               |

|        | —                   |                                |

|        |                     |                                |

#### 12.0 TIMER3 MODULE

The Timer3 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers: TMR3H and TMR3L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

- Reset from CCP module trigger

Figure 12-1 is a simplified block diagram of the Timer3 module.

Register 12-1 shows the Timer3 control register. This register controls the operating mode of the Timer3 module and sets the CCP clock source.

Register 10-1 shows the Timer1 control register. This register controls the operating mode of the Timer1 module, as well as contains the Timer1 oscillator enable bit (T1OSCEN), which can be a clock source for Timer3.

#### REGISTER 12-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|--------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |        |        | bit 0  |

| bit 7   | <b>RD16:</b> 16-bit Read/Write M<br>1 = Enables register Read/                                                                         |                                               | e 16-bit operation                   |      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------|------|

|         | 0 = Enables register Read/                                                                                                             | Write of Timer3 in two                        | 8-bit operations                     |      |

| bit 6-3 | T3CCP2:T3CCP1: Timer3                                                                                                                  | and Timer1 to CCPx B                          | Enable bits                          |      |

|         | 1x = Timer3 is the clock so<br>01 = Timer3 is the clock so<br>Timer1 is the clock so<br>00 = Timer1 is the clock so                    | urce for compare/cap<br>ource for compare/cap | ture of CCP2,<br>ture of CCP1        |      |

| bit 5-4 | T3CKPS1:T3CKPS0: Time                                                                                                                  | r3 Input Clock Presca                         | le Select bits                       |      |

|         | 11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                               |                                               |                                      |      |

| bit 2   | T3SYNC: Timer3 External (<br>(Not usable if the system clWhen TMR3CS = 1:1 = Do not synchronize external cl0 = Synchronize external cl | ock comes from Time<br>ernal clock input      |                                      |      |

|         | When TMR3CS = 0:                                                                                                                       |                                               |                                      |      |

|         | This bit is ignored. Timer3 u                                                                                                          | uses the internal clock                       | when TMR3CS = 0.                     |      |

| bit 1   | TMR3CS: Timer3 Clock So                                                                                                                | urce Select bit                               |                                      |      |

|         | <ol> <li>1 = External clock input from<br/>(on the rising edge after<br/>0 = Internal clock (Fosc/4)</li> </ol>                        |                                               |                                      |      |

| bit 0   | TMR3ON: Timer3 On bit                                                                                                                  |                                               |                                      |      |

|         | 1 = Enables Timer3<br>0 = Stops Timer3                                                                                                 |                                               |                                      |      |

|         | Legend:                                                                                                                                |                                               |                                      |      |

|         | R = Readable bit                                                                                                                       | W = Writable bit                              | U = Unimplemented bit, read as '0'   |      |

|         | - n = Value at POR reset                                                                                                               | '1' = Bit is set                              | '0' = Bit is cleared x = Bit is unkr | nown |

#### 12.2 Timer1 Oscillator

The Timer1 oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. The oscillator is a low power oscillator rated up to 200 KHz. See Section 10.0 for further details.

#### 12.3 Timer3 Interrupt

The TMR3 Register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR3IF (PIR2<1>). This interrupt can be enabled/disabled by setting/clearing TMR3 interrupt enable bit, TMR3IE (PIE2<1>).

#### 12.4 Resetting Timer3 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer3.

| Note: | The special event triggers from the CCP |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|

|       | module will not set interrupt flag bit  |  |  |  |  |  |

|       | TMR3IF (PIR1<0>).                       |  |  |  |  |  |

Timer3 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer3 is running in Asynchronous Counter mode, this RESET operation may not work. In the event that a write to Timer3 coincides with a special event trigger from CCP1, the write will take precedence. In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer3.

#### Value on Value on Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 POR. all other BOR RESETS GIE/ PEIE/ INTCON TMR0IE **INTOIE** RBIE TMR0IF **INT0IF** RBIF 0000 000x 0000 000u GIEH GIEL PIR2 BCLIF LVDIF CCP2IF TMR3IF 0000 0000 0000 0000 PIE2 \_ \_ BCLIE LVDIE TMR3IE CCP2IE 0000 0000 0000 0000 IPR2 BCLIP LVDIP TMR3IP CCP2IP 0000 0000 0000 0000 TMR3L Holding Register for the Least Significant Byte of the 16-bit TMR3 Register XXXX XXXX uuuu uuuu TMR3H Holding Register for the Most Significant Byte of the 16-bit TMR3 Register XXXX XXXX uuuu uuuu T1CON **RD16** T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON --00 0000 --uu uuuu T3CON T3SYNC **RD16** T3CCP2 T3CKPS1 T3CKPS0 T3CCP1 TMR3CS TMR3ON -000 0000 -uuu uuuu

#### TABLE 12-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

#### 13.0 CAPTURE/COMPARE/PWM (CCP) MODULES

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register, or as a PWM master/slave Duty Cycle register. Table 13-1 shows the timer resources of the CCP module modes. The operation of CCP1 is identical to that of CCP2, with the exception of the special event trigger. Therefore, operation of a CCP module in the following sections is described with respect to CCP1.

Table 13-2 shows the interaction of the CCP modules.

#### REGISTER 13-1: CCP1CON REGISTER/CCP2CON REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

|       | —   | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | DCxB1:DCxB0: PWM Duty Cycle bit1 and bit0                                                                                                         |

|         | Capture mode:                                                                                                                                     |

|         | Unused                                                                                                                                            |

|         | Compare mode:                                                                                                                                     |

|         | Unused                                                                                                                                            |

|         | PWM mode:                                                                                                                                         |

|         | These bits are the two LSbs (bit1 and bit0) of the 10-bit PWM duty cycle. The upper eight bits (DCx9:DCx2) of the duty cycle are found in CCPRxL. |

| bit 3-0 | CCPxM3:CCPxM0: CCPx Mode Select bits                                                                                                              |

|         | 0000 = Capture/Compare/PWM off (resets CCPx module)                                                                                               |

|         | 0001 = Reserved                                                                                                                                   |

|         | 0010 = Compare mode, toggle output on match (CCPxIF bit is set)                                                                                   |

|         | 0011 = Reserved                                                                                                                                   |

|         | 0100 = Capture mode, every falling edge                                                                                                           |

|         | 0101 = Capture mode, every rising edge                                                                                                            |

|         | 0110 = Capture mode, every 4th rising edge                                                                                                        |

|         | 0111 = Capture mode, every 16th rising edge                                                                                                       |

|         | 1000 = Compare mode,                                                                                                                              |

|         | Initialize CCP pin Low, on compare match force CCP pin High (CCPIF bit is set)                                                                    |

|         | 1001 = Compare mode,                                                                                                                              |

|         | Initialize CCP pin High, on compare match force CCP pin Low (CCPIF bit is set)                                                                    |

|         | 1010 = Compare mode,                                                                                                                              |

|         | Generate software interrupt on compare match (CCPIF bit is set, CCP pin is<br>unaffected)                                                         |

|         | 1011 = Compare mode,                                                                                                                              |

|         | Trigger special event (CCPIF bit is set)                                                                                                          |

|         | 11xx = PWM mode                                                                                                                                   |

|         |                                                                                                                                                   |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 14.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

#### 14.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI™)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The  $I^2C$  interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- · Slave mode

#### 14.4.4.1 I<sup>2</sup>C Master Mode Operation

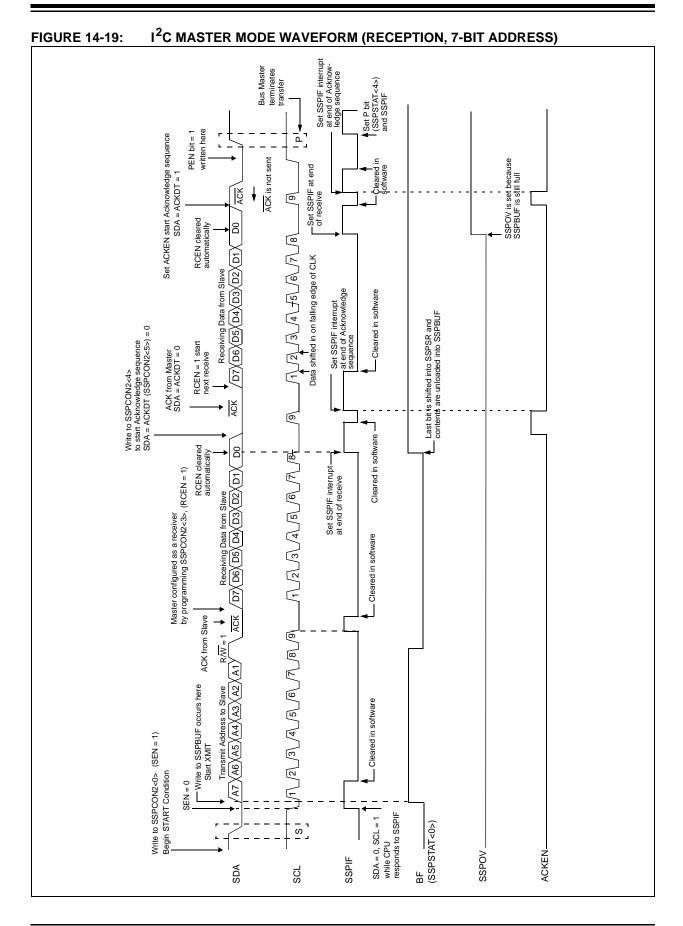

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated START condition. Since the Repeated START condition is also the beginning of the next serial transfer, the  $l^2C$  bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for the SPI mode operation is now used to set the SCL clock frequency for either 100 kHz, 400 kHz, or 1 MHz I<sup>2</sup>C operation. The baud rate generator reload value is contained in the lower 7 bits of the SSPADD register. The baud rate generator will automatically begin counting on a write to the SSPBUF. Once the given operation is complete, (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state. A typical transmit sequence would go as follows:

- a) The user generates a START condition by setting the START enable bit, SEN (SSPCON2<0>).

- b) SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- c) The user loads the SSPBUF with the address to transmit.

- d) Address is shifted out the SDA pin until all 8 bits are transmitted.

- e) The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- f) The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- g) The user loads the SSPBUF with eight bits of data.

- h) Data is shifted out the SDA pin until all 8 bits are transmitted.

- i) The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- j) The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- k) The user generates a STOP condition by setting the STOP enable bit, PEN (SSPCON2<2>).

- Interrupt is generated once the STOP condition is complete.

#### 15.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 15-1 shows the formula for computation of the baud rate for different USART modes, which only apply in Master mode (internal clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the formula in Table 15-1. From this, the error in baud rate can be determined. Example 15-1 shows the calculation of the baud rate error for the following conditions:

- Fosc = 16 MHz

- Desired Baud Rate = 9600

- BRGH = 0

- SYNC = 0

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 15.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### EXAMPLE 15-1: CALCULATING BAUD RATE ERROR

| Desired Baud Rate    | = Fosc / (64 (X + 1))                                                                                                                    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Solving for X:       |                                                                                                                                          |

| X<br>X<br>X          | = ((Fosc / Desired Baud rate) / 64) - 1<br>= ((16000000 / 9600) / 64) - 1<br>= [25.042] = 25                                             |

| Calculated Baud Rate | = 1600000 / (64 (25 + 1)) = 9615                                                                                                         |

| Error                | <ul> <li><u>(Calculated Baud Rate - Desired Baud Rate)</u><br/>Desired Baud Rate</li> <li>(9615 - 9600) / 9600</li> <li>0.16%</li> </ul> |

#### TABLE 15-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | NA                         |

Legend: X = value in SPBRG (0 to 255)

#### TABLE 15-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name  | Bit 7                                                           | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|-------|-----------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------------------------|---------------------------------|

| TXSTA | CSRC                                                            | TX9   | TXEN  | SYNC  | —     | BRGH  | TRMT  | TX9D  | 0000 -010               | 0000 -010                       |

| RCSTA | SPEN                                                            | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00x                       |

| SPBRG | SPBRG    Baud Rate Generator Register    0000 0000    0000 0000 |       |       |       |       |       |       |       |                         |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

To calculate the minimum acquisition time, Equation 16-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

#### EQUATION 16-1: ACQUISITION TIME

| TACO | 2 = | Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient |

|------|-----|-------------------------------------------------------------------------------------|

|      | =   | TAMP + TC + TCOFF                                                                   |

#### EQUATION 16-2: A/D MINIMUM CHARGING TIME

```

VHOLD = (VREF - (VREF/2048)) \cdot (1 - e^{(-Tc/CHOLD(RIC + RSS + RS))})

or

TC = -(120 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/2047)

```

Example 16-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following application system assumptions:

| ٠ | CHOLD            | =      | 120 pF  |

|---|------------------|--------|---------|

| • | Rs               | =      | 2.5 kΩ  |

| • | Conversion Error | $\leq$ | 1/2 LSb |

|   |                  |        |         |

- VDD =  $5V \rightarrow Rss = 7 k\Omega$

- Temperature = 50°C (system max.)

- VHOLD = 0V @ time = 0

#### EXAMPLE 16-1: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

$\begin{array}{rcl} {\rm TACQ} &=& {\rm TAMP} + {\rm TC} + {\rm TCOFF} \\ \\ {\rm Temperature \ coefficient \ is \ only \ required \ for \ temperatures > 25^{\circ}{\rm C}. \\ \\ {\rm TACQ} &=& 2\ \mu{\rm s} + {\rm Tc} + [({\rm Temp} - 25^{\circ}{\rm C})(0.05\ \mu{\rm s}/^{\circ}{\rm C})] \\ \\ {\rm TC} &=& -{\rm CHOLD}\ ({\rm RIC} + {\rm RSS} + {\rm RS})\ \ln(1/2047) \\ &\quad -120\ {\rm pF}\ (1\ k\Omega + 7\ k\Omega + 2.5\ k\Omega)\ \ln(0.0004885) \\ &\quad -120\ {\rm pF}\ (10.5\ k\Omega)\ \ln(0.0004885) \\ &\quad -1.26\ \mu{\rm s}\ (-7.6241) \\ &\quad 9.61\ \mu{\rm s} \\ \end{array}$

#### 16.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 12 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. The seven possible options for TAD are:

- 2Tosc

- 4Tosc

- 8Tosc

- 16Tosc

- 32Tosc

- 64Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 16-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

### 16.3 Configuring Analog Port Pins

The ADCON1, TRISA and TRISE registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins) may cause the input buffer to consume current that is out of the devices specification.

#### TABLE 16-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock Source (TAD) |             | Device Frequency        |                         |                         |                         |                              |  |  |  |

|-----------------------|-------------|-------------------------|-------------------------|-------------------------|-------------------------|------------------------------|--|--|--|

| Operation             | ADCS2:ADCS0 | 40 MHz                  | 20 MHz                  | 5 MHz                   | 1.25 MHz                | 333.33 kHz                   |  |  |  |

| 2Tosc                 | 000         | 50 ns                   | 100 ns <sup>(2)</sup>   | 400 ns <sup>(2)</sup>   | 1.6 μs                  | 6 μs                         |  |  |  |

| 4Tosc                 | 100         | 100 ns                  | 200 ns <sup>(2)</sup>   | 800 ns <sup>(2)</sup>   | 3.2 μs                  | 12 μs                        |  |  |  |

| 8Tosc                 | 001         | 200 ns                  | 400 ns <sup>(2)</sup>   | 1.6 μs                  | 6.4 μs                  | 24 μs <sup>(3)</sup>         |  |  |  |

| 16Tosc                | 101         | 400 ns                  | 800 ns <sup>(2)</sup>   | 3.2 μs                  | 12.8 μs                 | 48 μs <sup>(3)</sup>         |  |  |  |

| 32Tosc                | 010         | 800 ns                  | 1.6 μs                  | 6.4 μs                  | 25.6 μs <sup>(3)</sup>  | 96 μs <sup>(3)</sup>         |  |  |  |

| 64Tosc                | 110         | 1.6 μs                  | 3.2 μs                  | 12.8 μs                 | 51.2 μs <sup>(3)</sup>  | 192 μs <b><sup>(3)</sup></b> |  |  |  |

| RC                    | 011         | 2 - 6 μs <sup>(1)</sup>      |  |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu s.$

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

#### TABLE 16-2: TAD VS. DEVICE OPERATING FREQUENCIES (FOR EXTENDED, LC, DEVICES)

| AD Clock              | Source (TAD) | Device Frequency             |                           |                              |                             |  |  |  |  |

|-----------------------|--------------|------------------------------|---------------------------|------------------------------|-----------------------------|--|--|--|--|

| Operation ADCS2:ADCS0 |              | 4 MHz                        | 2 MHz                     | 1.25 MHz                     | 333.33 kHz                  |  |  |  |  |

| 2Tosc                 | 000          | 500 ns <b>(2)</b>            | 1.0 μs <sup>(2)</sup>     | 1.6 μs <b><sup>(2)</sup></b> | 6 μs                        |  |  |  |  |

| 4Tosc                 | 100          | 1.0 μs <b><sup>(2)</sup></b> | 2.0 μs <sup>(2)</sup>     | 3.2 μs <sup>(2)</sup>        | 12 μs                       |  |  |  |  |

| 8Tosc                 | 001          | 2.0 μs <sup>(2)</sup>        | 4.0 μs                    | 6.4 μs                       | 24 μs <sup>(3)</sup>        |  |  |  |  |

| 16Tosc                | 101          | 4.0 μs <sup>(2)</sup>        | 8.0 μs                    | 12.8 μs                      | 48 μs <b>(3)</b>            |  |  |  |  |

| 32Tosc                | 010          | 8.0 μs                       | 16.0 μs                   | 25.6 μs <sup>(3)</sup>       | 96 μs <b><sup>(3)</sup></b> |  |  |  |  |

| 64Tosc                | 110          | 16.0 μs                      | 32.0 μs                   | 51.2 μs <sup>(3)</sup>       | 192 μs <sup>(3)</sup>       |  |  |  |  |

| RC                    | 011          | 3 - 9 μs <sup>(1,4)</sup>    | 3 - 9 μs <sup>(1,4)</sup> | 3 - 9 μs <sup>(1,4)</sup>    | 3 - 9 μs <sup>(1,4)</sup>   |  |  |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The RC source has a typical TAD time of 6  $\mu$ s.

**2:** These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

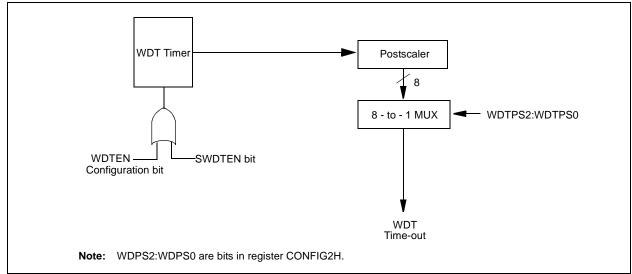

#### 18.2.2 WDT POSTSCALER

The WDT has a postscaler that can extend the WDT Reset period. The postscaler is selected at the time of device programming, by the value written to the CONFIG2H configuration register.

#### TABLE 18-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|

| CONFIG2H | —     | —     | _     | _     | WDTPS2 | WDTPS2 | WDTPS0 | WDTEN  |

| RCON     | IPEN  | LWRT  | —     | RI    | TO     | PD     | POR    | BOR    |

| WDTCON   | —     | _     |       |       |        |        | _      | SWDTEN |

Legend: Shaded cells are not used by the Watchdog Timer.

| Mnemo    | onic, | Description                    | Cuoloc | 16-k | oit Instr | uction V | Vord | Status    | Notos |

|----------|-------|--------------------------------|--------|------|-----------|----------|------|-----------|-------|

| Operands |       | Description                    | Cycles | MSb  |           |          | LSb  | Affected  | Notes |

| CONTROL  | OPERA | TIONS                          |        |      |           |          |      |           |       |

| BC       | n     | Branch if Carry                | 1 (2)  | 1110 | 0010      | nnnn     | nnnn | None      |       |

| BN       | n     | Branch if Negative             | 1 (2)  | 1110 | 0110      | nnnn     | nnnn | None      |       |

| BNC      | n     | Branch if Not Carry            | 1 (2)  | 1110 | 0011      | nnnn     | nnnn | None      |       |

| BNN      | n     | Branch if Not Negative         | 1 (2)  | 1110 | 0111      | nnnn     | nnnn | None      |       |

| BNOV     | n     | Branch if Not Overflow         | 1 (2)  | 1110 | 0101      | nnnn     | nnnn | None      |       |

| BNZ      | n     | Branch if Not Zero             | 2      | 1110 | 0001      | nnnn     | nnnn | None      |       |

| BOV      | n     | Branch if Overflow             | 1 (2)  | 1110 | 0100      | nnnn     | nnnn | None      |       |

| BRA      | n     | Branch Unconditionally         | 1 (2)  | 1101 | 0nnn      | nnnn     | nnnn | None      |       |

| BZ       | n     | Branch if Zero                 | 1 (2)  | 1110 | 0000      | nnnn     | nnnn | None      |       |

| CALL     | n, s  | Call subroutine1st word        | 2      | 1110 | 110s      | kkkk     | kkkk | None      |       |

|          |       | 2nd word                       |        | 1111 | kkkk      | kkkk     | kkkk |           |       |

| CLRWDT   | _     | Clear Watchdog Timer           | 1      | 0000 | 0000      | 0000     | 0100 | TO, PD    |       |

| DAW      | _     | Decimal Adjust WREG            | 1      | 0000 | 0000      | 0000     | 0111 | С         |       |

| GOTO     | n     | Go to address1st word          | 2      | 1110 | 1111      | kkkk     | kkkk | None      |       |

|          |       | 2nd word                       |        | 1111 | kkkk      | kkkk     | kkkk |           |       |

| NOP      | _     | No Operation                   | 1      | 0000 | 0000      | 0000     | 0000 | None      |       |

| NOP      | _     | No Operation (Note 4)          | 1      | 1111 | xxxx      | xxxx     | xxxx | None      |       |

| POP      | _     | Pop top of return stack (TOS)  | 1      | 0000 | 0000      | 0000     | 0110 | None      |       |

| PUSH     | _     | Push top of return stack (TOS) | 1      | 0000 | 0000      | 0000     | 0101 | None      |       |

| RCALL    | n     | Relative Call                  | 2      | 1101 | 1nnn      | nnnn     | nnnn | None      |       |

| RESET    |       | Software device RESET          | 1      | 0000 | 0000      | 1111     | 1111 | All       |       |

| RETFIE   | S     | Return from interrupt enable   | 2      | 0000 | 0000      | 0001     | 000s | GIE/GIEH, |       |

|          |       |                                |        |      |           |          |      | PEIE/GIEL |       |

| RETLW    | k     | Return with literal in WREG    | 2      | 0000 | 1100      | kkkk     | kkkk | None      |       |

| RETURN   | S     | Return from Subroutine         | 2      | 0000 | 0000      | 0001     | 001s | None      |       |

| SLEEP    | _     | Go into standby mode           | 1      | 0000 | 0000      | 0000     | 0011 | TO, PD    |       |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2 word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

#### 20.13 PICDEM 3 Low Cost PIC16CXXX Demonstration Board

The PICDEM 3 demonstration board is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with an LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 3 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer with an adapter socket, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 3 demonstration board to test firmware. A prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM 3 demonstration board is a LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM 3 demonstration board provides an additional RS-232 interface and Windows software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

#### 20.14 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included and the user may erase it and program it with the other sample programs using the PRO MATE II device programmer, or the PICSTART Plus development programmer, and easily debug and test the sample code. In addition, the PICDEM 17 demonstration board supports downloading of programs to and executing out of external FLASH memory on board. The PICDEM 17 demonstration board is also usable with the MPLAB ICE in-circuit emulator, or the PICMASTER emulator and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

#### 20.15 KEELOQ Evaluation and Programming Tools

KEELOQ evaluation and programming tools support Microchip's HCS Secure Data Products. The HCS evaluation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a programming interface to program test transmitters.

#### 21.2 DC Characteristics: PIC18CXX2 (Industrial, Extended) PIC18LCXX2 (Industrial) (Continued)

| DC CHARACTERISTICS |        |                                            | Standard O<br>Operating te | s (unless otherwise stated)<br>$\leq$ TA $\leq$ +85°C for industrial<br>$\leq$ TA $\leq$ +125°C for extended |       |                                               |

|--------------------|--------|--------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                             | Min                        | Max                                                                                                          | Units | Conditions                                    |

|                    | Vol    | Output Low Voltage                         |                            |                                                                                                              |       |                                               |

| D080               |        | I/O ports                                  | —                          | 0.6                                                                                                          | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C   |

| D080A              |        |                                            | —                          | 0.6                                                                                                          | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C  |

| D083               |        | OSC2/CLKOUT<br>(RC mode)                   | —                          | 0.6                                                                                                          | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C   |

| D083A              |        |                                            | —                          | 0.6                                                                                                          | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C  |

|                    | Vон    | Output High Voltage <sup>(3)</sup>         |                            |                                                                                                              |       |                                               |

| D090               |        | I/O ports                                  | Vdd - 0.7                  | —                                                                                                            | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С  |

| D090A              |        |                                            | Vdd - 0.7                  | —                                                                                                            | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С |

| D092               |        | OSC2/CLKOUT<br>(RC mode)                   | Vdd - 0.7                  | —                                                                                                            | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С  |

| D092A              |        |                                            | Vdd - 0.7                  | —                                                                                                            | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С |

| D150               | Vod    | Open Drain High Voltage                    | _                          | 8.5                                                                                                          | V     | RA4 pin                                       |

|                    |        | Capacitive Loading Specs<br>on Output Pins |                            |                                                                                                              |       |                                               |

| D101               | Сю     | All I/O pins and OSC2<br>(in RC mode)      | —                          | 50                                                                                                           | pF    | To meet the AC Timing<br>Specifications       |

| D102               | Св     | SCL, SDA                                   | —                          | 400                                                                                                          | pF    | In I <sup>2</sup> C mode                      |

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC MCU be driven with an external clock while in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

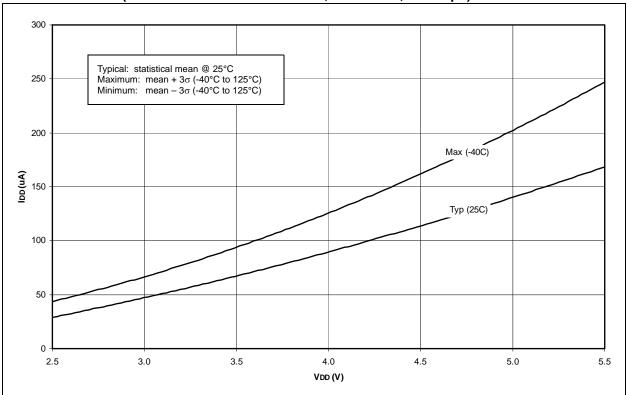

FIGURE 22-9: TYPICAL AND MAXIMUM IDD vs. VDD (TIMER1 AS MAIN OSCILLATOR, 32.768 kHz, C = 47 pF)

© 1999-2013 Microchip Technology Inc.