Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lc452-i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

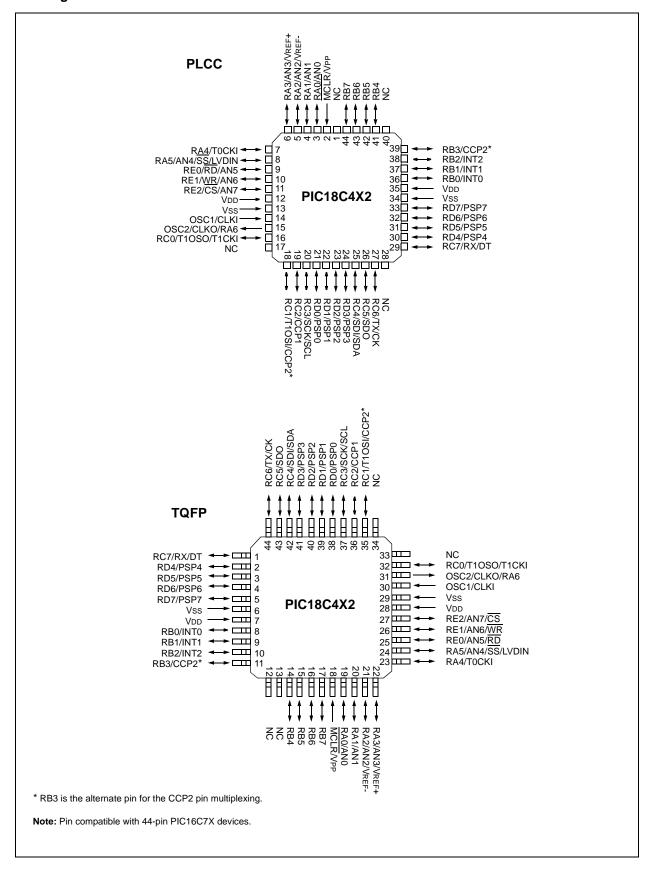

#### **Pin Diagrams**

**TABLE 1-2:** PIC18C2X2 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Din Name        | Pin N | umber | Pin  | Buffer | Description                                                      |  |  |  |  |  |

|-----------------|-------|-------|------|--------|------------------------------------------------------------------|--|--|--|--|--|

| Pin Name        | DIP   | SOIC  | Туре | Type   | Description                                                      |  |  |  |  |  |

|                 |       |       |      |        | PORTC is a bi-directional I/O port.                              |  |  |  |  |  |

| RC0/T1OSO/T1CKI | 11    | 11    |      |        |                                                                  |  |  |  |  |  |

| RC0             |       |       | I/O  | ST     | Digital I/O.                                                     |  |  |  |  |  |

| T1OSO           |       |       | 0    | _      | Timer1 oscillator output.                                        |  |  |  |  |  |

| T1CKI           |       |       | I    | ST     | Timer1/Timer3 external clock input.                              |  |  |  |  |  |

| RC1/T1OSI/CCP2  | 12    | 12    |      |        |                                                                  |  |  |  |  |  |

| RC1             |       |       | I/O  | ST     | Digital I/O.                                                     |  |  |  |  |  |

| T1OSI           |       |       | I    | CMOS   | Timer1 oscillator input.                                         |  |  |  |  |  |

| CCP2            |       |       | I/O  | ST     | Capture2 input, Compare2 output, PWM2 output.                    |  |  |  |  |  |

| RC2/CCP1        | 13    | 13    |      |        |                                                                  |  |  |  |  |  |

| RC2             |       |       | I/O  | ST     | Digital I/O.                                                     |  |  |  |  |  |

| CCP1            |       |       | I/O  | ST     | Capture1 input/Compare1 output/PWM1 output.                      |  |  |  |  |  |

| RC3/SCK/SCL     | 14    | 14    |      |        |                                                                  |  |  |  |  |  |

| RC3             |       |       | I/O  | ST     | Digital I/O.                                                     |  |  |  |  |  |

| SCK             |       |       | I/O  | ST     | Synchronous serial clock input/output for SPI mode.              |  |  |  |  |  |

| SCL             |       |       | I/O  | ST     | Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |  |  |  |  |

| RC4/SDI/SDA     | 15    | 15    |      |        |                                                                  |  |  |  |  |  |

| RC4             |       |       | I/O  | ST     | Digital I/O.                                                     |  |  |  |  |  |

| SDI             |       |       | I    | ST     | SPI Data In.                                                     |  |  |  |  |  |

| SDA             |       |       | I/O  | ST     | I <sup>2</sup> C Data I/O.                                       |  |  |  |  |  |

| RC5/SDO         | 16    | 16    |      |        |                                                                  |  |  |  |  |  |

| RC5             |       |       | I/O  | ST     | Digital I/O.                                                     |  |  |  |  |  |

| SDO             |       |       | 0    | _      | SPI Data Out.                                                    |  |  |  |  |  |

| RC6/TX/CK       | 17    | 17    |      |        |                                                                  |  |  |  |  |  |

| RC6             |       |       | I/O  | ST     | Digital I/O.                                                     |  |  |  |  |  |

| TX              |       |       | 0    | _      | USART Asynchronous Transmit.                                     |  |  |  |  |  |

| CK              |       |       | I/O  | ST     | USART Synchronous Clock (see related RX/DT).                     |  |  |  |  |  |

| RC7/RX/DT       | 18    | 18    |      |        |                                                                  |  |  |  |  |  |

| RC7             |       |       | I/O  | ST     | Digital I/O.                                                     |  |  |  |  |  |

| RX              |       |       | I    | ST     | USART Asynchronous Receive.                                      |  |  |  |  |  |

| DT              |       |       | I/O  | ST     | USART Synchronous Data (see related TX/CK).                      |  |  |  |  |  |

| Vss             | 8, 19 | 8, 19 | Р    |        | Ground reference for logic and I/O pins.                         |  |  |  |  |  |

| VDD             | 20    | 20    | Р    | _      | Positive supply for logic and I/O pins.                          |  |  |  |  |  |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels I = Input

O = Output

OD = Open Drain (no P diode to VDD)

CMOS = CMOS compatible input or output

P = Power

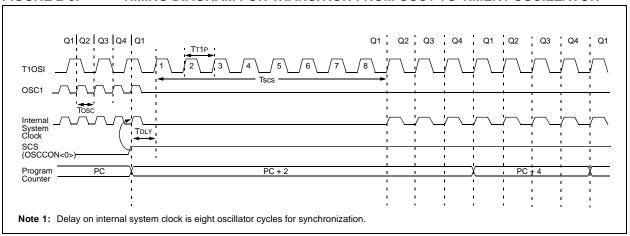

#### 2.6.2 OSCILLATOR TRANSITIONS

The PIC18CXX2 devices contain circuitry to prevent "glitches" when switching between oscillator sources. Essentially, the circuitry waits for eight rising edges of the clock source that the processor is switching to. This ensures that the new clock source is stable and that it's pulse width will not be less than the shortest pulse width of the two clock sources.

A timing diagram indicating the transition from the main oscillator to the Timer1 oscillator is shown in Figure 2-8. The Timer1 oscillator is assumed to be running all the time. After the SCS bit is set, the processor is frozen at the next occurring Q1 cycle. After eight synchronization cycles are counted from the Timer1 oscillator, operation resumes. No additional delays are required after the synchronization cycles.

FIGURE 2-8: TIMING DIAGRAM FOR TRANSITION FROM OSC1 TO TIMER1 OSCILLATOR

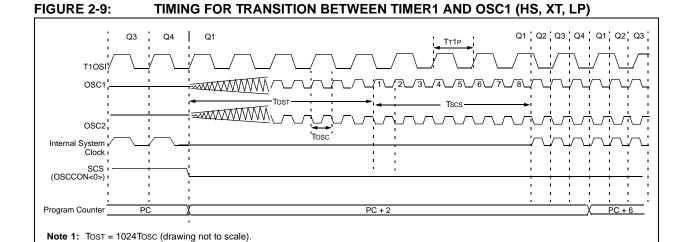

The sequence of events that takes place when switching from the Timer1 oscillator to the main oscillator will depend on the mode of the main oscillator. In addition to eight clock cycles of the main oscillator, additional delays may take place.

If the main oscillator is configured for an external crystal (HS, XT, LP), then the transition will take place after an oscillator start-up time (TOST) has occurred. A timing diagram indicating the transition from the Timer1 oscillator to the main oscillator for HS, XT and LP modes is shown in Figure 2-9.

#### 4.0 MEMORY ORGANIZATION

There are two memory blocks in Enhanced MCU devices. These memory blocks are:

- · Program Memory

- · Data Memory

Program and data memory use separate buses so that concurrent access can occur.

### 4.1 Program Memory Organization

A 21-bit program counter is capable of addressing the 2-Mbyte program memory space. Accessing a location between the physically implemented memory and the 2-Mbyte address will cause a read of all '0's (a NOP instruction).

PIC18C252 and PIC18C452 have 32 Kbytes of EPROM, while PIC18C242 and PIC18C442 have 16 Kbytes of EPROM. This means that PIC18CX52 devices can store up to 16K of single word instructions, and PIC18CX42 devices can store up to 8K of single word instructions.

The RESET vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

Figure 4-1 shows the Program Memory Map for PIC18C242/442 devices and Figure 4-2 shows the Program Memory Map for PIC18C252/452 devices.

#### 7.0 INTERRUPTS

The PIC18CXX2 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high priority level, or a low priority level. The high priority interrupt vector is at 000008h and the low priority interrupt vector is at 000018h. High priority interrupt events will override any low priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB® IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

Each interrupt source has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- · Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set. Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared. When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority level. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC® mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH, or GIEL bit. High priority interrupt sources can interrupt a low priority interrupt.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (000008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

### REGISTER 7-5: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (PIR2)

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-------|-------|--------|--------|

| _     | _   | _   | _   | BCLIF | LVDIF | TMR3IF | CCP2IF |

| bit 7 |     |     |     |       |       |        | hit 0  |

bit 7-4 **Unimplemented:** Read as '0'

bit 3 BCLIF: Bus Collision Interrupt Flag bit

1 = A bus collision occurred (must be cleared in software)

0 = No bus collision occurred

bit 2 LVDIF: Low Voltage Detect Interrupt Flag bit

1 = A low voltage condition occurred (must be cleared in software)

0 = The device voltage is above the Low Voltage Detect trip point

bit 1 TMR3IF: TMR3 Overflow Interrupt Flag bit

1 = TMR3 register overflowed (must be cleared in software)

0 = TMR3 register did not overflow

bit 0 CCP2IF: CCPx Interrupt Flag bit

Capture mode:

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM mode:

Unused in this mode

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

**TABLE 10-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER**

| Name   | Bit 7                                                                      | Bit 6         | Bit 5     | Bit 4     | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>RESETS |

|--------|----------------------------------------------------------------------------|---------------|-----------|-----------|---------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/GIEH                                                                   | PEIE/<br>GIEL | TMR0IE    | INT0IE    | RBIE    | TMR0IF | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>                                                       | ADIF          | RCIF      | TXIF      | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>                                                       | ADIE          | RCIE      | TXIE      | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>                                                       | ADIP          | RCIP      | TXIP      | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 0000 0000            | 0000 0000                       |

| TMR1L  | Holding Re                                                                 |               | xxxx xxxx | uuuu uuuu |         |        |        |        |                      |                                 |

| TMR1H  | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |               |           |           |         |        |        |        |                      | uuuu uuuu                       |

| T1CON  | RD16                                                                       |               | T1CKPS1   | T1CKPS0   | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 00 0000              | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module. **Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

#### 12.1 Timer3 Operation

Timer3 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- · As an asynchronous counter

The operating mode is determined by the clock select bit, TMR3CS (T3CON<1>).

When TMR3CS = 0, Timer3 increments every instruction cycle. When TMR3CS = 1, Timer3 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer3 also has an internal "RESET input". This RESET can be generated by the CCP module (Section 12.0).

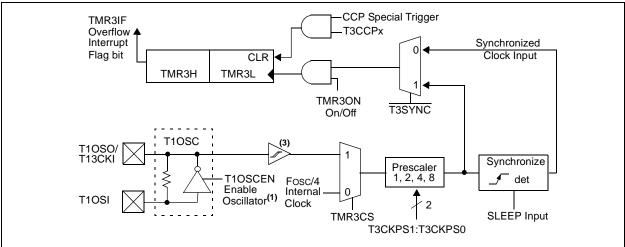

#### FIGURE 12-1: TIMER3 BLOCK DIAGRAM

Note 1: When enable bit T1OSCEN is cleared, the inverter and feedback resistor are turned off. This eliminates power drain.

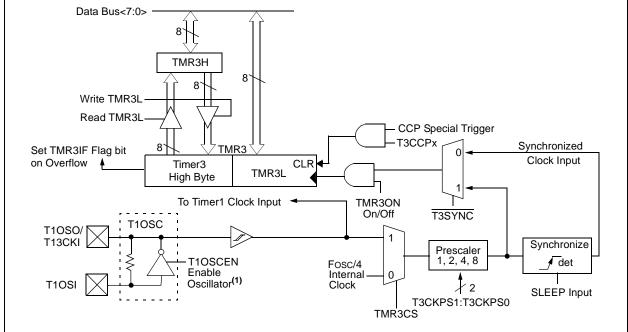

#### FIGURE 12-2: TIMER3 BLOCK DIAGRAM CONFIGURED IN 16-BIT READ/WRITE MODE

Note 1: When enable bit T1OSCEN is cleared, the inverter and feedback resistor are turned off. This eliminates power drain.

#### 13.5.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 13-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F       | 0x1F       | 0x17       |

| Maximum Resolution (bits)  | 14       | 12       | 10        | 8          | 7          | 6.58       |

#### TABLE 13-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Name    | Bit 7                               | Bit 6         | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Valu<br>PC<br>BC | R,   | all o | e on<br>other<br>SETS |

|---------|-------------------------------------|---------------|-------------|---------|---------|--------|---------|---------|------------------|------|-------|-----------------------|

| INTCON  | GIE/<br>GIEH                        | PEIE/<br>GIEL | TMR0IE      | INTOIE  | RBIE    | TMR0IF | INT0IF  | RBIF    | 0000             | 000x | 0000  | 000u                  |

| PIR1    | PSPIF <sup>(1)</sup>                | ADIF          | RCIF        | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000             | 0000 | 0000  | 0000                  |

| PIE1    | PSPIE <sup>(1)</sup>                | ADIE          | RCIE        | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000             | 0000 | 0000  | 0000                  |

| IPR1    | PSPIP <sup>(1)</sup>                | ADIP          | RCIP        | TXIP    | SSPIP   | CCP1IP | TMR2IP  | TMR1IP  | 0000             | 0000 | 0000  | 0000                  |

| TRISC   | PORTC Da                            | ata Direction | Register    |         |         |        |         |         | 1111             | 1111 | 1111  | 1111                  |

| TMR2    | Timer2 Mo                           | dule Registe  | er          |         |         |        |         |         | 0000             | 0000 | 0000  | 0000                  |

| PR2     | Timer2 Mo                           | dule Period   | Register    |         |         |        |         |         | 1111             | 1111 | 1111  | 1111                  |

| T2CON   | 1                                   | TOUTPS3       | TOUTPS2     | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000             | 0000 | -000  | 0000                  |

| CCPR1L  | Capture/Co                          | ompare/PWI    | M Register1 | (LSB)   |         |        |         |         | xxxx             | xxxx | uuuu  | uuuu                  |

| CCPR1H  | Capture/Co                          | ompare/PWI    | M Register1 | (MSB)   |         |        |         |         | xxxx             | xxxx | uuuu  | uuuu                  |

| CCP1CON | —                                   |               |             |         |         |        |         |         | 00               | 0000 | 00    | 0000                  |

| CCPR2L  | Capture/Compare/PWM Register2 (LSB) |               |             |         |         |        |         |         |                  |      | uuuu  | uuuu                  |

| CCPR2H  | Capture/Compare/PWM Register2 (MSB) |               |             |         |         |        |         |         |                  |      | uuuu  | uuuu                  |

| CCP2CON | _                                   | _             | DC2B1       | DC2B0   | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00               | 0000 | 00    | 0000                  |

$\label{eq:local_equation} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \textbf{u} = \textbf{unchanged}, \textbf{-} = \textbf{unimplemented}, \textbf{read as '0'}. \textbf{Shaded cells are not used by PWM and Timer2}.$

# 15.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 15-1 shows the formula for computation of the baud rate for different USART modes, which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 15-1. From this, the error in baud rate can be determined.

Example 15-1 shows the calculation of the baud rate error for the following conditions:

- Fosc = 16 MHz

- Desired Baud Rate = 9600

- BRGH = 0

- SYNC = 0

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the Fosc/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 15.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### **EXAMPLE 15-1: CALCULATING BAUD RATE ERROR**

| Desired Baud Rate    | = Fosc / (64 (X + 1))                                                                         |

|----------------------|-----------------------------------------------------------------------------------------------|

| Solving for X:       |                                                                                               |

| X<br>X<br>X          | = ((Fosc / Desired Baud rate) / 64) - 1<br>= ((16000000 / 9600) / 64) - 1<br>= [25.042] = 25  |

| Calculated Baud Rate | = 16000000 / (64 (25 + 1))<br>= 9615                                                          |

| Error                | = (Calculated Baud Rate - Desired Baud Rate) Desired Baud Rate = (9615 - 9600) / 9600 = 0.16% |

### TABLE 15-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | NA                         |

Legend: X = value in SPBRG (0 to 255)

#### TABLE 15-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name  | Bit 7   | Bit 6    | Bit 5     | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|-------|---------|----------|-----------|-----------|-------|-------|-------|-------|-------------------------|---------------------------------|

| TXSTA | CSRC    | TX9      | TXEN      | SYNC      | _     | BRGH  | TRMT  | TX9D  | 0000 -010               | 0000 -010                       |

| RCSTA | SPEN    | RX9      | SREN      | CREN      | ADDEN | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00x                       |

| SPBRG | Baud Ra | te Gener | 0000 0000 | 0000 0000 |       |       |       |       |                         |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

### 15.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

# 15.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- If enable bit TXIE is set, the interrupt will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- Enable the transmission by setting enable bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

TABLE 15-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name   | Bit 7                   | Bit 6         | Bit 5  | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other RESETS |

|--------|-------------------------|---------------|--------|-----------|-----------|--------|--------|--------|-------------------------|---------------------------|

| INTCON | GIE/<br>GIEH            | PEIE/<br>GIEL | TMR0IE | INT0IE    | RBIE      | TMR0IF | INT0IF | RBIF   | 0000 000x               | 0000 000u                 |

| PIR1   | PSPIF <sup>(1)</sup>    | ADIF          | RCIF   | TXIF      | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                 |

| PIE1   | PSPIE <sup>(1)</sup>    | ADIE          | RCIE   | TXIE      | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                 |

| IPR1   | PSPIP <sup>(1)</sup>    | ADIP          | RCIP   | TXIP      | SSPIP     | CCP1IP | TMR2IP | TMR1IP | 0000 0000               | 0000 0000                 |

| RCSTA  | SPEN                    | RX9           | SREN   | CREN      | ADDEN     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                 |

| TXREG  | USART Transmit Register |               |        |           |           |        |        |        |                         | 0000 0000                 |

| TXSTA  | CSRC                    | TX9           | TXEN   | SYNC      | _         | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                 |

| SPBRG  | Baud Rate               | e Genera      |        | 0000 0000 | 0000 0000 |        |        |        |                         |                           |

Legend: x = unknown, - = unimplemented, read as '0'.

Shaded cells are not used for Synchronous Slave Transmission.

**Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18C2X2 devices. Always maintain these bits clear.

The value that is in the ADRESH/ADRESL registers is not modified for a Power-on Reset. The ADRESH/ADRESL registers will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 16.1. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- Configure the A/D module:

- Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear ADIF bit

- · Set ADIE bit

- · Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared OR

- · Waiting for the A/D interrupt

- Read A/D Result registers (ADRESH/ADRESL); clear bit ADIF if required.

- For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

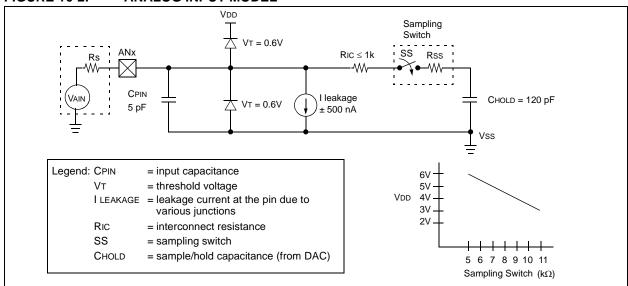

### 16.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 16-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is  $2.5 \ k\Omega$ . After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

**Note:** When the conversion is started, the holding capacitor is disconnected from the input pin.

#### FIGURE 16-2: ANALOG INPUT MODEL

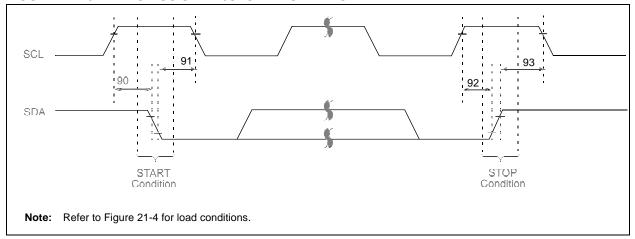

FIGURE 21-16: I<sup>2</sup>C BUS START/STOP BITS TIMING

## TABLE 21-15: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

| Param.<br>No. | Symbol  | Characteristic  |              | Min  | Max | Units | Conditions                  |

|---------------|---------|-----------------|--------------|------|-----|-------|-----------------------------|

| 90            | Tsu:sta | START condition | 100 kHz mode | 4700 | _   | ns    | Only relevant for Repeated  |

|               |         | Setup time      | 400 kHz mode | 600  | _   |       | START condition             |

| 91            | Thd:sta | START condition | 100 kHz mode | 4000 | _   | ns    | After this period the first |

|               |         | Hold time       | 400 kHz mode | 600  | _   |       | clock pulse is generated    |

| 92            | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | _   | ns    |                             |

|               |         | Setup time      | 400 kHz mode | 600  | _   |       |                             |

| 93            | Thd:sto | STOP condition  | 100 kHz mode | 4000 | _   | ns    |                             |

|               |         | Hold time       | 400 kHz mode | 600  | _   |       |                             |

TABLE 21-21: A/D CONVERTER CHARACTERISTICS: PIC18CXX2 (INDUSTRIAL, EXTENDED) PIC18LCXX2 (INDUSTRIAL)

| Param<br>No. | Symbol | Charac                     | teristic                  | Min            | Тур  | Max         | Units                                                                                               | Conditions                                   |

|--------------|--------|----------------------------|---------------------------|----------------|------|-------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------|

| A01          | NR     | Resolution                 |                           | _              | _    | 10          | bit                                                                                                 | VREF = VDD ≥ 3.0V                            |

|              |        |                            |                           | _              | _    | 10          | bit                                                                                                 | VREF = VDD < 3.0V                            |

| A03          | EIL    | Integral linearity         | / error                   | _              | _    | <±1         | LSb                                                                                                 | VREF = VDD ≥ 3.0V                            |

|              |        |                            |                           |                |      | <±2         | LSb                                                                                                 | VREF = VDD < 3.0V                            |

| A04          | EDL    | Differential lines         | arity error               |                | _    | <±1         | LSb                                                                                                 | $VREF = VDD \ge 3.0V$                        |

|              |        |                            |                           |                | <±2  | LSb         | VREF = VDD < 3.0V                                                                                   |                                              |

| A05          | EFS    | Full scale error           |                           |                | _    | <±1         | LSb                                                                                                 | $VREF = VDD \ge 3.0V$                        |

|              |        |                            |                           | _              |      | <±1         | LSb                                                                                                 | VREF = VDD < 3.0V                            |

| A06          | Eoff   | Offset error               |                           | _              | _    | <±1         | LSb                                                                                                 | VREF = VDD ≥ 3.0V                            |

|              |        |                            |                           | _              |      | <±1         | LSb                                                                                                 | VREF = VDD < 3.0V                            |

| A10          | _      | Monotonicity               | guaranteed <sup>(3)</sup> |                |      | _           | VSS ≤ VAIN ≤ VREF                                                                                   |                                              |

| A20          | VREF   | Reference voltage          |                           | 0V             | _    | _           | V                                                                                                   |                                              |

| A20A         |        | (VREFH - VREFL)            |                           | 3V             | _    | _           | V                                                                                                   | For 10-bit resolution                        |

| A21          | VREFH  | Reference volta            | ige High                  | AVss           | _    | AVDD + 0.3V | V                                                                                                   |                                              |

| A22          | VREFL  | Reference volta            | age Low                   | AVss -<br>0.3V | _    | AVDD        | V                                                                                                   |                                              |

| A25          | VAIN   | Analog input vo            | ltage                     | AVss -<br>0.3V | _    | VREF + 0.3V | V                                                                                                   |                                              |

| A30          | ZAIN   | Recommended analog voltage |                           | _              | _    | 10.0        | kΩ                                                                                                  |                                              |

| A40          | lad    | A/D conversion             | PIC18 <b>C</b> XXX        | _              | 180  | _           | μΑ                                                                                                  | Average current                              |

|              |        | current (VDD)              | PIC18 <b>LC</b> XXX       |                | 90   | _           | μА                                                                                                  | consumption when A/D is on <b>(Note 1)</b> . |

| A50          | IREF   | VREF input curr            | 10                        | _              | 1000 | μ <b>A</b>  | During VAIN acquisition. Based on differential of VHOLD to VAIN. To charge CHOLD, see Section 16.0. |                                              |

|              |        |                            |                           |                | _    | 10          | μА                                                                                                  | During A/D conversion cycle.                 |

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

VREF current is from RA2/AN2/VREF- and RA3/AN3/VREF+ pins or AVDD and AVSS pins, whichever is selected as reference input.

- **2:**  $VSS \le VAIN \le VREF$

- 3: The A/D conversion result never decreases with an increase in the Input Voltage, and has no missing codes.

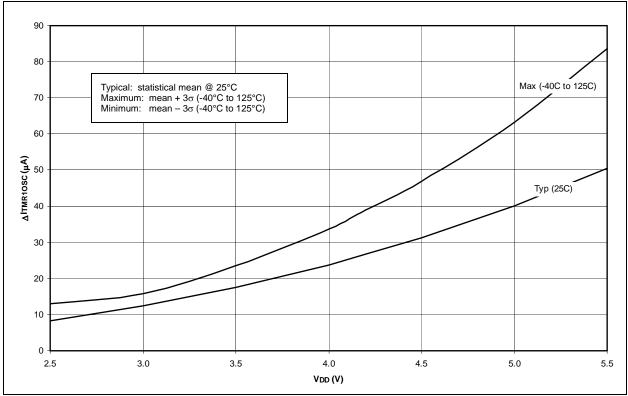

FIGURE 22-15: TYPICAL AND MAXIMUM ∆ITMR1 vs. VDD OVER TEMPERATURE (-40°C TO +125°C, TIMER1 WITH OSCILLATOR, XTAL=32 kHZ, C1 AND C2 = 47 pF)

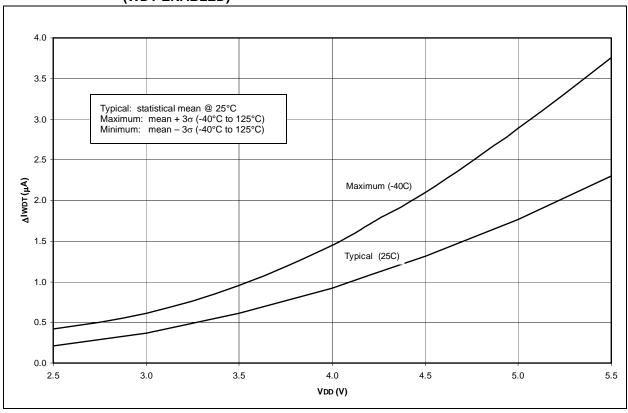

FIGURE 22-16: TYPICAL AND MAXIMUM AIWDT vs. VDD OVER TEMPERATURE (WDT ENABLED)

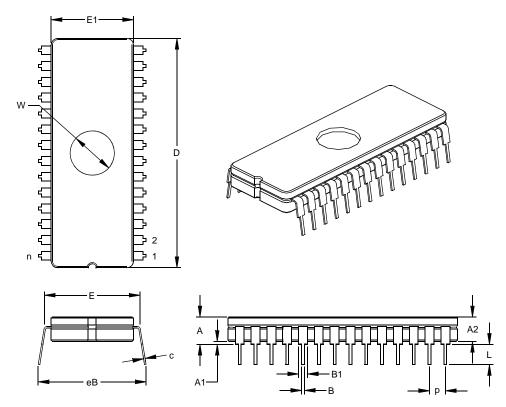

## 28-Lead Ceramic Dual In-line with Window (JW) - 600 mil (CERDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |    | INCHES* |       | MILLIMETERS |       |       |       |

|----------------------------|----|---------|-------|-------------|-------|-------|-------|

| Dimension Limits           |    | MIN     | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n  |         | 28    |             |       | 28    |       |

| Pitch                      | р  |         | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | Α  | .195    | .210  | .225        | 4.95  | 5.33  | 5.72  |

| Ceramic Package Height     | A2 | .155    | .160  | .165        | 3.94  | 4.06  | 4.19  |

| Standoff                   | A1 | .015    | .038  | .060        | 0.38  | 0.95  | 1.52  |

| Shoulder to Shoulder Width | Е  | .595    | .600  | .625        | 15.11 | 15.24 | 15.88 |

| Ceramic Pkg. Width         | E1 | .514    | .520  | .526        | 13.06 | 13.21 | 13.36 |

| Overall Length             | D  | 1.430   | 1.460 | 1.490       | 36.32 | 37.08 | 37.85 |

| Tip to Seating Plane       | L  | .125    | .138  | .150        | 3.18  | 3.49  | 3.81  |

| Lead Thickness             | С  | .008    | .010  | .012        | 0.20  | 0.25  | 0.30  |

| Upper Lead Width           | B1 | .050    | .058  | .065        | 1.27  | 1.46  | 1.65  |

| Lower Lead Width           | В  | .016    | .020  | .023        | 0.41  | 0.51  | 0.58  |

| Overall Row Spacing §      | eB | .610    | .660  | .710        | 15.49 | 16.76 | 18.03 |

| Window Diameter            | W  | .270    | .280  | .290        | 6.86  | 7.11  | 7.37  |

<sup>\*</sup>Controlling Parameter

§ Significant Characteristic

JEDEC Equivalent: MO-103

Drawing No. C04-013

NOTES:

|      | uction Set1 | 07 |

|------|-------------|----|

| nstr |             |    |

|      | ADDLW 1     |    |

|      | ADDWF 1     |    |

|      | ADDWFC1     | 94 |

|      | ANDLW1      | 94 |

|      | ANDWF 1     | 95 |

|      | BC          | 95 |

|      | BCF1        |    |

|      | BN          |    |

|      |             |    |

|      | BNC         | -  |

|      | BNOV 1      |    |

|      | BNZ 1       |    |

|      | BOV2        | 01 |

|      | BRA 1       | 99 |

|      | BSF1        | 99 |

|      | BTFSC2      | 00 |

|      | BTFSS       |    |

|      | BTG         |    |

|      |             | -  |

|      | BZ2         | -  |

|      | CALL2       | -  |

|      | CLRF2       | 03 |

|      | CLRWDT 2    | 03 |

|      | COMF2       | 04 |

|      | CPFSEQ2     | 04 |

|      | CPFSGT2     | -  |

|      | CPFSLT2     |    |

|      | DAW         |    |

|      |             |    |

|      | DECF        |    |

|      | DECFSNZ2    |    |

|      | DECFSZ      | 07 |

|      | GOTO2       | 80 |

|      | INCF2       | 08 |

|      | INCFSZ2     | 09 |

|      | INFSNZ      |    |

|      | IORLW2      |    |

|      | IORWF       |    |

|      | _           | -  |

|      | LFSR        |    |

|      | MOVF2       |    |

|      | MOVFF2      | 12 |

|      | MOVLB2      | 12 |

|      | MOVLW2      | 13 |

|      | MOVWF2      |    |

|      | MULLW       |    |

|      | MULWF       |    |

|      |             |    |

|      |             |    |

|      | NOP         | -  |

|      | RCALL2      |    |

|      | RESET2      | 17 |

|      | RETFIE2     | 18 |

|      | RETLW2      | 18 |

|      | RETURN2     | 19 |

|      | RLCF2       | 19 |

|      | RLNCF       | -  |

|      | RRCF        |    |

|      | -           | -  |

|      | RRNCF2      |    |

|      | SETF2       |    |

|      | SLEEP       | 22 |

|      | SUBFWB2     | 22 |

|      | SUBLW2      | 23 |

|      | SUBWF       |    |

|      | SUBWFB      | -  |

|      | SWAPF       |    |

|      |             |    |

|      | TBLRD       | -  |

|      | TBLWT2      | -  |

|      | TSTFSZ2     | 27 |

| XORLW                                          | 227        |

|------------------------------------------------|------------|

| XORWF                                          | 228        |

| Summary Table                                  | 190        |

| INT Interrupt (RB0/INT). See Interrupt Sources |            |

| INTCON Register                                |            |

| RBIF Bit                                       | 00         |

|                                                |            |

| INTCON Registers                               | ხე         |

| Inter-Integrated Circuit. See I <sup>2</sup> C |            |

| Internal Program Memory                        |            |

| Read/Writes                                    |            |

| Interrupt Sources                              | 179        |

| A/D Conversion Complete                        | 168        |

| Capture Complete (CCP)                         |            |

| Compare Complete (CCP)                         |            |

| INTO                                           |            |

| Interrupt-on-Change (RB7:RB4)                  | 70<br>80   |

| PORTB, on Change                               |            |

| RB0/INT Pin, External                          |            |

| COD Desaite /Transmit Complete                 | 15         |

| SSP Receive/Transmit Complete                  |            |

| TMR0                                           |            |

| TMR0 Overflow                                  |            |

| TMR1 Overflow 97, 99, 103,                     |            |

| TMR2 to PR2 Match                              |            |

| TMR2 to PR2 Match (PWM) 101,                   | 112        |

| USART Receive/Transmit Complete                | 149        |

| Interrupts, Enable Bits                        |            |

| CCP1 Enable (CCP1IE Bit)                       | 109        |

| Interrupts, Flag Bits                          |            |

| A/D Converter Flag (ADIF Bit)                  | 167        |

| CCP1 Flag (CCP1IF Bit)                         | 110        |

| Interrupt-on-Change (RB7:RB4) Flag (RBIF Bit)  |            |

| IORLW                                          |            |

| IORWF                                          |            |

| IPR Registers                                  |            |

| IFK Registers                                  | 12         |

| K                                              |            |

| KEELOQ Evaluation and Programming Tools        | 222        |

| REELOQ EVALUATION AND FROGRAMMING TOOLS        | 232        |

| L                                              |            |

| LFSR                                           | 211        |

| Long Write                                     | 211        |

| and Interrupts                                 | <b>5</b> 0 |

|                                                |            |

| Operation                                      |            |

| Sequence of Events                             |            |

| Unexpected Termination                         |            |

| Low Voltage Detect                             | 173        |

| Block Diagrams                                 |            |

| External Reference Source                      |            |

| Internal Reference Source                      | 174        |

| Converter Characteristics                      | 242        |

| Effects of a RESET                             | 177        |

| Operation                                      |            |

| Current Consumption                            |            |

| During SLEEP                                   |            |

| Reference Voltage Set Point                    | 177        |

| LVD. See Low Voltage Detect.                   | .,,        |

| CCO LOTT TORRAGO DOGOGO.                       |            |

| M                                             |             | PICSTART Plus Entry Level Development System  | 23               | 31 |

|-----------------------------------------------|-------------|-----------------------------------------------|------------------|----|

| Master Synchronous Serial Port (MSSP). See S  | SP          | PIE Registers                                 |                  | 7( |

| Memory Organization                           | <b>J</b> F. | Pin Functions                                 |                  |    |

|                                               | 40          | MCLR/VPP                                      | 10. <sup>-</sup> | 13 |

| Data Memory                                   |             | OSC1/CLKIN                                    |                  |    |

| Program Memory                                |             | OSC2/CLKOUT                                   |                  |    |

| Migration from Baseline to Enhanced Devices   |             | RA0/AN0                                       |                  |    |

| MOVF                                          |             | RA1/AN1                                       |                  |    |

| MOVFF                                         | 212         | RA2/AN2                                       | ,                |    |

| MOVLB                                         | 212         |                                               |                  |    |

| MOVLW                                         | 213         | RA3/AN3/VREF                                  | ,                |    |

| MOVWF                                         | 213         | RA4/T0CKI                                     |                  |    |

| MPLAB C17 and MPLAB C18 C Compilers           | 229         | RA5/AN4/SS                                    |                  |    |

| MPLAB ICD In-Circuit Debugger                 | 231         | RB0/INT                                       |                  |    |

| MPLAB ICE High Performance Universal          |             | RB1                                           |                  |    |

| In-Circuit Emulator with MPLAB IDE            | 230         | RB2                                           | ,                |    |

| MPLAB Integrated Development                  |             | RB3                                           | ,                |    |

| Environment Software                          | 229         | RB4                                           | 11, ʻ            | 14 |

| MPLINK Object Linker/MPLIB Object Librarian . |             | RB5                                           | 11, 1            | 14 |

| MULLW                                         |             | RB6                                           | 11, 1            | 14 |

| Multi-Master Mode                             |             | RB7                                           | 11, <sup>-</sup> | 14 |

|                                               |             | RC0/T1OSO/T1CKI                               | 12, <sup>-</sup> | 15 |

| MULWF                                         | 214         | RC1/T1OSI/CCP2                                | -                |    |

| N                                             |             | RC2/CCP1                                      |                  |    |

|                                               |             | RC3/SCK/SCL                                   |                  |    |

| NEGF                                          |             | RC4/SDI/SDA                                   | ,                |    |

| NOP                                           | 215         | RC5/SDO                                       | ,                |    |

| 0                                             |             | RC6/TX/CK                                     | ,                |    |

|                                               |             |                                               | ,                |    |

| On-Chip Reset Circuit                         |             | RC7/RX/DT                                     | ,                |    |

| Block Diagram                                 | 25          | RD0/PSP0                                      |                  |    |

| OPCODE Field Descriptions                     | 188         | RD1/PSP1                                      |                  |    |

| OPTION_REG Register                           |             | RD2/PSP2                                      |                  |    |

| PS2:PS0 Bits                                  | 95          | RD3/PSP3                                      |                  |    |

| PSA Bit                                       | 95          | RD4/PSP4                                      | <i>'</i>         | 16 |

| T0CS Bit                                      | 95          | RD5/PSP5                                      | <i>"</i>         | 16 |

| T0SE Bit                                      | 95          | RD6/PSP6                                      | <i>'</i>         | 16 |

| Oscillator Configuration                      | 179         | RD7/PSP7                                      | '                | 16 |

| Oscillator Configurations                     |             | RE0/RD/AN5                                    | <sup>,</sup>     | 16 |

| HS                                            |             | RE1/WR/AN6                                    | ·                | 16 |

| HS + PLL                                      |             | RE2/CS/AN7                                    |                  | 16 |

| LP                                            |             | VDD                                           |                  |    |

| RC                                            |             | Vss                                           | ,                |    |

| _                                             | , -         | PIR Registers                                 | ,                |    |

| RCIO                                          |             | Pointer, FSR                                  |                  |    |

| XT                                            |             | POR. See Power-on Reset.                      |                  | )( |

| Oscillator, Timer1                            |             | PORTA                                         |                  |    |

| Oscillator, WDT                               | 183         |                                               |                  | 7  |

| P                                             |             | Associated Registers                          |                  |    |

|                                               |             | Initialization                                |                  |    |

| Packaging                                     |             | PORTA Register                                |                  |    |

| Parallel Slave Port (PSP)                     |             | RA3:RA0 and RA5 Port Pins                     |                  |    |

| Associated Registers                          | 91          | RA4/T0CKI Pin                                 |                  |    |

| Block Diagram                                 | 90          | RA6 Pin                                       |                  | 78 |

| RE0/RD/AN5 Pin                                | 89, 90      | TRISA Register                                |                  | 77 |

| RE1/WR/AN6 Pin                                | 89, 90      | PORTB                                         |                  |    |

| RE2/CS/AN7 Pin                                | 89, 90      | Associated Registers                          | 8                | 82 |

| Read Waveforms                                |             | Initialization                                | 8                | 80 |

| Select (PSPMODE Bit)                          | -           | PORTB Register                                | 8                | 80 |

| Timing Diagram                                | •           | RB0/INT Pin, External                         |                  |    |

| Write Waveforms                               |             | RB3 Pin                                       |                  |    |

| PICDEM 1 Low Cost PIC MCU                     |             | RB3:RB0 Port Pins                             |                  |    |

| Demonstration Board                           | 224         | RB7:RB4 Interrupt-on-Change Flag (RBIF Bit) . |                  | -  |

|                                               |             | RB7:RB4 Port Pins                             |                  |    |

| PICDEM 17 Demonstration Board                 | 232         |                                               |                  |    |

| PICDEM 2 Low Cost PIC16CXX                    | 224         | TRISB Register                                |                  | J  |

| Demonstration Board                           | 231         |                                               |                  |    |

| PICDEM 3 Low Cost PIC16CXXX                   |             |                                               |                  |    |

| Demonstration Board                           | 232         |                                               |                  |    |