Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

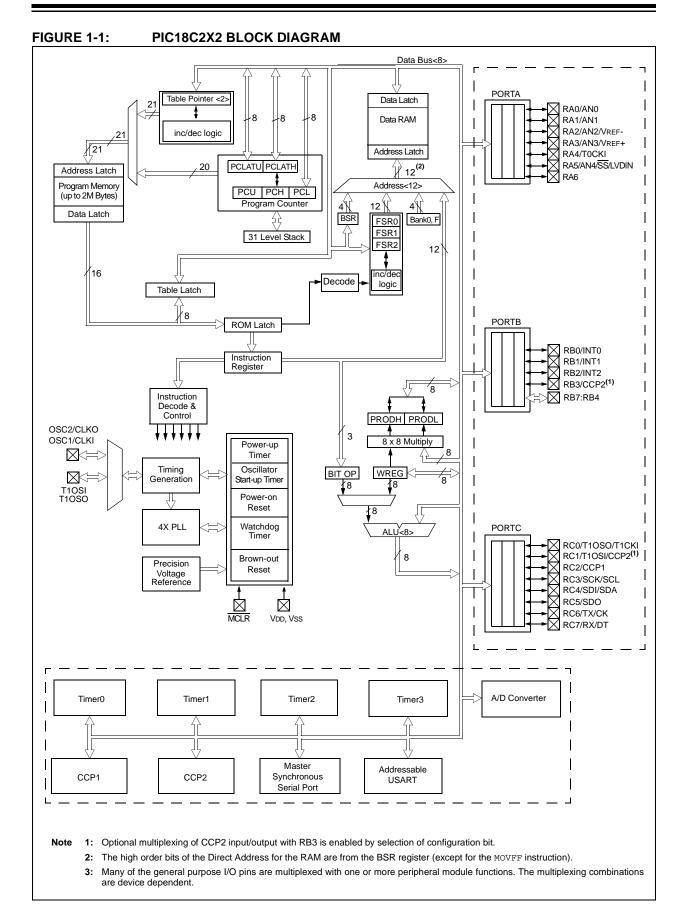

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

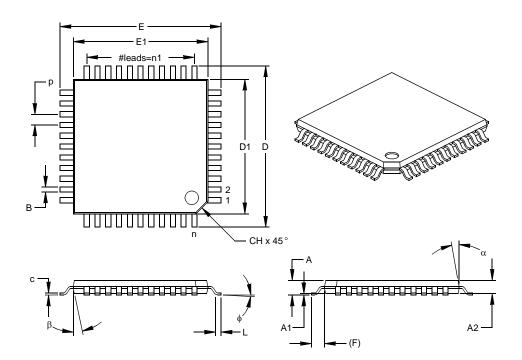

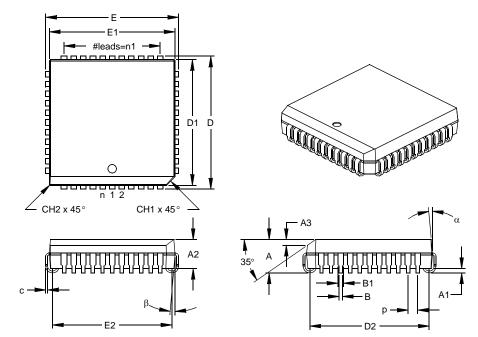

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lc452-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Oscillator                         | Power-up                  | (2)                | - (2)                     | Wake-up from                  |  |

|------------------------------------|---------------------------|--------------------|---------------------------|-------------------------------|--|

| Configuration                      | PWRTE = 0PWRTE = 1        |                    | Brown-out <sup>(2)</sup>  | SLEEP or<br>Oscillator Switch |  |

| HS with PLL enabled <sup>(1)</sup> | 72 ms + 1024Tosc<br>+ 2ms | 1024Tosc<br>+ 2 ms | 72 ms + 1024Tosc<br>+ 2ms | 1024Tosc + 2 ms               |  |

| HS, XT, LP                         | 72 ms + 1024Tosc          | 1024Tosc           | 72 ms + 1024Tosc          | 1024Tosc                      |  |

| EC                                 | 72 ms                     | _                  | 72 ms                     | —                             |  |

| External RC                        | 72 ms                     |                    | 72 ms                     | —                             |  |

**Note 1:** 2 ms is the nominal time required for the 4x PLL to lock.

**2:** 72 ms is the nominal Power-up Timer delay.

#### REGISTER 3-1: RCON REGISTER BITS AND POSITIONS

| R/W-0 | R/W-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-0 | R/W-0 |

|-------|-------|-----|-------|-------|-------|-------|-------|

| IPEN  | LWRT  | —   | RI    | TO    | PD    | POR   | BOR   |

| bit 7 |       |     |       |       |       |       | bit 0 |

**Note:** See Register 4-3 on page 53 for bit definitions.

## TABLE 3-2:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

| Condition                                     | Program<br>Counter    | RCON<br>Register | RI | то | PD | POR | BOR | STKFUL | STKUNF |

|-----------------------------------------------|-----------------------|------------------|----|----|----|-----|-----|--------|--------|

| Power-on Reset                                | 0000h                 | 00-1 1100        | 1  | 1  | 1  | 0   | 0   | u      | u      |

| MCLR Reset during normal operation            | 0000h                 | 00-u uuuu        | u  | u  | u  | u   | u   | u      | u      |

| Software Reset during normal operation        | 0000h                 | 0u-0 uuuu        | 0  | u  | u  | u   | u   | u      | u      |

| Stack Full Reset during normal operation      | 0000h                 | 0u-u uull        | u  | u  | u  | u   | u   | u      | 1      |

| Stack Underflow Reset during normal operation | 0000h                 | 0u-u uull        | u  | u  | u  | u   | u   | 1      | u      |

| MCLR Reset during SLEEP                       | 0000h                 | 00-u 10uu        | u  | 1  | 0  | u   | u   | u      | u      |

| WDT Reset                                     | 0000h                 | 0u-u 01uu        | 1  | 0  | 1  | u   | u   | u      | u      |

| WDT Wake-up                                   | PC + 2                | uu-u 00uu        | u  | 0  | 0  | u   | u   | u      | u      |

| Brown-out Reset                               | 0000h                 | 0u-1 11u0        | 1  | 1  | 1  | 1   | 0   | u      | u      |

| Interrupt wake-up from SLEEP                  | PC + 2 <sup>(1)</sup> | uu-u 00uu        | u  | 1  | 0  | u   | u   | u      | u      |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (0x000008h or 0x000018h).

| Register Applicable Devices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |           |           |                       |

|-----------------------------|-----|------------------------------------|---------------------------------------------------------------|---------------------------------|-----------|-----------|-----------------------|

| TOSU                        | 242 | 442                                | 252                                                           | 452                             | 0 0000    | 0 0000    | 0 uuuu <b>(3)</b>     |

| TOSH                        | 242 | 442                                | 252                                                           | 452                             | 0000 0000 | 0000 0000 | uuuu uuuu <b>(3)</b>  |

| TOSL                        | 242 | 442                                | 252                                                           | 452                             | 0000 0000 | 0000 0000 | uuuu uuuu <b>(3)</b>  |

| STKPTR                      | 242 | 442                                | 252                                                           | 452                             | 00-0 0000 | 00-0 0000 | uu-u uuuu <b>(3)</b>  |

| PCLATU                      | 242 | 442                                | 252                                                           | 452                             | 0 0000    | 0 0000    | u uuuu                |

| PCLATH                      | 242 | 442                                | 252                                                           | 452                             | 0000 0000 | 0000 0000 | uuuu uuuu             |

| PCL                         | 242 | 442                                | 252                                                           | 452                             | 0000 0000 | 0000 0000 | PC + 2 <sup>(2)</sup> |

| TBLPTRU                     | 242 | 442                                | 252                                                           | 452                             | 00 0000   | 00 0000   | uu uuuu               |

| TBLPTRH                     | 242 | 442                                | 252                                                           | 452                             | 0000 0000 | 0000 0000 | սսսս սսսս             |

| TBLPTRL                     | 242 | 442                                | 252                                                           | 452                             | 0000 0000 | 0000 0000 | uuuu uuuu             |

| TABLAT                      | 242 | 442                                | 252                                                           | 452                             | 0000 0000 | 0000 0000 | uuuu uuuu             |

| PRODH                       | 242 | 442                                | 252                                                           | 452                             | xxxx xxxx | uuuu uuuu | uuuu uuuu             |

| PRODL                       | 242 | 442                                | 252                                                           | 452                             | xxxx xxxx | uuuu uuuu | uuuu uuuu             |

| INTCON                      | 242 | 442                                | 252                                                           | 452                             | 0000 000x | 0000 000u | uuuu uuuu <b>(1)</b>  |

| INTCON2                     | 242 | 442                                | 252                                                           | 452                             | 1111 -1-1 | 1111 -1-1 | uuuu -u-u <b>(1)</b>  |

| INTCON3                     | 242 | 442                                | 252                                                           | 452                             | 11-0 0-00 | 11-0 0-00 | uu-u u-uu <b>(1)</b>  |

| INDF0                       | 242 | 442                                | 252                                                           | 452                             | N/A       | N/A       | N/A                   |

| POSTINC0                    | 242 | 442                                | 252                                                           | 452                             | N/A       | N/A       | N/A                   |

| POSTDEC0                    | 242 | 442                                | 252                                                           | 452                             | N/A       | N/A       | N/A                   |

| PREINC0                     | 242 | 442                                | 252                                                           | 452                             | N/A       | N/A       | N/A                   |

| PLUSW0                      | 242 | 442                                | 252                                                           | 452                             | N/A       | N/A       | N/A                   |

| FSR0H                       | 242 | 442                                | 252                                                           | 452                             | 0000      | 0000      | uuuu                  |

| FSR0L                       | 242 | 442                                | 252                                                           | 452                             | XXXX XXXX | uuuu uuuu | սսսս սսսս             |

| WREG                        | 242 | 442                                | 252                                                           | 452                             | XXXX XXXX | uuuu uuuu | սսսս սսսս             |

| INDF1                       | 242 | 442                                | 252                                                           | 452                             | N/A       | N/A       | N/A                   |

| POSTINC1                    | 242 | 442                                | 252                                                           | 452                             | N/A       | N/A       | N/A                   |

| POSTDEC1                    | 242 | 442                                | 252                                                           | 452                             | N/A       | N/A       | N/A                   |

| PREINC1                     | 242 | 442                                | 252                                                           | 452                             | N/A       | N/A       | N/A                   |

| PLUSW1                      | 242 | 442                                | 252                                                           | 452                             | N/A       | N/A       | N/A                   |

#### TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 3-2 for RESET value for specific condition.

- 5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

- 6: The long write enable is only reset on a POR or MCLR Reset.

- 7: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read as '0'.

## 4.3 Fast Register Stack

A "fast interrupt return" option is available for interrupts. A Fast Register Stack is provided for the STATUS, WREG and BSR registers and are only one in depth. The stack is not readable or writable and is loaded with the current value of the corresponding register when the processor vectors for an interrupt. The values in the registers are then loaded back into the working registers, if the FAST RETURN instruction is used to return from the interrupt.

A low or high priority interrupt source will push values into the stack registers. If both low and high priority interrupts are enabled, the stack registers cannot be used reliably for low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten.

If high priority interrupts are not disabled during low priority interrupts, users must save the key registers in software during a low priority interrupt.

If no interrupts are used, the fast register stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a FAST CALL instruction must be executed.

Example 4-1 shows a source code example that uses the fast register stack.

#### EXAMPLE 4-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|-----------------|---------------------------------------------------------|

| SUB1            |                                                         |

| RETURN FAST     | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

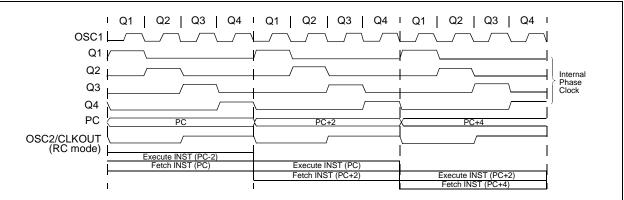

## FIGURE 4-4: CLOCK/INSTRUCTION CYCLE

4.4 PCL, PCLATH and PCLATU

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21-bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCH register. The Upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCU register may be performed through the PCLATU register.

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the LSB of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

The contents of PCLATH and PCLATU will be transferred to the program counter by an operation that writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see Section 4.8.1).

## 4.5 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 4-4.

#### 4.7.1 TWO-WORD INSTRUCTIONS

The PIC18CXX2 devices have four two-word instructions: MOVFF, CALL, GOTO and LFSR. The second word of these instructions has the 4 MSBs set to 1's and is a special kind of NOP instruction. The lower 12bits of the second word contain data to be used by the instruction. If the first word of the instruction is executed, the data in the second word is accessed. If the second word of the instruction is executed by itself (first word was skipped), it will execute as a NOP. This action is necessary when the two-word instruction is preceded by a conditional instruction that changes the PC. A program example that demonstrates this concept is shown in Example 4-3. Refer to Section 19.0 for further details of the instruction set.

| EXAMPLE 4-3: | <b>TWO-WORD INSTRUCTIONS</b> |

|--------------|------------------------------|

|              |                              |

| CASE 1:             |            |            |                                     |

|---------------------|------------|------------|-------------------------------------|

| Object Code         | Source Cod | le         |                                     |

| 0110 0110 0000 0000 | TSTFSZ     | REG1       | ; is RAM location 0?                |

| 1100 0001 0010 0011 | MOVFF      | REG1, REG2 | ; No, execute 2-word instruction    |

| 1111 0100 0101 0110 |            |            | ; 2nd operand holds address of REG2 |

| 0010 0100 0000 0000 | ADDWF      | REG3       | ; continue code                     |

| CASE 2:             |            |            |                                     |

| Object Code         | Source Cod | le         |                                     |

| 0110 0110 0000 0000 | TSTFSZ     | REG1       | ; is RAM location 0?                |

| 1100 0001 0010 0011 | MOVFF      | REG1, REG2 | ; Yes                               |

| 1111 0100 0101 0110 |            |            | ; 2nd operand becomes NOP           |

| 0010 0100 0000 0000 | ADDWF      | REG3       | ; continue code                     |

## 4.8 Lookup Tables

Lookup tables are implemented two ways. These are:

- Computed GOTO

- Table Reads

## 4.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL).

A lookup table can be formed with an ADDWF PCL instruction and a group of RETLW 0xnn instructions. WREG is loaded with an offset into the table, before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW 0xnn instructions that returns the value 0xnn to the calling function.

The offset value (value in WREG) specifies the number of bytes that the program counter should advance.

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

## 4.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory allows 2 bytes of data to be stored in each instruction location.

Lookup table data may be stored 2 bytes per program word by using table reads and writes. The table pointer (TBLPTR) specifies the byte address and the table latch (TABLAT) contains the data that is read from, or written to program memory. Data is transferred to/from program memory one byte at a time.

A description of the Table Read/Table Write operation is shown in Section 5.0.

## 5.1 Control Registers

Several control registers are used in conjunction with the  ${\tt TBLRD}$  and  ${\tt TBLWT}$  instructions. These include the:

- TBLPTR registers

- TABLAT register

- RCON register

#### 5.1.1 RCON REGISTER

The LWRT bit specifies the operation of Table Writes to internal memory when the VPP voltage is applied to the MCLR pin. When the LWRT bit is set, the controller continues to execute user code, but long Table Writes are allowed (for programming internal program memory) from user mode. The LWRT bit can be cleared only by performing either a POR or MCLR Reset.

#### REGISTER 5-1: RCON REGISTER (ADDRESS: FD0h)

| R/W-0 | R/W-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-0 | R/W-0 |

|-------|-------|-----|-------|-------|-------|-------|-------|

| IPEN  | LWRT  | —   | RI    | TO    | PD    | POR   | BOR   |

| bit 7 |       |     |       |       |       |       | bit 0 |

|  | bit 7 | <b>IPEN:</b> | Interrupt | Prioritv | Enable bit |

|--|-------|--------------|-----------|----------|------------|

|--|-------|--------------|-----------|----------|------------|

- 1 = Enable priority levels on interrupts

- 0 = Disable priority levels on interrupts (16CXXX compatibility mode)

- bit 6 LWRT: Long Write Enable bit

- 1 = Enable TBLWT to internal program memory

- 0 = Disable TBLWT to internal program memory.

- Note:Only cleared on a POR or MCLR Reset.This bit has no effect on TBLWTs to external program memory.

- bit 5 Unimplemented: Read as '0'

- bit 4 RI: RESET Instruction Flag bit

- 1 = No RESET instruction occurred

- 0 = A RESET instruction occurred

- bit 3 TO: Time-out bit

- 1 = After power-up, CLRWDT instruction, or SLEEP instruction

- 0 = A WDT time-out occurred

- bit 2 **PD:** Power-down bit

- 1 = After power-up or by the CLRWDT instruction

- 0 = By execution of the SLEEP instruction

- bit 1 POR: Power-on Reset Status bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 BOR: Brown-out Reset Status bit

- 1 = No Brown-out Reset or POR Reset occurred

- 0 = A Brown-out Reset or POR Reset occurred

- (must be set in software after a Brown-out Reset occurs)

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 8.0 I/O PORTS

Depending on the device selected, there are either five ports, or three ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

The data latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

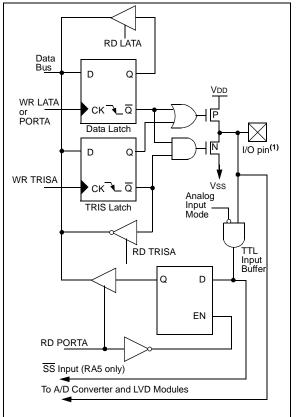

## 8.1 PORTA, TRISA and LATA Registers

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

| Note: | On a Power-on Reset, these pins are con- |

|-------|------------------------------------------|

|       | figured as digital inputs.               |

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch.

The Data Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register reads and writes the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

The other PORTA pins are multiplexed with analog inputs and the analog VREF+ and VREF- inputs. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 8-1: INITIALIZING PORTA

| CLRF PORTA   | ; Initialize PORTA by<br>; clearing output |

|--------------|--------------------------------------------|

|              | ; data latches                             |

| CLRF LATA    | ; Alternate method                         |

|              | ; to clear output                          |

|              | ; data latches                             |

| MOVLW 0x07   | ; Configure A/D                            |

| MOVWF ADCON1 | ; for digital inputs                       |

| MOVLW 0xCF   | ; Value used to                            |

|              | ; initialize data                          |

|              | ; direction                                |

| MOVWF TRISA  | ; Set RA<3:0> as inputs                    |

|              | ; RA<5:4> as outputs                       |

|              |                                            |

|              |                                            |

FIGURE 8-1:

#### BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

## TABLE 8-1: PORTA FUNCTIONS

| Name             | Bit# | Buffer | Function                                                                                                     |

|------------------|------|--------|--------------------------------------------------------------------------------------------------------------|

| RA0/AN0          | bit0 | TTL    | Input/output or analog input.                                                                                |

| RA1/AN1          | bit1 | TTL    | Input/output or analog input.                                                                                |

| RA2/AN2/VREF-    | bit2 | TTL    | Input/output or analog input or VREF                                                                         |

| RA3/AN3/VREF+    | bit3 | TTL    | Input/output or analog input or VREF+.                                                                       |

| RA4/T0CKI        | bit4 | ST     | Input/output or external clock input for Timer0.<br>Output is open drain type.                               |

| RA5/SS/AN4/LVDIN | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input, or low voltage detect input. |

| OSC2/CLKO/RA6    | bit6 | TTL    | OSC2 or clock output or I/O pin.                                                                             |

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 8-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7 | Bit 6   | Bit 5     | Bit 4     | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|-------|---------|-----------|-----------|--------|-------|-------|-------|-------------------------|---------------------------------|

| PORTA  | —     | RA6     | RA5       | RA4       | RA3    | RA2   | RA1   | RA0   | 0x 0000                 | 0u 0000                         |

| LATA   |       | Latch A | Data Outp | out Regis | ster   |       |       |       | xx xxxx                 | uu uuuu                         |

| TRISA  |       | PORTA   | Data Dire | ction Reg | gister |       |       |       | 11 1111                 | 11 1111                         |

| ADCON1 | ADFM  | ADCS2   | —         | —         | PCFG3  | PCFG2 | PCFG1 | PCFG0 | 0- 0000                 | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

$\ensuremath{\textcircled{}^\circ}$  1999-2013 Microchip Technology Inc.

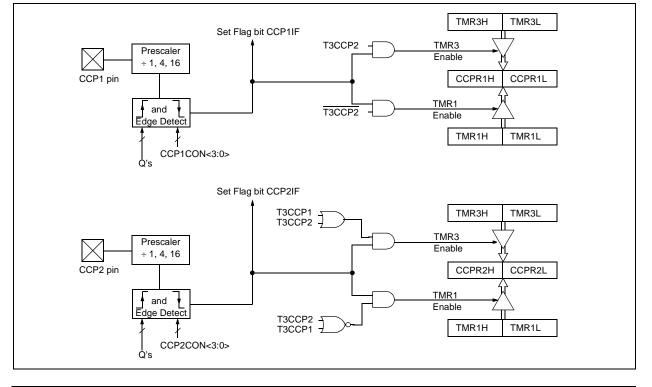

## 13.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on pin RC2/CCP1. An event is defined as:

- · every falling edge

- every rising edge

- every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 13.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-                |

|-------|---------------------------------------------------------|

|       | put, a write to the port can cause a capture condition. |

|       | oonalion.                                               |

#### 13.3.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (either Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each CCP module is selected in the T3CON register.

#### 13.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 13.3.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 13-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

## EXAMPLE 13-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON, F  | ; | Turn CCP module off |

|-------|-------------|---|---------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the  |

|       |             | ; | new prescaler mode  |

|       |             | ; | value and CCP ON    |

| MOVWF | CCP1CON     | ; | Load CCP1CON with   |

|       |             | ; | this value          |

|       |             |   |                     |

## FIGURE 13-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

| TABLE 15-4: | BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0) |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

| PAUD        | Fosc = 40 MHz         |            |                             | F                     | Fosc = 20 MHz |                             |                       | Fosc = 16 MHz |                             |                       | Fosc = 10 MHz |                             |  |

|-------------|-----------------------|------------|-----------------------------|-----------------------|---------------|-----------------------------|-----------------------|---------------|-----------------------------|-----------------------|---------------|-----------------------------|--|

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error    | SPBRG<br>value<br>(decimal) |  |

| 0.3         | NA                    |            | _                           | NA                    | _             | _                           | NA                    | _             | _                           | NA                    | _             | _                           |  |

| 1.2         | NA                    | —          | —                           | 1.221                 | +1.73         | 255                         | 1.202                 | +0.16         | 207                         | 1.202                 | +0.16         | 129                         |  |

| 2.4         | 2.44                  | -1.70      | 255                         | 2.404                 | +0.16         | 129                         | 2.404                 | +0.16         | 103                         | 2.404                 | +0.16         | 64                          |  |

| 9.6         | 9.62                  | -0.16      | 64                          | 9.469                 | -1.36         | 32                          | 9.615                 | +0.16         | 25                          | 9.766                 | +1.73         | 15                          |  |

| 19.2        | 18.94                 | +1.38      | 32                          | 19.53                 | +1.73         | 15                          | 19.23                 | +0.16         | 12                          | 19.53                 | +1.73         | 7                           |  |

| 76.8        | 78.13                 | -1.70      | 7                           | 78.13                 | +1.73         | 3                           | 83.33                 | +8.51         | 2                           | 78.13                 | +1.73         | 1                           |  |

| 96          | 89.29                 | +7.52      | 6                           | 104.2                 | +8.51         | 2                           | NA                    | —             | —                           | NA                    | —             | —                           |  |

| 300         | 312.50                | -4.00      | 1                           | 312.5                 | +4.17         | 0                           | NA                    | _             | —                           | NA                    | —             | —                           |  |

| 500         | 625.00                | -20.00     | 0                           | NA                    | —             |                             | NA                    |               | —                           | NA                    | —             | —                           |  |

| HIGH        | 2.44                  | —          | 255                         | 312.5                 | _             | 0                           | 250                   | —             | 0                           | 156.3                 | —             | 0                           |  |

| LOW         | 625.00                | —          | 0                           | 1.221                 | —             | 255                         | 0.977                 | —             | 255                         | 0.6104                | —             | 255                         |  |

| DAUD        | Fosc = 7.15909 MHz    |            | Fos                         | Fosc = 5.0688 MHz     |            |                             | Fosc = 4 MHz          |            |                             | Fosc = 3.579545 MHz   |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | NA                    |            | _                           | 0.31                  | +3.13      | 255                         | 0.3005                | -0.17      | 207                         | 0.301                 | +0.23      | 185                         |

| 1.2         | 1.203                 | +0.23      | 92                          | 1.2                   | 0          | 65                          | 1.202                 | +1.67      | 51                          | 1.190                 | -0.83      | 46                          |

| 2.4         | 2.380                 | -0.83      | 46                          | 2.4                   | 0          | 32                          | 2.404                 | +1.67      | 25                          | 2.432                 | +1.32      | 22                          |

| 9.6         | 9.322                 | -2.90      | 11                          | 9.9                   | +3.13      | 7                           | NA                    |            | —                           | 9.322                 | -2.90      | 5                           |

| 19.2        | 18.64                 | -2.90      | 5                           | 19.8                  | +3.13      | 3                           | NA                    | _          | —                           | 18.64                 | -2.90      | 2                           |

| 76.8        | NA                    | _          | _                           | 79.2                  | +3.13      | 0                           | NA                    | _          | _                           | NA                    | _          | _                           |

| 96          | NA                    | —          | —                           | NA                    | _          | —                           | NA                    | _          | —                           | NA                    | _          | _                           |

| 300         | NA                    | _          | _                           |

| 500         | NA                    | —          | —                           | NA                    | _          | —                           | NA                    | _          | —                           | NA                    | _          | _                           |

| HIGH        | 111.9                 | —          | 0                           | 79.2                  | _          | 0                           | 62.500                | _          | 0                           | 55.93                 | _          | 0                           |

| LOW         | 0.437                 | —          | 255                         | 0.3094                | _          | 255                         | 3.906                 |            | 255                         | 0.2185                |            | 255                         |

| DAUD                | F                     | osc = 1    | MHz                         | Fos                   | SC = 32.76 | 68 kHz                      |

|---------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.300                 | +0.16      | 51                          | 0.256                 | -14.67     | 1                           |

| 1.2                 | 1.202                 | +0.16      | 12                          | NA                    | _          | _                           |

| 2.4                 | 2.232                 | -6.99      | 6                           | NA                    | —          | —                           |

| 9.6                 | NA                    | —          | —                           | NA                    | —          | —                           |

| 19.2                | NA                    | _          | _                           | NA                    | _          | —                           |

| 76.8                | NA                    | _          | —                           | NA                    | _          | _                           |

| 96                  | NA                    | _          | —                           | NA                    | _          | _                           |

| 300                 | NA                    | _          | —                           | NA                    | _          | _                           |

| 500                 | NA                    | _          | _                           | NA                    | —          | —                           |

| HIGH                | 15.63                 | _          | 0                           | 0.512                 | —          | 0                           |

| LOW                 | 0.0610                | —          | 255                         | 0.0020                | —          | 255                         |

NOTES:

address (HERE)

address (Jump)

0; address (HERE+2)

| BTG   |               | Bit Toggl                                  | e f                                                                                    |                                               | ВС        | v              | Branch if                                                         | Overflow                                                       |             |  |  |

|-------|---------------|--------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------|-----------|----------------|-------------------------------------------------------------------|----------------------------------------------------------------|-------------|--|--|

| Synt  | ax:           | [ <i>label</i> ] B                         | STG f,b[,a]                                                                            |                                               | Sy        | ntax:          | [ <i>label</i> ] B                                                | OV n                                                           |             |  |  |

| Oper  | rands:        | 0 ≤ f ≤ 25                                 | 5                                                                                      |                                               | Ор        | erands:        | -128 ≤ n ≤                                                        | $-128 \le n \le 127$                                           |             |  |  |

|       |               | 0 ≤ b < 7<br>a ∈ [0,1]                     |                                                                                        |                                               | Ор        | eration:       |                                                                   | if overflow bit is '1' $(PC) + 2 + 2n \rightarrow PC$          |             |  |  |

| Oper  | ration:       | $(\overline{f} < b >) \rightarrow 1$       | f <b></b>                                                                              |                                               | Sta       | atus Affected: | None                                                              |                                                                |             |  |  |

| Statu | us Affected:  | None                                       |                                                                                        |                                               | En        | coding:        | 1110                                                              | 0100 nn                                                        | nn nnnn     |  |  |

| Enco  | oding:        | 0111                                       | bbba f                                                                                 | fff ffff                                      |           | scription:     | If the Ove                                                        | rflow bit is '1                                                | , then the  |  |  |

| Desc  | cription:     | inverted. I<br>will be sel<br>value. If 'a | ata memory I<br>If 'a' is 0, the<br>ected, overrid<br>a' = 1, then th<br>as per the BS | Access Bank<br>ding the BSR<br>le bank will b |           |                | The 2's co<br>added to t<br>have incre<br>instruction<br>PC+2+2n. | he PC. Since<br>emented to fe<br>to the new ad<br>This instrue |             |  |  |

| Word  | ds:           | 1                                          |                                                                                        |                                               |           |                | a two-cycl                                                        | e instruction                                                  |             |  |  |

| Cycl  | es:           | 1                                          |                                                                                        |                                               | Wo        | ords:          | 1                                                                 |                                                                |             |  |  |

| QC    | vcle Activity |                                            |                                                                                        |                                               | Су        | cles:          | 1(2)                                                              |                                                                |             |  |  |

|       | Q1            | Q2                                         | Q3                                                                                     | Q4                                            |           | Cycle Activity | <i>r</i> :                                                        |                                                                |             |  |  |

|       | Decode        | Read<br>register 'f'                       | Process<br>Data                                                                        | Write<br>register 'f'                         | lf -      | Jump:<br>Q1    | Q2                                                                | Q3                                                             | Q4          |  |  |

| Exar  | nole:         |                                            | PORTC, 4,                                                                              |                                               |           | Decode         | Read literal<br>'n'                                               | Process<br>Data                                                | Write to PC |  |  |

|       | Before Instru |                                            |                                                                                        | •                                             |           | No             | No                                                                | No                                                             | No          |  |  |

|       | PORTC         |                                            | 0101 [0x75]                                                                            |                                               | 14        | operation      | operation                                                         | operation                                                      | operation   |  |  |

|       | After Instruc | tion:                                      |                                                                                        |                                               | If        | No Jump:       | 00                                                                | 00                                                             | 04          |  |  |

|       | PORTC         | = 0110 (                                   | 0101 [0x65]                                                                            |                                               |           | Q1<br>Decode   | Q2<br>Read literal                                                | Q3<br>Process                                                  | Q4<br>No    |  |  |

|       |               |                                            |                                                                                        |                                               |           | Decode         | 'n'                                                               | Data                                                           | operation   |  |  |

|       |               |                                            |                                                                                        |                                               | <u>Ex</u> | ample:         | HERE                                                              | BOV Jump                                                       |             |  |  |

**Before Instruction** PC

After Instruction If Overflow=

=

PC =

If Overflow= PC =

1;

| DECFSZ                                    |                 | Decreme                                                                                                                                                      | Decrement f, skip if 0                                                                                               |                       |                        |  |  |  |  |

|-------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|--|--|--|--|

| Syntax:                                   |                 | [label]                                                                                                                                                      | [ label ] DECFSZ f [,d [,a]]                                                                                         |                       |                        |  |  |  |  |

| Operands:                                 |                 | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                          |                                                                                                                      |                       |                        |  |  |  |  |

| Operation:                                |                 | (f) – 1 $\rightarrow$ c<br>skip if rest                                                                                                                      |                                                                                                                      |                       |                        |  |  |  |  |

| Status Affect                             | ed:             | None                                                                                                                                                         |                                                                                                                      |                       |                        |  |  |  |  |

| Encoding:                                 |                 | 0010                                                                                                                                                         | 11da                                                                                                                 | ffff                  | ffff                   |  |  |  |  |

| Description:                              |                 | placed in V<br>result is pl<br>(default).<br>If the resu<br>tion, which<br>discarded<br>instead, m<br>instruction<br>Bank will b<br>the BSR v<br>bank will b | decremented. If 'd' is 0, the result is<br>placed in WREG. If 'd' is 1, the<br>result is placed back in register 'f' |                       |                        |  |  |  |  |

| Words:                                    |                 | BSR value (default).<br>1                                                                                                                                    |                                                                                                                      |                       |                        |  |  |  |  |

| Cycles:<br>Q Cycle Act                    | ivity:          | 1(2)<br><b>Note:</b> 3 c<br>by                                                                                                                               | -                                                                                                                    | skip and<br>d instruc |                        |  |  |  |  |

| Q Oycle Act                               | ivity.          | Q2                                                                                                                                                           | Q3                                                                                                                   | 3                     | Q4                     |  |  |  |  |

| Decod                                     | е               | Read<br>register 'f'                                                                                                                                         | Proce<br>Data                                                                                                        | ss V                  | Write to<br>estination |  |  |  |  |

| If skip:                                  |                 |                                                                                                                                                              |                                                                                                                      |                       |                        |  |  |  |  |

| Q1                                        |                 | Q2                                                                                                                                                           | Q3                                                                                                                   | 5                     | Q4                     |  |  |  |  |

| No                                        |                 | No                                                                                                                                                           | No                                                                                                                   |                       | No                     |  |  |  |  |

| operatio                                  |                 | operation                                                                                                                                                    | operat                                                                                                               |                       | peration               |  |  |  |  |

| If skip and fo                            | VIIOW           | -                                                                                                                                                            | _                                                                                                                    |                       | <u>.</u>               |  |  |  |  |

| Q1                                        |                 | Q2                                                                                                                                                           | Q3                                                                                                                   | 5<br>T                | Q4                     |  |  |  |  |

| No<br>operatio                            | n               | No<br>operation                                                                                                                                              | No<br>operat                                                                                                         | ion                   | No<br>peration         |  |  |  |  |

| No                                        |                 | No                                                                                                                                                           | No                                                                                                                   |                       | No                     |  |  |  |  |

| operatio                                  | on              | operation                                                                                                                                                    | operat                                                                                                               | ion o                 | peration               |  |  |  |  |

| Example:                                  | Example:        |                                                                                                                                                              | DECFS<br>GOTO                                                                                                        |                       | F, 1, 1<br>)P          |  |  |  |  |

| Before In<br>PC<br>After Ins<br>CNT<br>If | cnt             | = Addres<br>ion<br>= CNT -<br>= 0;                                                                                                                           |                                                                                                                      |                       |                        |  |  |  |  |

| If                                        | PC<br>CNT<br>PC | ≠ 0;                                                                                                                                                         | s (CON<br>s (HER                                                                                                     |                       |                        |  |  |  |  |

| DCFSNZ             | Decrement f, skip if not 0                                                                                                                                                |                                                                                                                                                            |                 |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Syntax:            | [label] D                                                                                                                                                                 | CFSNZ f[,                                                                                                                                                  | d [,a]          |  |  |  |  |  |

| Operands:          | $0 \le f \le 255$                                                                                                                                                         | 5                                                                                                                                                          |                 |  |  |  |  |  |

|                    | d ∈ [0,1]                                                                                                                                                                 |                                                                                                                                                            |                 |  |  |  |  |  |

| Onerting           | a ∈ [0,1]                                                                                                                                                                 | 14                                                                                                                                                         |                 |  |  |  |  |  |

| Operation:         | (f) – 1 $\rightarrow$ c<br>skip if resu                                                                                                                                   |                                                                                                                                                            |                 |  |  |  |  |  |

| Status Affected:   | None                                                                                                                                                                      |                                                                                                                                                            |                 |  |  |  |  |  |

| Encoding:          | 0100                                                                                                                                                                      | 11da fff                                                                                                                                                   | f ffff          |  |  |  |  |  |

| Description:       | remented.<br>placed in V<br>result is pl<br>(default).<br>If the resu<br>instruction<br>fetched, is<br>executed i<br>cycle instr<br>Access Ba<br>overriding<br>then the b | The contents of register 'f' are dec-<br>remented. If 'd' is 0, the result is<br>placed in WREG. If 'd' is 1, the<br>result is placed back in register 'f' |                 |  |  |  |  |  |

| Words:             | рег ше во<br>1                                                                                                                                                            | SR value (de                                                                                                                                               | auit).          |  |  |  |  |  |

| Cycles:            | 1(2)                                                                                                                                                                      |                                                                                                                                                            |                 |  |  |  |  |  |

| Q Cycle Activity   | by                                                                                                                                                                        | ycles if skip a<br>a 2-word inst                                                                                                                           |                 |  |  |  |  |  |

| Q1                 | Q2                                                                                                                                                                        | Q3                                                                                                                                                         | Q4              |  |  |  |  |  |

| Decode             | Read                                                                                                                                                                      | Process                                                                                                                                                    | Write to        |  |  |  |  |  |

|                    | register 'f'                                                                                                                                                              | Data                                                                                                                                                       | destination     |  |  |  |  |  |

| If skip:           | 00                                                                                                                                                                        | 00                                                                                                                                                         | 0.4             |  |  |  |  |  |

| Q1                 | Q2                                                                                                                                                                        | Q3                                                                                                                                                         | Q4              |  |  |  |  |  |

| No<br>operation    | No<br>operation                                                                                                                                                           | No<br>operation                                                                                                                                            | No<br>operation |  |  |  |  |  |

| If skip and follow |                                                                                                                                                                           | •                                                                                                                                                          | operation       |  |  |  |  |  |

| Q1                 | Q2                                                                                                                                                                        | Q3                                                                                                                                                         | Q4              |  |  |  |  |  |

| No                 | No                                                                                                                                                                        | No                                                                                                                                                         | No              |  |  |  |  |  |

| operation          | operation                                                                                                                                                                 | operation                                                                                                                                                  | operation       |  |  |  |  |  |

| No                 | No                                                                                                                                                                        | No                                                                                                                                                         | No              |  |  |  |  |  |

| operation          | operation                                                                                                                                                                 | operation                                                                                                                                                  | operation       |  |  |  |  |  |

| Example:           | ZERO                                                                                                                                                                      | DCFSNZ TEM<br>:                                                                                                                                            | IP, 1, 0        |  |  |  |  |  |

| Before Instr       | uction                                                                                                                                                                    |                                                                                                                                                            |                 |  |  |  |  |  |

| TEMP               | =                                                                                                                                                                         | ?                                                                                                                                                          |                 |  |  |  |  |  |

| After Instruc      |                                                                                                                                                                           | ר האיםית                                                                                                                                                   |                 |  |  |  |  |  |

| TEMP<br>If TEM     | =<br>P =                                                                                                                                                                  | TEMP - 1,<br>0;                                                                                                                                            |                 |  |  |  |  |  |

| PC<br>If TEM       | =<br>P ≠                                                                                                                                                                  | Address<br>0;                                                                                                                                              | (ZERO)          |  |  |  |  |  |

| PC                 | ₽ ≠<br>=                                                                                                                                                                  | 0;<br>Address                                                                                                                                              | (NZERO)         |  |  |  |  |  |

|                    |                                                                                                                                                                           |                                                                                                                                                            |                 |  |  |  |  |  |

| IOR                                         | LW                     | Inclusive                   | Inclusive OR literal with WREG |      |                  |  |  |  |  |

|---------------------------------------------|------------------------|-----------------------------|--------------------------------|------|------------------|--|--|--|--|

| Synt                                        | tax:                   | [ label ]                   | IORLW                          | k    |                  |  |  |  |  |

| Ope                                         | rands:                 | $0 \leq k \leq 255$         |                                |      |                  |  |  |  |  |

| Operation: (WREG) .OR. $k \rightarrow WREG$ |                        |                             |                                |      |                  |  |  |  |  |

| State                                       | us Affected:           | N,Z                         |                                |      |                  |  |  |  |  |

| Enc                                         | oding:                 | 0000                        | 1001                           | kkkk | kkkk             |  |  |  |  |

| Des                                         | cription:              | /REG a<br>iteral 'k<br>WREC |                                |      |                  |  |  |  |  |

| Wor                                         | ds:                    | 1                           |                                |      |                  |  |  |  |  |

| Cycl                                        | es:                    | 1                           |                                |      |                  |  |  |  |  |

| QC                                          | Cycle Activity:        |                             |                                |      |                  |  |  |  |  |

|                                             | Q1                     | Q2                          | Q3                             | 3    | Q4               |  |  |  |  |

|                                             | Decode                 | Read<br>literal 'k'         | Proce<br>Data                  |      | Write to<br>WREG |  |  |  |  |

| Example:<br>Before Instruc                  |                        | IORLW                       | 0x35                           |      |                  |  |  |  |  |

|                                             | WREG<br>After Instruct | = 0x9A                      |                                |      |                  |  |  |  |  |

WREG = 0xBF

| IORWF                              | Inclusive OR WREG with f                                                                                                                                                                                                                                                                   |             |        |                |  |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|----------------|--|--|--|

| Syntax:                            | [ label ]                                                                                                                                                                                                                                                                                  | IORWF       | f [,d  | [,a]           |  |  |  |

| Operands:                          | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                        |             |        |                |  |  |  |