Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lc452t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| Pin Name                                     | Pi        | n Numb | ber  | Pin      | Buffer           | Description                                                                                                                                                     |

|----------------------------------------------|-----------|--------|------|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                     | DIP       | PLCC   | TQFP | Туре     | Туре             | Description                                                                                                                                                     |

| MCLR/VPP<br>MCLR                             | 1         | 2      | 18   | I        | ST               | Master clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active                                                       |

| Vpp                                          |           |        |      | Р        |                  | low RESET to the device.<br>Programming voltage input.                                                                                                          |

| NC                                           |           |        |      | _        | _                | These pins should be left unconnected.                                                                                                                          |

| OSC1/CLKI<br>OSC1                            | 13        | 14     | 30   | I        | ST               | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode, CMOS otherwise |

| CLKI                                         |           |        |      | I        | CMOS             | External clock source input. Always associated with<br>pin function OSC1. (See related OSC1/CLKIN,<br>OSC2/CLKOUT pins.)                                        |

| OSC2/CLKO/RA6<br>OSC2                        | 14        | 15     | 31   | 0        | _                | Oscillator crystal output.<br>Oscillator crystal output. Connects to crystal                                                                                    |

| CLKO                                         |           |        |      | 0        | _                | or resonator in Crystal Oscillator mode.<br>In RC mode, OSC2 pin outputs CLKOUT, which has<br>1/4 the frequency of OSC1 and denotes the instruction             |

| RA6                                          |           |        |      | I/O      | TTL              | cycle rate.<br>General Purpose I/O pin.                                                                                                                         |

|                                              |           |        |      |          |                  | PORTA is a bi-directional I/O port.                                                                                                                             |

| RA0/AN0                                      | 2         | 3      | 19   |          |                  |                                                                                                                                                                 |

| RA0                                          |           | -      |      | I/O      | TTL              | Digital I/O.                                                                                                                                                    |

| AN0                                          |           |        |      | Ι        | Analog           | Analog input 0.                                                                                                                                                 |

| RA1/AN1                                      | 3         | 4      | 20   |          |                  |                                                                                                                                                                 |

| RA1                                          |           |        |      | I/O      | TTL              | Digital I/O.                                                                                                                                                    |

| AN1                                          |           |        |      | I        | Analog           | Analog input 1.                                                                                                                                                 |

| RA2/AN2/VREF-                                | 4         | 5      | 21   |          |                  |                                                                                                                                                                 |

| RA2                                          |           |        |      | I/O      | TTL              | Digital I/O.                                                                                                                                                    |

| AN2<br>Vref-                                 |           |        |      |          | Analog<br>Analog | Analog input 2.<br>A/D Reference Voltage (Low) input.                                                                                                           |

| RA3/AN3/VREF+                                | 5         | 6      | 22   |          | / indiog         |                                                                                                                                                                 |

| RA3                                          | 5         | 0      | 22   | I/O      | TTL              | Digital I/O.                                                                                                                                                    |

| AN3                                          |           |        |      |          | Analog           | Analog input 3.                                                                                                                                                 |

| VREF+                                        |           |        |      | Ι        | Analog           | A/D Reference Voltage (High) input.                                                                                                                             |

| RA4/T0CKI                                    | 6         | 7      | 23   |          |                  |                                                                                                                                                                 |

| RA4<br>T0CKI                                 |           |        |      | I/O<br>I | ST/OD<br>ST      | Digital I/O. Open drain when configured as output.<br>Timer0 external clock input.                                                                              |

| RA5/AN4/SS/LVDIN                             | 7         | 8      | 24   |          |                  |                                                                                                                                                                 |

| RA5                                          |           |        |      | I/O      | TTL              | Digital I/O.                                                                                                                                                    |

| AN4                                          |           |        |      |          | Analog           | Analog input 4.                                                                                                                                                 |

| SS                                           |           |        |      |          | ST               | SPI Slave Select input.                                                                                                                                         |

|                                              |           |        |      | I        | Analog           | Low Voltage Detect Input.                                                                                                                                       |

| RA6                                          |           |        |      |          |                  | See the OSC2/CLKO/RA6 pin.                                                                                                                                      |

| Legend: TTL = TTL<br>ST = Schm<br>O = Output | nitt Trig |        |      | MOS le   | vels I = I       | OS = CMOS compatible input or output<br>Input<br>Power                                                                                                          |

| TABLE 1-3: PIC 10C4AZ PINOUT I/O DESCRIPTIONS | TABLE 1-3: | PIC18C4X2 PINOUT I/O DESCRIPTIONS |

|-----------------------------------------------|------------|-----------------------------------|

|-----------------------------------------------|------------|-----------------------------------|

OD = Open Drain (no P diode to VDD)

$\odot$  1999-2013 Microchip Technology Inc.

| Oscillator                         | Power-up                  | (2)                | - (2)                     | Wake-up from                  |

|------------------------------------|---------------------------|--------------------|---------------------------|-------------------------------|

| Configuration                      | PWRTE = 0                 | PWRTE = 1          | Brown-out <sup>(2)</sup>  | SLEEP or<br>Oscillator Switch |

| HS with PLL enabled <sup>(1)</sup> | 72 ms + 1024Tosc<br>+ 2ms | 1024Tosc<br>+ 2 ms | 72 ms + 1024Tosc<br>+ 2ms | 1024Tosc + 2 ms               |

| HS, XT, LP                         | 72 ms + 1024Tosc          | 1024Tosc           | 72 ms + 1024Tosc          | 1024Tosc                      |

| EC                                 | 72 ms                     | _                  | 72 ms                     | —                             |

| External RC                        | 72 ms                     |                    | 72 ms                     | —                             |

**Note 1:** 2 ms is the nominal time required for the 4x PLL to lock.

**2:** 72 ms is the nominal Power-up Timer delay.

#### REGISTER 3-1: RCON REGISTER BITS AND POSITIONS

| R/W-0 | R/W-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-0 | R/W-0 |

|-------|-------|-----|-------|-------|-------|-------|-------|

| IPEN  | LWRT  | —   | RI    | TO    | PD    | POR   | BOR   |

| bit 7 |       |     |       |       |       |       | bit 0 |

**Note:** See Register 4-3 on page 53 for bit definitions.

# TABLE 3-2:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

| Condition                                     | Program<br>Counter    | RCON<br>Register | RI | то | PD | POR | BOR | STKFUL | STKUNF |

|-----------------------------------------------|-----------------------|------------------|----|----|----|-----|-----|--------|--------|

| Power-on Reset                                | 0000h                 | 00-1 1100        | 1  | 1  | 1  | 0   | 0   | u      | u      |

| MCLR Reset during normal operation            | 0000h                 | 00-u uuuu        | u  | u  | u  | u   | u   | u      | u      |

| Software Reset during normal operation        | 0000h                 | 0u-0 uuuu        | 0  | u  | u  | u   | u   | u      | u      |

| Stack Full Reset during normal operation      | 0000h                 | 0u-u uull        | u  | u  | u  | u   | u   | u      | 1      |

| Stack Underflow Reset during normal operation | 0000h                 | 0u-u uull        | u  | u  | u  | u   | u   | 1      | u      |

| MCLR Reset during SLEEP                       | 0000h                 | 00-u 10uu        | u  | 1  | 0  | u   | u   | u      | u      |

| WDT Reset                                     | 0000h                 | 0u-u 01uu        | 1  | 0  | 1  | u   | u   | u      | u      |

| WDT Wake-up                                   | PC + 2                | uu-u 00uu        | u  | 0  | 0  | u   | u   | u      | u      |

| Brown-out Reset                               | 0000h                 | 0u-1 11u0        | 1  | 1  | 1  | 1   | 0   | u      | u      |

| Interrupt wake-up from SLEEP                  | PC + 2 <sup>(1)</sup> | uu-u 00uu        | u  | 1  | 0  | u   | u   | u      | u      |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (0x000008h or 0x000018h).

| Register                | Applicable Devices |     |     | ces | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |  |

|-------------------------|--------------------|-----|-----|-----|------------------------------------|---------------------------------------------------------------|---------------------------------|--|--|--|

| TRISE                   | 242                | 442 | 252 | 452 | 0000 -111                          | 0000 -111                                                     | uuuu -uuu                       |  |  |  |

| TRISD                   | 242                | 442 | 252 | 452 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |  |  |

| TRISC                   | 242                | 442 | 252 | 452 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |  |  |

| TRISB                   | 242                | 442 | 252 | 452 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |  |  |

| TRISA <sup>(5, 7)</sup> | 242                | 442 | 252 | 452 | -111 1111 <b>(5)</b>               | -111 1111 <b>(5)</b>                                          | -uuu uuuu <b><sup>(5)</sup></b> |  |  |  |

| LATE                    | 242                | 442 | 252 | 452 | xxx                                | uuu                                                           | uuu                             |  |  |  |

| LATD                    | 242                | 442 | 252 | 452 | xxxx xxxx                          | սսսս սսսս                                                     | uuuu uuuu                       |  |  |  |

| LATC                    | 242                | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |

| LATB                    | 242                | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |

| LATA <sup>(5, 7)</sup>  | 242                | 442 | 252 | 452 | -xxx xxxx(5)                       | -uuu uuuu <b>(5)</b>                                          | -uuu uuuu <b>(5)</b>            |  |  |  |

| PORTE                   | 242                | 442 | 252 | 452 | 000                                | 000                                                           | uuu                             |  |  |  |

| PORTD                   | 242                | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |

| PORTC                   | 242                | 442 | 252 | 452 | XXXX XXXX                          | սսսս սսսս                                                     | uuuu uuuu                       |  |  |  |

| PORTB                   | 242                | 442 | 252 | 452 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |

| PORTA <sup>(5, 7)</sup> | 242                | 442 | 252 | 452 | -x0x 0000 <b>(5)</b>               | -u0u 0000 <b>(5)</b>                                          | -uuu uuuu <sup>(5)</sup>        |  |  |  |

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 3-2 for RESET value for specific condition.

5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

**6:** The long write enable is only reset on a POR or  $\overline{MCLR}$  Reset.

7: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read as '0'.

## 4.0 MEMORY ORGANIZATION

There are two memory blocks in Enhanced MCU devices. These memory blocks are:

- Program Memory

- Data Memory

Program and data memory use separate buses so that concurrent access can occur.

#### 4.1 Program Memory Organization

A 21-bit program counter is capable of addressing the 2-Mbyte program memory space. Accessing a location between the physically implemented memory and the 2-Mbyte address will cause a read of all '0's (a NOP instruction).

PIC18C252 and PIC18C452 have 32 Kbytes of EPROM, while PIC18C242 and PIC18C442 have 16 Kbytes of EPROM. This means that PIC18CX52 devices can store up to 16K of single word instructions, and PIC18CX42 devices can store up to 8K of single word instructions.

The RESET vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

Figure 4-1 shows the Program Memory Map for PIC18C242/442 devices and Figure 4-2 shows the Program Memory Map for PIC18C252/452 devices.

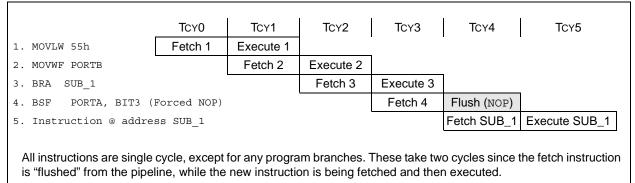

#### 4.6 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO), then two cycles are required to complete the instruction (Example 4-2).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### EXAMPLE 4-2: INSTRUCTION PIPELINE FLOW

### 4.7 Instructions in Program Memory

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSB ='0'). Figure 4-5 shows an example of how instruction words are stored in the program memory. To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read '0' (see Section 4.4). The CALL and GOTO instructions have an absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 4-5 shows how the instruction "GOTO 00006h" is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single word instructions that the PC will be offset by. Section 19.0 provides further details of the instruction set.

#### FIGURE 4-5: INSTRUCTIONS IN PROGRAM MEMORY

|                |             |                    | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|-------------|--------------------|---------|---------|---------------------------|

|                | Program M   |                    |         |         | 000000h                   |

|                | Byte Locati | ions $\rightarrow$ |         |         | 000002h                   |

|                |             |                    |         |         | 000004h                   |

|                |             |                    |         |         | 000006h                   |

| Instruction 1: | MOVLW       | 055h               | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO        | 000006h            | EFh     | 03h     | 00000Ah                   |

|                |             |                    | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF       | 123h, 456h         | Clh     | 23h     | 00000Eh                   |

|                |             |                    | F4h     | 56h     | 000010h                   |

|                |             |                    |         |         | 000012h                   |

|                |             |                    |         |         | 000014h                   |

# PIC18CXX2

NOTES:

### 13.1 CCP1 Module

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

#### TABLE 13-1: CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource   |  |  |

|----------|------------------|--|--|

| Capture  | Timer1 or Timer3 |  |  |

| Compare  | Timer1 or Timer3 |  |  |

| PWM      | Timer2           |  |  |

## 13.2 CCP2 Module

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

### TABLE 13-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                                                                               |

|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | TMR1 or TMR3 time-base. Time-base can be different for each CCP.                                                                          |

| Capture   | Compare   | The compare could be configured for the special event trigger, which clears either TMR1, or TMR3, depending upon which time-base is used. |

| Compare   | Compare   | The compare(s) could be configured for the special event trigger, which clears TMR1, or TMR3, depending upon which time-base is used.     |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                   |

| PWM       | Capture   | None.                                                                                                                                     |

| PWM       | Compare   | None.                                                                                                                                     |

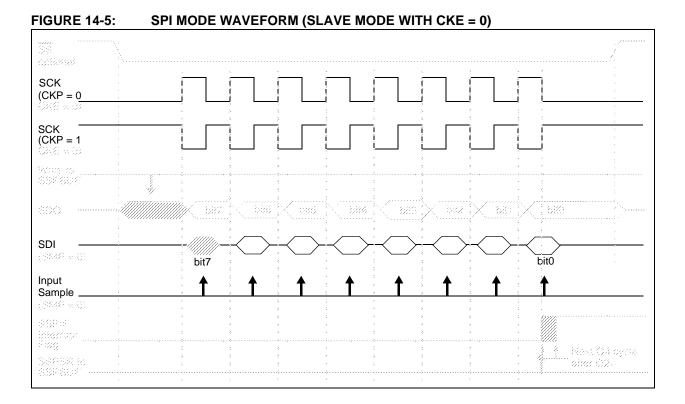

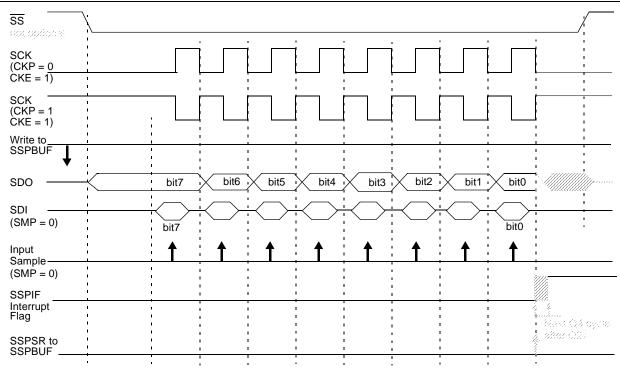

### FIGURE 14-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

#### 14.4.1.1 Addressing

Once the MSSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit BF is set.

- c) An ACK pulse is generated.

- MSSP interrupt flag bit SSPIF (PIR1<3>) is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

#### 14.4.1.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address <u>byte</u> overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

#### 14.4.1.3 Transmission

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 14-9).

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Pin RC3/SCK/SCL should be enabled by setting bit CKP.

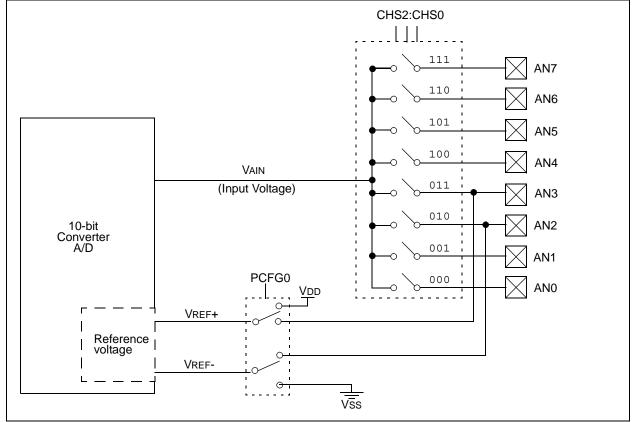

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and VSS) or the voltage level on the RA3/AN3/ VREF+ pin and RA2/AN2/VREF-.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off and any conversion is aborted.

Each port pin associated with the A/D converter can be configured as an analog input (RA3 can also be a voltage reference) or as a digital I/O.

The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ ADRESL registers, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 16-1.

#### FIGURE 16-1: A/D BLOCK DIAGRAM

# PIC18CXX2

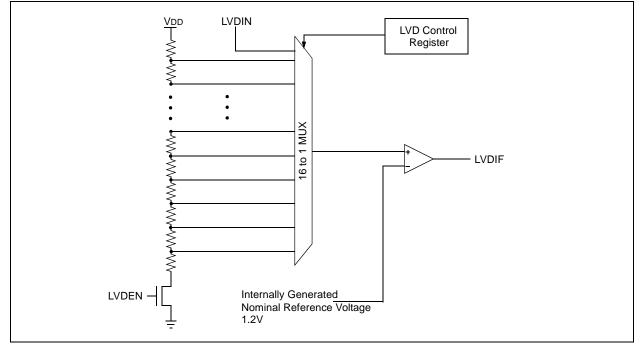

#### FIGURE 17-2: LOW VOLTAGE DETECT (LVD) BLOCK DIAGRAM

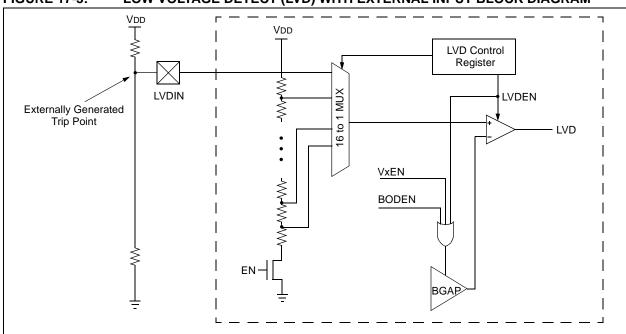

The LVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits LVDL3:LVDL0 are set to 1111. In this state, the comparator input is multiplexed from the external input pin LVDIN (Figure 17-3). This gives flexibility, because it allows a user to configure the Low Voltage Detect interrupt to occur at any voltage in the valid operating range.

FIGURE 17-3: LOW VOLTAGE DETECT (LVD) WITH EXTERNAL INPUT BLOCK DIAGRAM

### 18.2 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO/RA6 pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the RCON register will be cleared upon a WDT time-out.

The Watchdog Timer is enabled/disabled by a device configuration bit. If the WDT is enabled, software execution may not disable this function. When the WDTEN configuration bit is cleared, the SWDTEN bit enables/ disables the operation of the WDT. The WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT postscaler may be assigned using the configuration bits.

**Note:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

**Note:** When a CLRWDT instruction is executed and the postscaler is assigned to the WDT, the postscaler count will be cleared, but the postscaler assignment is not changed.

#### 18.2.1 CONTROL REGISTER

Register 18-7 shows the WDTCON register. This is a readable and writable register, which contains a control bit that allows software to override the WDT enable configuration bit, only when the configuration bit has disabled the WDT.

#### **REGISTER 18-7: WDTCON REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

|       | —   | —   | —   | —   | —   | _   | SWDTEN |

| bit 7 |     |     |     |     |     |     | bit 0  |

#### bit 7-1 Unimplemented: Read as '0'

- bit 0 SWDTEN: Software Controlled Watchdog Timer Enable bit

- 1 = Watchdog Timer is on

- Watchdog Timer is turned off if the WDTEN configuration bit in the configuration register = '0'

| Legend:                            |                          |

|------------------------------------|--------------------------|

| R = Readable bit                   | W = Writable bit         |

| U = Unimplemented bit, read as '0' | - n = Value at POR Reset |

| TABLE 19-2: | PIC18CXXX INSTRUCTION SET | (CONTINUED) |

|-------------|---------------------------|-------------|

|-------------|---------------------------|-------------|

| Mnem     | nonic,  | Description                     | Cycles       | 16-  | bit Inst | ruction | Word | Status          | Natas |

|----------|---------|---------------------------------|--------------|------|----------|---------|------|-----------------|-------|

| Operands |         | Description                     | Cycles       | MSb  |          |         | LSb  | Affected        | Notes |

| LITERAL  | OPERATI | ONS                             |              |      |          |         |      |                 |       |

| ADDLW    | k       | Add literal and WREG            | 1            | 0000 | 1111     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| ANDLW    | k       | AND literal with WREG           | 1            | 0000 | 1011     | kkkk    | kkkk | Z, N            |       |

| IORLW    | k       | Inclusive OR literal with WREG  | 1            | 0000 | 1001     | kkkk    | kkkk | Z, N            |       |

| LFSR     | f, k    | Move literal (12-bit) 2nd word  | 2            | 1110 | 1110     | 00ff    | kkkk | None            |       |

|          |         | to FSRx 1st word                |              | 1111 | 0000     | kkkk    | kkkk |                 |       |

| MOVLB    | k       | Move literal to BSR<3:0>        | 1            | 0000 | 0001     | 0000    | kkkk | None            |       |

| MOVLW    | k       | Move literal to WREG            | 1            | 0000 | 1110     | kkkk    | kkkk | None            |       |

| MULLW    | k       | Multiply literal with WREG      | 1            | 0000 | 1101     | kkkk    | kkkk | None            |       |

| RETLW    | k       | Return with literal in WREG     | 2            | 0000 | 1100     | kkkk    | kkkk | None            |       |

| SUBLW    | k       | Subtract WREG from literal      | 1            | 0000 | 1000     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| XORLW    | k       | Exclusive OR literal with WREG  | 1            | 0000 | 1010     | kkkk    | kkkk | Z, N            |       |

| DATA ME  |         | PROGRAM MEMORY OPERATI          | ONS          |      |          |         |      |                 |       |

| TBLRD*   |         | Table Read                      | 2            | 0000 | 0000     | 0000    | 1000 | None            |       |

| TBLRD*+  |         | Table Read with post-increment  |              | 0000 | 0000     | 0000    | 1001 | None            |       |

| TBLRD*-  |         | Table Read with post-decrement  |              | 0000 | 0000     | 0000    | 1010 | None            |       |

| TBLRD+*  |         | Table Read with pre-increment   |              | 0000 | 0000     | 0000    | 1011 | None            |       |

| TBLWT*   |         | Table Write                     | 2 <b>(5)</b> | 0000 | 0000     | 0000    | 1100 | None            |       |

| TBLWT*+  |         | Table Write with post-increment |              | 0000 | 0000     | 0000    | 1101 | None            |       |

| TBLWT*-  |         | Table Write with post-decrement |              | 0000 | 0000     | 0000    | 1110 | None            |       |

| TBLWT+*  |         | Table Write with pre-increment  |              | 0000 | 0000     | 0000    | 1111 | None            |       |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2 word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

# PIC18CXX2

| ADDWFC ADD WREG and Carry bit to f              |                                                                                                                                                                                                                                                                                             |                 |           |                   |  |  |  |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|-------------------|--|--|--|

| Syntax:                                         | [ label ] Al                                                                                                                                                                                                                                                                                | DWFC            | f [,d [,a | a]                |  |  |  |

| Operands:                                       | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                       | 5               |           |                   |  |  |  |

| Operation:                                      | : $(WREG) + (f) + (C) \rightarrow dest$                                                                                                                                                                                                                                                     |                 |           |                   |  |  |  |

| Status Affected: N,OV, C, DC, Z                 |                                                                                                                                                                                                                                                                                             |                 |           |                   |  |  |  |

| Encoding:                                       | 0010                                                                                                                                                                                                                                                                                        | 00da            | ffff      | ffff              |  |  |  |

| Words:                                          | Description: Add WREG, the Carry Flag and data<br>memory location 'f'. If 'd' is 0, the<br>result is placed in WREG. If 'd' is 1,<br>the result is placed in data memory<br>location 'f'. If 'a' is 0, the Access<br>Bank will be selected. If 'a' is 1, the<br>BSR will not be overridden. |                 |           |                   |  |  |  |

|                                                 | 1                                                                                                                                                                                                                                                                                           |                 |           |                   |  |  |  |

| Cycles: 1<br>Q Cycle Activity:<br>Q1 Q2 Q3 Q4   |                                                                                                                                                                                                                                                                                             |                 |           |                   |  |  |  |

| Decode                                          | Read<br>register 'f'                                                                                                                                                                                                                                                                        | Process<br>Data |           | ite to<br>ination |  |  |  |

| Example: ADDWFC REG, 0, 1<br>Before Instruction |                                                                                                                                                                                                                                                                                             |                 |           |                   |  |  |  |

| ANDLW                                                                                                       | AND liter           | AND literal with WREG             |      |                  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------|------|------------------|--|--|--|--|

| Syntax:                                                                                                     | [label] A           | NDLW                              | k    |                  |  |  |  |  |

| Operands:                                                                                                   | $0 \le k \le 25$    | $0 \le k \le 255$                 |      |                  |  |  |  |  |

| Operation:                                                                                                  | (WREG).             | (WREG) .AND. $k \rightarrow WREG$ |      |                  |  |  |  |  |

| Status Affected:                                                                                            | N,Z                 |                                   |      |                  |  |  |  |  |

| Encoding:                                                                                                   | 0000                | 1011                              | kkkk | kkkk             |  |  |  |  |

| Description: The contents of WREG are ANDec<br>with the 8-bit literal 'k'. The result is<br>placed in WREG. |                     |                                   |      |                  |  |  |  |  |

| Words:                                                                                                      | 1                   |                                   |      |                  |  |  |  |  |

| Cycles:                                                                                                     | 1                   |                                   |      |                  |  |  |  |  |

| Q Cycle Activit                                                                                             | y:                  |                                   |      |                  |  |  |  |  |

| Q1                                                                                                          | Q2                  | Q3                                |      | Q4               |  |  |  |  |

| Decode                                                                                                      | Read literal<br>'k' | Proce:<br>Data                    |      | /rite to<br>VREG |  |  |  |  |

| Example:                                                                                                    | ANDLW               | 0x5F                              |      |                  |  |  |  |  |

| Carry          | bit= | 1    |  |  |  |  |

|----------------|------|------|--|--|--|--|

| REG            | =    | 0x02 |  |  |  |  |

| WREG           | =    | 0x4D |  |  |  |  |

| ar Instruction |      |      |  |  |  |  |

# After Instruction

| Carry | bit= | 0    |

|-------|------|------|

| REG   | =    | 0x02 |

| WREG  | =    | 0x50 |

**Before Instruction** WREG = 0xA3

#### After Instruction

WREG =  $0 \times 03$

# PIC18CXX2

| SLEEP             | EEP Enter SLEEP mode                 |                              | SUBFWB       | Subtract         | Subtract f from WREG with borro |                                  |                  |  |

|-------------------|--------------------------------------|------------------------------|--------------|------------------|---------------------------------|----------------------------------|------------------|--|

| Syntax:           | [ label ]                            | SLEEP                        |              | Syntax:          | [ label ]                       | SUBFWB                           | f [,d [,a]       |  |

| Operands:         | None                                 |                              |              | Operands:        | $0 \le f \le 25$                |                                  |                  |  |

| Operation:        | $00h \rightarrow W$                  | /DT,                         |              |                  | d ∈ [0,1]                       |                                  |                  |  |

|                   |                                      | T postscaler,                |              |                  | a ∈ [0,1]                       |                                  |                  |  |

|                   | $1 \rightarrow TO, 0 \rightarrow PD$ |                              |              | Operation:       |                                 | $-(f) - (\overline{C}) -$        | → dest           |  |

|                   |                                      |                              |              | Status Affected: | N,OV, C,                        | DC, Z                            |                  |  |

| Status Affected:  | TO, PD                               |                              |              | Encoding:        | 0101                            | 01da f                           | fff fff          |  |

| Encoding:         |                                      |                              | Description: |                  | register 'f' an                 |                                  |                  |  |

| Description:      |                                      | er-down statu                |              |                  |                                 | from WREG                        |                  |  |

|                   |                                      | The time-out<br>et. Watchdog |              |                  |                                 | thod). If 'd' is<br>WREG. If 'd' |                  |  |

|                   |                                      | caler are clea               |              |                  | is stored i                     | in register 'f' (                | default). If 'a' |  |

|                   | The proc                             | essor is put i               | nto SLEEP    |                  |                                 | cess Bank w                      |                  |  |

|                   | mode wit                             | th the oscillat              | or stopped.  |                  |                                 | g the BSR va<br>bank will be s   |                  |  |

| Nords:            | 1                                    |                              |              |                  |                                 | value (defau                     |                  |  |

| Cycles:           | 1                                    |                              |              | Words:           | 1                               |                                  |                  |  |

| Q Cycle Activity  | <i>/</i> :                           |                              |              | Cycles:          | 1                               |                                  |                  |  |

| Q1                | Q2                                   | Q3                           | Q4           | Q Cycle Activity |                                 |                                  |                  |  |

| Decode            | No                                   | Process                      | Go to        | Q1               | Q2                              | Q3                               | Q4               |  |

|                   | operation                            | Data                         | sleep        | Decode           | Read                            | Process                          | Write to         |  |

| Example:          | SLEEP                                |                              |              |                  | register 'f'                    | Data                             | destination      |  |

| Before Instr      | uction                               |                              |              | Example 1:       | SUBFWB                          | REG, 1,                          | 0                |  |

| $\overline{TO} =$ | ?                                    |                              |              | Before Instru    | uction                          |                                  |                  |  |

| PD =              | ?                                    |                              |              | REG              | = 3                             |                                  |                  |  |

| After Instruc     | 1 †                                  |                              |              | WREG<br>C        | = 2<br>= 1                      |                                  |                  |  |

| $\frac{10}{PD} =$ | 0                                    |                              |              | After Instruc    |                                 |                                  |                  |  |

| If WDT cause      | es wake-up, tl                       | his bit is clea              | red.         | REG              | = FF                            |                                  |                  |  |

|                   |                                      |                              |              | WREG             | = 2                             |                                  |                  |  |

|                   |                                      |                              |              | C<br>Z           | = 0<br>= 0                      |                                  |                  |  |

|                   |                                      |                              |              | Ν                | = 1                             | ; result :                       | is negativ       |  |

|                   |                                      |                              |              | Example 2:       | SUBFWB                          | REG, 0,                          | 0                |  |

|                   |                                      |                              |              | Before Instru    | uction                          |                                  |                  |  |

|                   |                                      |                              |              | REG              | = 2                             |                                  |                  |  |

|                   |                                      |                              |              | WREG<br>C        | = 5<br>= 1                      |                                  |                  |  |

|                   |                                      |                              |              | After Instruc    | tion                            |                                  |                  |  |

|                   |                                      |                              |              | REG              | = 2                             |                                  |                  |  |

|                   |                                      |                              |              | WREG<br>C        | = 3<br>= 1                      |                                  |                  |  |

|                   |                                      |                              |              | Z                | = 1<br>= 0                      |                                  |                  |  |

|                   |                                      |                              |              | Ν                | = 0                             | ; result :                       | is positiv       |  |

|                   |                                      |                              |              | Example 3:       | SUBFWB                          | REG, 1,                          | 0                |  |

|                   |                                      |                              |              | Before Instru    |                                 |                                  |                  |  |

|                   |                                      |                              |              | REG              | = 1                             |                                  |                  |  |

|                   |                                      |                              |              | WREG<br>C        | = 2<br>= 0                      |                                  |                  |  |

|                   |                                      |                              |              | After Instruc    | tion                            |                                  |                  |  |

|                   |                                      |                              |              | REG              | = 0                             |                                  |                  |  |

|                   |                                      |                              |              |                  |                                 |                                  |                  |  |

|                   |                                      |                              |              | WREG             | = 2                             |                                  |                  |  |

|                   |                                      |                              |              | WREG<br>C<br>Z   | = 2<br>= 1<br>= 1               | ; result :                       | is zero          |  |

# 21.3 AC (Timing) Characteristics

#### 21.3.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS                | 3                               | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|----------------------------|---------------------------------|-----------|----------------------------------------|

| 2. TppS                    |                                 | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                          |                                 |           |                                        |

| F                          | Frequency                       | Т         | Time                                   |

| Lowercase le               | etters (pp) and their meanings: |           |                                        |

| рр                         |                                 |           |                                        |

| сс                         | CCP1                            | osc       | OSC1                                   |

| ck                         | CLKOUT                          | rd        | RD                                     |

| CS                         | CS                              | rw        | RD or WR                               |

| di                         | SDI                             | sc        | SCK                                    |

| do                         | SDO                             | SS        | SS                                     |

| dt                         | Data in                         | tO        | TOCKI                                  |

| io                         | I/O port                        | t1        | T1CKI                                  |

| mc                         | MCLR                            | wr        | WR                                     |

| Uppercase le               | etters and their meanings:      |           |                                        |

| S                          |                                 |           |                                        |

| F                          | Fall                            | Р         | Period                                 |

| н                          | High                            | R         | Rise                                   |

| I                          | Invalid (Hi-impedance)          | V         | Valid                                  |

| L                          | Low                             | Z         | Hi-impedance                           |

| I <sup>2</sup> C only      |                                 |           |                                        |

| AA                         | output access                   | High      | High                                   |

| BUF                        | Bus free                        | Low       | Low                                    |

| TCC:ST (I <sup>2</sup> C s | specifications only)            |           |                                        |

| CC                         |                                 |           |                                        |

| HD                         | Hold                            | SU        | Setup                                  |

| ST                         |                                 |           |                                        |

| DAT                        | DATA input hold                 | STO       | STOP condition                         |

| STA                        | START condition                 |           |                                        |

| TABLE 21-5: | PLL CLOCK TIMING SPECIFICATION ( | VDD = 4.2V - 5.5V) |

|-------------|----------------------------------|--------------------|

|             |                                  |                    |

| Param<br>No. | Symbol       | Characteristic                      | Min | Мах | Units | Conditions |

|--------------|--------------|-------------------------------------|-----|-----|-------|------------|

|              | TRC          | PLL Start-up Time (Lock Time)       |     | 2   | ms    |            |

|              | $\Delta CLK$ | CLKOUT Stability (Jitter) using PLL | -2  | +2  | %     |            |

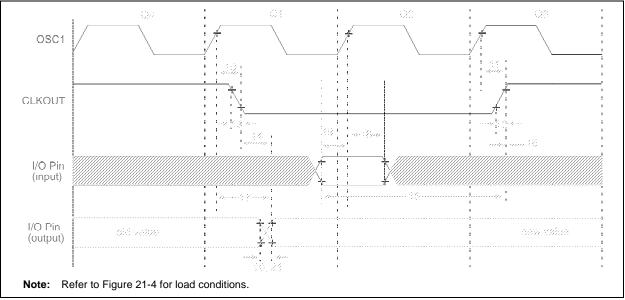

#### FIGURE 21-6: CLKOUT AND I/O TIMING

#### TABLE 21-6: CLKOUT AND I/O TIMING REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                                  |                 | Min          | Тур | Мах         | Units | Conditions |

|---------------|----------|-------------------------------------------------|-----------------|--------------|-----|-------------|-------|------------|

| 10            | TosH2ckL | OSC1↑ to CLKOUT↓                                |                 |              | 75  | 200         | ns    | (1)        |

| 11            | TosH2ckH | OSC1↑ to CLKOUT↑                                |                 | —            | 75  | 200         | ns    | (1)        |

| 12            | TckR     | CLKOUT rise time                                |                 | _            | 35  | 100         | ns    | (1)        |

| 13            | TckF     | CLKOUT fall time                                |                 | _            | 35  | 100         | ns    | (1)        |

| 14            | TckL2ioV | CLKOUT ↓ to Port out v                          | alid            | _            | _   | 0.5TCY + 20 | ns    | (1)        |

| 15            | TioV2ckH | Port in valid before CLK                        | OUT ↑           | 0.25Tcy + 25 | _   |             | ns    | (1)        |

| 16            | TckH2iol | Port in hold after CLKOUT ↑                     |                 | 0            |     |             | ns    | (1)        |

| 17            | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid  |                 | _            | 50  | 150         | ns    |            |

| 18            | TosH2iol | OSC1↑ (Q2 cycle) to                             | PIC18CXXX       | 100          | _   |             | ns    |            |

| 18A           |          | Port input invalid<br>(I/O in hold time)        | PIC18LCXXX      | 200          | —   | _           | ns    |            |

| 19            | TioV2osH | Port input valid to OSC1<br>(I/O in setup time) | 1               | 0            | —   | —           | ns    |            |

| 20            | TioR     | Port output rise time                           | PIC18CXXX       | _            | 12  | 25          | ns    |            |

| 20A           |          |                                                 | PIC18LCXXX      |              | _   | 50          | ns    |            |

| 21            | TioF     | Port output fall time                           | PIC18CXXX       |              | 12  | 25          | ns    |            |

| 21A           |          |                                                 | PIC18LCXXX      | _            | _   | 50          | ns    |            |

| 22††          | TINP     | INT pin high or low time                        |                 | Тсү          | _   |             | ns    |            |

| 23††          | Trbp     | RB7:RB4 change INT h                            | igh or low time | Тсү          | _   |             | ns    |            |

| 24††          | TRCP     | RC7:RC4 change INT h                            | igh or low time | 20           |     |             | ns    |            |

these parameters are asynchronous events not related to any internal clock edges.

**Note 1:** Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

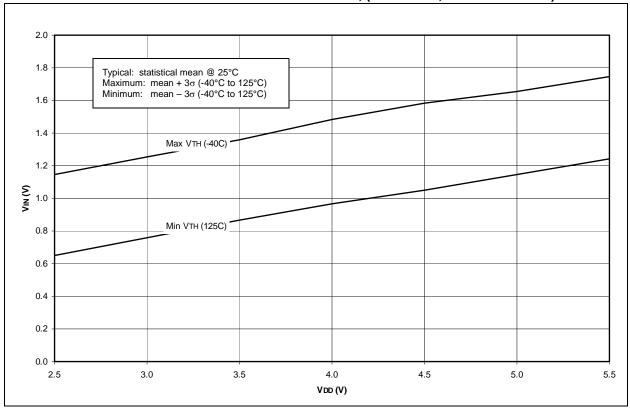

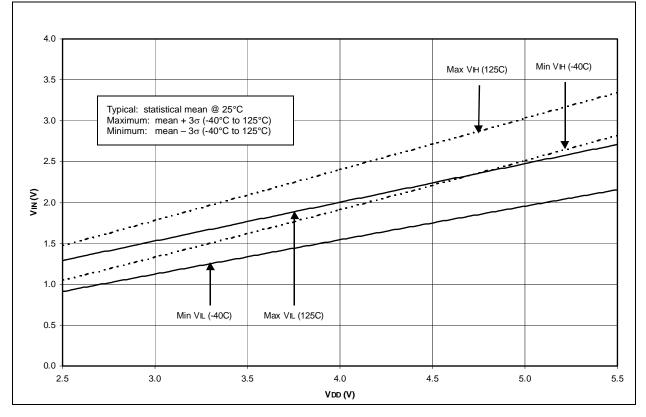

FIGURE 22-25: MINIMUM AND MAXIMUM VIN vs. VDD, (TTL INPUT, -40°C TO +125°C)

© 1999-2013 Microchip Technology Inc.

# 23.0 PACKAGING INFORMATION

### 23.1 Package Marking Information

#### 28-Lead PDIP (Skinny DIP)

| Example | ample          |  |  |

|---------|----------------|--|--|

|         | PIC18C242-I/SP |  |  |

**1**0117017

| 28- | Lead | SOIC |  |

|-----|------|------|--|

|     |      |      |  |

| Example |

|---------|

|---------|

| Leger | ld: XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>*                                                                                                                                                                  | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |