Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                                |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb202-e-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | Pin Num                         | per/Grid | Locator            |     |                      |                                             |

|--------------|---------------------------------|----------|--------------------|-----|----------------------|---------------------------------------------|

| Pin Function | 28-Pin<br>SPDIP/SOIC/<br>SSOP   |          | 44-Pin<br>TQFP/QFN |     |                      | Description                                 |

| RP0          | 4                               | 1        | 21                 | I/O | ST                   | Remappable Peripheral (input or output).    |

| RP1          | 5                               | 2        | 22                 | I/O | ST                   |                                             |

| RP2          | 6                               | 3        | 23                 | I/O | ST                   |                                             |

| RP3          | 7                               | 4        | 24                 | I/O | ST                   |                                             |

| RP5          | 2                               | 27       | 19                 | I/O | ST                   |                                             |

| RP6          | 3,15                            | 28       | 20                 | I/O | ST                   | 1                                           |

| RP7          | 16                              | 13       | 43                 | I/O | ST                   |                                             |

| RP8          | 17                              | 14       | 44                 | I/O | ST                   | 1                                           |

| RP9          | 18                              | 15       | 1                  | I/O | ST                   |                                             |

| RP10         | 21                              | 18       | 8                  | I/O | ST                   |                                             |

| RP11         | 22                              | 19       | 9                  | I/O | ST                   |                                             |

| RP13         | 24                              | 21       | 11                 | I/O | ST                   |                                             |

| RP14         | 25                              | 22       | 14                 | I/O | ST                   |                                             |

| RP15         | 26                              | 23       | 15                 | I/O | ST                   |                                             |

| RP16         | _                               |          | 25                 | I/O | ST                   |                                             |

| RP17         | _                               |          | 26                 | I/O | ST                   |                                             |

| RP18         | _                               |          | 27                 | I/O | ST                   |                                             |

| RP19         | _                               | —        | 36                 | I/O | ST                   |                                             |

| RP20         | _                               |          | 37                 | I/O | ST                   |                                             |

| RP21         | _                               |          | 38                 | I/O | ST                   |                                             |

| RP22         | _                               |          | 2                  | I/O | ST                   |                                             |

| RP23         | _                               |          | 3                  | I/O | ST                   |                                             |

| RP24         |                                 |          | 4                  | I/O | ST                   | 1                                           |

| RP25         |                                 | —        | 5                  | I/O | ST                   |                                             |

| RPI4         | 11                              | 8        | 33                 | Ι   | ST                   | Remappable Peripheral (input).              |

| RTCC         | 25                              | 22       | 14                 | 0   | —                    | Real-Time Clock Alarm/Seconds Pulse Output. |

| SCL1         | 17                              | 14       | 44                 | I/O | l <sup>2</sup> C     | I2C1 Synchronous Serial Clock Input/Output. |

| SCL2         | 7                               | 4        | 24                 | I/O | l <sup>2</sup> C     | I2C2 Synchronous Serial Clock Input/Output. |

| SCLKI        | 12                              | 9        | 34                 | Ι   | —                    | Secondary Oscillator Digital Clock Input.   |

| SDA1         | 18                              | 15       | 1                  | I/O | l <sup>2</sup> C     | I2C1 Data Input/Output.                     |

| SDA2         | 6                               | 3        | 23                 | I/O | l <sup>2</sup> C     | I2C2 Data Input/Output.                     |

| SOSCI        | 11                              | 8        | 33                 | Ι   | ANA                  | Secondary Oscillator/Timer1 Clock Input.    |

| SOSCO        | 12                              | 9        | 34                 | 0   | ANA                  | Secondary Oscillator/Timer1 Clock Output.   |

| ANA =        | Schmitt Trigger<br>Analog input | -        |                    |     | = TTL co<br>= Output | pompatible input I = Input<br>P = Power     |

#### **TABLE 1-3**: PIC24FJ128GB204 FAMILY PINOUT DESCRIPTION (CONTINUED)

$I^2C = ST$  with  $I^2C^{TM}$  or SMBus levels

NOTES:

| U-0          | R/W-0                              | R/W-0                                                                                                                           | R/W-0            | R/W-0             | R/W-0           | U-0             | R/W-0    |  |  |  |  |

|--------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-----------------|-----------------|----------|--|--|--|--|

| _            | RTCIF                              | DMA5IF                                                                                                                          | <b>SPI3RXIF</b>  | SPI2RXIF          | SPI1RXIF        | _               | KEYSTRIF |  |  |  |  |

| bit 15       |                                    | ł                                                                                                                               |                  |                   |                 |                 | bit      |  |  |  |  |

|              |                                    |                                                                                                                                 |                  |                   |                 |                 |          |  |  |  |  |

| R/W-0        | R/W-0                              | R/W-0                                                                                                                           | U-0              | U-0               | R/W-0           | R/W-0           | U-0      |  |  |  |  |

| CRYDNIF      | INT4IF                             | INT3IF                                                                                                                          |                  |                   | MI2C2IF         | SI2C2IF         |          |  |  |  |  |

| bit 7        |                                    |                                                                                                                                 |                  |                   |                 |                 | bit      |  |  |  |  |

| Legend:      |                                    |                                                                                                                                 |                  |                   |                 |                 |          |  |  |  |  |

| R = Readab   | ole bit                            | W = Writable                                                                                                                    | bit              | U = Unimplen      | nented bit, rea | d as '0'        |          |  |  |  |  |

| -n = Value a |                                    | '1' = Bit is set                                                                                                                |                  | '0' = Bit is clea |                 | x = Bit is unkr | nwn      |  |  |  |  |

|              |                                    | i Ditio oot                                                                                                                     |                  |                   |                 |                 |          |  |  |  |  |

| bit 15       | Unimpleme                          | nted: Read as '                                                                                                                 | 0'               |                   |                 |                 |          |  |  |  |  |

| bit 14       | RTCIF: Real                        | -Time Clock and                                                                                                                 | l Calendar Inter | rupt Flag Statu   | s bit           |                 |          |  |  |  |  |

|              | 1 = Interrupt                      | request has occ                                                                                                                 | curred           |                   |                 |                 |          |  |  |  |  |

|              | 0 = Interrupt                      | request has not                                                                                                                 | occurred         |                   |                 |                 |          |  |  |  |  |

| bit 13       | DMA5IF: DM                         | A5IF: DMA Channel 5 Interrupt Flag Status bit                                                                                   |                  |                   |                 |                 |          |  |  |  |  |

|              | 1 = Interrupt request has occurred |                                                                                                                                 |                  |                   |                 |                 |          |  |  |  |  |

|              | •                                  | request has not                                                                                                                 |                  |                   |                 |                 |          |  |  |  |  |

| bit 12       |                                    | SPI3RXIF: SPI3 Receive Interrupt Flag Status bit 1 = Interrupt request has occurred                                             |                  |                   |                 |                 |          |  |  |  |  |

|              |                                    | request has occ<br>request has not                                                                                              |                  |                   |                 |                 |          |  |  |  |  |

| bit 11       | -                                  | -                                                                                                                               |                  | us bit            |                 |                 |          |  |  |  |  |

|              |                                    | SPI2 Receive Interrupt Flag Status bit<br>ot request has occurred                                                               |                  |                   |                 |                 |          |  |  |  |  |

|              | •                                  | request has not                                                                                                                 |                  |                   |                 |                 |          |  |  |  |  |

| bit 10       | SPI1RXIF: S                        | SPI1RXIF: SPI1 Receive Interrupt Flag Status bit                                                                                |                  |                   |                 |                 |          |  |  |  |  |

|              |                                    | request has occ                                                                                                                 |                  |                   |                 |                 |          |  |  |  |  |

|              | •                                  | request has not                                                                                                                 |                  |                   |                 |                 |          |  |  |  |  |

| bit 9        | Unimpleme                          | nted: Read as '                                                                                                                 | 0'               |                   |                 |                 |          |  |  |  |  |

| bit 8        |                                    | Cryptographic K                                                                                                                 |                  | am Done Interru   | upt Flag Status | bit             |          |  |  |  |  |

|              | •                                  | 1 = Interrupt request has occurred                                                                                              |                  |                   |                 |                 |          |  |  |  |  |

|              | -                                  | <ul> <li>Interrupt request has not occurred</li> <li>CRYDNIF: Cryptographic Operation Done Interrupt Flag Status bit</li> </ul> |                  |                   |                 |                 |          |  |  |  |  |

| bit 7        |                                    |                                                                                                                                 |                  | nterrupt Flag St  | atus bit        |                 |          |  |  |  |  |

|              |                                    | request has occ<br>request has not                                                                                              |                  |                   |                 |                 |          |  |  |  |  |

|              |                                    | request has hot                                                                                                                 | occurred         |                   |                 |                 |          |  |  |  |  |

| hit 6        | INTAIL Even                        | INT4IF: External Interrupt 4 Flag Status bit                                                                                    |                  |                   |                 |                 |          |  |  |  |  |

| bit 6        |                                    | ernal Interrupt 4<br>request has occ                                                                                            | •                |                   |                 |                 |          |  |  |  |  |

### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| R/W-0         | R/W-0         | R/W-0                                             | R/W-0                     | R/W-0             | R/W-0           | R/W-0             | R/W-0       |

|---------------|---------------|---------------------------------------------------|---------------------------|-------------------|-----------------|-------------------|-------------|

| U2TXIE        | U2RXIE        | INT2IE <sup>(1)</sup>                             | T5IE                      | T4IE              | OC4IE           | OC3IE             | DMA2IE      |

| bit 15        | 1             |                                                   |                           |                   |                 | 1                 | bit 8       |

|               |               |                                                   |                           |                   |                 |                   |             |

| U-0           | U-0           | U-0                                               | R/W-0                     | R/W-0             | R/W-0           | R/W-0             | R/W-0       |

| _             | —             | —                                                 | INT1IE <sup>(1)</sup>     | CNIE              | CMIE            | MI2C1IE           | SI2C1IE     |

| bit 7         |               |                                                   |                           |                   |                 |                   | bit 0       |

| Legend:       |               |                                                   |                           |                   |                 |                   |             |

| R = Readabl   | e hit         | W = Writable                                      | hit                       | II = Unimplen     | nented bit, rea | d as '0'          |             |

| -n = Value at |               | '1' = Bit is set                                  |                           | '0' = Bit is clea |                 | x = Bit is unkn   | own         |

|               |               |                                                   |                           |                   | uicu            |                   | lowin       |

| bit 15        | U2TXIE: UAF   | RT2 Transmitter                                   | Interrupt Enal            | ble bit           |                 |                   |             |

|               |               | request is enab                                   | -                         |                   |                 |                   |             |

|               | 0 = Interrupt | request is not e                                  | nabled                    |                   |                 |                   |             |

| bit 14        |               | RT2 Receiver Ir                                   | •                         | e bit             |                 |                   |             |

|               |               | request is enab<br>request is not e               |                           |                   |                 |                   |             |

| bit 13        | •             | rnal Interrupt 2                                  |                           |                   |                 |                   |             |

| DIL 15        |               | request is enab                                   |                           |                   |                 |                   |             |

|               |               | request is not e                                  |                           |                   |                 |                   |             |

| bit 12        | T5IE: Timer5  | Interrupt Enab                                    | le bit                    |                   |                 |                   |             |

|               |               | request is enab                                   |                           |                   |                 |                   |             |

|               | -             | request is not e                                  |                           |                   |                 |                   |             |

| bit 11        |               | Interrupt Enab                                    |                           |                   |                 |                   |             |

|               |               | request is enab<br>request is not e               |                           |                   |                 |                   |             |

| bit 10        | •             | ut Compare Ch                                     |                           | ot Enable bit     |                 |                   |             |

|               | =             | request is enab                                   |                           | p                 |                 |                   |             |

|               |               | request is not e                                  |                           |                   |                 |                   |             |

| bit 9         | OC3IE: Outp   | ut Compare Ch                                     | annel 3 Interru           | pt Enable bit     |                 |                   |             |

|               |               | request is enab                                   |                           |                   |                 |                   |             |

| <b>h</b> # 0  | •             | request is not e                                  |                           | L :4              |                 |                   |             |

| bit 8         |               | IA Channel 2 In<br>request is enab                | -                         | DI                |                 |                   |             |

|               |               | request is enab                                   |                           |                   |                 |                   |             |

| bit 7-5       |               | ted: Read as '                                    |                           |                   |                 |                   |             |

| bit 4         | INT1IE: Exte  | rnal Interrupt 1                                  | Enable bit <sup>(1)</sup> |                   |                 |                   |             |

|               |               | request is enab<br>request is not e               |                           |                   |                 |                   |             |

| bit 3         | CNIE: Input ( | Change Notifica                                   | tion Interrupt E          | Enable bit        |                 |                   |             |

|               |               | request is enab<br>request is not e               |                           |                   |                 |                   |             |

| bit 2         | CMIE: Comp    | arator Interrupt                                  | Enable bit                |                   |                 |                   |             |

|               |               | request is enab                                   |                           |                   |                 |                   |             |

|               | 0 = Interrupt | request is not e                                  | nabled                    |                   |                 |                   |             |

|               |               | errupt is enabled<br>ormation, see <mark>S</mark> |                           |                   |                 | l to an available | RPn or RPIn |

#### REGISTER 8-14: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

© 2013-2015 Microchip Technology Inc.

### REGISTER 8-28: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

| U-0           | R/W-1                                                                                                                             | R/W-0              | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|

| _             | U2TXIP2                                                                                                                           | U2TXIP1            | U2TXIP0          | _                | U2RXIP2          | U2RXIP1         | U2RXIP0 |  |  |  |

| bit 15        |                                                                                                                                   |                    |                  |                  |                  |                 | bit     |  |  |  |

|               |                                                                                                                                   |                    |                  |                  |                  |                 |         |  |  |  |

| U-0           | R/W-1                                                                                                                             | R/W-0              | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |

| —             | INT2IP2                                                                                                                           | INT2IP1            | INT2IP0          | —                | T5IP2            | T5IP1           | T5IP0   |  |  |  |

| bit 7         |                                                                                                                                   |                    |                  |                  |                  |                 | bit     |  |  |  |

| Legend:       |                                                                                                                                   |                    |                  |                  |                  |                 |         |  |  |  |

| R = Readabl   | e hit                                                                                                                             | W = Writable       | hit              | II = Unimplen    | nented bit, read | 1 as '0'        |         |  |  |  |

| -n = Value at |                                                                                                                                   | '1' = Bit is set   |                  | '0' = Bit is cle |                  | x = Bit is unkr | nown    |  |  |  |

|               |                                                                                                                                   |                    |                  | 0 2000 000       |                  |                 |         |  |  |  |

| bit 15        | Unimplemen                                                                                                                        | ted: Read as '     | ) <b>'</b>       |                  |                  |                 |         |  |  |  |

| bit 14-12     | -                                                                                                                                 |                    |                  | t Priority bits  |                  |                 |         |  |  |  |

|               | <b>U2TXIP&lt;2:0&gt;:</b> UART2 Transmitter Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                    |                  |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                 |                    |                  |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                 |                    |                  |                  |                  |                 |         |  |  |  |

|               | •<br>001 = Interrupt is Priority 1                                                                                                |                    |                  |                  |                  |                 |         |  |  |  |

|               | 000 = Interru                                                                                                                     | pt source is dis   | abled            |                  |                  |                 |         |  |  |  |

| bit 11        | Unimplemen                                                                                                                        | ted: Read as '     | o <b>'</b>       |                  |                  |                 |         |  |  |  |

| bit 10-8      | U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits                                                                               |                    |                  |                  |                  |                 |         |  |  |  |

|               | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                        |                    |                  |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                 |                    |                  |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                 |                    |                  |                  |                  |                 |         |  |  |  |

|               | •<br>001 = Interrupt is Priority 1                                                                                                |                    |                  |                  |                  |                 |         |  |  |  |

|               | 000 = Interru                                                                                                                     | pt source is dis   | abled            |                  |                  |                 |         |  |  |  |

| bit 7         | Unimplemen                                                                                                                        | ted: Read as '     | o'               |                  |                  |                 |         |  |  |  |

| bit 6-4       | INT2IP<2:0>:                                                                                                                      | External Interr    | upt 2 Priority b | oits             |                  |                 |         |  |  |  |

|               | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                        |                    |                  |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                 |                    |                  |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                 |                    |                  |                  |                  |                 |         |  |  |  |

|               | 001 = Interru                                                                                                                     | pt is Priority 1   |                  |                  |                  |                 |         |  |  |  |

|               |                                                                                                                                   | pt source is dis   | abled            |                  |                  |                 |         |  |  |  |

| bit 3         | Unimplemen                                                                                                                        | ted: Read as '     | כ'               |                  |                  |                 |         |  |  |  |

| bit 2-0       | T5IP<2:0>: Timer5 Interrupt Priority bits                                                                                         |                    |                  |                  |                  |                 |         |  |  |  |

|               | 111 = Interru                                                                                                                     | pt is Priority 7 ( | highest priority | interrupt)       |                  |                 |         |  |  |  |

|               | •                                                                                                                                 |                    |                  |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                 |                    |                  |                  |                  |                 |         |  |  |  |

|               | -                                                                                                                                 |                    |                  |                  |                  |                 |         |  |  |  |

|               | 001 = Interru                                                                                                                     | pt is Priority 1   |                  |                  |                  |                 |         |  |  |  |

# 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers:

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources. The CLKDIV register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The OSCTUN register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 1.5\%$ . It also controls the FRC self-tuning features, described in Section 9.5 "FRC Self-Tuning".

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| —      | COSC2 | COSC1 | COSC0 | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/SO-0  | R/W-0                 | R-0 <sup>(3)</sup> | U-0 | R/CO-0 | R/W-0  | R/W-0  | R/W-0 |

|---------|-----------------------|--------------------|-----|--------|--------|--------|-------|

| CLKLOCK | IOLOCK <sup>(2)</sup> | LOCK               | —   | CF     | POSCEN | SOSCEN | OSWEN |

| bit 7   |                       |                    |     |        |        |        | bit 0 |

| Legend:           | CO = Clearable Only bit | SO = Settable Only bit |                    |

|-------------------|-------------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared   | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

- bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits

- 111 = Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = Reserved

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

### bit 11 Unimplemented: Read as '0'

#### bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(1)</sup>

- 111 = Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = Reserved

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

- Note 1: Reset values for these bits are determined by the FNOSCx Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1', once the IOLOCK bit is set, it cannot be cleared.

- 3: This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

### 11.1.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

### 11.1.2 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, each port pin can also be individually configured for either a digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V), on any desired digital only pins, by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

# 11.2 Configuring Analog Port Pins (ANSx)

The ANSx and TRISx registers control the operation of the pins with analog function. Each port pin with analog function is associated with one of the ANSx bits (see Register 11-1 through Register 11-3), which decides if the pin function should be analog or digital. Refer to Table 11-1 for detailed behavior of the pin for different ANSx and TRISx bit settings.

When reading the PORTx register, all pins configured as analog input channels will read as cleared (a low level).

#### 11.2.1 ANALOG INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Most input pins are able to handle DC voltages of up to 5.5V, a level typical for digital logic circuits. However, several pins can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should always be avoided.

Table 11-2 summarizes the different voltage tolerances. For more information, refer to **Section 33.0 "Electrical Characteristics"** for more details.

| Pin Function   | ANSx Setting | TRISx Setting | Comments                                                                                                                                   |

|----------------|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Input   | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Analog Output  | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Digital Input  | 0            | 1             | Firmware must wait at least one instruction cycle<br>after configuring a pin as a digital input before a valid<br>input value can be read. |

| Digital Output | 0            | 0             | Make sure to disable the analog output function on the pin if any is present.                                                              |

### TABLE 11-1: CONFIGURING ANALOG/DIGITAL FUNCTION OF AN I/O PIN

### TABLE 11-2: INPUT VOLTAGE LEVELS FOR PORT OR PIN TOLERATED DESCRIPTION INPUT

| Port or Pin                  | Tolerated Input | Description                                                          |  |  |

|------------------------------|-----------------|----------------------------------------------------------------------|--|--|

| PORTA<10:7,4> <sup>(1)</sup> |                 |                                                                      |  |  |

| PORTB<11:10,8:4>             | 5.5V            | Tolerates input levels above VDD; useful<br>for most standard logic. |  |  |

| PORTC<9:3> <sup>(1)</sup>    |                 |                                                                      |  |  |

| PORTA<3:0>                   |                 |                                                                      |  |  |

| PORTB<15:13,9,3:0>           | Vdd             | Only VDD input levels are tolerated.                                 |  |  |

| PORTC<2:0> <sup>(1)</sup>    |                 |                                                                      |  |  |

**Note 1:** Not all of these pins are implemented in 28-pin devices. Refer to **Section 1.0 "Device Overview**" for a complete description of port pin implementation.

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| _      | —   | RP9R5 | RP9R4 | RP9R3 | RP9R2 | RP9R1 | RP9R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP8R5 | RP8R4 | RP8R3 | RP8R2 | RP8R1 | RP8R0 |

| bit 7  | ·   |       | •     |       | •     | •     | bit 0 |

|        |     |       |       |       |       |       |       |

#### REGISTER 11-27: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP9R<5:0>: RP9 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP9 (see Table 11-4 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | RP8R<5:0>: RP8 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP8 (see Table 11-4 for peripheral function numbers). |

# REGISTER 11-28: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      |     | RP11R5 | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| _      |     | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7  | •   |        | •      |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP11R<5:0>:** RP11 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP11 (see Table 11-4 for peripheral function numbers).

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **RP10R<5:0>:** RP10 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP10 (see Table 11-4 for peripheral function numbers).

# REGISTER 11-35: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12<sup>(1)</sup>

| U-0           | U-0                                                                                                   | R/W-0            | R/W-0         | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |

|---------------|-------------------------------------------------------------------------------------------------------|------------------|---------------|------------------------------------|--------|--------------------|--------|

| —             | —                                                                                                     | RP25R5           | RP25R4        | RP25R3                             | RP25R2 | RP25R1             | RP25R0 |

| bit 15        |                                                                                                       |                  |               | -<br>-                             |        |                    | bit 8  |

|               |                                                                                                       |                  |               |                                    |        |                    |        |

| U-0           | U-0                                                                                                   | R/W-0            | R/W-0         | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |

| —             | —                                                                                                     | RP24R5           | RP24R4        | RP24R3                             | RP24R2 | RP24R1             | RP24R0 |

| bit 7         |                                                                                                       | •                |               |                                    | •      |                    | bit 0  |

|               |                                                                                                       |                  |               |                                    |        |                    |        |

| Legend:       |                                                                                                       |                  |               |                                    |        |                    |        |

| R = Readable  | e bit                                                                                                 | W = Writable bit |               | U = Unimplemented bit, read as '0' |        |                    |        |

| -n = Value at | POR                                                                                                   | '1' = Bit is set |               | '0' = Bit is cleared               |        | x = Bit is unknown |        |

|               |                                                                                                       |                  |               |                                    |        |                    |        |

| bit 15-14     | Unimplemen                                                                                            | ted: Read as '   | )'            |                                    |        |                    |        |

| bit 13-8      | RP25R<5:0>:                                                                                           | RP25 Output      | Pin Mapping b | its                                |        |                    |        |

|               | Peripheral Output Number n is assigned to pin, RP25 (see Table 11-4 for peripheral function numbers). |                  |               |                                    |        |                    |        |

| bit 7-6       | Unimplemen                                                                                            | ted: Read as '   | )'            |                                    |        |                    |        |

| bit 5-0       | RP24R<5:0>: RP24 Output Pin Mapping bits                                                              |                  |               |                                    |        |                    |        |

5-0 **RP24R<5:0>:** RP24 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP24 (see Table 11-4 for peripheral function numbers).

Note 1: These pins are not available in 28-pin devices.

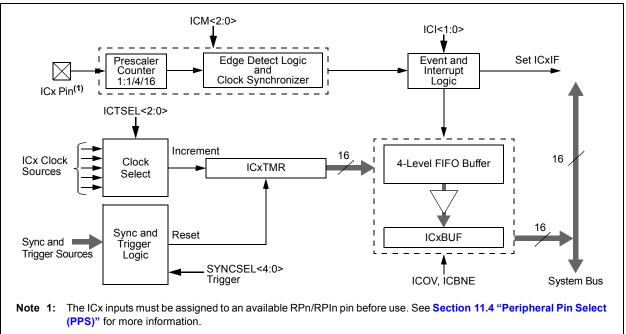

# 14.0 INPUT CAPTURE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Input Capture with Dedicated Timer" (DS39722). The information in this data sheet supersedes the information in the FRM.

Devices in the PIC24FJ128GB204 family contain six independent input capture modules. Each of the modules offers a wide range of configuration and operating options for capturing external pulse events and generating interrupts.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 30 user-selectable sync/trigger sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to 6 clock sources available for each module, driving a separate, internal 16-bit counter

The module is controlled through two registers: ICxCON1 (Register 14-1) and ICxCON2 (Register 14-2). A general block diagram of the module is shown in Figure 14-1.

# 14.1 General Operating Modes

#### 14.1.1 SYNCHRONOUS AND TRIGGER MODES

When the input capture module operates in a Free-Running mode, the internal 16-bit counter, ICxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow. Its period is synchronized to the selected external clock source. When a capture event occurs, the current 16-bit value of the internal counter is written to the FIFO buffer.

In Synchronous mode, the module begins capturing events on the ICx pin as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the internal counter to run.

Standard, free-running operation is selected by setting the SYNCSELx bits (ICxCON2<4:0>) to '00000' and clearing the ICTRIG bit (ICxCON2<7>). Synchronous and Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The ICTRIG bit selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the sync/trigger source.

When the SYNCSELx bits are set to '00000' and ICTRIG is set, the module operates in Software Trigger mode. In this case, capture operations are started by manually setting the TRIGSTAT bit (ICxCON2<6>).

### FIGURE 14-1: INPUT CAPTURE x BLOCK DIAGRAM

#### 19.7.1 USB OTG MODULE CONTROL REGISTERS

# REGISTER 19-3: U10TGSTAT: USB OTG STATUS REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   |     | -   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| R-0, HSC | U-0 | R-0, HSC | U-0 | R-0, HSC | R-0, HSC | U-0 | R-0, HSC |

|----------|-----|----------|-----|----------|----------|-----|----------|

| ID       | —   | LSTATE   | —   | SESVD    | SESEND   | —   | VBUSVD   |

| bit 7    |     |          |     |          |          |     | bit 0    |

| Legend:           | U = Unimplemented bit, read as '0' |                           |                    |

|-------------------|------------------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit                   | HSC = Hardware Settable/C | learable bit       |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                   |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | ID: ID Pin State Indicator bit                                                                                                                                                               |

|          | <ul> <li>1 = No plug is attached or a Type B cable has been plugged into the USB receptacle</li> <li>0 = A Type A plug has been plugged into the USB receptacle</li> </ul>                   |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                   |

| bit 5    | LSTATE: Line State Stable Indicator bit                                                                                                                                                      |

|          | <ul> <li>1 = The USB line state (as defined by SE0 and JSTATE) has been stable for the previous 1 ms</li> <li>0 = The USB line state has not been stable for the previous 1 ms</li> </ul>    |

| bit 4    | Unimplemented: Read as '0'                                                                                                                                                                   |

| bit 3    | SESVD: Session Valid Indicator bit                                                                                                                                                           |

|          | <ul> <li>1 = The VBUS voltage is above VA_SESS_VLD (as defined in the "USB 2.0 Specification") on the A or<br/>B-device</li> </ul>                                                           |

|          | 0 = The VBUS voltage is below VA_SESS_VLD on the A or B-device                                                                                                                               |

| bit 2    | SESEND: B Session End Indicator bit                                                                                                                                                          |

|          | <ul> <li>1 = The VBUS voltage is below VB_SESS_END (as defined in the "USB 2.0 Specification") on the B-device</li> <li>0 = The VBUS voltage is above VB_SESS_END on the B-device</li> </ul> |

| bit 1    | Unimplemented: Read as '0'                                                                                                                                                                   |

| bit 0    | VBUSVD: A VBUS Valid Indicator bit                                                                                                                                                           |

|          | <ul> <li>1 = The VBUS voltage is above VA_VBUS_VLD (as defined in the "USB 2.0 Specification") on the A-device</li> <li>0 = The VBUS voltage is below VA_VBUS_VLD on the A-device</li> </ul> |

|          |                                                                                                                                                                                              |

#### REGISTER 21-7: PMCSxMD: EPMP CHIP SELECT x MODE REGISTER (CONTINUED)

- bit 1-0 **DWAITE<1:0>:** Chip Select x Data Hold After Read/Write Strobe Wait State bits

- For Write Operations:11 = Wait of 3¼ TcY10 = Wait of 2¼ TcY01 = Wait of 1¼ TcY00 = Wait of ¼ TcYFor Read Operations:11 = Wait of 3 TcY10 = Wait of 2 TcY01 = Wait of 1 TcY00 = Wait of 0 TcY

#### REGISTER 21-8: PMSTAT: EPMP STATUS REGISTER (SLAVE MODE ONLY)

| R-0, HSC | R/W-0, HS | U-0 | U-0 | R-0, HSC            | R-0, HSC            | R-0, HSC            | R-0, HSC            |

|----------|-----------|-----|-----|---------------------|---------------------|---------------------|---------------------|

| IBF      | IBOV      | —   | —   | IB3F <sup>(1)</sup> | IB2F <sup>(1)</sup> | IB1F <sup>(1)</sup> | IB0F <sup>(1)</sup> |

| bit 15   |           |     |     |                     |                     |                     | bit 8               |

| R-1, HSC | R/W-0, HS | U-0 | U-0 | R-1, HSC | R-1, HSC | R-1, HSC | R-1, HSC |

|----------|-----------|-----|-----|----------|----------|----------|----------|

| OBE      | OBUF      | —   | —   | OB3E     | OB2E     | OB1E     | OB0E     |

| bit 7    |           |     |     |          |          |          | bit 0    |

| Legend:           | HS = Hardware Settable bit | HSC = Hardware Settable/C   | Clearable bit      |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15    | IBF: Input Buffer Full Status bit                                                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>1 = All writable Input Buffer registers are full</li> <li>0 = Some or all of the writable Input Buffer registers are empty</li> </ul>                           |

| bit 14    | IBOV: Input Buffer Overflow Status bit                                                                                                                                   |

|           | <ul> <li>1 = A write attempt to a full Input Buffer register occurred (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul>                         |

| bit 13-12 | Unimplemented: Read as '0'                                                                                                                                               |

| bit 11-8  | IB3F:IB0F: Input Buffer x Status Full bits <sup>(1)</sup>                                                                                                                |

|           | <ul> <li>1 = Input buffer contains unread data (reading the buffer will clear this bit)</li> <li>0 = Input buffer does not contain unread data</li> </ul>                |

| bit 7     | OBE: Output Buffer Empty Status bit                                                                                                                                      |

|           | <ul> <li>1 = All readable Output Buffer registers are empty</li> <li>0 = Some or all of the readable Output Buffer registers are full</li> </ul>                         |

| bit 6     | OBUF: Output Buffer Underflow Status bit                                                                                                                                 |

|           | <ul> <li>1 = A read occurred from an empty Output Buffer register (must be cleared in software)</li> <li>0 = No underflow occurred</li> </ul>                            |

| bit 5-4   | Unimplemented: Read as '0'                                                                                                                                               |

| bit 3-0   | <b>OB3E:OB0E:</b> Output Buffer x Status Empty bits                                                                                                                      |

|           | <ul> <li>1 = Output Buffer register is empty (writing data to the buffer will clear this bit)</li> <li>0 = Output Buffer register contains untransmitted data</li> </ul> |

| Note 1:   | Even though an individual bit represents the byte in the buffer, the bits corresponding to the word (Byte 0 and 1, or Byte 2 and 3) get cleared, even on byte reading.   |

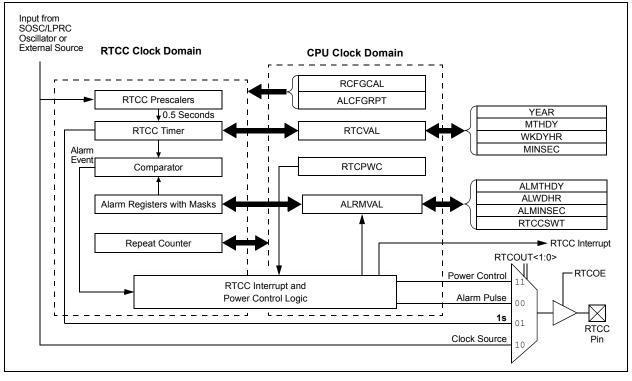

# 22.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "dsPIC33/PIC24 Family Reference Manual", "RTCC with External Power Control" (DS39745).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- Operates in Deep Sleep mode

- Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- · Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- Alarm repeat with decrementing counter

- Alarm with indefinite repeat chime

- · Year 2000 to 2099 leap year correction

### FIGURE 22-1: RTCC BLOCK DIAGRAM

- · BCD format for smaller software overhead

- Optimized for long-term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

- Optimized for long-term battery operation

- Fractional second synchronization

- Calibration to within ±2.64 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Ability to periodically wake up external devices without CPU intervention (external power control)

- Power control output for external circuit control

- · Calibration takes effect every 15 seconds

- Runs from any one of the following:

- External Real-Time Clock (RTC) of 32.768 kHz

- Internal 31.25 kHz LPRC clock

- 50 Hz or 60 Hz external input

### 22.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator, LPRC internal oscillator or an external 50 Hz/60 Hz power line input as the clock reference for the RTCC module. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

| R/W-0         | R/W-0                                                                                                                                                                                | R/W-0                                 | R/W-0           | U-0                 | U-0              | R/W-0            | R/W-0            |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|---------------------|------------------|------------------|------------------|--|--|--|

| ASEN          | LPEN                                                                                                                                                                                 | CTMREQ                                | BGREQ           |                     |                  | ASINT1           | ASINT0           |  |  |  |

| bit 15        |                                                                                                                                                                                      |                                       |                 |                     |                  |                  | bit 8            |  |  |  |

| U-0           | U-0                                                                                                                                                                                  | U-0                                   | U-0             | R/W-0               | R/W-0            | R/W-0            | R/W-0            |  |  |  |

| 0-0           | 0-0                                                                                                                                                                                  | 0-0                                   | 0-0             | WM1                 | WM0              | CM1              | CM0              |  |  |  |

| <br>bit 7     |                                                                                                                                                                                      |                                       |                 | VVIVII              | VIVIO            | CIVIT            | bit 0            |  |  |  |

|               |                                                                                                                                                                                      |                                       |                 |                     |                  |                  |                  |  |  |  |

| Legend:       |                                                                                                                                                                                      |                                       |                 |                     |                  |                  |                  |  |  |  |

| R = Readabl   | e bit                                                                                                                                                                                | W = Writable                          | oit             | U = Unimplem        | ented bit, rea   | d as '0'         |                  |  |  |  |

| -n = Value at | POR                                                                                                                                                                                  | '1' = Bit is set                      |                 | '0' = Bit is clea   | ared             | x = Bit is unkr  | nown             |  |  |  |

| bit 15        | ASEN: Auto-S                                                                                                                                                                         | Scan Enable bi                        | :               |                     |                  |                  |                  |  |  |  |

|               | 1 = Auto-scan<br>0 = Auto-scan                                                                                                                                                       |                                       |                 |                     |                  |                  |                  |  |  |  |

| oit 14        | LPEN: Low-P                                                                                                                                                                          | ower Enable bi                        | t               |                     |                  |                  |                  |  |  |  |

|               |                                                                                                                                                                                      | er is enabled aft<br>r is enabled aft |                 |                     |                  |                  |                  |  |  |  |

| oit 13        | CTMREQ: CTMU Request bit                                                                                                                                                             |                                       |                 |                     |                  |                  |                  |  |  |  |

|               |                                                                                                                                                                                      | enabled when t<br>not enabled by      |                 | oled and active     |                  |                  |                  |  |  |  |

| bit 12        | BGREQ: Band Gap Request bit                                                                                                                                                          |                                       |                 |                     |                  |                  |                  |  |  |  |

|               |                                                                                                                                                                                      | is enabled whe                        |                 | nabled and acti     | ve               |                  |                  |  |  |  |

| bit 11-10     | Unimplement                                                                                                                                                                          | ted: Read as '                        | )'              |                     |                  |                  |                  |  |  |  |

| bit 9-8       | ASINT<1:0>:                                                                                                                                                                          | Auto-Scan (Th                         | reshold Detect  | i) Interrupt Mod    | e bits           |                  |                  |  |  |  |

|               | 10 = Interrupt                                                                                                                                                                       | after valid com<br>after Threshol     | pare has occu   |                     |                  | npare has occu   | rred             |  |  |  |

| bit 7-4       | Unimplement                                                                                                                                                                          | ted: Read as '                        | )'              |                     |                  |                  |                  |  |  |  |

| bit 3-2       | WM<1:0>: Wr                                                                                                                                                                          | rite Mode bits                        |                 |                     |                  |                  |                  |  |  |  |

|               | 11 = Reserved                                                                                                                                                                        |                                       |                 |                     |                  |                  |                  |  |  |  |

|               | 10 = Auto-compare only (conversion results are not saved, but interrupts are generated when a valid match occurs, as defined by the CMx and ASINTx bits)                             |                                       |                 |                     |                  |                  |                  |  |  |  |

|               |                                                                                                                                                                                      |                                       |                 |                     |                  | etermined by th  | ne reaister bits |  |  |  |

|               | when a r                                                                                                                                                                             | match occurs, a                       | as defined by t | he CMx bits)        |                  |                  |                  |  |  |  |

|               |                                                                                                                                                                                      |                                       |                 | saved to a loca     | tion determine   | ed by the buffer | register bits)   |  |  |  |