#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                                |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb202-e-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ64GB202 PIC24FJ128GB202

- PIC24FJ64GB204 PIC24FJ128GB204

The PIC24FJ128GB204 family expands the capabilities of the PIC24F family by adding a complete selection of Cryptographic Engines, ISO 7816 support and I<sup>2</sup>S support to its existing features. This combination, along with its ultra low-power features, Direct Memory Access (DMA) for peripherals and USB On-The-Go, make this family the new standard for mixed-signal PIC<sup>®</sup> microcontrollers in one economical and power-saving package.

### 1.1 Core Features

### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> Digital Signal Controllers (DSCs). The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 32 Kbytes (data)

- A 16-element Working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- Operational performance up to 16 MIPS

### 1.1.2 XLP POWER-SAVING TECHNOLOGY

The PIC24FJ128GB204 family of devices introduces a greatly expanded range of power-saving operating modes for the ultimate in power conservation. The new modes include:

- Retention Sleep with essential circuits being powered from a separate low-voltage regulator

- Deep Sleep without RTCC for the lowest possible power consumption under software control

- VBAT mode (with or without RTCC) to continue limited operation from a backup battery when VDD is removed

Many of these new low-power modes also support the continuous operation of the low-power, on-chip Real-Time Clock/Calendar (RTCC), making it possible for an application to keep time while the device is otherwise asleep.

Aside from these new features, PIC24FJ128GB204 family devices also include all of the legacy power-saving features of previous PIC24F microcontrollers, such as:

- On-the-Fly Clock Switching, allowing the selection of a lower power clock during run time

- Doze Mode Operation, for maintaining peripheral clock speed while slowing the CPU clock

- Instruction-Based Power-Saving Modes, for quick invocation of Idle and the many Sleep modes

## 1.1.3 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC24FJ128GB204 family offer five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes

- Two External Clock (EC) modes

- A Phase-Locked Loop (PLL) frequency multiplier, which allows clock speeds of up to 32 MHz

- A Fast Internal Oscillator (FRC) Nominal 8 MHz output with multiple frequency divider options and automatic frequency self-calibration during run time

- A separate Low-Power Internal RC Oscillator (LPRC) – 31 kHz nominal for low-power, timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

### 1.1.4 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve. This extends the ability of applications to grow from the relatively simple, to the powerful and complex, yet still selecting a Microchip device.

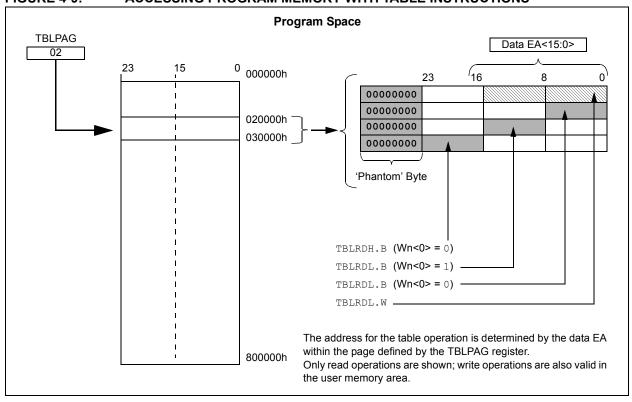

### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two, 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'. In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are described in Section 6.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

Note: Only Table Read operations will execute in the configuration memory space where Device IDs are located; Table Write operations are not allowed.

### FIGURE 4-9: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

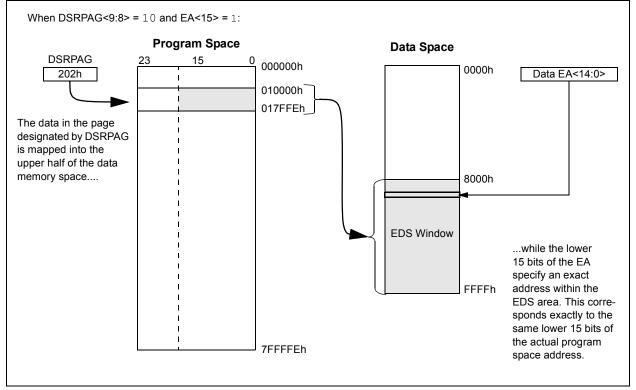

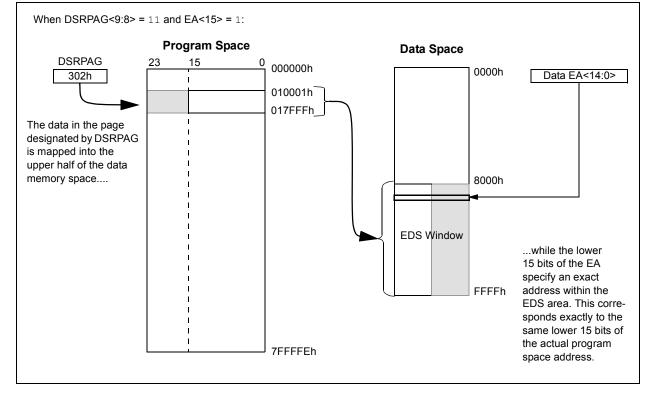

#### READING DATA FROM PROGRAM 4.3.3 MEMORY USING EDS

The upper 32 Kbytes of Data Space may optionally be mapped into any 16K word page of the program space. This provides transparent access of stored constant data from the Data Space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the Data Space occurs when the MSb of EA is '1' and the DSRPAG<9> bit is also '1'. The lower 8 bits of DSRPAG are concatenated to the Wn<14:0> bits to form a 23-bit EA to access program memory. The DSRPAG<8> bit decides which word should be addressed; when the bit is '0', the lower word and when '1', the upper word of the program memory is accessed.

The entire program memory is divided into 512 EDS pages, from 200h to 3FFh, each consisting of 16K words of data. Pages, 200h to 2FFh, correspond to the lower words of the program memory, while 300h to 3FFh correspond to the upper words of the program memory.

Using this EDS technique, the entire program memory can be accessed. Previously, the access to the upper word of the program memory was not supported.

Table 4-37 provides the corresponding 23-bit EDS address for program memory with EDS page and source addresses.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- · Execution prior to exiting the loop due to an interrupt

- · Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

| DSRPAG<br>(Data Space Read Register) |                |                    | Comment                           |

|--------------------------------------|----------------|--------------------|-----------------------------------|

| 200h                                 |                | 000000h to 007FFEh | Lower words of 4M program         |

| •                                    |                | •                  | instructions (8 Mbytes); for      |

| •                                    |                | •                  | read operations only              |

| •                                    |                | •                  |                                   |

| 2FFh                                 |                | 7F8000h to 7FFFEh  |                                   |

| 300h                                 | 8000h to FFFFh | 000001h to 007FFFh | Upper words of 4M program         |

| •                                    |                | •                  | instructions (4 Mbytes remaining, |

| •                                    |                | •                  | 4 Mbytes are phantom bytes); for  |

| •                                    |                | •                  | read operations only              |

| 3FFh                                 |                | 7F8001h to 7FFFFFh |                                   |

| 000h                                 |                | Invalid Address    | Address error trap <sup>(1)</sup> |

### TABLE 4-37: EDS PROGRAM ADDRESS WITH DIFFERENT PAGES AND ADDRESSES

Note 1: When the source/destination address is above 8000h and DSRPAG/DSWPAG is '0', an address error trap will occur.

#### EXAMPLE 4-3: EDS READ CODE FROM PROGRAM MEMORY IN ASSEMBLY

| ; Set the  | EDS page from where the dat | a to be read                                              |

|------------|-----------------------------|-----------------------------------------------------------|

| mov        | #0x0202, w0                 |                                                           |

| mov        | w0, DSRPAG                  | ;page 0x202, consisting lower words, is selected for read |

| mov        | #0x000A, w1                 | ;select the location (0x0A) to be read                    |

| bset       | w1, #15                     | ;set the MSB of the base address, enable EDS mode         |

| ;Read a by | te from the selected locati | on                                                        |

| mov.b      | [w1++], w2                  | ;read Low byte                                            |

| mov.b      | [w1++], w3                  | ;read High byte                                           |

| ;Read a wo | rd from the selected locati | on                                                        |

| mov        | [w1], w2                    | ;                                                         |

| ;Read Doub | le - word from the selected | llocation                                                 |

| mov.d      | [w1], w2                    | ;two word read, stored in w2 and w3                       |

|            |                             |                                                           |

### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION TO ACCESS UPPER WORD

### REGISTER 5-2: DMACHn: DMA CHANNEL n CONTROL REGISTER

| U-0    | U-0 | U-0 | r-0 | U-0 | R/W-0 | R/W-0                 | R/W-0                |

|--------|-----|-----|-----|-----|-------|-----------------------|----------------------|

| —      | —   | —   | —   | _   | NULLW | RELOAD <sup>(1)</sup> | CHREQ <sup>(3)</sup> |

| bit 15 |     |     |     |     |       |                       | bit 8                |

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0 | R/W-0 |

|---------|---------|---------|---------|---------|---------|-------|-------|

| SAMODE1 | SAMODE0 | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN  |

| bit 7   |         |         |         |         |         |       | bit 0 |

| Legend:           | r = Reserved bit |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-13 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                         |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12    | Reserved: Maintain as '0'                                                                                                                                                                                                                                                                                                                          |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                         |

| bit 10    | NULLW: Null Write Mode bit                                                                                                                                                                                                                                                                                                                         |

|           | <ul> <li>1 = A dummy write is initiated to DMASRCn for every write to DMADSTn</li> <li>0 = No dummy write is initiated</li> </ul>                                                                                                                                                                                                                  |

| bit 9     | RELOAD: Address and Count Reload bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>1 = DMASRCn, DMADSTn and DMACNTn registers are reloaded to their previous values upon the start of the next operation</li> <li>0 = DMASRCn, DMADSTn and DMACNTn are not reloaded on the start of the next operation<sup>(2)</sup></li> </ul>                                                                                              |

| bit 8     | CHREQ: DMA Channel Software Request bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                             |

|           | <ul> <li>1 = A DMA request is initiated by software; automatically cleared upon completion of a DMA transfer</li> <li>0 = No DMA request is pending</li> </ul>                                                                                                                                                                                     |

| bit 7-6   | SAMODE<1:0>: Source Address Mode Selection bits                                                                                                                                                                                                                                                                                                    |

|           | <ul> <li>11 = DMASRCn is used in Peripheral Indirect Addressing and remains unchanged</li> <li>10 = DMASRCn is decremented based on the SIZE bit after a transfer completion</li> <li>01 = DMASRCn is incremented based on the SIZE bit after a transfer completion</li> <li>00 = DMASRCn remains unchanged after a transfer completion</li> </ul> |

| bit 5-4   | DAMODE<1:0>: Destination Address Mode Selection bits                                                                                                                                                                                                                                                                                               |

|           | <ul> <li>11 = DMADSTn is used in Peripheral Indirect Addressing and remains unchanged</li> <li>10 = DMADSTn is decremented based on the SIZE bit after a transfer completion</li> <li>01 = DMADSTn is incremented based on the SIZE bit after a transfer completion</li> <li>00 = DMADSTn remains unchanged after a transfer completion</li> </ul> |

| bit 3-2   | TRMODE<1:0>: Transfer Mode Selection bits                                                                                                                                                                                                                                                                                                          |

|           | <ul> <li>11 = Repeated Continuous mode</li> <li>10 = Continuous mode</li> <li>01 = Repeated One-Shot mode</li> <li>00 = One-Shot mode</li> </ul>                                                                                                                                                                                                   |

| bit 1     | SIZE: Data Size Selection bit                                                                                                                                                                                                                                                                                                                      |

|           | 1 = Byte (8-bit)<br>0 = Word (16-bit)                                                                                                                                                                                                                                                                                                              |

| bit 0     | CHEN: DMA Channel Enable bit                                                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = The corresponding channel is enabled</li> <li>0 = The corresponding channel is disabled</li> </ul>                                                                                                                                                                                                                                    |

|           | Only the original DMACNTn is required to be stored to recover the original DMASRCn and DMADSTn values.                                                                                                                                                                                                                                             |

- 2: DMACNTn will always be reloaded in Repeated mode transfers, regardless of the state of the RELOAD bit.

- 3: The number of transfers executed while CHREQ is set depends on the configuration of TRMODE<1:0>.

| 1                                 | Reset – GOTO Instruction    | 000000h                                                          |

|-----------------------------------|-----------------------------|------------------------------------------------------------------|

|                                   | Reset – GOTO Address        | 000002h                                                          |

|                                   | Reserved                    | 000004h                                                          |

|                                   | Oscillator Fail Trap Vector |                                                                  |

|                                   | Address Error Trap Vector   | ]                                                                |

|                                   | Stack Error Trap Vector     | 1                                                                |

|                                   | Math Error Trap Vector      | 1                                                                |

|                                   | Reserved                    | 1                                                                |

|                                   | Reserved                    | ]                                                                |

|                                   | Reserved                    | ]                                                                |

|                                   | Interrupt Vector 0          | 000014h                                                          |

|                                   | Interrupt Vector 1          | 1                                                                |

|                                   | —                           | ]                                                                |

|                                   | —                           | ] ]                                                              |

|                                   | —                           | ] ]                                                              |

|                                   | Interrupt Vector 52         | 00007Ch                                                          |

|                                   | Interrupt Vector 53         | 00007Eh / Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| lity                              | Interrupt Vector 54         | 000080h                                                          |

| Decreasing Natural Order Priority | _                           |                                                                  |

| <u>م</u>                          |                             | 1                                                                |

| qei                               |                             | 1                                                                |

| ō                                 | Interrupt Vector 116        | 0000FCh                                                          |

| a                                 | Interrupt Vector 117        | ]0000FEh ノ                                                       |

| atu                               | Reserved                    | 000100h                                                          |

| ž                                 | Reserved                    | 000102h                                                          |

| ing                               | Reserved                    | 1                                                                |

| as                                | Oscillator Fail Trap Vector | 1                                                                |

| cre                               | Address Error Trap Vector   | 1                                                                |

| De                                | Stack Error Trap Vector     | 1                                                                |

|                                   | Math Error Trap Vector      | 1                                                                |

|                                   | Reserved                    | 1                                                                |

|                                   | Reserved                    | ]                                                                |

|                                   | Reserved                    | ]                                                                |

|                                   | Interrupt Vector 0          | 000114h                                                          |

|                                   | Interrupt Vector 1          |                                                                  |

|                                   |                             |                                                                  |

|                                   | —                           |                                                                  |

|                                   |                             | ]                                                                |

|                                   | Interrupt Vector 52         | 00017Ch                                                          |

|                                   | Interrupt Vector 53         | 00017Eh > Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 54         | 000180h                                                          |

|                                   |                             | ]                                                                |

|                                   |                             | ]                                                                |

|                                   | —                           |                                                                  |

| L                                 | Interrupt Vector 116        | 1                                                                |

| V                                 | Interrupt Vector 117        | 0001FEh                                                          |

|                                   | Start of Code               | 000200h                                                          |

### TABLE 8-1: TRAP VECTOR DETAILS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 000112h      | Reserved           |

### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3 (CONTINUED)

- bit 5 INT3IF: External Interrupt 3 Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

- bit 4-3 Unimplemented: Read as '0'

- bit 2 MI2C2IF: Master I2C2 Event Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 1 SI2C2IF: Slave I2C2 Event Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 Unimplemented: Read as '0'

| U-0           | U-0   | R/W-1            | R/W-1  | R/W-1                                   | R/W-1  | R/W-1   | R/W-1  |

|---------------|-------|------------------|--------|-----------------------------------------|--------|---------|--------|

| _             | _     | MDC2R5           | MDC2R4 | MDC2R3                                  | MDC2R2 | MDC2R1  | MDC2R0 |

| bit 15        |       | -                |        | ·                                       |        |         | bit 8  |

|               |       |                  |        |                                         |        |         |        |

| U-0           | U-0   | R/W-1            | R/W-1  | R/W-1                                   | R/W-1  | R/W-1   | R/W-1  |

| _             | _     | MDC1R5           | MDC1R4 | MDC1R3                                  | MDC1R2 | MDC21R1 | MDC1R0 |

| bit 7         |       |                  | •      |                                         | •      |         | bit 0  |

|               |       |                  |        |                                         |        |         |        |

| Legend:       |       |                  |        |                                         |        |         |        |

| R = Readable  | e bit | W = Writable     | bit    | U = Unimplemented bit, read as '0'      |        |         |        |

| -n = Value at | POR   | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is unknown |        |         | nown   |

### REGISTER 11-22: RPINR31: PERIPHERAL PIN SELECT INPUT REGISTER 31

bit 15-14 Unimplemented: Read as '0'

bit 13-8 MDC2R<5:0>: Assign TX Carrier 2 Input (MDCIN2) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 MDC1R<5:0>: Assign TX Carrier 1 Input (MDCIN1) to Corresponding RPn or RPIn Pin bits

### REGISTER 11-35: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12<sup>(1)</sup>

| U-0           | U-0           | R/W-0            | R/W-0          | R/W-0                                   | R/W-0            | R/W-0           | R/W-0          |

|---------------|---------------|------------------|----------------|-----------------------------------------|------------------|-----------------|----------------|

| —             | —             | RP25R5           | RP25R4         | RP25R3                                  | RP25R2           | RP25R1          | RP25R0         |

| bit 15        |               |                  |                | -<br>-                                  |                  |                 | bit 8          |

|               |               |                  |                |                                         |                  |                 |                |

| U-0           | U-0           | R/W-0            | R/W-0          | R/W-0                                   | R/W-0            | R/W-0           | R/W-0          |

| —             | —             | RP24R5           | RP24R4         | RP24R3                                  | RP24R2           | RP24R1          | RP24R0         |

| bit 7         |               | •                |                |                                         | •                |                 | bit 0          |

|               |               |                  |                |                                         |                  |                 |                |

| Legend:       |               |                  |                |                                         |                  |                 |                |

| R = Readable  | e bit         | W = Writable     | bit            | U = Unimplem                            | nented bit, read | 1 as '0'        |                |

| -n = Value at | POR           | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unknown |                  |                 | nown           |

|               |               |                  |                |                                         |                  |                 |                |

| bit 15-14     | Unimplemen    | ted: Read as '   | )'             |                                         |                  |                 |                |

| bit 13-8      | RP25R<5:0>:   | RP25 Output      | Pin Mapping b  | its                                     |                  |                 |                |

|               | Peripheral Ou | tput Number n    | is assigned to | pin, RP25 (see                          | Table 11-4 for   | peripheral func | tion numbers). |

| bit 7-6       | Unimplemen    | ted: Read as '   | )'             |                                         |                  |                 |                |

| bit 5-0       | RP24R<5:0>:   | RP24 Output      | Pin Mapping b  | its                                     |                  |                 |                |

5-0 **RP24R<5:0>:** RP24 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP24 (see Table 11-4 for peripheral function numbers).

Note 1: These pins are not available in 28-pin devices.

NOTES:

### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | IC32  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0       | R/W-0, HS | U-0 | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-1    |

|-------------|-----------|-----|----------|----------|----------|----------|----------|

| ICTRIG      | TRIGSTAT  | —   | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7 bit 0 |           |     |          |          |          |          |          |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | <b>d as</b> '0'    |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-9 | Unimplemented: Read as '0'                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8    | IC32: Cascade Two IC Modules Enable bit (32-bit operation)                                                                                                                                |

|          | <ul> <li>1 = ICx and ICy operate in cascade as a 32-bit module (this bit must be set in both modules)</li> <li>0 = ICx functions independently as a 16-bit module</li> </ul>              |

| bit 7    | ICTRIG: Input Capture x Sync/Trigger Select bit                                                                                                                                           |

|          | <ul> <li>1 = Triggers ICx from the source designated by the SYNCSELx bits</li> <li>0 = Synchronizes ICx with the source designated by the SYNCSELx bits</li> </ul>                        |

| bit 6    | TRIGSTAT: Timer Trigger Status bit                                                                                                                                                        |

|          | <ul> <li>1 = Timer source has been triggered and is running (set in hardware, can be set in software)</li> <li>0 = Timer source has not been triggered and is being held clear</li> </ul> |

| bit 5    | Unimplemented: Read as '0'                                                                                                                                                                |

- **Note 1:** Use these inputs as trigger sources only and never as sync sources.

- 2: Never use an IC module as its own trigger source by selecting this mode.

### 19.4.2 RECEIVING AN IN TOKEN IN DEVICE MODE

- 1. Attach to a USB host and enumerate as described in Chapter 9 of the "USB 2.0 Specification".

- 2. Create a data buffer and populate it with the data to send to the host.

- 3. In the appropriate (Even or Odd) TX BD for the desired endpoint:

- a) Set up the status register (BDnSTAT) with the correct data toggle (DATA0/1) value and the byte count of the data buffer.

- b) Set up the address register (BDnADR) with the starting address of the data buffer.

- c) Set the UOWN bit of the status register to '1'.

- When the USB module receives an IN token, it automatically transmits the data in the buffer. Upon completion, the module updates the status register (BDnSTAT) and sets the Transfer Done Interrupt Flag, TRNIF (U1IR<3>).

### 19.4.3 RECEIVING AN OUT TOKEN IN DEVICE MODE

- 1. Attach to a USB host and enumerate as described in Chapter 9 of the "USB 2.0 Specification".

- 2. Create a data buffer with the amount of data you are expecting from the host.

- 3. In the appropriate (Even or Odd) TX BD for the desired endpoint:

- a) Set up the status register (BDnSTAT) with the correct data toggle (DATA0/1) value and the byte count of the data buffer.

- b) Set up the address register (BDnADR) with the starting address of the data buffer.

- c) Set the UOWN bit of the status register to '1'.

- 4. When the USB module receives an OUT token, it automatically receives the data sent by the host to the buffer. Upon completion, the module updates the status register (BDnSTAT) and sets the Transfer Done Interrupt Flag, TRNIF (U1IR<3>).

### **19.5 Host Mode Operation**

The following sections describe how to perform common Host mode tasks. In Host mode, USB transfers are invoked explicitly by the host software. The host software is responsible for the Acknowledge portion of the transfer. Also, all transfers are performed using the USB Endpoint 0 Control register (U1EP0) and Buffer Descriptors.

### 19.5.1 ENABLE HOST MODE AND DISCOVER A CONNECTED DEVICE

- Enable Host mode by setting the HOSTEN bit (U1CON<3>). This causes the Host mode control bits in other USB OTG registers to become available.

- Enable the D+ and D- pull-down resistors by setting the DPPULDWN and DMPULDWN bits (U10TGCON<5:4>). Disable the D+ and Dpull-up resistors by clearing the DPPULUP and DMPULUP bits (U10TGCON<7:6>).

- At this point, Start-of-Frame (SOF) generation begins with the SOF counter loaded with 12,000. Eliminate noise on the USB by clearing the SOFEN bit (U1CON<0>) to disable Start-of-Frame packet generation.

- 4. Enable the device attached interrupt by setting the ATTACHIE bit (U1IE<6>).

- Wait for the device attached interrupt (U1IR<6> = 1). This is signaled by the USB device changing the state of D+ or D- from '0' to '1' (SE0 to J-state). After it occurs, wait 100 ms for the device power to stabilize.

- Check the state of the JSTATE and SE0 bits in U1CON. If the JSTATE bit (U1CON<7>) is '0', the connecting device is low speed. If the connecting device is low speed, set the LSPDEN and LSPD bits (U1ADDR<7> and U1EP0<7>, respectively) to enable low-speed operation.

- Reset the USB device by setting the USBRST bit (U1CON<4>) for at least 50 ms, sending Reset signaling on the bus. After 50 ms, terminate the Reset by clearing USBRST.

- In order to keep the connected device from going into suspend, enable the SOF packet generation by setting the SOFEN bit.

- 9. Wait 10 ms for the device to recover from Reset.

- 10. Perform enumeration as described by Chapter 9 of the "USB 2.0 Specification".

### REGISTER 19-13: U1CNFG2: USB CONFIGURATION REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0  | R/W-0    | R/W-0                   | U-0 | R/W-0                 |

|-------|-----|-----|--------|----------|-------------------------|-----|-----------------------|

| —     | —   | —   | PUVBUS | EXTI2CEN | UVBUSDIS <sup>(1)</sup> | —   | UTRDIS <sup>(1)</sup> |

| bit 7 |     |     |        |          |                         |     | bit 0                 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-5 | Unimplemented: Read as '0'                                                                                                                                              |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4    | PUVBUS: VBUS Pull-up Enable bit                                                                                                                                         |

|          | 1 = Pull-up on VBUS pin is enabled                                                                                                                                      |

|          | 0 = Pull-up on VBUS pin is disabled                                                                                                                                     |

| bit 3    | EXTI2CEN: I <sup>2</sup> C <sup>™</sup> Interface for External Module Control Enable bit                                                                                |

|          | <ul> <li>1 = External module(s) is controlled via the l<sup>2</sup>C interface</li> <li>0 = External module(s) is controlled via the dedicated pins</li> </ul>          |

| bit 2    | UVBUSDIS: USB On-Chip 5V Boost Regulator Builder Disable bit <sup>(1)</sup>                                                                                             |

|          | <ul> <li>1 = On-chip boost regulator builder is disabled; digital output control interface is enabled</li> <li>0 = On-chip boost regulator builder is active</li> </ul> |

| bit 1    | Unimplemented: Read as '0'                                                                                                                                              |

| bit 0    | UTRDIS: USB On-Chip Transceiver Disable bit <sup>(1)</sup>                                                                                                              |

|          | <ul> <li>1 = On-chip transceiver is disabled; digital transceiver interface is enabled</li> <li>0 = On-chip transceiver is active</li> </ul>                            |

**Note 1:** Never change these bits while the USBPWR bit is set (U1PWRC<0> = 1).

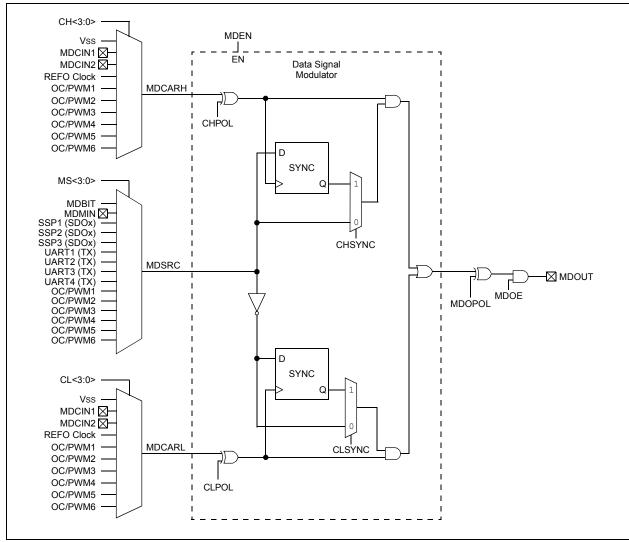

### 20.0 DATA SIGNAL MODULATOR (DSM)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Data Signal Modulator (DSM)" (DS39744). The information in this data sheet supersedes the information in the FRM.

The Data Signal Modulator (DSM) allows the user to mix a digital data stream (the "modulator signal") with a carrier signal to produce a modulated output. Both the carrier and the modulator signals are supplied to the DSM module, either internally from the output of a peripheral, or externally through an input pin. The modulated output signal is generated by performing a logical AND operation of both the carrier and modulator signals, and then it is provided to the MDOUT pin. Using this method, the DSM can generate the following types of key modulation schemes:

- Frequency Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Figure 20-1 shows a simplified block diagram of the Data Signal Modulator peripheral.

### FIGURE 20-1: SIMPLIFIED BLOCK DIAGRAM OF THE DATA SIGNAL MODULATOR

### 24.1 User Interface

### 24.1.1 POLYNOMIAL INTERFACE

The CRC module can be programmed for CRC polynomials of up to the  $32^{nd}$  order, using up to 32 bits.

Polynomial length, which reflects the highest exponent in the equation, is selected by the PLEN<4:0> bits (CRCCON2<4:0>).

The CRCXORL and CRCXORH registers control which exponent terms are included in the equation. Setting a particular bit includes that exponent term in the equation. Functionally, this includes an XOR operation on the corresponding bit in the CRC engine. Clearing the bit disables the XOR.

For example, consider two CRC polynomials, one is a 16-bit and the other is a 32-bit equation.

### EQUATION 24-1: 16-BIT, 32-BIT CRC POLYNOMIALS

X16 + X12 + X5 + 1

and

X32+X26 + X23 + X22 + X16 + X12 + X11 + X10 + X8 + X7 + X5 + X4 + X2 + X + 1

To program these polynomials into the CRC generator, set the register bits, as shown in Table 24-1.

Note that the appropriate positions are set to '1' to indicate that they are used in the equation (for example, X26 and X23). The '0' bit required by the equation is always XORed; thus, X0 is a don't care. For a polynomial of length 32, it is assumed that the 32<sup>nd</sup> bit will be used. Therefore, the X<31:1> bits do not have the 32<sup>nd</sup> bit.

### 24.1.2 DATA INTERFACE

The module incorporates a FIFO that works with a variable data width. Input data width can be configured to any value between 1 and 32 bits using the DWIDTH<4:0> bits (CRCCON2<12:8>). When the data width is greater than 15, the FIFO is 4 words deep. When the DWIDTHx bits are between 15 and 8, the FIFO is 8 words deep. When the DWIDTHx bits are less than 8, the FIFO is 16 words deep.

The data for which the CRC is to be calculated must first be written into the FIFO. Even if the data width is less than 8, the smallest data element that can be written into the FIFO is 1 byte. For example, if the DWIDTHx bits are 5, then the size of the data is DWIDTH<4:0> + 1 or 6. The data is written as a whole byte; the two unused upper bits are ignored by the module.

Once data is written into the MSb of the CRCDAT registers (that is, the MSb as defined by the data width), the value of the VWORD<4:0> bits (CRCCON1<12:8>) increments by one. For example, if the DWIDTHx bits are 24, the VWORDx bits will increment when bit 7 of CRCDATH is written. Therefore, CRCDATL must always be written to before CRCDATH.

The CRC engine starts shifting data when the CRCGO bit is set and the value of the VWORDx bits is greater than zero.

Each word is copied out of the FIFO into a buffer register, which decrements the VWORDx bits. The data is then shifted out of the buffer. The CRC engine continues shifting at a rate of two bits per instruction cycle, until the VWORDx bits reach zero. This means that for a given data width, it takes half that number of instructions for each word to complete the calculation. For example, it takes 16 cycles to calculate the CRC for a single word of 32-bit data.

When the VWORDx bits reach the maximum value for the configured value of the DWIDTHx bits (4, 8 or 16), the CRCFUL bit becomes set. When the VWORDx bits reach zero, the CRCMPT bit becomes set. The FIFO is emptied and the VWORD<4:0> bits are set to '00000' whenever CRCEN is '0'.

At least one instruction cycle must pass after a write to CRCWDAT before a read of the VWORDx bits is done.

### TABLE 24-1: CRC SETUP EXAMPLES FOR 16 AND 32-BIT POLYNOMIALS

| CRC Control Bits | Bit Values          |                     |  |  |  |

|------------------|---------------------|---------------------|--|--|--|

| CRC Control Bits | 16-Bit Polynomial   | 32-Bit Polynomial   |  |  |  |

| PLEN<4:0>        | 01111               | 11111               |  |  |  |

| X<31:16>         | 0000 0000 0000 0001 | 0000 0100 1100 0001 |  |  |  |

| X<15:0>          | 0001 0000 0010 00x  | 0001 1101 1011 011x |  |  |  |

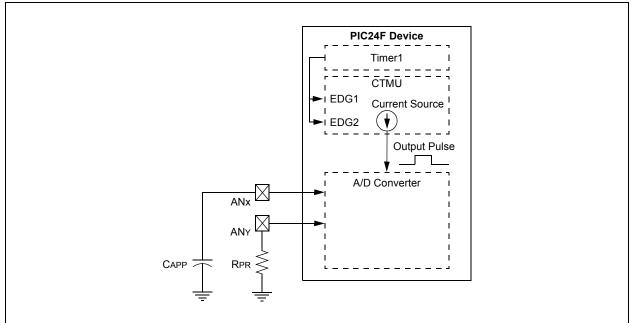

## FIGURE 28-1: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR CAPACITANCE MEASUREMENT

### REGISTER 30-3: CW3: FLASH CONFIGURATION WORD 3 (CONTINUED)

- bit 7

Reserved: Always maintain as '1'

bit 6-0

WPFP<6:0>: Write-Protected Code Segment Boundary Page bits<sup>(3)</sup>

Designates the 512 instruction words page boundary of the protected Code Segment.

If WPEND = 1:

Specifies the lower page boundary of the protected Code Segment; the last page being the last implemented page in the device.

If WPEND = 0:

Specifies the upper page boundary of the protected Code Segment; Page 0 being the lower boundary.

- **Note 1:** Regardless of WPCFG status, if WPEND = 1 or if the WPFP<6:0> bits correspond to the Configuration Word page, the Configuration Word page is protected.

- 2: Ensure that the SCLKI pin is made a digital input while using this configuration (see Table 11-1).

- 3: For the 64K devices (PIC24FJ64GB2XX), maintain WPFP6 as '0'.

- 4: This Configuration bit only takes effect when PLL is not being used.

### REGISTER 30-5: DEVID: DEVICE ID REGISTER

| U-1                      | U-1                                           | U-1             | U-1             | U-1          | U-1              | U-1             | U-1    |

|--------------------------|-----------------------------------------------|-----------------|-----------------|--------------|------------------|-----------------|--------|

|                          | —                                             | _               |                 | —            |                  |                 | —      |

| bit 23                   |                                               |                 |                 |              |                  |                 | bit 16 |

|                          |                                               |                 |                 |              |                  |                 |        |

| R                        | R                                             | R               | R               | R            | R                | R               | R      |

| FAMID7                   | ID7 FAMID6 FAMID5 FAMID4 FAMID3 FAMID2 FAMID1 |                 |                 |              |                  |                 | FAMID0 |

| bit 15                   |                                               |                 |                 |              |                  |                 | bit 8  |

|                          |                                               |                 |                 |              |                  |                 |        |

| R                        | R                                             | R               | R               | R            | R                | R               | R      |

| DEV7                     | DEV6                                          | DEV5            | DEV4            | DEV3         | DEV2             | DEV1            | DEV0   |

| bit 7                    |                                               |                 |                 |              |                  |                 | bit 0  |

|                          |                                               |                 |                 |              |                  |                 |        |

| Legend: R = Readable bit |                                               |                 |                 | U = Unimplem | nented bit, read | <b>l as</b> '1' |        |

|                          |                                               |                 |                 |              |                  |                 |        |

| bit 23-16                | Unimplement                                   | ted: Read as '1 | ,               |              |                  |                 |        |

| bit 15-8                 | FAMID<7:0>:                                   | Device Family   | Identifier bits |              |                  |                 |        |

|                          | 0100 1100 =                                   | PIC24FJ1280     | B204 family     |              |                  |                 |        |

|                          |                                               |                 |                 |              |                  |                 |        |

bit 7-0 **DEV<7:0>:** Individual Device Identifier bits 0101 1000 = PIC24FJ64GB202 0101 1010 = PIC24FJ128GB202 0101 1001 = PIC24FJ64GB204 0101 1011 = PIC24FJ128GB204

### REGISTER 30-6: DEVREV: DEVICE REVISION REGISTER

| U-0       | U-0            | U-0 | U-0 | U-0             | U-0            | U-0  | U-0    |

|-----------|----------------|-----|-----|-----------------|----------------|------|--------|

| _         | —              | —   | —   | —               | —              | —    | —      |

| bit 23    |                |     |     |                 |                |      | bit 16 |

|           |                |     |     |                 |                |      |        |

| U-0       | U-0            | U-0 | U-0 | U-0             | U-0            | U-0  | U-0    |

| _         | —              | —   | —   | —               | —              | —    | —      |

| bit 15    |                |     | •   | •               |                |      | bit 8  |

|           |                |     |     |                 |                |      |        |

| U-0       | U-0            | U-0 | U-0 | R               | R              | R    | R      |

| _         | _              | —   | —   | REV3            | REV2           | REV1 | REV0   |

| bit 7     |                |     |     |                 |                |      | bit 0  |

|           |                |     |     |                 |                |      |        |

| Lagand, D | - Doodahla hit |     |     | II – I Inimalor | onted hit read |      |        |

**Legend:** R = Readable bit U = Unimplemented bit, read as '1'

bit 23-4 Unimplemented: Read as '1'

bit 3-0 **REV<3:0>:** Device Revision Identifier bits

## 30.4 Program Verification and Code Protection

PIC24FJ128GB204 family devices provide two complimentary methods to protect application code from overwrites and erasures. These also help to protect the device from inadvertent configuration changes during run time.

### 30.4.1 GENERAL SEGMENT PROTECTION

For all devices in the PIC24FJ128GB204 family, the on-chip program memory space is treated as a single block, known as the General Segment (GS). Code protection for this block is controlled by one Configuration bit, GCP. This bit inhibits external reads and writes to the program memory space. It has no direct effect in normal execution mode.

Write protection is controlled by the GWRP bit in Configuration Word 1. When GWRP is programmed to '0', internal write and erase operations to program memory are blocked.

### 30.4.2 CODE SEGMENT PROTECTION

In addition to global General Segment protection, a separate subrange of the program memory space can be individually protected against writes and erases. This area can be used for many purposes where a separate block of write and erase-protected code is needed, such as bootloader applications. Unlike common boot block implementations, the specially protected segment in the PIC24FJ128GB204 family devices can be located by the user anywhere in the program space and configured in a wide range of sizes.

Code Segment (CS) protection provides an added level of protection to a designated area of program memory by disabling the NVM safety interlock whenever a write or erase address falls within a specified range. It does not override General Segment protection controlled by the GCP or GWRP bits. For example, if GCP and GWRP are enabled, enabling segmented code protection for the bottom half of program memory does not undo General Segment protection for the top half.

The size and type of protection for the segmented code range are configured by the WPFPx, WPEND, WPCFG and WPDIS bits in Configuration Word 3. Code Segment protection is enabled by programming the WPDIS bit (= 0). The WPFPx bits specify the size of the segment to be protected, by specifying the 512-word code page that is the start or end of the protected segment. The specified region is inclusive, therefore, this page will also be protected.

The WPEND bit determines if the protected segment uses the top or bottom of the program space as a boundary. Programming WPEND (= 0) sets the bottom of program memory (000000h) as the lower boundary of the protected segment. Leaving WPEND unprogrammed (= 1) protects the specified page through the last page of implemented program memory, including the Configuration Word locations.

A separate bit, WPCFG, is used to protect the last page of program space, including the Flash Configuration Words. Programming WPCFG (= 0) protects the last page in addition to the pages selected by the WPEND and WPFP<6:0> bits setting. This is useful in circumstances where write protection is needed for both the Code Segment in the bottom of the memory and the Flash Configuration Words.

The various options for segment code protection are shown in Table 30-2.

| Segmen | Segment Configuration Bits |       | Write/Erase Protection of Code Segment                                                                                                                                                                        |  |  |  |

|--------|----------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| WPDIS  | WPEND                      | WPCFG | Write/Erase Protection of Code Segment                                                                                                                                                                        |  |  |  |

| 1      | х                          | Х     | No additional protection is enabled; all program memory protection is configured by GCP and GWRP.                                                                                                             |  |  |  |

| 0      | 1                          | X     | Addresses from the first address of the code page are defined by WPFP<6:0> through the end of implemented program memory (inclusive); erase/write-protected, including Flash Configuration Words.             |  |  |  |

| 0      | 0                          | 1     | Address, 000000h through the last address of the code page, is defined by WPFP<6:0> (inclusive); erase/write-protected.                                                                                       |  |  |  |

| 0      | 0                          | 0     | Address, 000000h through the last address of the code page, is defined by WPFP<6:0> (inclusive); erase/write-protected and the last page, including the Flash Configuration Words, are erase/write-protected. |  |  |  |

TABLE 30-2: CODE SEGMENT PROTECTION CONFIGURATION OPTIONS