Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                     |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT        |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

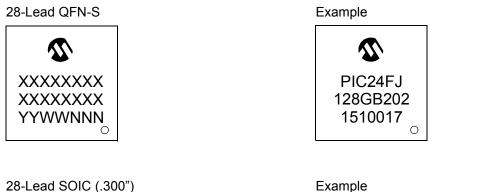

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb202-i-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Analog Features**

- 10/12-Bit, 12-Channel Analog-to-Digital (A/D) Converter:

- Conversion rate of 500 ksps (10-bit), 200 ksps (12-bit)

- Conversion available during Sleep and Idle

- Three Rail-to-Rail, Enhanced Analog Comparators with Programmable Input/Output Configuration

- Three On-Chip Programmable Voltage References

- Charge Time Measurement Unit (CTMU):

- Used for capacitive touch sensing, up to 12 channels

- Time measurement down to 100 ps resolution

- Operation in Sleep mode

# **Peripheral Features**

- Up to Five External Interrupt Sources

- Peripheral Pin Select (PPS); Allows Independent I/O Mapping of many Peripherals

- Five 16-Bit Timers/Counters with Prescaler:

Can be paired as 32-bit timers/counters

- Six-Channel DMA supports All Peripheral modules:

- Minimizes CPU overhead and increases data throughput

- Six Input Capture modules, each with a Dedicated 16-Bit Timer

- Six Output Compare/PWM modules, each with a Dedicated 16-Bit Timer

- Enhanced Parallel Master/Slave Port (EPMP/EPSP)

- Hardware Real-Time Clock/Calendar (RTCC):

- Runs in Sleep, Deep Sleep and VBAT modes

- Three 3-Wire/4-Wire SPI modules:

- Support four Frame modes

- Variable FIFO buffer

- I<sup>2</sup>S mode

- Variable width from 2-bit to 32-bit

- Two I<sup>2</sup>C<sup>™</sup> modules Support Multi-Master/

- Slave mode and 7-Bit/10-Bit Addressing

- Four UART modules:

- Support RS-485, RS-232 and LIN/J2602

- On-chip hardware encoder/decoder for IrDA®

- Smart Card ISO 7816 support on UART1 and UART2 only:

- T = 0 protocol with automatic error handling

- T = 1 protocol

- Dedicated Guard Time Counter (GTC)

- Dedicated Waiting Time Counter (WTC)

- Auto-wake-up on Auto-Baud Detect (ABD)

- 4-level deep FIFO buffer

- Programmable 32-Bit Cyclic Redundancy Check (CRC) Generator

- Digital Signal Modulator provides On-Chip FSK and PSK Modulation for a Digital Signal Stream

- High-Current Sink/Source (18 mA/18 mA) on All I/O Pins

- Configurable Open-Drain Outputs on Digital I/O Pins

- 5.5V Tolerant Inputs on Most Pins

# **High-Performance CPU**

- Modified Harvard Architecture

- Up to 16 MIPS Operation @ 32 MHz

- 8 MHz Internal Oscillator:

- 96 MHz PLL option

- Multiple clock divide options

- Run-time self-calibration capability for maintaining better than ±0.20% accuracy

- Fast start-up

- 17-Bit x 17-Bit Single-Cycle Hardware Fractional/Integer Multiplier

- 32-Bit by 16-Bit Hardware Divider

- 16 x 16-Bit Working Register Array

- C Compiler Optimized Instruction Set Architecture (ISA)

- Two Address Generation Units (AGUs) for Separate Read and Write Addressing of Data Memory

## **Special Microcontroller Features**

- Supply Voltage Range of 2.0V to 3.6V

- Two On-Chip Voltage Regulators (1.8V and 1.2V) for Regular and Extreme Low-Power Operation

- 20,000 Erase/Write Cycle Endurance Flash Program Memory, Typical

- Flash Data Retention: 20 Years Minimum

- Self-Programmable under Software Control

- · Programmable Reference Clock Output

- In-Circuit Serial Programming™ (ICSP™) and In-Circuit Emulation (ICE) via 2 Pins

- JTAG Programming and Boundary Scan Support

- Fail-Safe Clock Monitor (FSCM) Operation:

- Detects clock failure and switches to on-chip, Low-Power RC Oscillator

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Separate Brown-out Reset (BOR) and Deep Sleep Brown-out Reset (DSBOR) Circuits

- Programmable High/Low-Voltage Detect (HLVD)

- Flexible Watchdog Timer (WDT) with its Own RC Oscillator for Reliable Operation

- Standard and Ultra Low-Power Watchdog Timers (ULPW) for Reliable Operation in Standard and Deep Sleep modes

## TABLE 4-21: DMA REGISTER MAP

|              | -21. |        |        |        |        |        |        |         |              |               |              |         |         |         |         |       |        |                                        |

|--------------|------|--------|--------|--------|--------|--------|--------|---------|--------------|---------------|--------------|---------|---------|---------|---------|-------|--------|----------------------------------------|

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8        | Bit 7         | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1 | Bit 0  | All<br>Resets                          |

| DMACON       | 0450 | DMAEN  | _      | —      | _      | _      | _      | _       | —            | —             | —            | _       | —       | _       | —       | _     | PRSSEL | 0000                                   |

| DMABUF       | 0452 |        |        |        |        |        |        |         | DMA Trans    | fer Data Buff | er           |         |         |         |         |       |        | 0000                                   |

| DMAL         | 0454 |        |        |        |        |        |        | DN      | IA High Add  | ress Limit Re | egister      |         |         |         |         |       |        | 0000                                   |

| DMAH         | 0456 |        |        |        |        |        |        | DN      | IA Low Add   | ress Limit Re | gister       |         |         |         |         |       |        | 0000                                   |

| DMACH0       | 0458 | —      | _      | _      | r      | _      | NULLW  | RELOAD  | CHREQ        | SAMODE1       | SAMODE0      | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT0      | 045A | DBUFWF | _      | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF |         | _     | HALFEN | 0000                                   |

| DMASRC0      | 045C |        |        |        |        |        |        | DMA C   | hannel 0 So  | urce Addres   | s Register   |         |         |         |         |       |        | 0000                                   |

| DMADST0      | 045E |        |        |        |        |        |        | DMA Cha | annel 0 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT0      | 0460 |        |        |        |        |        |        | DMA Ch  | annel 0 Trai | nsaction Cou  | nt Register  |         |         |         |         |       |        | 0001                                   |

| DMACH1       | 0462 | _      | _      | _      | r      | _      | NULLW  | RELOAD  | CHREQ        | SAMODE1       | SAMODE0      | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT1      | 0464 | DBUFWF | _      | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF | _       | _     | HALFEN | 0000                                   |

| DMASRC1      | 0466 | İ. İ.  |        |        |        |        |        | DMA C   | hannel 1 So  | urce Addres   | s Register   |         |         |         |         |       |        | 0000                                   |

| DMADST1      | 0468 |        |        |        |        |        |        | DMA Cha | annel 1 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT1      | 046A |        |        |        |        |        |        | DMA Ch  | annel 1 Trai | nsaction Cou  | nt Register  |         |         |         |         |       |        | 0001                                   |

| DMACH2       | 046C | _      | —      | —      | r      | —      | NULLW  | RELOAD  | CHREQ        | SAMODE1       | SAMODE0      | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT2      | 046E | DBUFWF | _      | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF |         |       | HALFEN | 0000                                   |

| DMASRC2      | 0470 |        |        |        |        |        |        | DMA C   | hannel 2 So  | urce Addres   | s Register   |         |         |         |         |       |        | 0000                                   |

| DMADST2      | 0472 |        |        |        |        |        |        | DMA Cha | annel 2 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT2      | 0474 |        |        |        |        |        |        | DMA Ch  | annel 2 Trai | nsaction Cou  | nt Register  |         |         |         |         |       |        | 0001                                   |

| DMACH3       | 0476 | _      | _      | —      | r      | _      | NULLW  | RELOAD  | CHREQ        | SAMODE1       | SAMODE0      | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT3      | 0478 | DBUFWF | _      | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF | —       | _     | HALFEN | 0000                                   |

| DMASRC3      | 047A |        |        |        |        |        |        | DMA C   | hannel 3 Sc  | urce Addres   | s Register   |         |         |         |         |       |        | 0000                                   |

| DMADST3      | 047C |        |        |        |        |        |        | DMA Cha | annel 3 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT3      | 047E |        |        |        |        |        |        | DMA Ch  | annel 3 Trai | nsaction Cou  | nt Register  |         |         |         |         |       |        | 0001                                   |

| DMACH4       | 0480 | _      | _      | —      | r      | _      | NULLW  | RELOAD  | CHREQ        | SAMODE1       | SAMODE0      | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT4      | 0482 | DBUFWF | _      | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF |         |       | HALFEN | 0000                                   |

| DMASRC4      | 0484 | · · ·  |        |        |        |        |        | DMA C   | hannel 4 Sc  | urce Addres   | s Register   |         |         |         |         |       |        | 0000                                   |

| DMADST4      | 0486 |        |        |        |        |        |        | DMA Cha | annel 4 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT4      | 0488 |        |        |        |        |        |        | DMA Ch  | annel 4 Trai | nsaction Cou  | nt Register  |         |         |         |         |       |        | 0001                                   |

| DMACH5       | 048A | _      | _      | _      | r      | _      | NULLW  | RELOAD  | CHREQ        | SAMODE1       |              | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT5      | 048C | DBUFWF | _      | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF | _       | _     | HALFEN | 0000                                   |

| DMASRC5      | 048E |        |        | •      |        |        |        | DMA C   | hannel 5 Sc  | urce Addres   | s Register   |         | •       |         |         |       |        | 0000                                   |

| DMADST5      | 0490 |        |        |        |        |        |        | DMA Cha | annel 5 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT5      | 0492 |        |        |        |        |        |        | DMA Ch  | annel 5 Trai | nsaction Cou  | nt Register  |         |         |         |         |       |        | 0001                                   |

|              |      |        |        |        |        |        |        |         |              |               | <b>v</b>     |         |         |         |         |       |        | اـــــــــــــــــــــــــــــــــــــ |

Legend: - = unimplemented, read as '0'; r = reserved bit. Reset values are shown in hexadecimal.

| R/W-0         | R/W-0         | R/W-0                                             | R/W-0                     | R/W-0             | R/W-0           | R/W-0             | R/W-0       |

|---------------|---------------|---------------------------------------------------|---------------------------|-------------------|-----------------|-------------------|-------------|

| U2TXIE        | U2RXIE        | INT2IE <sup>(1)</sup>                             | T5IE                      | T4IE              | OC4IE           | OC3IE             | DMA2IE      |

| bit 15        | 1             |                                                   |                           |                   |                 | 1                 | bit 8       |

|               |               |                                                   |                           |                   |                 |                   |             |

| U-0           | U-0           | U-0                                               | R/W-0                     | R/W-0             | R/W-0           | R/W-0             | R/W-0       |

| _             | —             | —                                                 | INT1IE <sup>(1)</sup>     | CNIE              | CMIE            | MI2C1IE           | SI2C1IE     |

| bit 7         |               |                                                   |                           |                   |                 |                   | bit 0       |

| Legend:       |               |                                                   |                           |                   |                 |                   |             |

| R = Readabl   | e hit         | W = Writable                                      | hit                       | II = Unimplen     | nented bit, rea | d as '0'          |             |

| -n = Value at |               | '1' = Bit is set                                  |                           | '0' = Bit is clea |                 | x = Bit is unkn   | own         |

|               |               |                                                   |                           |                   | uicu            |                   | lowin       |

| bit 15        | U2TXIE: UAF   | RT2 Transmitter                                   | Interrupt Enal            | ble bit           |                 |                   |             |

|               |               | request is enab                                   | -                         |                   |                 |                   |             |

|               | 0 = Interrupt | request is not e                                  | nabled                    |                   |                 |                   |             |

| bit 14        |               | RT2 Receiver Ir                                   | •                         | e bit             |                 |                   |             |

|               |               | request is enab<br>request is not e               |                           |                   |                 |                   |             |

| bit 13        | •             | rnal Interrupt 2                                  |                           |                   |                 |                   |             |

| DIL 15        |               | request is enab                                   |                           |                   |                 |                   |             |

|               |               | request is not e                                  |                           |                   |                 |                   |             |

| bit 12        | T5IE: Timer5  | Interrupt Enab                                    | le bit                    |                   |                 |                   |             |

|               |               | request is enab                                   |                           |                   |                 |                   |             |

|               | -             | request is not e                                  |                           |                   |                 |                   |             |

| bit 11        |               | Interrupt Enab                                    |                           |                   |                 |                   |             |

|               |               | request is enab<br>request is not e               |                           |                   |                 |                   |             |

| bit 10        | •             | ut Compare Ch                                     |                           | ot Enable bit     |                 |                   |             |

|               | =             | request is enab                                   |                           | p                 |                 |                   |             |

|               |               | request is not e                                  |                           |                   |                 |                   |             |

| bit 9         | OC3IE: Outp   | ut Compare Ch                                     | annel 3 Interru           | pt Enable bit     |                 |                   |             |

|               |               | request is enab                                   |                           |                   |                 |                   |             |

| <b>h</b> # 0  | •             | request is not e                                  |                           | L :4              |                 |                   |             |

| bit 8         |               | IA Channel 2 In<br>request is enab                | -                         | DI                |                 |                   |             |

|               |               | request is enab                                   |                           |                   |                 |                   |             |

| bit 7-5       |               | ted: Read as '                                    |                           |                   |                 |                   |             |

| bit 4         | INT1IE: Exte  | rnal Interrupt 1                                  | Enable bit <sup>(1)</sup> |                   |                 |                   |             |

|               |               | request is enab<br>request is not e               |                           |                   |                 |                   |             |

| bit 3         | CNIE: Input ( | Change Notifica                                   | tion Interrupt E          | Enable bit        |                 |                   |             |

|               |               | request is enab<br>request is not e               |                           |                   |                 |                   |             |

| bit 2         | CMIE: Comp    | arator Interrupt                                  | Enable bit                |                   |                 |                   |             |

|               |               | request is enab                                   |                           |                   |                 |                   |             |

|               | 0 = Interrupt | request is not e                                  | nabled                    |                   |                 |                   |             |

|               |               | errupt is enabled<br>ormation, see <mark>S</mark> |                           |                   |                 | l to an available | RPn or RPIn |

### REGISTER 8-14: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

© 2013-2015 Microchip Technology Inc.

## REGISTER 8-24: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| U-0              | U-0                                                                   | U-0                                                                                              | U-0                                                 | U-0               | R/W-1            | R/W-0           | R/W-0   |

|------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------|------------------|-----------------|---------|

| _                |                                                                       |                                                                                                  |                                                     |                   | DMA1IP2          | DMA1IP1         | DMA1IP0 |

| pit 15           |                                                                       |                                                                                                  |                                                     |                   |                  |                 | bit     |

| U-0              | R/W-1                                                                 | R/W-0                                                                                            | R/W-0                                               | U-0               | R/W-1            | R/W-0           | R/W-0   |

| —                | AD1IP2                                                                | AD1IP1                                                                                           | AD1IP0                                              | —                 | U1TXIP2          | U1TXIP1         | U1TXIP0 |

| bit 7            |                                                                       |                                                                                                  |                                                     |                   |                  |                 | bit     |

| Legend:          |                                                                       |                                                                                                  |                                                     |                   |                  |                 |         |

| R = Readal       | ole bit                                                               | W = Writable                                                                                     | bit                                                 | U = Unimplem      | nented bit, read | l as '0'        |         |

| -n = Value a     | at POR                                                                | '1' = Bit is set                                                                                 |                                                     | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

|                  |                                                                       |                                                                                                  |                                                     |                   |                  |                 |         |

| bit 15-11        | -                                                                     | nted: Read as '                                                                                  |                                                     |                   |                  |                 |         |

| oit 10-8         | DMA1IP<2:0                                                            | >: DMA Chann                                                                                     | el 1 Interrupt P                                    | riority bits      |                  |                 |         |

|                  | 111 = Interru                                                         | pt is Priority 7 (                                                                               | highest priority                                    | interrupt)        |                  |                 |         |

|                  | •                                                                     |                                                                                                  |                                                     |                   |                  |                 |         |

|                  | •                                                                     |                                                                                                  |                                                     |                   |                  |                 |         |

|                  |                                                                       | pt is Priority 1<br>pt source is dis                                                             | abled                                               |                   |                  |                 |         |

| bit 7            | Unimplemer                                                            | •<br>•ted: Read as '                                                                             | )'                                                  |                   |                  |                 |         |

| oit 6-4          | AD1IP<2:0>:                                                           | ADC1 Interrup                                                                                    | t Priority bits                                     |                   |                  |                 |         |

|                  |                                                                       |                                                                                                  |                                                     |                   |                  |                 |         |

|                  | 111 = Interru                                                         | pt is Priority 7 (                                                                               | highest priority                                    | interrupt)        |                  |                 |         |

|                  | 111 = Interru<br>•                                                    | pt is Priority 7(                                                                                | highest priority                                    | interrupt)        |                  |                 |         |

|                  | 111 = Interru<br>•                                                    | pt is Priority 7(                                                                                | highest priority                                    | interrupt)        |                  |                 |         |

|                  | •<br>•                                                                |                                                                                                  | highest priority                                    | interrupt)        |                  |                 |         |

|                  | •<br>•<br>001 = Interru                                               | pt is Priority 7(<br>pt is Priority 1<br>pt source is dis                                        |                                                     | interrupt)        |                  |                 |         |

| bit 3            | •<br>•<br>001 = Interru<br>000 = Interru                              | pt is Priority 1<br>pt source is dis                                                             | abled                                               | interrupt)        |                  |                 |         |

|                  | •<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemer                | pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as 'o                                  | abled                                               |                   |                  |                 |         |

|                  | •<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemer<br>U1TXIP<2:03 | pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as 'o<br>>: UART1 Trans                | abled<br>o'<br>smitter Interrup                     | t Priority bits   |                  |                 |         |

|                  | •<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemer<br>U1TXIP<2:03 | pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as 'o                                  | abled<br>o'<br>smitter Interrup                     | t Priority bits   |                  |                 |         |

|                  | •<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemer<br>U1TXIP<2:03 | pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as 'o<br>>: UART1 Trans                | abled<br>o'<br>smitter Interrup                     | t Priority bits   |                  |                 |         |

|                  | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•    | pt is Priority 1<br>pt source is dis<br>nted: Read as 'o<br>>: UART1 Trans<br>pt is Priority 7 ( | abled<br>o'<br>smitter Interrup                     | t Priority bits   |                  |                 |         |

| bit 3<br>bit 2-0 | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•    | pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as 'o<br>>: UART1 Trans                | abled<br>o'<br>smitter Interrup<br>highest priority | t Priority bits   |                  |                 |         |

## REGISTER 8-26: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0         | U-0    | U-0            | U-0 | U-0         | U-0             | U-0         | U-0   |

|-------------|--------|----------------|-----|-------------|-----------------|-------------|-------|

| —           | —      | —              | —   | —           | —               | —           | —     |

| bit 15      |        |                |     |             |                 |             | bit 8 |

|             |        |                |     |             |                 |             |       |

| U-0         | U-0    | U-0            | U-0 | U-0         | R/W-1           | R/W-0       | R/W-0 |

|             | —      | —              | _   | _           |                 | INT1IP<2:0> |       |

| bit 7       |        |                |     |             |                 |             | bit 0 |

|             |        |                |     |             |                 |             |       |

| Legend:     |        |                |     |             |                 |             |       |

| R = Readabl | le bit | W = Writable b | bit | U = Unimple | mented bit, rea | d as '0'    |       |

|                   |                  | • • • • • • • • • • • • • • • • • • • • |                    |

|-------------------|------------------|-----------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                    | x = Bit is unknown |

### bit 15-3 Unimplemented: Read as '0'

- INT1IP<2:0>: External Interrupt 1 Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

bit 2-0

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 SPI1RXIPO \_\_\_\_ SPI2RXIP2 SPI2RXIP1 SPI2RXIPO \_\_\_\_ SPI1RXIP2 SPI1RXIP1 bit 8 bit 15 U-0 U-0 U-0 U-0 U-0 R/W-1 R/W-0 R/W-0 **KEYSTRIP2** KEYSTRIP1 **KEYSTRIP0** bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 Unimplemented: Read as '0' bit 14-12 SPI2RXIP<2:0>: SPI2 Receive Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled bit 11 Unimplemented: Read as '0' bit 10-8 SPI1RXIP<2:0>: SPI1 Receive Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled bit 7-3 Unimplemented: Read as '0' bit 2-0 KEYSTRIP<2:0>: Cryptographic Key Store Program Done Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled

### REGISTER 8-35: IPC14: INTERRUPT PRIORITY CONTROL REGISTER 14

## REGISTER 11-23: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | RP1R5 | RP1R4 | RP1R3 | RP1R2 | RP1R1 | RP1R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP0R5 | RP0R4 | RP0R3 | RP0R2 | RP0R1 | RP0R0 |

| bit 7  |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP1R<5:0>: RP1 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP1 (see Table 11-4 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | RP0R<5:0>: RP0 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP0 (see Table 11-4 for peripheral function numbers). |

#### REGISTER 11-24: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| _      | _   | RP3R5 | RP3R4 | RP3R3 | RP3R2 | RP3R1 | RP3R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| _      | —   | RP2R5 | RP2R4 | RP2R3 | RP2R2 | RP2R1 | RP2R0 |

| bit 7  |     | -     |       |       | •     | •     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP3R<5:0>:** RP3 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP3 (see Table 11-4 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP2R<5:0>:** RP2 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP2 (see Table 11-4 for peripheral function numbers).

### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 4 OCFLT0: Output Compare x PWM Fault 0 (OCFA pin) Condition Status bit<sup>(2,4)</sup>

- 1 = PWM Fault 0 has occurred

- 0 = No PWM Fault 0 has occurred

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is only cleared by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode on  $OCx^{(2)}$

- 110 = Edge-Aligned PWM mode on  $OCx^{(2)}$

- 101 = Double Compare Continuous Pulse mode: Initializes the OCx pin low; toggles the OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes the OCx pin low; toggles the OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare Continuous Pulse mode: Compare events continuously toggle the OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high; compare event forces the OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low; compare event forces the OCx pin high

- 000 = Output compare channel is disabled

- Note 1: The OCx output must also be configured to an available RPn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

- 2: The Fault input enable and Fault status bits are valid when OCM<2:0> = 111 or 110.

- **3:** The Comparator 1 output controls the OC1-OC2 channels; Comparator 2 output controls the OC3-OC4 channels; Comparator 3 output controls the OC5-OC6 channels.

- 4: The OCFA/OCFB Fault input must also be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

## REGISTER 16-1: SPIxCON1L: SPIx CONTROL REGISTER 1 LOW (CONTINUED)

| bit 7   | SSEN: Slave Select Enable bit (Slave mode) <sup>(2)</sup>                                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = $\overline{SSx}$ pin is used by the macro in Slave mode; $\overline{SSx}$ pin is used as the slave select inpu 0 = SSx pin is not used by the macro (SSx pin will be controlled by the port I/O) |

| bit 6   | CKP: Clock Polarity Select bit                                                                                                                                                                       |

|         | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                             |

| bit 5   | MSTEN: Master Mode Enable bit                                                                                                                                                                        |

|         | 1 = Master mode<br>0 = Slave mode                                                                                                                                                                    |

| bit 4   | DISSDI: Disable SDIx Input Port bit                                                                                                                                                                  |

|         | <ul> <li>1 = SDIx pin is not used by the module; pin is controlled by the port function</li> <li>0 = SDIx pin is controlled by the module</li> </ul>                                                 |

| bit 3   | DISSCK: Disable SCKx Output Port bit                                                                                                                                                                 |

|         | <ul> <li>1 = SCKx pin is not used by the module; pin is controlled by the port function</li> <li>0 = SCKx pin is controlled by the module</li> </ul>                                                 |

| bit 2   | MCLKEN: Master Clock Enable bit <sup>(3)</sup>                                                                                                                                                       |

|         | <ul> <li>1 = MCLK is used by the BRG</li> <li>0 = PBCLK is used by the BRG</li> </ul>                                                                                                                |

| bit 1   | SPIFE: Frame Sync Pulse Edge Select bit                                                                                                                                                              |

|         | <ul> <li>1 = Frame Sync pulse (Idle-to-active edge) coincides with the first bit clock</li> <li>0 = Frame Sync pulse (Idle-to-active edge) precedes the first bit clock</li> </ul>                   |

| bit 0   | ENHBUF: Enhanced Buffer Mode Enable bit                                                                                                                                                              |

|         | <ol> <li>1 = Enhanced Buffer mode is enabled</li> <li>0 = Enhanced Buffer mode is disabled</li> </ol>                                                                                                |

| Note 1: | When AUDEN = 1, this module functions as if CKE = 0, regardless of its actual value.                                                                                                                 |

- **2:** When FRMEN = 1, SSEN is not used.

- **3:** MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

# 17.2 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator reload value, use Equation 17-1.

EQUATION 17-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1)</sup>

$$I2CxBRG = \left( \left( \frac{1}{FSCL} - PGDx \right) \times \frac{FCY}{2} \right) - 2$$

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

# 17.3 Slave Address Masking

The I2CxMSK register (Register 17-4) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond, whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '0010000000', the slave module will detect both addresses, '000000000' and '001000000'.

To enable address masking, the Intelligent Peripheral Management Interface (IPMI) must be disabled by clearing the STRICT bit (I2CxCONL<11>).

Note: As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 17-1 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| TABLE 17-1: | I <sup>2</sup> C <sup>™</sup> RESERVED ADDRESSES <sup>(1)</sup> |

|-------------|-----------------------------------------------------------------|

|-------------|-----------------------------------------------------------------|

| Slave Address | R/W Bit | Description                            |  |  |  |  |

|---------------|---------|----------------------------------------|--|--|--|--|

| 0000 000      | 0       | General Call Address <sup>(2)</sup>    |  |  |  |  |

| 0000 000      | 1       | Start Byte                             |  |  |  |  |

| 0000 001      | Х       | Cbus Address                           |  |  |  |  |

| 0000 01x      | х       | Reserved                               |  |  |  |  |

| 0000 1xx      | Х       | HS Mode Master Code                    |  |  |  |  |

| 1111 0xx      | х       | 10-Bit Slave Upper Byte <sup>(3)</sup> |  |  |  |  |

| 1111 1xx      | Х       | Reserved                               |  |  |  |  |

**Note 1:** The address bits listed here will never cause an address match independent of address mask settings.

2: The address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

## REGISTER 19-11: U1SOF: USB OTG START-OF-FRAME COUNT REGISTER (HOST MODE ONLY)

| U-0            | U-0   | U-0             | U-0   | U-0          | U-0              | U-0      | U-0   |

|----------------|-------|-----------------|-------|--------------|------------------|----------|-------|

| —              |       | —               | _     | —            |                  | _        |       |

| bit 15         |       | · · · · ·       |       |              |                  |          | bit 8 |

|                |       |                 |       |              |                  |          |       |

| R/W-0          | R/W-0 | R/W-0           | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                |       |                 | CNT   | <7:0>        |                  |          |       |

| bit 7          |       |                 |       |              |                  |          | bit 0 |

|                |       |                 |       |              |                  |          |       |

| Legend:        |       |                 |       |              |                  |          |       |

| R = Readable b | it    | W = Writable bi | t     | U = Unimplen | nented bit, read | 1 as '0' |       |

| R – Reauable bit  |                  | 0 – Onimplemented bit, rea |                    |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 CNT<7:0>: Start-of-Frame Size bits

Value represents 10 + (packet size of n bytes). For example:

0100 1010 = 64-byte packet

0010 1010 = **32-byte packet** 0001 0010 = **8-byte packet**

## 22.2 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- Alarm Value Registers

### 22.2.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value register window (RTCVALH and RTCVALL) uses the RTCPTRx bits (RCFGCAL<9:8>) to select the desired Timer register pair (see Table 22-1).

By writing the RTCVALH byte, the RTCPTR<1:0> bits (the RTCC Pointer value) decrement by one until they reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 22-1: RTCVAL REGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Window |             |  |  |  |  |

|-------------|----------------------------|-------------|--|--|--|--|

| RICPIRSI.02 | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |  |

| 00          | MINUTES                    | SECONDS     |  |  |  |  |

| 01          | WEEKDAY                    | HOURS       |  |  |  |  |

| 10          | MONTH                      | DAY         |  |  |  |  |

| 11          | —                          | YEAR        |  |  |  |  |

The Alarm Value register window (ALRMVALH and ALRMVALL) uses the ALRMPTRx bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 22-2).

By writing the ALRMVALH byte, the ALRMPTR<1:0> bits (the Alarm Pointer value) decrement by one until they reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL until the pointer value is manually changed.

#### TABLE 22-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |  |

|---------|-----------------------------|--------------|--|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |  |

| 00      | ALRMMIN                     | ALRMSEC      |  |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |  |

| 11      | _                           | _            |  |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes, the ALRMPTR<1:0> value will be decremented. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note: | This only applies to read operations and |

|-------|------------------------------------------|

|       | not write operations.                    |

## 22.2.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RCFGCAL<13>) must be set (see Example 22-1).

| Note: | To avoid accidental writes to the timer, it is<br>recommended that the RTCWREN bit<br>(RCFGCAL<13>) is kept clear at any<br>other time. For the RTCWREN bit to be<br>set, there is only one instruction cycle time<br>window allowed between the 55h/AA<br>sequence and the setting of RTCWREN;<br>therefore, it is recommended that code |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | therefore, it is recommended that code follow the procedure in Example 22-1.                                                                                                                                                                                                                                                              |

## 22.2.3 SELECTING RTCC CLOCK SOURCE

The clock source for the RTCC module can be selected using the RTCLK<1:0> bits in the RTCPWC register. When the bits are set to '00', the Secondary Oscillator (SOSC) is used as the reference clock and when the bits are '01', LPRC is used as the reference clock. When RTCLK<1:0> = 10 and 11, the external power line (50 Hz and 60 Hz) is used as the clock source.

### EXAMPLE 22-1: SETTING THE RTCWREN BIT

```

asm volatile("push w7");

asm volatile("push w8");

asm volatile("disi #5");

asm volatile("mov #0x55, w7");

asm volatile("mov w7, _NVMKEY");

asm volatile("mov #0xAA, w8");

asm volatile("mov w8, _NVMKEY");

asm volatile("bset _RCFGCAL, #13"); //set the RTCWREN bit

asm volatile("pop w8");

asm volatile("pop w7");

```

## REGISTER 24-3: CRCXORL: CRC XOR POLYNOMIAL REGISTER, LOW BYTE

| R/W-0                             | R/W-0 | R/W-0            | R/W-0        | R/W-0                                   | R/W-0    | R/W-0 | R/W-0 |

|-----------------------------------|-------|------------------|--------------|-----------------------------------------|----------|-------|-------|

|                                   |       |                  | Χ<           | :15:8>                                  |          |       |       |

| bit 15                            |       |                  |              |                                         |          |       | bit 8 |

|                                   |       |                  |              |                                         |          |       |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0        | R/W-0                                   | R/W-0    | R/W-0 | U-0   |

|                                   |       |                  | X<7:1>       |                                         |          |       | —     |

| bit 7                             |       |                  |              |                                         |          |       | bit 0 |

| Legend:                           |       |                  |              |                                         |          |       |       |

| R = Readable bit W = Writable bit |       |                  | U = Unimplem | nented bit, read                        | d as '0' |       |       |

| -n = Value at F                   | POR   | '1' = Bit is set |              | '0' = Bit is cleared x = Bit is unknown |          |       | nown  |

bit 15-1 X<15:1>: XOR of Polynomial Term x<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '0'

### REGISTER 24-4: CRCXORH: CRC XOR POLYNOMIAL REGISTER, HIGH BYTE

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0  | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|--------|-----------------|-------|-------|

|                                    |       |       | Χ<                                 | 31:24> |                 |       |       |

| bit 15                             |       |       |                                    |        |                 |       | bit 8 |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0  | R/W-0           | R/W-0 | R/W-0 |

|                                    |       |       | Χ<                                 | 23:16> |                 |       |       |

| bit 7                              |       |       |                                    |        |                 |       | bit C |

| Legend:                            |       |       |                                    |        |                 |       |       |

| R = Readable bit W = Writable bit  |       | bit   | U = Unimplemented bit, read as '0' |        |                 |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is clea                  | ared   | x = Bit is unkr | nown  |       |

bit 15-0 X<31:16>: XOR of Polynomial Term x<sup>n</sup> Enable bits

### REGISTER 25-9: AD1CSSH: ADC1 INPUT SCAN SELECT REGISTER (HIGH WORD)

| R/W-0   | R/W-0 | R/W-0      | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|---------|-------|------------|-------|-------|-----|-----|-------|

|         |       | CSS<31:27> |       |       |     |     | —     |

| bit 15  |       |            |       |       |     |     | bit 8 |

|         |       |            |       |       |     |     |       |

| U-0     | U-0   | U-0        | U-0   | U-0   | U-0 | U-0 | U-0   |

| —       | —     | —          | —     | —     | —   | —   | —     |

| bit 7   |       |            |       |       |     |     | bit 0 |

|         |       |            |       |       |     |     |       |

| Legend: |       |            |       |       |     |     |       |

| Logona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-11 CSS<31:27>: ADC1 Input Scan Selection bits 1 = Includes corresponding channel for input scan

0 = Skips channel for input scan

## REGISTER 25-10: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER (LOW WORD)

| U-0    | R/W-0                    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0   |

|--------|--------------------------|-------|-------|-------|-------|-------|-------|

| —      | CSS<14:9> <sup>(1)</sup> |       |       |       |       | —     |       |

| bit 15 |                          |       |       |       |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | CSS   | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

- bit 14-9CSS<14:9>: ADC1 Input Scan Selection bits(1)1 = Includes corresponding channel for input scan0 = Skips channel for input scanbit 8Unimplemented: Read as '0'bit 7-0CSS<7:0>: ADC1 Input Scan Selection bits1 = Includes corresponding channel for input scan

- 0 = Skips channel for input scan

bit 10-0 Unimplemented: Read as '0'

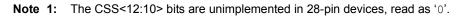

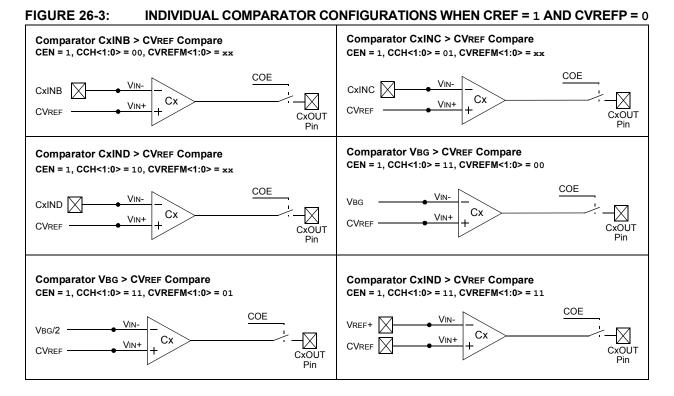

## FIGURE 26-4: INDIVIDUAL COMPARATOR CONFIGURATIONS WHEN CREF = 1 AND CVREFP = 1

| R/W-0         | U-0                                                                                                                                                   | R/W-0                                  | U-0           | U-0                                    | U-0              | U-0             | U-0             |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------|----------------------------------------|------------------|-----------------|-----------------|--|--|

| HLVDEN        | —                                                                                                                                                     | LSIDL                                  |               | _                                      | —                |                 | —               |  |  |

| bit 15        |                                                                                                                                                       |                                        |               |                                        |                  |                 | bit 8           |  |  |

|               |                                                                                                                                                       |                                        |               |                                        |                  |                 |                 |  |  |

| R/W-0         | R/W-0                                                                                                                                                 | R/W-0                                  | U-0           | R/W-0                                  | R/W-0            | R/W-0           | R/W-0           |  |  |

| VDIR          | BGVST                                                                                                                                                 | IRVST                                  |               | HLVDL3                                 | HLVDL2           | HLVDL1          | HLVDL0          |  |  |

| bit 7         |                                                                                                                                                       |                                        |               |                                        |                  |                 | bit             |  |  |

| Legend:       |                                                                                                                                                       |                                        |               |                                        |                  |                 |                 |  |  |

| R = Readabl   | e bit                                                                                                                                                 | W = Writable I                         | oit           | U = Unimplem                           | nented bit, read | d as '0'        |                 |  |  |

| -n = Value at | POR                                                                                                                                                   | '1' = Bit is set                       |               | '0' = Bit is clea                      | ared             | x = Bit is unkr | nown            |  |  |

|               |                                                                                                                                                       |                                        |               |                                        |                  |                 |                 |  |  |

| bit 15        | HLVDEN: Hi                                                                                                                                            | gh/Low-Voltage                         | Detect Powe   | r Enable bit                           |                  |                 |                 |  |  |

|               | 1 = HLVD is<br>0 = HLVD is                                                                                                                            |                                        |               |                                        |                  |                 |                 |  |  |

| bit 14        |                                                                                                                                                       | nted: Read as '0                       | ,             |                                        |                  |                 |                 |  |  |

| bit 13        | -                                                                                                                                                     |                                        |               |                                        |                  |                 |                 |  |  |

| DIL 15        | LSIDL: HLVD Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode                                                   |                                        |               |                                        |                  |                 |                 |  |  |

|               | 0 = Continues module operation in Idle mode                                                                                                           |                                        |               |                                        |                  |                 |                 |  |  |

| bit 12-8      | Unimplemented: Read as '0'                                                                                                                            |                                        |               |                                        |                  |                 |                 |  |  |

| bit 7         | VDIR: Voltage Change Direction Select bit                                                                                                             |                                        |               |                                        |                  |                 |                 |  |  |

|               |                                                                                                                                                       |                                        |               | exceeds the trip<br>falls below the tr |                  |                 |                 |  |  |

| bit 6         | BGVST: Band Gap Voltage Stable Flag bit                                                                                                               |                                        |               |                                        |                  |                 |                 |  |  |

|               |                                                                                                                                                       | s that the band g<br>s that the band g | •             |                                        |                  |                 |                 |  |  |

| bit 5         | IRVST: Internal Reference Voltage Stable Flag bit                                                                                                     |                                        |               |                                        |                  |                 |                 |  |  |

|               | 1 = Internal reference voltage is stable; the High-Voltage Detect logic generates the interrupt flag at the specified voltage range                   |                                        |               |                                        |                  |                 |                 |  |  |

|               |                                                                                                                                                       |                                        |               | ; the High-Voltag<br>d the HLVD inter  |                  |                 | te the interrup |  |  |

| bit 4         | Unimpleme                                                                                                                                             | nted: Read as 'o                       | )'            |                                        |                  |                 |                 |  |  |

| bit 3-0       | HLVDL<3:0>                                                                                                                                            | High/Low-Volt                          | age Detection | n Limit bits                           |                  |                 |                 |  |  |

|               | <pre>1111 = External analog input is used (input comes from the HLVDIN pin) 1110 = Trip Point 1<sup>(1)</sup> 1101 = Trip Point 2<sup>(1)</sup></pre> |                                        |               |                                        |                  |                 |                 |  |  |

|               | 1100 <b>= Trip</b>                                                                                                                                    | Point 30                               |               |                                        |                  |                 |                 |  |  |

|               | •                                                                                                                                                     |                                        |               |                                        |                  |                 |                 |  |  |

|               | •<br>0100 = Trip Point 11 <sup>(1)</sup>                                                                                                              |                                        |               |                                        |                  |                 |                 |  |  |

|               | 0100 - Trin                                                                                                                                           | Doint 11(1)                            |               |                                        |                  |                 |                 |  |  |

### REGISTER 29-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

## REGISTER 30-3: CW3: FLASH CONFIGURATION WORD 3 (CONTINUED)

- bit 7

Reserved: Always maintain as '1'

bit 6-0

WPFP<6:0>: Write-Protected Code Segment Boundary Page bits<sup>(3)</sup>

Designates the 512 instruction words page boundary of the protected Code Segment.

If WPEND = 1:

Specifies the lower page boundary of the protected Code Segment; the last page being the last implemented page in the device.

If WPEND = 0:

Specifies the upper page boundary of the protected Code Segment; Page 0 being the lower boundary.

- **Note 1:** Regardless of WPCFG status, if WPEND = 1 or if the WPFP<6:0> bits correspond to the Configuration Word page, the Configuration Word page is protected.

- 2: Ensure that the SCLKI pin is made a digital input while using this configuration (see Table 11-1).

- 3: For the 64K devices (PIC24FJ64GB2XX), maintain WPFP6 as '0'.

- 4: This Configuration bit only takes effect when PLL is not being used.

| Assembly<br>Mnemonic |        | Assembly Syntax  | Description                                                                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|------------------|------------------------------------------------------------------------------------------|---------------|----------------|--------------------------|

| GOTO                 | GOTO   | Expr             | Go to Address                                                                            | 2             | 2              | None                     |

|                      | GOTO   | Wn               | Go to Indirect                                                                           | 1             | 2              | None                     |

| INC                  | INC    | f                | f = f + 1                                                                                | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | f,WREG           | WREG = f + 1                                                                             | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | Ws,Wd            | Wd = Ws + 1                                                                              | 1             | 1              | C, DC, N, OV, Z          |

| INC2                 | INC2   | f                | f = f + 2                                                                                | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | f,WREG           | WREG = f + 2                                                                             | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | Ws,Wd            | Wd = Ws + 2                                                                              | 1             | 1              | C, DC, N, OV, Z          |

| IOR                  | IOR    | f                | f = f .IOR. WREG                                                                         | 1             | 1              | N, Z                     |

|                      | IOR    | f,WREG           | WREG = f .IOR. WREG                                                                      | 1             | 1              | N, Z                     |

|                      | IOR    | #lit10,Wn        | Wd = lit10 .IOR. Wd                                                                      | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,Ws,Wd         | Wd = Wb .IOR. Ws                                                                         | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,#lit5,Wd      | Wd = Wb .IOR. lit5                                                                       | 1             | 1              | N, Z                     |

| LNK                  | LNK    | #lit14           | Link Frame Pointer                                                                       | 1             | 1              | None                     |

| LSR                  | LSR    | f                | f = Logical Right Shift f                                                                | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | f,WREG           | WREG = Logical Right Shift f                                                             | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Ws,Wd            | Wd = Logical Right Shift Ws                                                              | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Wb, Wns, Wnd     | Wnd = Logical Right Shift Wb by Wns                                                      | 1             | 1              | N, Z                     |

|                      | LSR    | Wb,#lit5,Wnd     | Wnd = Logical Right Shift Wb by lit5                                                     | 1             | 1              | N, Z                     |

| MOV                  | MOV    | f,Wn             | Move f to Wn                                                                             | 1             | 1              | None                     |