#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                     |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT        |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb202-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

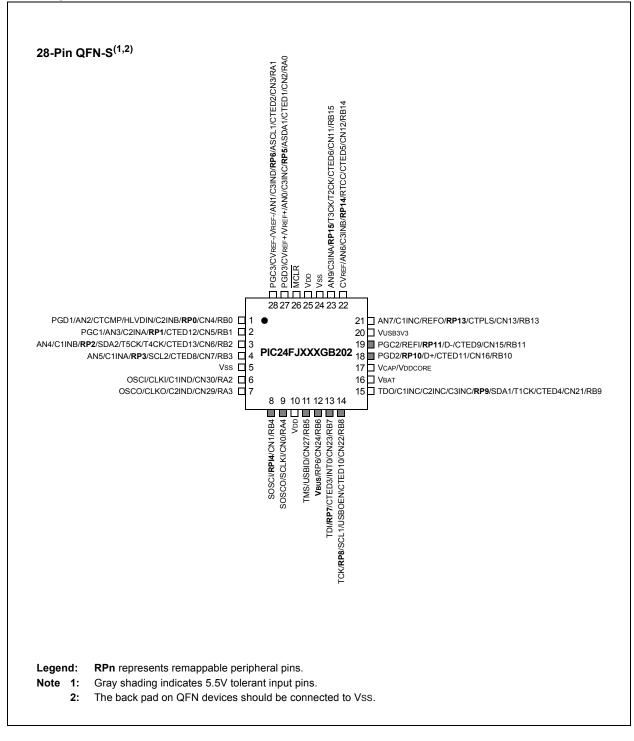

### **Pin Diagrams (Continued)**

|                      | Pin Num                       | per/Grid        | Locator            |     |                 |                                            |

|----------------------|-------------------------------|-----------------|--------------------|-----|-----------------|--------------------------------------------|

| Pin Function         | 28-Pin<br>SPDIP/SOIC/<br>SSOP | 28-Pin<br>QFN-S | 44-Pin<br>TQFP/QFN | I/O | Input<br>Buffer | Description                                |

| PMA0/PMALL           | _                             | —               | 3                  | 0   |                 | Parallel Master Port Address.              |

| PMA1/PMALH           |                               |                 | 2                  | 0   | _               |                                            |

| PMA14/PMCS/<br>PMCS1 | -                             | —               | 15                 | 0   | —               |                                            |

| PMA2/PMALU           | —                             | —               | 12                 | 0   | _               |                                            |

| PMA3                 | —                             |                 | 38                 | 0   | _               |                                            |

| PMA4                 |                               |                 | 37                 | 0   | _               |                                            |

| PMA5                 | _                             |                 | 4                  | 0   | _               |                                            |

| PMA6                 |                               |                 | 5                  | 0   | _               |                                            |

| PMA7                 | _                             | _               | 13                 | 0   | _               |                                            |

| PMA8                 |                               |                 | 32                 | 0   | _               |                                            |

| PMA9                 |                               |                 | 35                 | 0   | _               |                                            |

| PMACK1               |                               | —               | 27                 | Ι   | ST/TTL          | Parallel Master Port Acknowledge Input 1.  |

| PMBE0                |                               | _               | 36                 | 0   | _               | Parallel Master Port Byte Enable 0 Strobe. |

| PMBE1                |                               | —               | 25                 | 0   | _               | Parallel Master Port Byte Enable 1 Strobe. |

| PMCS1                |                               | _               | 30                 | I/O | ST/TTL          | Parallel Master Port Chip Select 1 Strobe. |

| PMD0                 |                               |                 | 21                 | I/O | ST/TTL          | Parallel Master Port Data (Demultiplexed   |

| PMD1                 | _                             |                 | 22                 | I/O | ST/TTL          | Master mode) or Address/Data (Multiplexed  |

| PMD2                 |                               | —               | 23                 | I/O | ST/TTL          | Master modes).                             |

| PMD3                 |                               |                 | 1                  | I/O | ST/TTL          |                                            |

| PMD4                 |                               |                 | 44                 | I/O | ST/TTL          |                                            |

| PMD5                 |                               |                 | 43                 | I/O | ST/TTL          |                                            |

| PMD6                 |                               |                 | 20                 | I/O | ST/TTL          |                                            |

| PMD7                 |                               |                 | 19                 | I/O | ST/TTL          |                                            |

| PMRD                 |                               |                 | 11                 | 0   | _               | Parallel Master Port Read Strobe.          |

| PMWR                 | _                             | —               | 24                 | 0   | —               | Parallel Master Port Write Strobe.         |

| RA0                  | 2                             | 27              | 19                 | I/O | ST              | PORTA Digital I/Os.                        |

| RA1                  | 3                             | 28              | 20                 | I/O | ST              |                                            |

| RA2                  | 9                             | 6               | 30                 | I/O | ST              |                                            |

| RA3                  | 10                            | 7               | 31                 | I/O | ST              |                                            |

| RA4                  | 12                            | 9               | 34                 | Ι   | ST              |                                            |

| RA7                  | _                             | —               | 13                 | I/O | ST              |                                            |

| RA8                  | _                             | —               | 32                 | I/O | ST              |                                            |

|                      |                               | —               | 35                 | I/O | ST              |                                            |

| RA9                  |                               |                 | 1                  |     | ST              | 1                                          |

### TABLE 1-3: PIC24FJ128GB204 FAMILY PINOUT DESCRIPTION (CONTINUED)

$I^2C$  = ST with  $I^2C^{TM}$  or SMBus levels

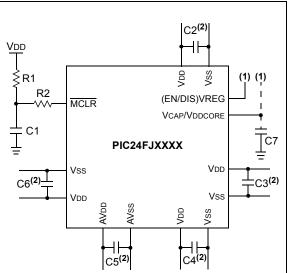

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC24FJ128GB204 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin

(see Section 2.3 "Master Clear (MCLR) Pin")

- ENVREG/DISVREG and VCAP/VDDCORE pins (see Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

#### FIGURE 2-1: RECOMMENDED

#### MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1 µF, 20V ceramic

C7: 10  $\mu\text{F},$  6.3V or greater, tantalum or ceramic R1: 10  $k\Omega$

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)" for the explanation of the ENVREG/DISVREG pin connections.

- 2: The example shown is for a PIC24F device with five VDD/VSs and AVDD/AVss pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

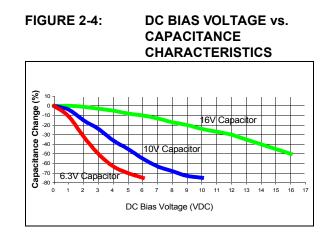

### 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

Typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 2.5V or 1.8V core voltage. Suggested capacitors are shown in Table 2-1.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 31.0 "Development Support"**.

| U-0          | R/W-1                                                                                     | R/W-0                                                                                                                             | R/W-0            | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |

|--------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------|-----------------|---------|--|--|--|

| _            | SPI3TXIP2                                                                                 | SPI3TXIP1                                                                                                                         | SPI3TXIP0        | _                | SPI3IP2         | SPI3IP1         | SPI3IP0 |  |  |  |

| bit 15       |                                                                                           |                                                                                                                                   |                  |                  |                 | •               | bit     |  |  |  |

|              |                                                                                           |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

| U-0          | R/W-1                                                                                     | R/W-0                                                                                                                             | R/W-0            | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |

|              | U4TXIP2                                                                                   | U4TXIP1                                                                                                                           | U4TXIP0          | —                | U4RXIP2         | U4RXIP1         | U4RXIP0 |  |  |  |

| bit 7        |                                                                                           |                                                                                                                                   |                  |                  |                 |                 | bit     |  |  |  |

| Legend:      |                                                                                           |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

| R = Readab   | le bit                                                                                    | W = Writable                                                                                                                      | bit              | U = Unimple      | mented bit, rea | d as '0'        |         |  |  |  |

| -n = Value a | It POR                                                                                    | '1' = Bit is set                                                                                                                  |                  | '0' = Bit is cle | eared           | x = Bit is unkr | nown    |  |  |  |

| bit 15       | Unimplemen                                                                                | ted: Read as '                                                                                                                    | )'               |                  |                 |                 |         |  |  |  |

| bit 14-12    | -                                                                                         | 0>: SPI3 Trans                                                                                                                    |                  | riority bits     |                 |                 |         |  |  |  |

|              | 111 = Interru                                                                             | pt is Priority 7 (                                                                                                                | highest priority | / interrupt)     |                 |                 |         |  |  |  |

|              | •                                                                                         |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              | •                                                                                         |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              | 001 = Interrupt is Priority 1                                                             |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              | -                                                                                         | ot source is dis                                                                                                                  |                  |                  |                 |                 |         |  |  |  |

| bit 11       | -                                                                                         | ted: Read as '                                                                                                                    |                  |                  |                 |                 |         |  |  |  |

| bit 10-8     | SPI3IP<2:0>: SPI3 General Interrupt Priority bits                                         |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> <li>•</li> </ul> |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              | •                                                                                         |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              | •                                                                                         |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              | 001 = Interru                                                                             | pt is Priority 1<br>ot source is dis                                                                                              | ablad            |                  |                 |                 |         |  |  |  |

| bit 7        | -                                                                                         | ted: Read as '                                                                                                                    |                  |                  |                 |                 |         |  |  |  |

| bit 6-4      | -                                                                                         |                                                                                                                                   |                  | t Priority hite  |                 |                 |         |  |  |  |

| Dit 0-4      |                                                                                           | <b>U4TXIP&lt;2:0&gt;:</b> UART4 Transmitter Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                  |                  |                 |                 |         |  |  |  |

|              | •                                                                                         | (                                                                                                                                 | g.ieet prienty   |                  |                 |                 |         |  |  |  |

|              | •                                                                                         |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              | •<br>001 = Interrup                                                                       | ot is Priority 1                                                                                                                  |                  |                  |                 |                 |         |  |  |  |

|              |                                                                                           | ot source is dis                                                                                                                  | abled            |                  |                 |                 |         |  |  |  |

| bit 3        | Unimplemen                                                                                | ted: Read as '                                                                                                                    | )'               |                  |                 |                 |         |  |  |  |

| bit 2-0      | U4RXIP<2:0>: UART4 Receiver Interrupt Priority bits                                       |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              | 111 = Interrup                                                                            | ot is Priority 7 (                                                                                                                | highest priority | interrupt)       |                 |                 |         |  |  |  |

|              | •                                                                                         |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              | •                                                                                         |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              |                                                                                           |                                                                                                                                   |                  |                  |                 |                 |         |  |  |  |

|              | 001 = Interrup                                                                            | ot is Priority 1                                                                                                                  |                  |                  |                 |                 |         |  |  |  |

#### REGISTER 8-42: IPC22: INTERRUPT PRIORITY CONTROL REGISTER 22

| U-0                | R/W-0                                      | R/W-0                                                                                                                          | R/W-0                                                | R/W-0                                                    | R/W-0                            | R/W-0                      | R/W-0        |

|--------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------|----------------------------------|----------------------------|--------------|

| _                  |                                            |                                                                                                                                |                                                      | RODIV<14:8>                                              |                                  |                            |              |

| bit 15             |                                            |                                                                                                                                |                                                      |                                                          |                                  |                            | bit 8        |

| R/W-0              | R/W-0                                      | R/W-0                                                                                                                          | R/W-0                                                | R/W-0                                                    | R/W-0                            | R/W-0                      | R/W-0        |

|                    |                                            |                                                                                                                                | RODI                                                 | V<7:0>                                                   |                                  |                            |              |

| bit 7              |                                            |                                                                                                                                |                                                      |                                                          |                                  |                            | bit C        |

| Legend:            |                                            |                                                                                                                                |                                                      |                                                          |                                  |                            |              |

| R = Readat         | ole bit                                    | W = Writable bit                                                                                                               |                                                      | U = Unimplem                                             | ented bit, read                  | 1 as '0'                   |              |

| -n = Value a       | at POR                                     | '1' = Bit is set                                                                                                               |                                                      | '0' = Bit is clea                                        |                                  | x = Bit is unkr            | iown         |

| bit 15<br>bit 14-0 | RODIV<14:0<br>Specifies the<br>For example | nted: Read as '0'<br>>: Reference Osci<br>e 1/2 period of the r<br>:: Period of ref_clk_<br>111111 = REFO c<br>111110 = REFO c | eference closed<br>output $\leq$ [R<br>lock is the b | ock in the source<br>eference Source<br>base clock frequ | e * 2] * RODIV<br>ency divided b | y 65,534 (32,7             |              |

|                    | 000000000<br>000000000                     | 000011 = REFO c<br>000010 = REFO c<br>000001 = REFO c<br>000000 = REFO c                                                       | lock is the b<br>lock is the b                       | base clock freque                                        | ency divided b<br>ency divided b | y 4 (2 * 2)<br>y 2 (1 * 2) | y <b>(1)</b> |

#### REGISTER 9-5: REFOCONH: REFERENCE OSCILLATOR CONTROL HIGH REGISTER

Note 1: The ROTRIMx values are ignored.

NOTES:

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

| R/W-0        | R/W-0                            | R/W-0                               | R/W-0                        | U-0               | R/W-0               | R/W-0               | R/W-0         |

|--------------|----------------------------------|-------------------------------------|------------------------------|-------------------|---------------------|---------------------|---------------|

| FLTMD        | FLTOUT                           | FLTTRIEN                            | OCINV                        | —                 | DCB1 <sup>(3)</sup> | DCB0 <sup>(3)</sup> | OC32          |

| bit 15       |                                  |                                     | •                            | •                 | •                   | •                   | bit 8         |

|              |                                  |                                     |                              |                   |                     |                     |               |

| R/W-0        | R/W-0, HS                        | R/W-0                               | R/W-0                        | R/W-1             | R/W-1               | R/W-0               | R/W-0         |

| OCTRIG       | TRIGSTAT                         | OCTRIS                              | SYNCSEL4                     | SYNCSEL3          | SYNCSEL2            | SYNCSEL1            | SYNCSEL0      |

| bit 7        |                                  |                                     |                              |                   |                     |                     | bit (         |

|              |                                  |                                     |                              |                   |                     |                     |               |

| Legend:      |                                  | HS = Hardwa                         | re Settable bit              |                   |                     |                     |               |

| R = Readal   | ble bit                          | W = Writable                        | bit                          | U = Unimplen      | nented bit, read    | d as '0'            |               |

| -n = Value a | at POR                           | '1' = Bit is set                    |                              | '0' = Bit is clea | ared                | x = Bit is unkn     | nown          |

|              |                                  |                                     |                              |                   |                     |                     |               |

| bit 15       | FLTMD: Faul                      | t Mode Select I                     | oit                          |                   |                     |                     |               |

|              |                                  |                                     | ed until the Fau             | It source is ren  | noved and the       | corresponding       | OCFLT0 bit i  |

|              |                                  | n software<br>de is maintaine       | d until the Faul             | lt source is rem  | oved and a ne       | w PWM period        | etarte        |

| bit 14       | FLTOUT: Fau                      |                                     |                              |                   |                     |                     | 510/15        |

|              |                                  | put is driven hig                   | oh on a Fault                |                   |                     |                     |               |

|              |                                  | put is driven lov                   |                              |                   |                     |                     |               |

| bit 13       | FLTTRIEN: F                      | ault Output Sta                     | te Select bit                |                   |                     |                     |               |

|              |                                  |                                     | t on a Fault cor             |                   |                     |                     |               |

|              |                                  |                                     | ected by a Fau               | llt               |                     |                     |               |

| bit 12       |                                  | ut Compare x I                      | nvert bit                    |                   |                     |                     |               |

|              | 1 = OCx outp                     | ut is inverted<br>ut is not inverte | d                            |                   |                     |                     |               |

| bit 11       | •                                | ted: Read as '                      |                              |                   |                     |                     |               |

| bit 10-9     | •                                |                                     | e Least Signific             | ant hite(3)       |                     |                     |               |

| DIL 10-9     |                                  |                                     | e by $\frac{3}{4}$ of the ir |                   | <b>`</b>            |                     |               |

|              |                                  |                                     | e by $\frac{1}{2}$ of the ir |                   |                     |                     |               |

|              |                                  |                                     | e by ¼ of the in             |                   |                     |                     |               |

|              |                                  |                                     | s at the start of            |                   | -                   |                     |               |

| bit 8        |                                  |                                     | odules Enable b              | oit (32-bit opera | ation)              |                     |               |

|              |                                  | module operati<br>module operati    |                              |                   |                     |                     |               |

| bit 7        |                                  | •                                   | Trigger/Sync S               | Select hit        |                     |                     |               |

|              |                                  |                                     | ource designate              |                   | CSELx bits          |                     |               |

|              |                                  |                                     | the source desi              |                   |                     | s                   |               |

| bit 6        | TRIGSTAT: ⊺                      | imer Trigger St                     | atus bit                     |                   |                     |                     |               |

|              |                                  |                                     | riggered and is              | •                 |                     |                     |               |

|              |                                  |                                     | en triggered an              | -                 |                     |                     |               |

| bit 5        |                                  |                                     | Output Pin Dir               | ection Select b   | vit                 |                     |               |

|              | 1 = OCx pin is<br>0 = Output Co  |                                     | eral x is connec             | ted to an OCx     | pin                 |                     |               |

|              | Never use an OC                  | x module as its                     |                              |                   | -                   | mode or anothe      | er equivalent |

|              | SYNCSELx settir Use these inputs | -                                   | ces only and n               | aver se evine or  |                     |                     |               |

| 2:           |                                  | as ingger sour                      | Ces only and the             | ever as sync st   |                     |                     |               |

3: The DCB<1:0> bits are double-buffered in PWM modes only (OCM<2:0> (OCxCON1<2:0>) = 111, 110).

#### REGISTER 16-2: SPIxCON1H: SPIx CONTROL REGISTER 1 HIGH

| R/W-0               | R/W-0                            | R/W-0                               | R/W-0                       | R/W-0                                  | R/W-0                   | R/W-0                  | R/W-0                  |

|---------------------|----------------------------------|-------------------------------------|-----------------------------|----------------------------------------|-------------------------|------------------------|------------------------|

| AUDEN <sup>(1</sup> | ) SPISGNEXT                      | IGNROV                              | IGNTUR                      | AUDMONO <sup>(2)</sup>                 | URDTEN <sup>(3)</sup>   | AUDMOD1 <sup>(4)</sup> | AUDMOD0 <sup>(4)</sup> |

| bit 15              |                                  |                                     |                             | -                                      |                         |                        | bit 8                  |

|                     |                                  |                                     |                             |                                        |                         |                        |                        |

| R/W-0               | R/W-0                            | R/W-0                               | R/W-0                       | R/W-0                                  | R/W-0                   | R/W-0                  | R/W-0                  |

| FRMEN               | FRMSYNC                          | FRMPOL                              | MSSEN                       | FRMSYPW                                | FRMCNT2                 | FRMCNT1                | FRMCNT0                |

| bit 7               |                                  |                                     |                             |                                        |                         |                        | bit C                  |

|                     |                                  |                                     |                             |                                        |                         |                        |                        |

| Legend:             |                                  |                                     |                             |                                        |                         |                        |                        |

| R = Reada           | able bit                         | W = Writable                        | bit                         | U = Unimplem                           | ented bit, read         | as '0'                 |                        |

| -n = Value          | at POR                           | '1' = Bit is set                    |                             | '0' = Bit is clea                      | red                     | x = Bit is unkr        | iown                   |

|                     |                                  |                                     |                             |                                        |                         |                        |                        |

| bit 15              | AUDEN: Audi                      | o Codec Supp                        | ort Enable bit <sup>(</sup> | 1)                                     |                         |                        |                        |

|                     |                                  |                                     |                             | ntrols the directio                    |                         |                        |                        |

|                     |                                  | le functions as<br>s of their actua |                             | , FRMSYNC = N                          | ISTEN, FRMC             | NT<2:0> = 001          | and SMP = $0$ ,        |

|                     |                                  | tocol is disable                    |                             |                                        |                         |                        |                        |

| bit 14              | SPISGNEXT:                       | SPIx Sign-Exte                      | end RX FIFO                 | Read Data Enab                         | le bit                  |                        |                        |

|                     |                                  | RX FIFO is sig                      |                             |                                        |                         |                        |                        |

|                     | 0 = Data from                    | RX FIFO is no                       | t sign-extende              | ed                                     |                         |                        |                        |

| bit 13              | IGNROV: Igno                     |                                     |                             |                                        |                         |                        |                        |

|                     |                                  |                                     | DV) is NOT a (              | critical error; duri                   | ing ROV, data           | in the FIFO is r       | not overwritten        |

|                     | by the rec                       | a critical error                    | that stops SP               | Loperation                             |                         |                        |                        |

| bit 12              | IGNTUR: Igno                     |                                     |                             | roperation                             |                         |                        |                        |

|                     | -                                |                                     |                             | critical error an                      | d data indicate         | d by URDTEN            | is transmitted         |

|                     |                                  | SPIxTXB is not                      |                             |                                        |                         |                        |                        |

|                     |                                  | a critical error                    | -                           |                                        |                         |                        |                        |

| bit 11              | AUDMONO: A                       |                                     |                             |                                        |                         |                        |                        |

|                     | 1 = Audio data<br>0 = Audio data |                                     | each data wo                | rd is transmitted                      | on both left an         | d right channel        | s)                     |

| bit 10              | URDTEN: Tra                      | nsmit Underru                       | n Data Enable               | e bit <sup>(3)</sup>                   |                         |                        |                        |

|                     |                                  |                                     |                             | egisters during T<br>g Transmit Under  |                         | . ,                    | itions                 |

| bit 9-8             | AUDMOD<1:0                       |                                     | -                           | •                                      |                         |                        |                        |

|                     | 11 = PCM/DS                      |                                     |                             |                                        |                         |                        |                        |

|                     |                                  |                                     |                             | nctions as if SPII                     |                         |                        |                        |

|                     |                                  |                                     |                             | ctions as if SPIFE<br>f SPIFE = 0, reg |                         |                        | value                  |

| bit 7               | FRMEN: Fram                      |                                     |                             | 13FIFE = 0, 1eg                        |                         |                        |                        |

|                     |                                  |                                     |                             | pin is used as th                      | e ESYNC innu            | t/output)              |                        |

|                     |                                  | Plx support is o                    |                             |                                        |                         | output)                |                        |

| Note 1:             | AUDEN can only                   | be written whe                      | n the SPIEN                 | <b>bit =</b> 0.                        |                         |                        |                        |

|                     | AUDMONO can o                    |                                     |                             |                                        | s only valid for a      | AUDEN = 1.             |                        |

| 3:                  | URDTEN is only                   | valid when IGN                      | ITUR = 1.                   |                                        |                         |                        |                        |

| 4:                  | AUDMOD<1:0> c                    |                                     |                             |                                        |                         |                        |                        |

|                     | NOT in PCM/DSF                   | - mode, this m                      | odule function              | IS AS IT FRIMSYP                       | $vv = \perp$ , regardle | ess of its actual      | value.                 |

| R/W-0      | U-0                    | R/W-0                              | R/W-0                          | R/W-0                               | R/W-0                   | R/W-0                 | R/W-0                 |

|------------|------------------------|------------------------------------|--------------------------------|-------------------------------------|-------------------------|-----------------------|-----------------------|

| RXWIEN     | —                      | RXMSK5 <sup>(1)</sup>              | RXMSK4 <sup>(1,4)</sup>        | RXMSK3 <sup>(1,3)</sup>             | RXMSK2 <sup>(1,2)</sup> | RXMSK1 <sup>(1)</sup> | RXMSK0 <sup>(1)</sup> |

| bit 15     | •                      |                                    | ·                              | ·                                   | •                       | ·                     | bit 8                 |

|            |                        |                                    |                                |                                     |                         |                       |                       |

| R/W-0      | U-0                    | R/W-0                              | R/W-0                          | R/W-0                               | R/W-0                   | R/W-0                 | R/W-0                 |

| TXWIEN     | _                      | TXMSK5 <sup>(1)</sup>              | TXMSK4 <sup>(1,4)</sup>        | TXMSK3 <sup>(1,3)</sup>             | TXMSK2 <sup>(1,2)</sup> | TXMSK1 <sup>(1)</sup> | TXMSK0 <sup>(1)</sup> |

| bit 7      |                        |                                    |                                |                                     |                         |                       | bit C                 |

|            |                        |                                    |                                |                                     |                         |                       |                       |

| Legend:    |                        |                                    |                                |                                     |                         |                       |                       |

| R = Reada  | able bit               | W = Writable                       | bit                            | U = Unimpleme                       | nted bit, read as       | · '0'                 |                       |

| -n = Value | at POR                 | '1' = Bit is set                   |                                | '0' = Bit is clear                  | ed                      | x = Bit is unkn       | own                   |

| bit 14     | 0 = Disable            | es receive buffer                  | element waterr                 | nark interrupt wh<br>mark interrupt | en RXMSK<5:0            | > ≤ RXELM<5:(         | )>                    |

|            | -                      | ented: Read as<br>:0>: RX Buffer N |                                |                                     |                         |                       |                       |

| bit 13-8   |                        | its; used in conj                  |                                |                                     |                         |                       |                       |

| bit 7      |                        | Fransmit Watern                    |                                |                                     |                         |                       |                       |

|            | 1 = Trigger            |                                    | r element water                | mark interrupt wi                   | nen TXMSK<5:0           | > = TXELM<5:(         | )>                    |

| bit 6      | Unimplem               | ented: Read as                     | ·'O'                           |                                     |                         |                       |                       |

| bit 5-0    | TXMSK<5                | :0>: TX Buffer M                   | lask bits <sup>(1,2,3,4)</sup> |                                     |                         |                       |                       |

|            | TX mask b              | its; used in conj                  | unction with the               | TXWIEN bit.                         |                         |                       |                       |

| Note 1:    | Mask values this case. | s higher than Fl                   |                                | not valid. The mo                   | odule will not trig     | gger a match fo       | or any value in       |

| -          |                        |                                    |                                |                                     |                         |                       |                       |

#### REGISTER 16-7: SPIxIMSKH: SPIx INTERRUPT MASK REGISTER HIGH

- **2:** RXMSK2 and TXMSK2 bits are only present when FIFODEPTH = 8 or higher.

- 3: RXMSK3 and TXMSK3 bits are only present when FIFODEPTH = 16 or higher.

- 4: RXMSK4 and TXMSK4 bits are only present when FIFODEPTH = 32.

#### REGISTER 19-2: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER PROTOTYPE, CPU MODE (BD0STAT THROUGH BD63STAT)

| R/W-x  | R/W-x              | r-0 | r-0 | R/W-x | R/W-x  | R/W-x, HSC | R/W-x, HSC |

|--------|--------------------|-----|-----|-------|--------|------------|------------|

| UOWN   | DTS <sup>(1)</sup> | —   | —   | DTSEN | BSTALL | BC9        | BC8        |

| bit 15 |                    |     |     |       |        |            | bit 8      |

| R/W-x, HSC |

|------------|------------|------------|------------|------------|------------|------------|------------|

| BC7        | BC6        | BC5        | BC4        | BC3        | BC2        | BC1        | BC0        |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:           | r = Reserved bit | HSC = Hardware Setta  | able/Clearable bit |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | 'r' = Reserved bit    | x = Bit is unknown |

| bit 15    | UOWN: USB Own bit                                                                                                                                                                                                                                                                                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>The microcontroller core owns the BD and its corresponding buffer; the USB module ignores all<br/>other fields in the BD</li> </ul>                                                                                                                                                     |

| bit 14    | DTS: Data Toggle Packet bit <sup>(1)</sup>                                                                                                                                                                                                                                                       |

|           | 1 = Data 1 packet                                                                                                                                                                                                                                                                                |

|           | 0 = Data 0 packet                                                                                                                                                                                                                                                                                |

| bit 13-12 | Reserved: Maintain as '0'                                                                                                                                                                                                                                                                        |

| bit 11    | DTSEN: Data Toggle Synchronization Enable bit                                                                                                                                                                                                                                                    |

|           | <ul> <li>1 = Data toggle synchronization is enabled; data packets with incorrect Sync value will be ignored</li> <li>0 = No data toggle synchronization is performed</li> </ul>                                                                                                                  |

| bit 10    | BSTALL: Buffer STALL Enable bit                                                                                                                                                                                                                                                                  |

|           | <ul> <li>1 = Buffer STALL is enabled; STALL handshake is issued if a token is received that would use the BD in the given location (UOWN bit remains set, BD value is unchanged); corresponding EPSTALL bit will get set on any STALL handshake</li> <li>0 = Buffer STALL is disabled</li> </ul> |

| bit 9-0   | BC<9:0>: Byte Count bits                                                                                                                                                                                                                                                                         |

|           | This represents the number of bytes to be transmitted or the maximum number of bytes to be received during a transfer. Upon completion, the byte count is updated by the USB module with the actual number of bytes transmitted or received.                                                     |

| Note 1: T | his bit is ignored unless DTSEN = 1.                                                                                                                                                                                                                                                             |

#### REGISTER 19-16: U1IR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)

| U-0               | U-0 | U-0                        | U-0              | U-0                        | U-0       | U-0                | U-0       |

|-------------------|-----|----------------------------|------------------|----------------------------|-----------|--------------------|-----------|

| —                 | —   | —                          | —                | —                          | —         | —                  | —         |

| bit 15            |     |                            |                  |                            |           |                    | bit 8     |

|                   |     |                            |                  |                            |           |                    |           |

| R/K-0, HS         | U-0 | R/K-0, HS                  | R/K-0, HS        | R/K-0, HS                  | R/K-0, HS | R-0                | R/K-0, HS |

| STALLIF           | —   | RESUMEIF                   | IDLEIF           | TRNIF                      | SOFIF     | UERRIF             | URSTIF    |

| bit 7             |     |                            |                  |                            |           |                    | bit 0     |

|                   |     |                            |                  |                            |           |                    |           |

| Legend:           |     | U = Unimplem               | nented bit, read | l as '0'                   |           |                    |           |

| R = Readable bit  |     | K = Write '1' to Clear bit |                  | HS = Hardware Settable bit |           |                    |           |

| -n = Value at POR |     | '1' = Bit is set           |                  | '0' = Bit is cleared       |           | x = Bit is unknown |           |

| -n = Value at     | POR | '1' = Bit is set           |                  | '0' = Bit is clea          | ared      | x = Bit is unkr    | iown      |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | STALLIF: STALL Handshake Interrupt bit                                                                                                                                                                                                                                                                                                  |

|          | <ul> <li>1 = A STALL handshake was sent by the peripheral during the handshake phase of the transaction in<br/>Device mode</li> <li>0 = A STALL handshake has not been sent</li> </ul>                                                                                                                                                  |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                              |

| bit 5    |                                                                                                                                                                                                                                                                                                                                         |

| DIL 5    | <ul> <li>RESUMEIF: Resume Interrupt bit</li> <li>1 = A K-state is observed on the D+ or D- pin for 2.5 μs (differential '1' for low speed, differential '0' for full speed)</li> <li>0 = No K-state is observed</li> </ul>                                                                                                              |

| bit 4    | IDLEIF: Idle Detect Interrupt bit                                                                                                                                                                                                                                                                                                       |

|          | <ul> <li>1 = Idle condition is detected (constant Idle state of 3 ms or more)</li> <li>0 = No Idle condition is detected</li> </ul>                                                                                                                                                                                                     |

| bit 3    | TRNIF: Token Processing Complete Interrupt bit                                                                                                                                                                                                                                                                                          |

|          | <ul> <li>1 = Processing of the current token is complete; read the U1STAT register for endpoint information</li> <li>0 = Processing of the current token is not complete; clear the U1STAT register or load the next token from U1STAT (clearing this bit causes the U1STAT FIFO to advance)</li> </ul>                                 |

| bit 2    | SOFIF: Start-of-Frame Token Interrupt bit                                                                                                                                                                                                                                                                                               |

|          | 1 = A Start-of-Frame token is received by the peripheral or the Start-of-Frame threshold is reached by the host                                                                                                                                                                                                                         |

|          | 0 = No Start-of-Frame token is received or threshold reached                                                                                                                                                                                                                                                                            |

| bit 1    | <b>UERRIF</b> : USB Error Condition Interrupt bit (read-only)                                                                                                                                                                                                                                                                           |

|          | <ul> <li>1 = An unmasked error condition has occurred; only error states enabled in the U1EIE register can set<br/>this bit</li> </ul>                                                                                                                                                                                                  |

| · ·· •   | 0 = No unmasked error condition has occurred                                                                                                                                                                                                                                                                                            |

| bit 0    | URSTIF: USB Reset Interrupt bit                                                                                                                                                                                                                                                                                                         |

|          | <ul> <li>1 = Valid USB Reset has occurred for at least 2.5 μs; Reset state must be cleared before this bit can<br/>be reasserted</li> </ul>                                                                                                                                                                                             |

|          | 0 = No USB Reset has occurred. Individual bits can only be cleared by writing a '1' to the bit position<br>as part of a word write operation on the entire register. Using Boolean instructions or bitwise oper-<br>ations to write to a single bit position will cause all set bits, at the moment of the write, to become<br>cleared. |

| Note:    | Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the                                                                                                                                                                                                                       |

|          | entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause all set bits, at the moment of the write, to become cleared.                                                                                                                                                             |

#### 23.5.8 PROGRAMMING CFGPAGE (PAGE 0) CONFIGURATION BITS

- 1. If not already set, set the CRYON bit. Set KEYPG<3:0> to '0000'.

- 2. Read the PGMFAIL status bit. If this bit is '1', an illegal configuration has been selected and the programming operation will not be performed.

- Write the data to be programmed into the Configuration Page into CRYTXTC<31:0>. Any bits that are set ('1') will be permanently programmed, while any bits that are cleared ('0') will not be programmed and may be programmed at a later time.

- 4. Set the CRYWR bit. Poll the bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- 5. Once all programming has completed, set the CRYREAD bit to reload the values from the on-chip storage. A read operation must be performed to complete programming.

- Note: Do not clear the CRYON bit while the CRYREAD bit is set; this will result in an incomplete read operation and unavailable key data. To recover, set CRYON and CRYREAD, and allow the read operation to fully complete.

- 6. Poll the CRYREAD bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- For production programming, the TSTPGM bit can be set to indicate a successful programming operation. When TSTPGM is set, the PGMTST bit (CRYOTP<7>) will also be set, allowing users to see the OTP array status with performing a read operation on the array.

- **Note:** If the device enters Sleep mode during OTP programming, the contents of the OTP array may become corrupted. This is not a recoverable error. Users must ensure that entry into power-saving modes is disabled before OTP programming is performed.

#### 23.5.9 PROGRAMMING KEYS

- 1. If not already set, set the CRYON bit.

- 2. Configure KEYPG<3:0> to the page you want to program.

- 3. Read the PGMFAIL status bit. If this bit is '1', an illegal configuration has been selected and the programming operation will not be performed.

- 4. Write the data to be programmed into the Configuration Page into CRYTXTC<63:0>. Any bits that are set ('1') will be permanently programmed, while any bits that are cleared ('0') will not be programmed and may be programmed at a later time.

- 5. Set the CRYWR bit. Poll the bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- 6. Repeat Steps 2 through 5 for each OTP array page to be programmed.

- 7. Once all programming has completed, set the CRYREAD bit to reload the values from the on-chip storage. A read operation must be performed to complete programming.

- Note: Do not clear the CRYON bit while the CRYREAD bit is set; this will result in an incomplete read operation and unavailable key data. To recover, set CRYON and CRYREAD, and allow the read operation to fully complete.

- 8. Poll the CRYREAD bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- For production programming, the TSTPGM bit can be set to indicate a successful programming operation. When TSTPGM is set, the PGMTST bit (CRYOTP<7>) will also be set, allowing users to see the OTP array status with performing a read operation on the array.

- **Note:** If the device enters Sleep Mode during OTP programming, the contents of the OTP array may become corrupted. This is not a recoverable error. Users must ensure that entry into power-saving modes is disabled before OTP programming is performed.

#### 23.5.10 VERIFYING PROGRAMMED KEYS

To maintain key security, the secure OTP array has no provision to read back its data to any user-accessible memory space in any operating mode. Therefore, there is no way to directly verify programmed data. The only method for verifying that they have been programmed correctly is to perform an encryption operation with a known plaintext/ciphertext pair for each programmed key.

### REGISTER 25-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

| bit 6-2 | SMPI<4:0>: Interrupt Sample/DMA Increment Rate Select bits                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | When DMAEN = 1:                                                                                                                                                                       |

|         | 11111 = Increments the DMA address after completion of the 32nd sample/conversion operation                                                                                           |

|         | <ul> <li>11110 = Increments the DMA address after completion of the 31st sample/conversion operation</li> <li>•</li> </ul>                                                            |

|         | •                                                                                                                                                                                     |

|         | •                                                                                                                                                                                     |