###

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                                |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb202-i-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0  | Device Overview                                             |     |

|------|-------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with 16-Bit Microcontrollers |     |

| 3.0  | СРИ                                                         |     |

| 4.0  | Memory Organization                                         |     |

| 5.0  | Direct Memory Access Controller (DMA)                       |     |

| 6.0  | Flash Program Memory                                        |     |

| 7.0  | Resets                                                      |     |

| 8.0  | Interrupt Controller                                        |     |

| 9.0  | Oscillator Configuration                                    | 147 |

| 10.0 | Power-Saving Features                                       | 161 |

| 11.0 | I/O Ports                                                   | 173 |

| 12.0 | Timer1                                                      |     |

| 13.0 | Timer2/3 and Timer4/5                                       |     |

| 14.0 | Input Capture with Dedicated Timers                         |     |

|      | Output Compare with Dedicated Timers                        |     |

| 16.0 | Serial Peripheral Interface (SPI)                           |     |

| 17.0 |                                                             |     |

|      | Universal Asynchronous Receiver Transmitter (UART)          |     |

| 19.0 | Universal Serial Bus with On-The-Go Support (USB OTG)       |     |

| 20.0 |                                                             |     |

|      | Enhanced Parallel Master Port (EPMP)                        |     |

|      | Real-Time Clock and Calendar (RTCC)                         |     |

| 23.0 | Cryptographic Engine                                        |     |

|      | 32-Bit Programmable Cyclic Redundancy Check (CRC) Generator |     |

|      | 12-Bit A/D Converter with Threshold Detect                  |     |

|      | Triple Comparator Module                                    |     |

|      | Comparator Voltage Reference                                |     |

|      | Charge Time Measurement Unit (CTMU)                         |     |

|      | High/Low-Voltage Detect (HLVD)                              |     |

|      | Special Features                                            |     |

|      | Development Support                                         |     |

|      | Instruction Set Summary                                     |     |

|      | Electrical Characteristics                                  |     |

|      | Packaging Information                                       |     |

|      | endix A: Revision History                                   |     |

|      | (                                                           |     |

|      | Microchip Web Site                                          |     |

|      | omer Change Notification Service                            |     |

|      | omer Support                                                |     |

| Prod | uct Identification System                                   |     |

| TABI F 4-27 <sup>.</sup> | <b>CRC REGISTER MAP</b> |

|--------------------------|-------------------------|

| ADLL = -21.              |                         |

| © 20        | TABLE 4-2    | 27:  | CRC RE | GISTE  | R MAP  |         |         |         |         |             |   |

|-------------|--------------|------|--------|--------|--------|---------|---------|---------|---------|-------------|---|

| 2013-2015   | File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8       |   |

| 5 Microchin | CRCCON1      | 0158 | CRCEN  |        | CSIDL  | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0      | - |

|             | CRCCON2      | 015A | _      | _      | _      | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0     |   |

|             | CRCXORL      | 015C |        |        |        |         |         |         |         | X<15:1>     |   |

|             | CRCXORH      | 015E |        |        |        |         |         |         |         | X<31:       | 1 |

|             | CRCDATL      | 0160 |        |        |        |         |         |         | CRC     | Data Input  | F |

|             | CRCDATH      | 0162 |        |        |        |         |         |         | CRC     | Data Input  | F |

|             | CRCWDATL     | 0164 |        |        |        |         |         |         | CF      | RC Result R | e |

|             | CRCWDATH     | 0166 |        |        |        |         |         |         | CF      | RC Result R | e |

|             |              |      |        |        |        |         |         |         |         |             |   |

Legend: — = unimplemented, read as '0'; x = unknown value on Reset. Reset values are shown in hexadecimal.

#### TABLE 4-28: PERIPHERAL PIN SELECT REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12     | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7 | Bit 6 | Bit 5        | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     | All<br>Resets |

|--------------|------|--------|--------|-----------|------------|-----------|-----------|-----------|-----------|-------|-------|--------------|-----------|-----------|-----------|-----------|-----------|---------------|

| RPINR0       | 038C | _      | _      | INT1R5    | INT1R4     | INT1R3    | INT1R2    | INT1R1    | INT1R0    | _     | _     | OCTRIG1R5    | OCTRIG1R4 | OCTRIG1R3 | OCTRIG1R2 | OCTRIG1R1 | OCTRIG1R0 | 3F3F          |

| RPINR1       | 038E | -      | -      | INT3R5    | INT3R4     | INT3R3    | INT3R2    | INT3R1    | INT3R0    | _     | _     | INT2R5       | INT2R4    | INT2R3    | INT2R2    | INT2R1    | INT2R0    | 3F3F          |

| RPINR2       | 0390 | -      | -      | OCTRIG2R5 | OCTRIG2R4  | OCTRIG2R3 | OCTRIG2R2 | OCTRIG2R1 | OCTRIG2R0 | _     | _     | INT4R5       | INT4R4    | INT4R3    | INT4R2    | INT4R1    | INT4R0    | 3F3F          |

| RPINR7       | 039A | _      | _      | IC2R5     | IC2R4      | IC2R3     | IC2R2     | IC2R1     | IC2R0     | _     | _     | IC1R5        | IC1R4     | IC1R3     | IC1R2     | IC1R1     | IC1R0     | 3F3F          |

| RPINR8       | 039C | —      | —      | IC4R5     | IC4R4      | IC4R3     | IC4R2     | IC4R1     | IC4R0     | _     | _     | IC3R5        | IC3R4     | IC3R3     | IC3R2     | IC3R1     | IC3R0     | 3F3F          |

| RPINR9       | 039E | _      | _      | IC6R5     | IC6R4      | IC6R3     | IC6R2     | IC6R1     | IC6R0     | _     | _     | IC5R5        | IC5R4     | IC5R3     | IC5R2     | IC5R1     | IC5R0     | 3F3F          |

| RPINR11      | 03A2 | —      | _      | OCFBR5    | OCFBR4     | OCFBR3    | OCFBR2    | OCFBR1    | OCFBR0    | —     | —     | OCFAR5       | OCFAR4    | OCFAR3    | OCFAR2    | OCFAR1    | OCFAR0    | 3F3F          |

| RPINR17      | 03AE | —      | —      |           | U3RXR<5:0> |           |           |           | _         | _     | _     | _            | _         | -         | _         | _         | 3F00      |               |

| RPINR18      | 03B0 | _      | _      | U1CTSR5   | U1CTSR4    | U1CTSR3   | U1CTSR2   | U1CTSR1   | U1CTSR0   | _     | _     | U1RXR5       | U1RXR4    | U1RXR3    | U1RXR2    | U1RXR1    | U1RXR0    | 3F3F          |

| RPINR19      | 03B2 | —      | _      | U2CTSR5   | U2CTSR4    | U2CTSR3   | U2CTSR2   | U2CTSR1   | U2CTSR0   | —     | —     | U2RXR5       | U2RXR4    | U2RXR3    | U2RXR2    | U2RXR1    | U2RXR0    | 3F3F          |

| RPINR20      | 03B4 | —      | —      | SCK1R5    | SCK1R4     | SCK1R3    | SCK1R2    | SCK1R1    | SCK1R0    | —     | _     | SDI1R5       | SDI1R4    | SDI1R3    | SDI1R2    | SDI1R1    | SDI1R0    | 3F3F          |

| RPINR21      | 03B6 | _      | _      | U3CTSR5   | U3CTSR4    | U3CTSR3   | U3CTSR2   | U3CTSR1   | U3CTSR0   | _     | _     | SS1R5        | SS1R4     | SS1R3     | SS1R2     | SS1R1     | SS1R0     | 3F3F          |

| RPINR22      | 03B8 | —      | _      | SCK2R5    | SCK2R4     | SCK2R3    | SCK2R2    | SCK2R1    | SCK2R0    | —     | —     | SDI2R5       | SDI2R4    | SDI2R3    | SDI2R2    | SDI2R1    | SDI2R0    | 3F3F          |

| RPINR23      | 03BA | —      | —      | TMRCKR5   | TMRCKR4    | TMRCKR3   | TMRCKR2   | TMRCKR1   | TMRCKR0   | —     | _     | SS2R5        | SS2R4     | SS2R3     | SS2R2     | SS2R1     | SS2R0     | 3F3F          |

| RPINR27      | 03C2 | _      | _      | U4CTSR5   | U4CTSR4    | U4CTSR3   | U4CTSR2   | U4CTSR1   | U4CTSR0   | _     | _     | U4RXR5       | U4RXR4    | U4RXR3    | U4RXR2    | U4RXR1    | U4RXR0    | 3F3F          |

| RPINR28      | 03C4 | _      | _      | SCK3R5    | SCK3R4     | SCK3R3    | SCK3R2    | SCK3R1    | SCK3R0    | _     | -     | SDI3R5       | SDI3R4    | SDI3R3    | SDI3R2    | SDI3R1    | SDI3R0    | 3F3F          |

| RPINR29      | 03C6 | _      | _      | _         | _          | _         | _         | _         | _         | _     |       |              |           | SS3R      | <5:0>     |           |           | 003F          |

| RPINR30      | 03C8 | _      | _      | _         | _          | _         | _         | _         | _         | _     | -     | - MDMIR<5:0> |           |           |           | 003F      |           |               |

| RPINR31      | 03CA | _      |        | MDC2R5    | MDC2R4     | MDC2R3    | MDC2R2    | MDC2R1    | MDC2R0    | _     | -     | MDC1R5       | MDC1R4    | MDC1R3    | MDC1R2    | MDC1R1    | MDC1R0    | 3F3F          |

X<31:16>

CRC Data Input Register Low

CRC Data Input Register High

CRC Result Register Low

CRC Result Register High

Bit 7

CRCFUL

\_

Bit 6

CRCMPT

Bit 5

CRCISEL

\_

Bit 4

CRCGO

PLEN4

Bit 3

LENDIAN

PLEN3

Bit 2

\_

PLEN2

Bit 1

\_

PLEN1

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All

Resets

0040

0000

0000

0000

XXXX

XXXX

XXXX

XXXX

Bit 0

\_

PLEN0

\_

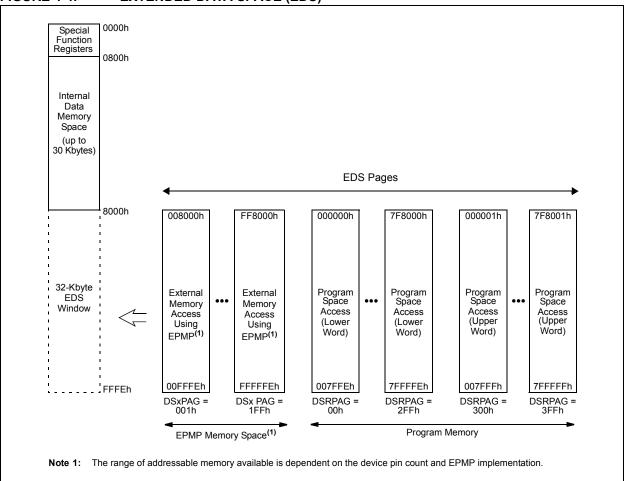

#### 4.2.5 EXTENDED DATA SPACE (EDS)

The Extended Data Space (EDS) allows PIC24F devices to address a much larger range of data than would otherwise be possible with a 16-bit address range. EDS includes any additional internal data memory not directly accessible by the lower 32-Kbyte data address space and any external memory through the Enhanced Parallel Master Port (EPMP).

In addition, EDS also allows read access to the program memory space. This feature is called Program Space Visibility (PSV) and is discussed in detail in Section 4.3.3 "Reading Data from Program Memory Using EDS".

Figure 4-4 displays the entire EDS space. The EDS is organized as pages, called EDS pages, with one page equal to the size of the EDS window (32 Kbytes). A particular EDS page is selected through the Data Space Read register (DSRPAG) or Data Space Write register (DSWPAG). For PSV, only the DSRPAG register is used. The combination of the DSRPAG register value and the 16-bit wide data address forms a 24-bit Effective Address (EA). The data addressing range of PIC24FJ128GB204 family devices depends on the version of the Enhanced Parallel Master Port implemented on a particular device; this is, in turn, a function of device pin count. Table 4-34 lists the total memory accessible by each of the devices in this family. For more details on accessing external memory using EPMP, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Enhanced Parallel Master Port (EPMP)"** (DS39730).

| <b>TABLE 4-34:</b> | TOTAL ACCESSIBLE DATA |

|--------------------|-----------------------|

|                    | MEMORY                |

| Family          | Internal<br>RAM | External RAM<br>Access Using<br>EPMP |

|-----------------|-----------------|--------------------------------------|

| PIC24FJXXXGB204 | 8K              | Up to 16 Mbytes                      |

| PIC24FJXXXGB202 | 8K              | Up to 64K                            |

**Note:** Accessing Page 0 in the EDS window will generate an address error trap as Page 0 is the base data memory (data locations, 0800h to 7FFFh, in the lower Data Space).

#### FIGURE 4-4: EXTENDED DATA SPACE (EDS)

#### REGISTER 5-1: DMACON: DMA ENGINE CONTROL REGISTER

| R/W-0                                                                | U-0 | U-0 | U-0 | U-0                                     | U-0 | U-0 | U-0    |  |  |

|----------------------------------------------------------------------|-----|-----|-----|-----------------------------------------|-----|-----|--------|--|--|

| DMAEN                                                                | —   | —   | —   | —                                       | —   | —   | —      |  |  |

| bit 15                                                               |     |     |     |                                         |     |     | bit 8  |  |  |

|                                                                      |     |     |     |                                         |     |     |        |  |  |

| U-0                                                                  | U-0 | U-0 | U-0 | U-0                                     | U-0 | U-0 | R/W-0  |  |  |

| _                                                                    | —   | —   | —   | —                                       | —   | —   | PRSSEL |  |  |

| bit 7                                                                |     |     |     |                                         |     |     | bit 0  |  |  |

|                                                                      |     |     |     |                                         |     |     |        |  |  |

| Legend:                                                              |     |     |     |                                         |     |     |        |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |     |     |                                         |     |     |        |  |  |

| -n = Value at POR '1' = Bit is set                                   |     |     |     | '0' = Bit is cleared x = Bit is unknown |     |     |        |  |  |

|                                                                      |     |     |     |                                         |     |     |        |  |  |

bit 15 DMAEN: DMA Module Enable bit

1 = Enables module

0 = Disables module and terminates all active DMA operation(s)

bit 14-1 Unimplemented: Read as '0'

bit 0 PRSSEL: Channel Priority Scheme Selection bit

1 = Round robin scheme

0 = Fixed priority scheme

### TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS (CONTINUED)

|                   | Vector | IRQ | IVT     | ΑΙντ    | Interrupt Bit Locations |          |              |  |  |

|-------------------|--------|-----|---------|---------|-------------------------|----------|--------------|--|--|

| Interrupt Source  | #      | #   | Address | Address | Flag                    | Enable   | Priority     |  |  |

| SPI1 General      | 17     | 9   | 000026h | 000126h | IFS0<9>                 | IEC0<9>  | IPC2<6:4>    |  |  |

| SPI1 Transmit     | 18     | 10  | 000028h | 000128h | IFS0<10>                | IEC0<10> | IPC2<10:8>   |  |  |

| SPI1 Receive      | 66     | 58  | 000088h | 000188h | IFS3<10>                | IEC3<10> | IPC14<10:8>  |  |  |

| SPI2 General      | 40     | 32  | 000054h | 000154h | IFS2<0>                 | IEC2<0>  | IPC8<2:0>    |  |  |

| SPI2 Transmit     | 41     | 33  | 000056h | 000156h | IFS2<1>                 | IEC2<1>  | IPC8<6:4>    |  |  |

| SPI2 Receive      | 67     | 59  | 00008Ah | 00018Ah | IFS3<11>                | IEC3<11> | IPC14<14:12> |  |  |

| SPI3 General      | 98     | 90  | 0000C8h | 0001C8h | IFS5<10>                | IEC5<10> | IPC22<10:8>  |  |  |

| SPI3 Transmit     | 99     | 91  | 0000CAh | 0001CAh | IFS5<11>                | IEC5<11> | IPC22<14:12> |  |  |

| SPI3 Receive      | 68     | 60  | 000054h | 000154h | IFS3<12>                | IEC3<12> | IPC15<2:0>   |  |  |

| Timer1            | 11     | 3   | 00001Ah | 00011Ah | IFS0<3>                 | IEC0<3>  | IPC0<14:12>  |  |  |

| Timer2            | 15     | 7   | 000022h | 000122h | IFS0<7>                 | IEC0<7>  | IPC1<14:12>  |  |  |

| Timer3            | 16     | 8   | 000024h | 000124h | IFS0<8>                 | IEC0<8>  | IPC2<2:0>    |  |  |

| Timer4            | 35     | 27  | 00004Ah | 00014Ah | IFS1<11>                | IEC1<11> | IPC6<14:12>  |  |  |

| Timer5            | 36     | 28  | 00004Ch | 00014Ch | IFS1<12>                | IEC1<12> | IPC7<2:0>    |  |  |

| UART1 Error       | 73     | 65  | 000096h | 000196h | IFS4<1>                 | IEC4<1>  | IPC16<6:4>   |  |  |

| UART1 Receiver    | 19     | 11  | 00002Ah | 00012Ah | IFS0<11>                | IEC0<11> | IPC2<14:12>  |  |  |

| UART1 Transmitter | 20     | 12  | 00002Ch | 00012Ch | IFS0<12>                | IEC0<12> | IPC3<2:0>    |  |  |

| UART2 Error       | 74     | 66  | 000098h | 000198h | IFS4<2>                 | IEC4<2>  | IPC16<10:8>  |  |  |

| UART2 Receiver    | 38     | 30  | 000050h | 000150h | IFS1<14>                | IEC1<14> | IPC7<10:8>   |  |  |

| UART2 Transmitter | 39     | 31  | 000052h | 000152h | IFS1<15>                | IEC1<15> | IPC7<14:12>  |  |  |

| UART3 Error       | 89     | 81  | 0000B6h | 0001B6h | IFS5<1>                 | IEC5<1>  | IPC20<6:4>   |  |  |

| UART3 Receiver    | 90     | 82  | 0000B8h | 0001B8h | IFS5<2>                 | IEC5<2>  | IPC20<10:8>  |  |  |

| UART3 Transmitter | 91     | 83  | 0000BAh | 0001BAh | IFS5<3>                 | IEC5<3>  | IPC20<14:12> |  |  |

| UART4 Error       | 95     | 87  | 0000C2h | 0001C2h | IFS5<7>                 | IEC5<7>  | IPC21<14:12> |  |  |

| UART4 Receiver    | 96     | 88  | 0000C4h | 0001C4h | IFS5<8>                 | IEC5<8>  | IPC22<2:0>   |  |  |

| UART4 Transmitter | 97     | 89  | 0000C6h | 0001C6h | IFS5<9>                 | IEC5<9>  | IPC22<6:4>   |  |  |

| USB               | 94     | 86  | 0000C0h | 0001C0h | IFS5<6>                 | IEC5<6>  | IPC21<10:8>  |  |  |

#### REGISTER 8-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

- bit 2 CMIF: Comparator Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 1 MI2C1IF: Master I2C1 Event Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: Slave I2C1 Event Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

#### REGISTER 8-11: IFS6: INTERRUPT FLAG STATUS REGISTER 6

| U-0                                                                       | U-0 | U-0            | U-0 | U-0                                | R/W-0 | U-0 | U-0   |  |

|---------------------------------------------------------------------------|-----|----------------|-----|------------------------------------|-------|-----|-------|--|

| —                                                                         | _   | —              | —   | —                                  | FSTIF | —   | —     |  |

| bit 15                                                                    |     |                |     |                                    |       |     | bit 8 |  |

|                                                                           |     |                |     |                                    |       |     |       |  |

| U-0                                                                       | U-0 | U-0            | U-0 | U-0                                | U-0   | U-0 | U-0   |  |

| —                                                                         | —   | —              | —   | —                                  | —     | —   | —     |  |

| bit 7                                                                     |     |                |     |                                    |       |     | bit 0 |  |

|                                                                           |     |                |     |                                    |       |     |       |  |

| Legend:                                                                   |     |                |     |                                    |       |     |       |  |

| R = Readable                                                              | bit | W = Writable I | bit | U = Unimplemented bit, read as '0' |       |     |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |     |                |     |                                    | iown  |     |       |  |

| bit 15-11 | Unimplemented: Read as '0'         |

|-----------|------------------------------------|

| hit 10    | ESTIE: EDC Solf Tupo Interrupt Ele |

- bit 10 FSTIF: FRC Self-Tune Interrupt Flag Status bit 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 9-0 Unimplemented: Read as '0'

#### REGISTER 8-12: IFS7: INTERRUPT FLAG STATUS REGISTER 7

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|-------|-----|--------|-----|-----|-----|-----|-----|--|

| —     | —   | JTAGIF | —   | —   | —   | —   | —   |  |

| bit 7 |     |        |     |     |     |     |     |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-6 Unimplemented: Read as '0'

bit 5 JTAGIF: JTAG Controller Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 4-0 Unimplemented: Read as '0'

#### 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

- Fast Internal RC (FRC) Oscillator

- · Low-Power Internal RC (LPRC) Oscillator

The Primary Oscillator and FRC sources have the option of using the internal USB PLL block, which generates both the USB module clock and a separate system clock from the 96 MHz PLL. Refer to **Section 9.6 "Oscillator Modes and USB Operation"** for additional information.

The internal FRC provides an 8 MHz clock source. It can optionally be reduced by the programmable clock divider to provide a range of system clock frequencies.

The selected clock source generates the processor and peripheral clock sources. The processor clock source is divided by two to produce the internal instruction cycle clock, FcY. In this document, the instruction cycle clock is also denoted by FOSC/2. The internal instruction cycle clock, FOSC/2, can be provided on the OSCO I/O pin for some operating modes of the Primary Oscillator.

### 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in program memory (for more information, refer to **Section 30.1 "Configuration Bits"**). The Primary Oscillator Configuration bits, POSCMD<1:0> (Configuration Word 2<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (Configuration Word 2<10:8>), select the oscillator source that is used at a Power-on Reset. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations.

The Configuration bits allow users to choose between the various clock modes, as shown in Table 9-1.

#### 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (Configuration Word 2<7:6>) are used to jointly configure device clock switching and the Fail-Safe Clock Monitor (FSCM). Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION |                   |             |            |       |  |  |  |  |  |  |

|---------------------------------------------------------|-------------------|-------------|------------|-------|--|--|--|--|--|--|

| Oscillator Mode                                         | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |  |  |  |  |  |  |

| Fast RC Oscillator with Postscaler (FRCDIV)             | Internal          | 11          | 111        | 1, 2  |  |  |  |  |  |  |

| (Reserved)                                              | Internal          | XX          | 110        | 1     |  |  |  |  |  |  |

| Low-Power RC Oscillator (LPRC)                          | Internal          | 11          | 101        | 1     |  |  |  |  |  |  |

| Secondary (Timer1) Oscillator<br>(SOSC)                 | Secondary         | 11          | 100        | 1     |  |  |  |  |  |  |

| Primary Oscillator (XT) with PLL<br>Module (XTPLL)      | Primary           | 01          | 011        |       |  |  |  |  |  |  |

| Primary Oscillator (EC) with PLL<br>Module (ECPLL)      | Primary           | 00          | 011        |       |  |  |  |  |  |  |

| Primary Oscillator (HS)                                 | Primary           | 10          | 010        |       |  |  |  |  |  |  |

| Primary Oscillator (XT)                                 | Primary           | 01          | 010        |       |  |  |  |  |  |  |

| Primary Oscillator (EC)                                 | Primary           | 00          | 010        |       |  |  |  |  |  |  |

| Fast RC Oscillator with PLL Module (FRCPLL)             | Internal          | 11          | 001        | 1     |  |  |  |  |  |  |

| Fast RC Oscillator (FRC)                                | Internal          | 11          | 000        | 1     |  |  |  |  |  |  |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

**Note 1:** OSCO pin function is determined by the OSCIOFCN Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

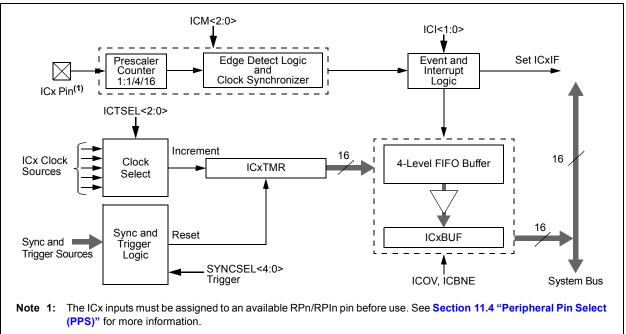

# 14.0 INPUT CAPTURE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Input Capture with Dedicated Timer" (DS39722). The information in this data sheet supersedes the information in the FRM.

Devices in the PIC24FJ128GB204 family contain six independent input capture modules. Each of the modules offers a wide range of configuration and operating options for capturing external pulse events and generating interrupts.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 30 user-selectable sync/trigger sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to 6 clock sources available for each module, driving a separate, internal 16-bit counter

The module is controlled through two registers: ICxCON1 (Register 14-1) and ICxCON2 (Register 14-2). A general block diagram of the module is shown in Figure 14-1.

#### 14.1 General Operating Modes

#### 14.1.1 SYNCHRONOUS AND TRIGGER MODES

When the input capture module operates in a Free-Running mode, the internal 16-bit counter, ICxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow. Its period is synchronized to the selected external clock source. When a capture event occurs, the current 16-bit value of the internal counter is written to the FIFO buffer.

In Synchronous mode, the module begins capturing events on the ICx pin as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the internal counter to run.

Standard, free-running operation is selected by setting the SYNCSELx bits (ICxCON2<4:0>) to '00000' and clearing the ICTRIG bit (ICxCON2<7>). Synchronous and Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The ICTRIG bit selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the sync/trigger source.

When the SYNCSELx bits are set to '00000' and ICTRIG is set, the module operates in Software Trigger mode. In this case, capture operations are started by manually setting the TRIGSTAT bit (ICxCON2<6>).

#### FIGURE 14-1: INPUT CAPTURE x BLOCK DIAGRAM

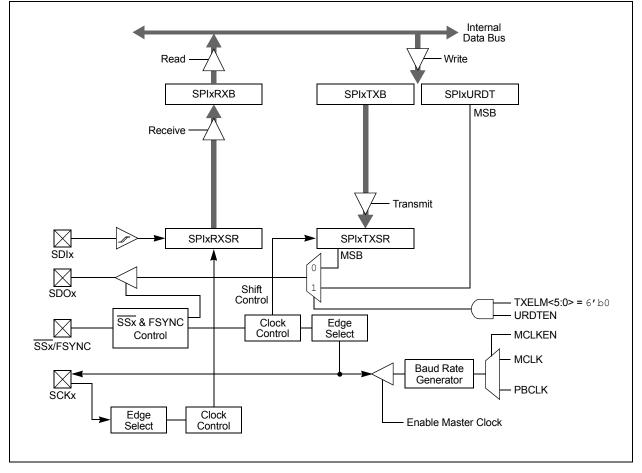

#### 16.1 Standard Master Mode

To set up the SPIx module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP<2:0> bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L and SPIxCON1H registers with the MSTEN bit (SPIxCON1L<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTATL<6>).

- 4. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 5. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

#### 16.2 Standard Slave Mode

To set up the SPIx module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF registers.

- 2. If using interrupts:

- a) Clear the SPIxBUFL and SPIxBUFH registers.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP<2:0> bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with the MSTEN bit (SPIxCON1L<5>) = 0.

- 4. Clear the SMP bit.

- If the CKE bit (SPIxCON1L<8>) is set, then the SSEN bit (SPIxCON1L<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

#### FIGURE 16-1: SPIX MODULE BLOCK DIAGRAM (STANDARD MODE)

### 18.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

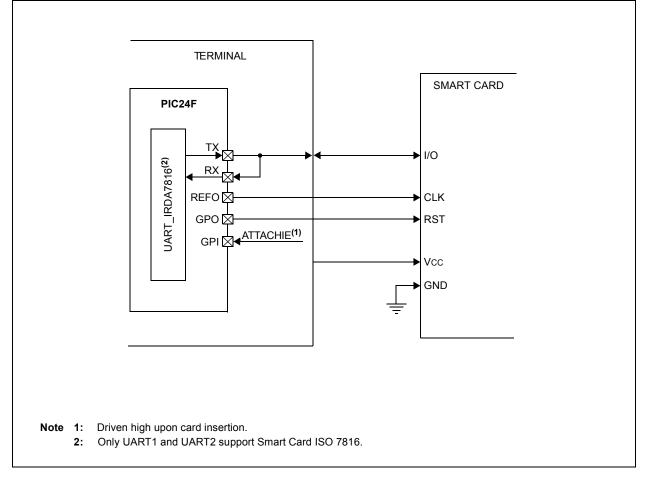

#### 18.8 Smart Card ISO 7816 Support

Figure 18-2 shows a Smart Card subsystem using a PIC24F microcontroller with a UARTx module for Smart Card data communication. Vcc to power the Smart Card can be supplied through a terminal or an

external power supply. The terminal is also responsible for clocking and resetting the Smart Card. The TX and RX line of the PIC24F device has to be shorted externally, and then connected to the I/O line of the Smart Card.

There are two protocols which are widely used for Smart Card communication between terminal and Smart Card:

- T = 0 (asynchronous, half-duplex, byte-oriented protocol)

- T = 1 (asynchronous, half-duplex, block-oriented protocol)

The selection of the T = 0 or T = 1 protocol is done using the PTRCL bit in the UxSCCON register.

#### 19.1.2 HOST AND OTG MODES

#### 19.1.2.1 D+ and D- Pull-Down Resistors

PIC24FJ128GB204 family devices have a built-in 15 kΩ pull-down resistor on the D+ and D- lines. These are used in tandem to signal to the bus that the microcontroller is operating in Host mode. They are engaged by setting the HOSTEN bit (U1CON<3>). If the OTGEN bit (U1OTGCON<2>) is set, then these pull-downs are enabled by setting the DPPULDWN and DMPULDWN bits (U1OTGCON<5:4>).

#### 19.1.2.2 Power Configurations

In Host mode, as well as Host mode in On-The-Go operation, the "USB 2.0 Specification" requires that the host application should supply power on VBUS. Since the microcontroller is running below VBUS, and is not able to source sufficient current, a separate power supply must be provided.

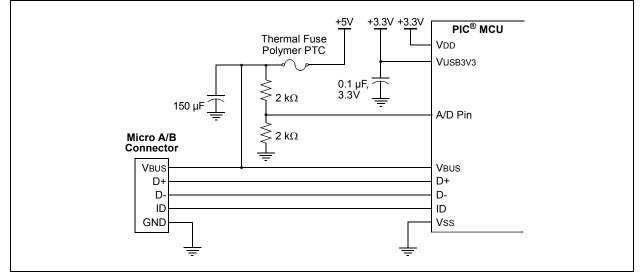

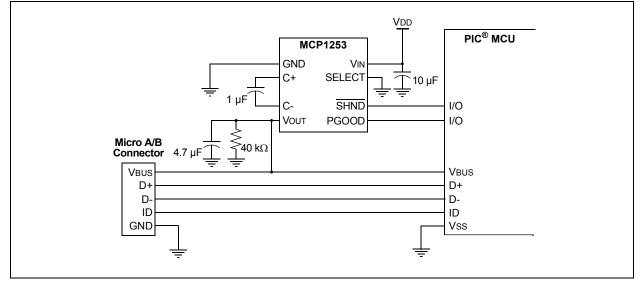

When the application is always operating in Host mode, a simple circuit can be used to supply VBUS and regulate current on the bus (Figure 19-6). For OTG operation, it is necessary to be able to turn VBUS on or off as needed, as the microcontroller switches between Device and Host modes. A typical example using an external charge pump is shown in Figure 19-7.

#### FIGURE 19-6: USB HOST INTERFACE EXAMPLE

#### FIGURE 19-7: USB OTG INTERFACE EXAMPLE

| Alarm Mask Setting<br>(AMASK<3:0>)              | Day of<br>the<br>Week | Month Day      | Hours M   | inutes Seconds |

|-------------------------------------------------|-----------------------|----------------|-----------|----------------|

| 0000 - Every half second<br>0001 - Every second |                       |                |           |                |

| 0010 - Every 10 seconds                         |                       |                |           | : s            |

| 0011 - Every minute                             |                       |                |           | s s            |

| 0100 - Every 10 minutes                         |                       |                |           | m:ss           |

| 0101 - Every hour                               |                       |                |           | n m : s s      |

| 0110 - Every day                                |                       |                | h h i n   | n m : s s      |

| 0111 - Every week                               | d                     |                | h h i n   | n m : s s      |

| 1000 - Every month                              |                       | /d             | d h h i n | n m : s s      |

| 1001 - Every year <sup>(1)</sup>                |                       | m m / d        | d h h i n | n m : s s      |

| Note 1: Annually, except when                   | n configured fo       | r February 29. |           |                |

#### 22.6 Power Control

The RTCC includes a power control feature that allows the device to periodically wake-up an external device, wait for the device to be stable before sampling wake-up events from that device and then shut down the external device. This can be done completely autonomously by the RTCC, without the need to wake from the current lower power mode (Sleep, Deep Sleep, etc.).

To use this feature:

- 1. Enable the RTCC (RTCEN = 1).

- 2. Set the PWCEN bit (RTCPWC<15>).

- 3. Configure the RTCC pin to drive the PWC control signal (RTCOE = 1 and RTCOUT<1:0> = 11).

The polarity of the PWC control signal may be chosen using the PWCPOL bit (RTCPWC<14>). An active-low or active-high signal may be used with the appropriate external switch to turn on or off the power to one or more external devices. The active-low setting may also be used in conjunction with an open-drain setting on the RTCC pin, in order to drive the ground pin(s) of the external device directly (with the appropriate external VDD pull-up device), without the need for external switches. Finally, the CHIME bit should be set to enable the PWC periodicity.

#### 22.7 RTCC VBAT Operation

The RTCC can operate in VBAT mode when there is a power loss on the VDD pin. The RTCC will continue to operate if the VBAT pin is powered on (it is usually connected to the battery).

Note: It is recommended to connect the VBAT pin to VDD if the VBAT mode is not used (not connected to the battery).

#### REGISTER 30-2: CW2: FLASH CONFIGURATION WORD 2

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| R/PO-1 | r-0 | R/PO-1 | R/PO-1  | R/PO-1                | R/PO-1 | R/PO-1 | R/PO-1 |

|--------|-----|--------|---------|-----------------------|--------|--------|--------|

| IESO   | —   | WDTCMX | ALTCMPI | ALTRB6 <sup>(2)</sup> | FNOSC2 | FNOSC1 | FNOSC0 |

| bit 15 |     |        |         |                       |        |        | bit 8  |

| R/PO-1  | R/PO-1 | R/PO-1   | R/PO-1  | R/PO-1  | r-1 | R/PO-1  | R/PO-1  |  |  |

|---------|--------|----------|---------|---------|-----|---------|---------|--|--|

| FCKSM1  | FCKSM0 | OSCIOFCN | WDTCLK1 | WDTCLK0 | _   | POSCMD1 | POSCMD0 |  |  |

| bit 7 b |        |          |         |         |     |         |         |  |  |

| Legend:           | r = Reserved bit | PO = Program Once bi  | t                  |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 23-16 | Unimplemented: Read as '1'                                                                                                                  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | IESO: Internal External Switchover bit                                                                                                      |

|           | 1 = IESO mode (Two-Speed Start-up) is enabled                                                                                               |

|           | 0 = IESO mode (Two-Speed Start-up) is disabled                                                                                              |

| bit 14    | Reserved: Read as '0'                                                                                                                       |

| bit 13    | WDTCMX: WDT Clock Multiplex Control bit                                                                                                     |

|           | 1 = WDT clock source is determined by the WDTCLK<1:0> Configuration bits                                                                    |

|           | 0 = WDT always uses LPRC as its clock source                                                                                                |

| bit 12    | ALTCMPI: Alternate Comparator Input bit                                                                                                     |

|           | <ul> <li>1 = C1INC is on RB13, C2INC is on RB9 and C3INC is on RA0</li> <li>0 = C1INC, C2INC and C3INC are on RB9</li> </ul>                |

| bit 11    | ALTRB6: Alternate RB6 Pin Function Enable bit <sup>(2)</sup>                                                                                |

| bit 11    |                                                                                                                                             |

|           | <ol> <li>= Appends the RP6/ASCL1/PMD6 functions of RB6 to RA1 pin functions</li> <li>= Keeps the RP6/ASCL1/PMD6 functions to RB6</li> </ol> |

| bit 10-8  | FNOSC<2:0>: Initial Oscillator Select bits                                                                                                  |

|           | 111 = Fast RC Oscillator with Postscaler (FRCDIV)                                                                                           |

|           | 110 = Reserved                                                                                                                              |

|           | 101 = Low-Power RC Oscillator (LPRC)                                                                                                        |

|           | 100 = Secondary Oscillator (SOSC)<br>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)                                         |

|           | 010 = Primary Oscillator (XT, HS, EC)                                                                                                       |

|           | 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)                                                                            |

|           | 000 = Fast RC Oscillator (FRC)                                                                                                              |

| bit 7-6   | FCKSM<1:0>: Clock Switching and Fail-Safe Clock Monitor Configuration bits                                                                  |

|           | 1x = Clock switching and Fail-Safe Clock Monitor are disabled                                                                               |

|           | 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled                                                                        |

|           | 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                         |

| Note 1:   | The 31 kHz FRC source is used when a Windowed WDT mode is selected and the LPRC is not being                                                |

|           | used as the system clock. The LPRC is used when the device is in Sleep mode and in all other cases.                                         |

| 2:        | When VBUS functionality is used, this Configuration bit must be programmed to '1'.                                                          |

#### 31.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 31.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 31.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB X IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 31.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB X IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 31.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

#### 31.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 31.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

#### TABLE 33-13: COMPARATOR DC SPECIFICATIONS

| -            | Operating Conditions: $2.0V < VDD < 3.6V$ Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                           |     |     |     |       |                    |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----|-----|-----|-------|--------------------|--|

| Param<br>No. | Symbol                                                                                                                                                                        | Characteristic                            | Min | Тур | Мах | Units | Comments           |  |

| D300         | VIOFF                                                                                                                                                                         | Input Offset Voltage                      |     | 20  | ±40 | mV    | (Note 1)           |  |

| D301         | VICM                                                                                                                                                                          | Input Common-Mode Voltage                 | 0   | _   | Vdd | V     | (Note 1)           |  |

| D302         | CMRR                                                                                                                                                                          | Common-Mode Rejection<br>Ratio            | 55  | —   | —   | dB    | (Note 1)           |  |

| D306         | IQCMP                                                                                                                                                                         | AVDD Quiescent Current per<br>Comparator  | _   | 27  | —   | μs    | Comparator enabled |  |

| D307         | TRESP                                                                                                                                                                         | Response Time                             | _   | 300 | _   | ns    | (Note 2)           |  |

| D308         | Тмс2оv                                                                                                                                                                        | Comparator Mode Change to<br>Valid Output | _   | —   | 10  | μs    |                    |  |

Note 1: Parameters are characterized but not tested.

2: Measured with one input at VDD/2 and the other transitioning from VSS to VDD, 40 mV step, 15 mV overdrive.

#### TABLE 33-14: COMPARATOR VOLTAGE REFERENCE DC SPECIFICATIONS

| -            | Operating Conditions: $2.0V < V_{DD} < 3.6V$ Operating temperature $-40^{\circ}C \le T_A \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le T_A \le +125^{\circ}C$ for Extended |                         |      |     |     |       |          |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-----|-----|-------|----------|

| Param<br>No. | Symbol                                                                                                                                                                          | Characteristic          | Min  | Тур | Max | Units | Comments |

| VR310        | TSET                                                                                                                                                                            | Settling Time           |      | _   | 10  | μs    | (Note 1) |

| VRD311       | CVRAA                                                                                                                                                                           | Absolute Accuracy       | -100 | —   | 100 | mV    |          |

| VRD312       | CVRur                                                                                                                                                                           | Unit Resistor Value (R) |      | 4.5 | _   | kΩ    |          |

Note 1: Measures the interval while CVR<4:0> transitions from '11111' to '00000'.

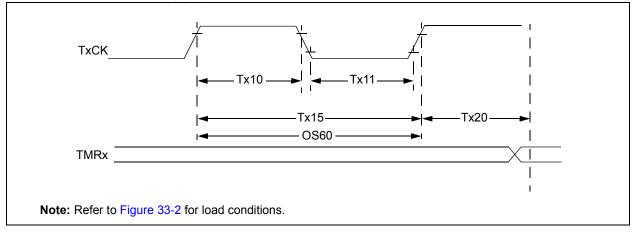

#### FIGURE 33-5: TIMER1, 2, 3, 4 AND 5 EXTERNAL CLOCK TIMING CHARACTERISTICS

| TABLE 33-26: | TIMER1 EXTERNAL | CLOCK TIM | IING REQUIREMENTS <sup>(1)</sup> |   |

|--------------|-----------------|-----------|----------------------------------|---|

|              |                 |           |                                  | 1 |

|              |           |                                                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                         |     |         |       |                                       |

|--------------|-----------|--------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------|-----|---------|-------|---------------------------------------|

| Param<br>No. | Symbol    | Charao                                                             | cteristic                                            | Min                                     | Тур | Мах     | Units | Conditions                            |

| TA10         | ТтхН      | T1CK High<br>Time                                                  | Synchronous,<br>No Prescaler                         | 0.5 TCY + 20                            | _   |         | ns    | Must also meet<br>Parameter TA15      |

|              |           |                                                                    | Synchronous, with Prescaler                          | 10                                      |     | —       | ns    |                                       |

|              |           |                                                                    | Asynchronous                                         | 10                                      |     | —       | ns    |                                       |

| TA11         | ΤτxL      | T1CK Low<br>Time                                                   | Synchronous,<br>No Prescaler                         | 0.5 TCY + 20                            |     | _       | ns    | Must also meet<br>Parameter TA15      |

|              |           |                                                                    | Synchronous, with Prescaler                          | 10                                      | _   | -       | ns    |                                       |

|              |           |                                                                    | Asynchronous                                         | 10                                      | _   | —       | ns    |                                       |

| TA15         | ΤτχΡ      | T1CK Input<br>Period                                               | Synchronous,<br>No Prescaler                         | Tcy + 40                                | _   | —       | ns    |                                       |

|              |           |                                                                    | Synchronous, with Prescaler                          | Greater of:<br>20 ns or<br>(Tcy + 40)/N | _   | —       | _     | N = Prescale Value<br>(1, 8, 64, 256) |

|              |           |                                                                    | Asynchronous                                         | 20                                      | _   | —       | ns    |                                       |

| OS60         | FT1       | SOSC1/T1CK O<br>Frequency Rang<br>enabled by settir<br>(T1CON<1>)) | e (oscillator                                        | DC                                      | _   | 50      | kHz   |                                       |

| TA20         | TCKEXTMRL | Delay from Exte<br>Edge to Timer Ir                                | rnal T1CK Clock                                      | 0.5 TCY                                 |     | 1.5 TCY |       |                                       |

**Note 1:** Timer1 is a Type A.

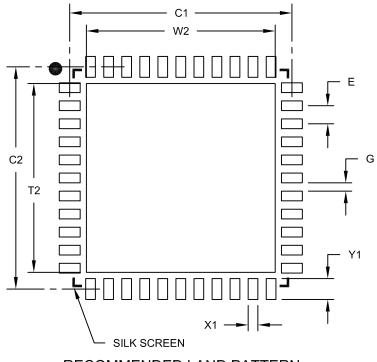

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | Units    | N N  | <b>/ILLIMETER</b> | S    |

|----------------------------|----------|------|-------------------|------|

| Dimensio                   | n Limits | MIN  | NOM               | MAX  |

| Contact Pitch              | E        |      | 0.65 BSC          |      |

| Optional Center Pad Width  | W2       |      |                   | 6.60 |

| Optional Center Pad Length | T2       |      |                   | 6.60 |

| Contact Pad Spacing        | C1       |      | 8.00              |      |

| Contact Pad Spacing        | C2       |      | 8.00              |      |

| Contact Pad Width (X44)    | X1       |      |                   | 0.35 |

| Contact Pad Length (X44)   | Y1       |      |                   | 0.85 |

| Distance Between Pads      | G        | 0.25 |                   |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

| Equationa |  |

|-----------|--|

| Equations |  |

| 16-Bit, 32-Bit CRC Polynomials         | 346 |

|----------------------------------------|-----|

| A/D Conversion Clock Period            | 368 |

| Baud Rate Reload Calculation           |     |

| Calculating the PWM Period             | 220 |

| Calculation for Maximum PWM Resolution |     |

| Estimating USB Transceiver             |     |

| Current Consumption                    |     |

| Fractional Divisor for ROTRIMx Bits    | 156 |

| Relationship Between Device and        |     |

| SPIx Clock Speed                       |     |

| UARTx Baud Rate with BRGH = 0          |     |

| UARTx Baud Rate with BRGH = 1          |     |

| Errata                                 | 7   |

| Extended Data Space (EDS)              | 303 |

| • • • •                                |     |

### F

| Flash Configuration Word Locations | 389 |

|------------------------------------|-----|

| Flash Configuration Words          | 36  |

| Flash Program Memory               | 79  |

| and Table Instructions             | 79  |

| Control Registers                  | 80  |

| Enhanced ICSP Operation            | 80  |

| JTAG Operation                     | 80  |

| Programming Algorithm              | 82  |

| Programming Operations             | 80  |

| RTSP Operation                     | 80  |

| Single-Word Programming            |     |

### G

| Analog/Digital Pins Configuration During       ICSP Operations       28         Connection Requirements       23         External Oscillator Pins       27         ICSP Programming Pins       26         Master Clear (MCLR) Pin       24         Power Supply Pins       24         Unused I/Os       28         Voltage Regulator Pins       25 | Getting Started with 16-Bit MCUs         |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----|

| Connection Requirements23External Oscillator Pins27ICSP Programming Pins26Master Clear (MCLR) Pin24Power Supply Pins24Unused I/Os28                                                                                                                                                                                                                | Analog/Digital Pins Configuration During |    |

| External Oscillator Pins27ICSP Programming Pins26Master Clear (MCLR) Pin24Power Supply Pins24Unused I/Os28                                                                                                                                                                                                                                         | ICSP Operations                          |    |

| ICSP Programming Pins                                                                                                                                                                                                                                                                                                                              | Connection Requirements                  |    |

| Master Clear (MCLR) Pin                                                                                                                                                                                                                                                                                                                            | External Oscillator Pins                 |    |

| Power Supply Pins                                                                                                                                                                                                                                                                                                                                  | ICSP Programming Pins                    |    |

| Unused I/Os                                                                                                                                                                                                                                                                                                                                        | Master Clear (MCLR) Pin                  | 24 |

|                                                                                                                                                                                                                                                                                                                                                    | Power Supply Pins                        | 24 |

| Voltage Regulator Pins25                                                                                                                                                                                                                                                                                                                           | Unused I/Os                              |    |

|                                                                                                                                                                                                                                                                                                                                                    | Voltage Regulator Pins                   |    |

#### Н

| I                                         |

|-------------------------------------------|

| I/O Ports                                 |

| Analog Port Pins Configuration (ANSx)     |

| Analog/Digital Function of an I/O Pin 174 |

| Input Change Notification (ICN) 177       |

| Open-Drain Configuration174               |

| Parallel (PIO)173                         |

| Peripheral Pin Select178                  |

| Pull-ups and Pull-Downs177                |

| Write/Read Timing 174                     |

| l <sup>2</sup> C                          |

| Communicating as Master in Single         |

| Master Environment245                     |

| Reserved Addresses                        |

| Setting Baud Rate as Bus Master           |

| Slave Address Masking247                  |

| In-Circuit Debuggers                      |

| MPLAB ICD 3 405                           |

| PICkit 3 405                              |

| In-Circuit Emulator System                |

| MPLAB REAL ICE405                         |

| Input Capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-Bit Cascaded Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 212                                                                                                                                                         |

| Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                             |

| Synchronous and Trigger Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                             |

| Input Capture with Dedicated Timers<br>Input Voltage Levels for Port or Pin Tolerated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                             |

| Description Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 174                                                                                                                                                         |

| Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                             |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 409                                                                                                                                                         |

| Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 407                                                                                                                                                         |

| Symbols Used in Opcode Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                             |