#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                     |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT        |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb202-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

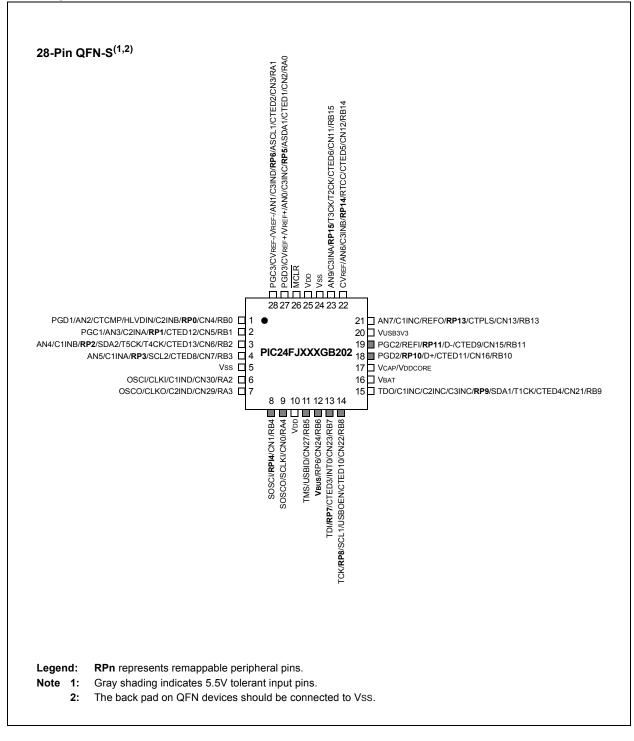

# **Pin Diagrams (Continued)**

|              | Pin Num                       | oer/Grid        | Locator            |     |                 |                         |  |  |  |

|--------------|-------------------------------|-----------------|--------------------|-----|-----------------|-------------------------|--|--|--|

| Pin Function | 28-Pin<br>SPDIP/SOIC/<br>SSOP | 28-Pin<br>QFN-S | 44-Pin<br>TQFP/QFN | I/O | Input<br>Buffer | Description             |  |  |  |

| RB0          | 4                             | 1               | 21                 | I/O | ST              | PORTB Digital I/Os.     |  |  |  |

| RB1          | 5                             | 2               | 22                 | I/O | ST              |                         |  |  |  |

| RB2          | 6                             | 3               | 23                 | I/O | ST              |                         |  |  |  |

| RB3          | 7                             | 4               | 24                 | I/O | ST              |                         |  |  |  |

| RB4          | 11                            | 8               | 33                 | Ι   | ST              |                         |  |  |  |

| RB5          | 14                            | 11              | 41                 | I/O | ST              |                         |  |  |  |

| RB6          | 15                            | 12              | 42                 | I/O | ST              |                         |  |  |  |

| RB7          | 16                            | 13              | 43                 | I/O | ST              |                         |  |  |  |

| RB8          | 17                            | 14              | 44                 | I/O | ST              |                         |  |  |  |

| RB9          | 18                            | 15              | 1                  | I/O | ST              |                         |  |  |  |

| RB10         | 21                            | 18              | 8                  | I/O | ST              |                         |  |  |  |

| RB11         | 22                            | 19              | 9                  | I/O | ST              |                         |  |  |  |

| RB13         | 24                            | 21              | 11                 | I/O | ST              |                         |  |  |  |

| RB14         | 25                            | 22              | 14                 | I/O | ST              |                         |  |  |  |

| RB15         | 26                            | 23              | 15                 | I/O | ST              |                         |  |  |  |

| RC0          | —                             | —               | 25                 | I/O | ST              | PORTC Digital I/Os.     |  |  |  |

| RC1          | —                             | —               | 26                 | I/O | ST              |                         |  |  |  |

| RC2          | —                             |                 | 27                 | I/O | ST              |                         |  |  |  |

| RC3          |                               | _               | 36                 | I/O | ST              | ]                       |  |  |  |

| RC4          |                               |                 | 37                 | I/O | ST              |                         |  |  |  |

| RC5          | —                             |                 | 38                 | I/O | ST              |                         |  |  |  |

| RC6          | _                             | _               | 2                  | I/O | ST              | ]                       |  |  |  |

| RC7          | —                             |                 | 3                  | I/O | ST              |                         |  |  |  |

| RC8          | —                             | —               | 4                  | I/O | ST              |                         |  |  |  |

| RC9          | _                             | _               | 5                  | I/O | ST              |                         |  |  |  |

| REFI         | 22                            | 19              | 9                  |     |                 | Reference Clock Input.  |  |  |  |

| REFO         | 24                            | 21              | 11                 | —   | _               | Reference Clock Output. |  |  |  |

#### **TABLE 1-3:** PIC24FJ128GB204 FAMILY PINOUT DESCRIPTION (CONTINUED)

ANA = Analog input  $l^2C$  = ST with  $l^2C^{TM}$  or SMBus levels

O = Output

P = Power

© 2013-2015 Microchip Technology Inc.

# 3.0 CPU

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the CPU, refer to the "dsPIC33/PIC24 Family Reference Manual", "CPU with Extended Data Space (EDS)" (DS39732). The information in this data sheet supersedes the information in the FRM.

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a Data, Address or Address Offset register. The 16<sup>th</sup> Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

The lower 32 Kbytes of the Data Space (DS) can be accessed linearly. The upper 32 Kbytes of the Data Space are referred to as Extended Data Space to which the extended data RAM, EPMP memory space or program memory can be mapped.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs. The core supports Inherent (no operand), Relative, Literal and Memory Direct Addressing modes, along with three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements.

For most instructions, the core is capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (that is, A + B = C) to be executed in a single cycle.

A high-speed, 17-bit x 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit x 16-bit or 8-bit x 8-bit, integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit, integer signed and unsigned division. All divide operations require 19 cycles to complete but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to 8 sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is shown in Figure 3-1.

# 3.1 Programmer's Model

The programmer's model for the PIC24F is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions.

A description of each register is provided in Table 3-1. All registers associated with the programmer's model are memory-mapped.

| TABI F 4-27 <sup>.</sup> | <b>CRC REGISTER MAP</b> |

|--------------------------|-------------------------|

| ADLL = -21.              |                         |

| © 20        | TABLE 4-2    | 27:  | CRC RE | GISTE  | R MAP  |         |         |         |         |             |   |

|-------------|--------------|------|--------|--------|--------|---------|---------|---------|---------|-------------|---|

| 2013-2015   | File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8       |   |

| 5 Microchin | CRCCON1      | 0158 | CRCEN  |        | CSIDL  | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0      | - |

|             | CRCCON2      | 015A | _      | _      | _      | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0     |   |

|             | CRCXORL      | 015C |        |        |        |         |         |         |         | X<15:1>     |   |

|             | CRCXORH      | 015E |        |        |        |         |         |         |         | X<31:       | 1 |

|             | CRCDATL      | 0160 |        |        |        |         |         |         | CRC     | Data Input  | F |

|             | CRCDATH      | 0162 |        |        |        |         |         |         | CRC     | Data Input  | F |

|             | CRCWDATL     | 0164 |        |        |        |         |         |         | CF      | RC Result R | e |

|             | CRCWDATH     | 0166 |        |        |        |         |         |         | CF      | RC Result R | e |

|             |              |      |        |        |        |         |         |         |         |             |   |

Legend: — = unimplemented, read as '0'; x = unknown value on Reset. Reset values are shown in hexadecimal.

### TABLE 4-28: PERIPHERAL PIN SELECT REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12    | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7 | Bit 6 | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     | All<br>Resets |

|--------------|------|--------|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|-------|-----------|-----------|-----------|-----------|-----------|-----------|---------------|

| RPINR0       | 038C | _      | _      | INT1R5    | INT1R4    | INT1R3    | INT1R2    | INT1R1    | INT1R0    | _     | _     | OCTRIG1R5 | OCTRIG1R4 | OCTRIG1R3 | OCTRIG1R2 | OCTRIG1R1 | OCTRIG1R0 | 3F3F          |

| RPINR1       | 038E | -      | -      | INT3R5    | INT3R4    | INT3R3    | INT3R2    | INT3R1    | INT3R0    | _     | _     | INT2R5    | INT2R4    | INT2R3    | INT2R2    | INT2R1    | INT2R0    | 3F3F          |

| RPINR2       | 0390 | -      | -      | OCTRIG2R5 | OCTRIG2R4 | OCTRIG2R3 | OCTRIG2R2 | OCTRIG2R1 | OCTRIG2R0 | _     | _     | INT4R5    | INT4R4    | INT4R3    | INT4R2    | INT4R1    | INT4R0    | 3F3F          |

| RPINR7       | 039A | _      | _      | IC2R5     | IC2R4     | IC2R3     | IC2R2     | IC2R1     | IC2R0     | _     | _     | IC1R5     | IC1R4     | IC1R3     | IC1R2     | IC1R1     | IC1R0     | 3F3F          |

| RPINR8       | 039C | —      | _      | IC4R5     | IC4R4     | IC4R3     | IC4R2     | IC4R1     | IC4R0     | _     | _     | IC3R5     | IC3R4     | IC3R3     | IC3R2     | IC3R1     | IC3R0     | 3F3F          |

| RPINR9       | 039E | _      | _      | IC6R5     | IC6R4     | IC6R3     | IC6R2     | IC6R1     | IC6R0     | _     | _     | IC5R5     | IC5R4     | IC5R3     | IC5R2     | IC5R1     | IC5R0     | 3F3F          |

| RPINR11      | 03A2 | —      | _      | OCFBR5    | OCFBR4    | OCFBR3    | OCFBR2    | OCFBR1    | OCFBR0    | —     | —     | OCFAR5    | OCFAR4    | OCFAR3    | OCFAR2    | OCFAR1    | OCFAR0    | 3F3F          |

| RPINR17      | 03AE | —      | _      |           |           | U3RXF     | ?<5:0>    |           |           | _     | _     | _         | _         | _         | -         | _         | _         | 3F00          |

| RPINR18      | 03B0 | _      | _      | U1CTSR5   | U1CTSR4   | U1CTSR3   | U1CTSR2   | U1CTSR1   | U1CTSR0   | _     | _     | U1RXR5    | U1RXR4    | U1RXR3    | U1RXR2    | U1RXR1    | U1RXR0    | 3F3F          |

| RPINR19      | 03B2 | —      | _      | U2CTSR5   | U2CTSR4   | U2CTSR3   | U2CTSR2   | U2CTSR1   | U2CTSR0   | —     | —     | U2RXR5    | U2RXR4    | U2RXR3    | U2RXR2    | U2RXR1    | U2RXR0    | 3F3F          |

| RPINR20      | 03B4 | —      | —      | SCK1R5    | SCK1R4    | SCK1R3    | SCK1R2    | SCK1R1    | SCK1R0    | —     | _     | SDI1R5    | SDI1R4    | SDI1R3    | SDI1R2    | SDI1R1    | SDI1R0    | 3F3F          |

| RPINR21      | 03B6 | _      | _      | U3CTSR5   | U3CTSR4   | U3CTSR3   | U3CTSR2   | U3CTSR1   | U3CTSR0   | _     | _     | SS1R5     | SS1R4     | SS1R3     | SS1R2     | SS1R1     | SS1R0     | 3F3F          |

| RPINR22      | 03B8 | —      | _      | SCK2R5    | SCK2R4    | SCK2R3    | SCK2R2    | SCK2R1    | SCK2R0    | —     | —     | SDI2R5    | SDI2R4    | SDI2R3    | SDI2R2    | SDI2R1    | SDI2R0    | 3F3F          |

| RPINR23      | 03BA | —      | —      | TMRCKR5   | TMRCKR4   | TMRCKR3   | TMRCKR2   | TMRCKR1   | TMRCKR0   | —     | _     | SS2R5     | SS2R4     | SS2R3     | SS2R2     | SS2R1     | SS2R0     | 3F3F          |

| RPINR27      | 03C2 | _      | _      | U4CTSR5   | U4CTSR4   | U4CTSR3   | U4CTSR2   | U4CTSR1   | U4CTSR0   | _     | _     | U4RXR5    | U4RXR4    | U4RXR3    | U4RXR2    | U4RXR1    | U4RXR0    | 3F3F          |

| RPINR28      | 03C4 | _      | _      | SCK3R5    | SCK3R4    | SCK3R3    | SCK3R2    | SCK3R1    | SCK3R0    | _     | -     | SDI3R5    | SDI3R4    | SDI3R3    | SDI3R2    | SDI3R1    | SDI3R0    | 3F3F          |

| RPINR29      | 03C6 | _      | _      | _         | _         | _         | _         | _         | _         | _     |       |           |           | SS3R      | <5:0>     |           |           | 003F          |

| RPINR30      | 03C8 | _      | _      | _         | _         | _         | _         | _         | _         | _     | -     |           |           | MDMIF     | <5:0>     |           |           | 003F          |

| RPINR31      | 03CA | _      |        | MDC2R5    | MDC2R4    | MDC2R3    | MDC2R2    | MDC2R1    | MDC2R0    | _     | -     | MDC1R5    | MDC1R4    | MDC1R3    | MDC1R2    | MDC1R1    | MDC1R0    | 3F3F          |

X<31:16>

CRC Data Input Register Low

CRC Data Input Register High

CRC Result Register Low

CRC Result Register High

Bit 7

CRCFUL

\_

Bit 6

CRCMPT

Bit 5

CRCISEL

\_

Bit 4

CRCGO

PLEN4

Bit 3

LENDIAN

PLEN3

Bit 2

\_

PLEN2

Bit 1

\_

PLEN1

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All

Resets

0040

0000

0000

0000

XXXX

XXXX

XXXX

XXXX

Bit 0

\_

PLEN0

\_

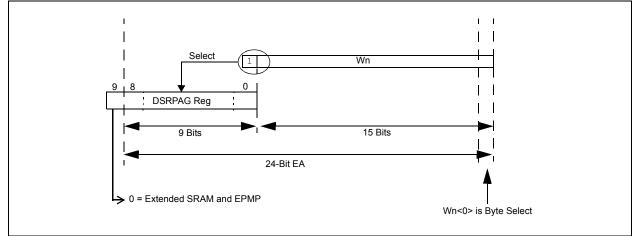

# 4.2.5.1 Data Read from EDS

In order to read the data from the EDS space first, an Address Pointer is set up by loading the required EDS page number into the DSRPAG register and assigning the offset address to one of the W registers. Once the above assignment is done, the EDS window is enabled by setting bit 15 of the Working register assigned with the offset address; then, the contents of the pointed EDS location can be read.

Figure 4-5 illustrates how the EDS space address is generated for read operations.

When the Most Significant bit of the EA is '1' and DSRPAG<9> = 0, the lower 9 bits of DSRPAG are concatenated to the lower 15 bits of the EA to form a 24-bit EDS space address for read operations.

Example 4-1 shows how to read a byte, word and double-word from EDS.

Note: All read operations from EDS space have an overhead of one instruction cycle. Therefore, a minimum of two instruction cycles is required to complete an EDS read. EDS reads under the REPEAT instruction; the first two accesses take three cycles and the subsequent accesses take one cycle.

### FIGURE 4-5: EDS ADDRESS GENERATION FOR READ OPERATIONS

### EXAMPLE 4-1: EDS READ CODE IN ASSEMBLY

```

; Set the EDS page from where the data to be read

#0x0002, w0

mov

mov

w0, DSRPAG ;page 2 is selected for read

#0x0800, w1 ;select the location (0x800) to be read

mov

w1, #15

;set the MSB of the base address, enable EDS mode

bset

;Read a byte from the selected location

mov.b

[w1++], w2 ;read Low byte

[w1++], w3

;read High byte

mov.b

;Read a word from the selected location

mov

[w1], w2

;

;Read Double - word from the selected location

mov.d

[w1], w2

;two word read, stored in w2 and w3

```

#### REGISTER 8-16: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3 (CONTINUED)

- bit 1 SI2C2IE: Slave I2C2 Event Interrupt Enable bit 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 0 Unimplemented: Read as '0'

- Note 1: If an external interrupt is enabled, the interrupt input must also be configured to an available RPn or RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

### REGISTER 8-38: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0             | U-0 | U-0              | U-0 | U-0               | U-0             | U-0                | U-0   |  |

|-----------------|-----|------------------|-----|-------------------|-----------------|--------------------|-------|--|

| _               | —   | —                | —   | —                 | —               | —                  |       |  |

| bit 15          |     |                  |     |                   |                 |                    | bit 8 |  |

|                 |     |                  |     |                   |                 |                    |       |  |

| U-0             | U-0 | U-0              | U-0 | U-0               | R/W-1           | R/W-0              | R/W-0 |  |

| _               | —   | —                | —   | —                 |                 |                    |       |  |

| bit 7           |     |                  |     |                   |                 |                    | bit 0 |  |

|                 |     |                  |     |                   |                 |                    |       |  |

| Legend:         |     |                  |     |                   |                 |                    |       |  |

| R = Readable    | bit | W = Writable     | bit | U = Unimplem      | nented bit, rea | d as '0'           |       |  |

| -n = Value at I | POR | '1' = Bit is set |     | '0' = Bit is clea | ared            | x = Bit is unknown |       |  |

bit 15-3 Unimplemented: Read as '0'

- HLVDIP<2:0>: High/Low-Voltage Detect Interrupt Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

bit 2-0

- •

- 001 = Interrupt is Priority 1

- 000 = Interrupt source is disabled

#### REGISTER 8-39: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

| U-0    | U-0   | U-0   | U-0   | U-0 | U-0 | U-0 | U-0   |

|--------|-------|-------|-------|-----|-----|-----|-------|

| —      | —     | —     | —     |     | —   | —   | —     |

| bit 15 |       |       |       |     |     |     | bit 8 |

|        |       |       |       |     |     |     |       |

| U-0    | R/W-1 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

| 00    | 1000 | 1010 0      | 10110 | 00 | 00 | 00 | 00    |

|-------|------|-------------|-------|----|----|----|-------|

| —     |      | CTMUIP<2:0> |       | —  | —  | —  | —     |

| bit 7 |      |             |       |    |    |    | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 6-4  | CTMUIP<2:0>: CTMU Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

| bit 3-0  | Unimplemented: Read as '0'                                 |

|                  | R/W-1                                                                                                                             | R/W-0                                                                                            | R/W-0                                                 | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|

| —                | U3TXIP2                                                                                                                           | U3TXIP1                                                                                          | U3TXIP0                                               | —                 | U3RXIP2          | U3RXIP1         | U3RXIP0 |  |  |  |  |  |

| bit 15           |                                                                                                                                   |                                                                                                  |                                                       |                   |                  |                 | bita    |  |  |  |  |  |

| U-0              | R/W-1                                                                                                                             | R/W-0                                                                                            | R/W-0                                                 | U-0               | U-0              | U-0             | U-0     |  |  |  |  |  |

| _                | U3ERIP2                                                                                                                           | U3ERIP1                                                                                          | U3ERIP0                                               | _                 | _                | _               | _       |  |  |  |  |  |

| bit 7            |                                                                                                                                   |                                                                                                  |                                                       |                   |                  |                 | bit     |  |  |  |  |  |

| Legend:          |                                                                                                                                   |                                                                                                  |                                                       |                   |                  |                 |         |  |  |  |  |  |

| R = Readab       | le hit                                                                                                                            | W = Writable                                                                                     | nit                                                   | U = Unimplen      | nented bit, read | l as '0'        |         |  |  |  |  |  |

| -n = Value a     |                                                                                                                                   | '1' = Bit is set                                                                                 |                                                       | '0' = Bit is clea |                  | x = Bit is unkr | own     |  |  |  |  |  |

|                  |                                                                                                                                   |                                                                                                  |                                                       |                   | area             |                 | lowin   |  |  |  |  |  |

| bit 15           | Unimplemen                                                                                                                        | ted: Read as '                                                                                   | )'                                                    |                   |                  |                 |         |  |  |  |  |  |

| bit 14-12        | -                                                                                                                                 |                                                                                                  |                                                       | ot Priority bits  |                  |                 |         |  |  |  |  |  |

|                  | <b>U3TXIP&lt;2:0&gt;:</b> UART3 Transmitter Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                                                                                  |                                                       |                   |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                                                                 |                                                                                                  | lightest phones                                       | (interrupt)       |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                                                                 |                                                                                                  |                                                       |                   |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                                                                 |                                                                                                  |                                                       |                   |                  |                 |         |  |  |  |  |  |

|                  | 001 = Interru<br>000 = Interru                                                                                                    | ot is Priority 1<br>ot source is disa                                                            | abled                                                 |                   |                  |                 |         |  |  |  |  |  |

| bit 11           | Unimplemen                                                                                                                        | ted: Read as '                                                                                   | )'                                                    |                   |                  |                 |         |  |  |  |  |  |

| bit 10-8         | U3RXIP<2:0>: UART3 Receiver Interrupt Priority bits                                                                               |                                                                                                  |                                                       |                   |                  |                 |         |  |  |  |  |  |

|                  | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                        |                                                                                                  |                                                       |                   |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                                                                 |                                                                                                  |                                                       |                   |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                                                                 |                                                                                                  |                                                       |                   |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                                                                 |                                                                                                  |                                                       |                   |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                                                                 |                                                                                                  |                                                       |                   |                  |                 |         |  |  |  |  |  |

|                  | •<br>•<br>001 = Interrup<br>000 = Interrup                                                                                        |                                                                                                  | abled                                                 |                   |                  |                 |         |  |  |  |  |  |

| bit 7            | 000 = Interru                                                                                                                     | ot source is dis                                                                                 |                                                       |                   |                  |                 |         |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen                                                                                                       | ot source is disa<br>ted: Read as '0                                                             | )'                                                    | ritv bits         |                  |                 |         |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                                                                                        | ot source is dis<br>ted: Read as '(<br>•: UART3 Error                                            | )'<br>Interrupt Prio                                  | •                 |                  |                 |         |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                                                                                        | ot source is disa<br>ted: Read as '0                                                             | )'<br>Interrupt Prio                                  | •                 |                  |                 |         |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                                                                                        | ot source is dis<br>ted: Read as '(<br>•: UART3 Error                                            | )'<br>Interrupt Prio                                  | •                 |                  |                 |         |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0><br>111 = Interru<br>•                                                                  | ot source is dis<br>ted: Read as '(<br>: UART3 Error<br>ot is Priority 7 ()                      | )'<br>Interrupt Prio                                  | •                 |                  |                 |         |  |  |  |  |  |

| bit 7<br>bit 6-4 | 000 = Interrup<br>Unimplemen<br>U3ERIP<2:0><br>111 = Interrup<br>•<br>•<br>•<br>001 = Interrup                                    | ot source is dis<br>ted: Read as '(<br>•: UART3 Error<br>ot is Priority 7 (1<br>ot is Priority 1 | ) <sup>,</sup><br>Interrupt Prior<br>highest priority | •                 |                  |                 |         |  |  |  |  |  |

|                  | 000 = Interrup<br>Unimplemen<br>U3ERIP<2:0><br>111 = Interrup                                                                     | ot source is dis<br>ted: Read as '(<br>: UART3 Error<br>ot is Priority 7 ()                      | )'<br>Interrupt Prior<br>highest priority<br>abled    | •                 |                  |                 |         |  |  |  |  |  |

#### REGISTER 8-40: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

#### REGISTER 8-43: IPC26: INTERRUPT PRIORITY CONTROL REGISTER 26

| U-0          | U-0           | U-0                                   | U-0              | U-0                                | R/W-1 | R/W-0           | R/W-0 |  |  |

|--------------|---------------|---------------------------------------|------------------|------------------------------------|-------|-----------------|-------|--|--|

| _            | —             | —                                     | —                |                                    |       | FSTIP<2:0>      |       |  |  |

| bit 15       |               |                                       |                  |                                    |       |                 | bit 8 |  |  |

|              |               |                                       |                  |                                    |       |                 |       |  |  |

| U-0          | U-0           | U-0                                   | U-0              | U-0                                | U-0   | U-0             | U-0   |  |  |

|              | —             | —                                     | _                |                                    | —     | _               | —     |  |  |

| bit 7        | ÷             | •                                     |                  |                                    | •     | ·               | bit 0 |  |  |

|              |               |                                       |                  |                                    |       |                 |       |  |  |

| Legend:      |               |                                       |                  |                                    |       |                 |       |  |  |

| R = Readab   | ole bit       | W = Writable I                        | oit              | U = Unimplemented bit, read as '0' |       |                 |       |  |  |

| -n = Value a | t POR         | '1' = Bit is set                      |                  | '0' = Bit is clea                  | ared  | x = Bit is unkn | own   |  |  |

|              |               |                                       |                  |                                    |       |                 |       |  |  |

| bit 15-11    | Unimplemen    | ited: Read as '0                      | )'               |                                    |       |                 |       |  |  |

| bit 10-8     | FSTIP<2:0>:   | FRC Self-Tune                         | Interrupt Prior  | ity bits                           |       |                 |       |  |  |

|              | 111 = Interru | pt is Priority 7 (I                   | nighest priority | interrupt)                         |       |                 |       |  |  |

|              | •             |                                       |                  |                                    |       |                 |       |  |  |

|              | •             |                                       |                  |                                    |       |                 |       |  |  |

|              | •             |                                       |                  |                                    |       |                 |       |  |  |

|              |               | pt is Priority 1<br>pt source is disa | ahled            |                                    |       |                 |       |  |  |

| bit 7-0      |               | ited: Read as '0                      |                  |                                    |       |                 |       |  |  |

|              | ommplemen     | iteu. iteau as (                      | ,                |                                    |       |                 |       |  |  |

#### REGISTER 8-44: IPC29: INTERRUPT PRIORITY CONTROL REGISTER 29

| U-0          | U-0           | U-0                 | U-0              | U-0                                | U-0      | U-0                | U-0      |  |

|--------------|---------------|---------------------|------------------|------------------------------------|----------|--------------------|----------|--|

| _            | —             | —                   | —                | _                                  | —        | —                  | —        |  |

| bit 15       |               |                     |                  |                                    |          |                    | bit 8    |  |

|              |               |                     |                  |                                    |          |                    |          |  |

| U-0          | R/W-1         | R/W-0               | R/W-0            | U-0                                | U-0      | U-0                | U-0      |  |

| _            |               | JTAGIP<2:0>         |                  |                                    | <u> </u> |                    | <u> </u> |  |

| bit 7        |               |                     |                  |                                    |          |                    | bit 0    |  |

|              |               |                     |                  |                                    |          |                    |          |  |

| Legend:      |               |                     |                  |                                    |          |                    |          |  |

| R = Readat   | ole bit       | W = Writable b      | oit              | U = Unimplemented bit, read as '0' |          |                    |          |  |

| -n = Value a | at POR        | '1' = Bit is set    |                  | '0' = Bit is cleared               |          | x = Bit is unknown |          |  |

|              |               |                     |                  |                                    |          |                    |          |  |

| bit 15-7     | Unimplemer    | nted: Read as '0    | )'               |                                    |          |                    |          |  |

| bit 6-4      | JTAGIP<2:0    | >: JTAG Interrup    | ot Priority bits |                                    |          |                    |          |  |

|              | 111 = Interru | pt is Priority 7 (ł | nighest priority | interrupt)                         |          |                    |          |  |

|              | •             |                     |                  |                                    |          |                    |          |  |

|              | •             |                     |                  |                                    |          |                    |          |  |

|              |               |                     |                  |                                    |          |                    |          |  |

|              |               | pt is Priority 1    |                  |                                    |          |                    |          |  |

|              |               | pt source is disa   |                  |                                    |          |                    |          |  |

| bit 3-0      | Unimplemer    | nted: Read as '0    | )'               |                                    |          |                    |          |  |

|              |               |                     |                  |                                    |          |                    |          |  |

| R/W-0        | R/W-0                                                    | R/W-0                                 | R/W-0          | R/W-0                | R/W-0           | R/W-0           | R/W-1  |  |  |  |

|--------------|----------------------------------------------------------|---------------------------------------|----------------|----------------------|-----------------|-----------------|--------|--|--|--|

| ROI          | DOZE2                                                    | DOZE1                                 | DOZE0          | DOZEN <sup>(1)</sup> | RCDIV2          | RCDIV1          | RCDIV0 |  |  |  |

| bit 15       |                                                          |                                       | •              |                      |                 | •               | bit 8  |  |  |  |

|              |                                                          |                                       |                |                      |                 |                 |        |  |  |  |

| R/W-0        | R/W-0                                                    | R/W-0                                 | U-0            | U-0                  | U-0             | U-0             | U-0    |  |  |  |

| CPDIV1       | CPDIV0                                                   | PLLEN                                 | _              | —                    | —               |                 | _      |  |  |  |

| bit 7        |                                                          |                                       |                |                      |                 |                 | bit (  |  |  |  |

|              |                                                          |                                       |                |                      |                 |                 |        |  |  |  |

| Legend:      |                                                          |                                       |                |                      |                 |                 |        |  |  |  |

| R = Readab   |                                                          | W = Writable                          |                | U = Unimplem         |                 |                 |        |  |  |  |

| -n = Value a | t POR                                                    | '1' = Bit is set                      |                | '0' = Bit is clea    | ared            | x = Bit is unkr | nown   |  |  |  |

| L:1 4 F      |                                                          | n an Internuet b                      |                |                      |                 |                 |        |  |  |  |

| bit 15       |                                                          | er on Interrupt b                     |                | set the CPU peri     | oboral clock re | atio to 1.1     |        |  |  |  |

|              |                                                          | s have no effect                      |                |                      |                 |                 |        |  |  |  |

| bit 14-12    |                                                          | CPU Periphera                         |                |                      |                 |                 |        |  |  |  |

|              | 111 = 1:128                                              |                                       |                |                      |                 |                 |        |  |  |  |

|              | 110 <b>= 1:64</b>                                        |                                       |                |                      |                 |                 |        |  |  |  |

|              | 101 <b>= 1:32</b>                                        |                                       |                |                      |                 |                 |        |  |  |  |

|              | 100 = 1:16                                               |                                       |                |                      |                 |                 |        |  |  |  |

|              | 011 = 1:8                                                |                                       |                |                      |                 |                 |        |  |  |  |

|              | 010 = 1:4<br>001 = 1:2                                   |                                       |                |                      |                 |                 |        |  |  |  |

|              | 001 = 1.2<br>000 = 1.1                                   |                                       |                |                      |                 |                 |        |  |  |  |

| bit 11       | DOZEN: Doz                                               | DOZEN: Doze Enable bit <sup>(1)</sup> |                |                      |                 |                 |        |  |  |  |

|              | 1 = DOZE<2                                               | :0> bits specify                      | the CPU perip  | oheral clock ratio   |                 |                 |        |  |  |  |

|              |                                                          | ipheral clock rat                     |                |                      |                 |                 |        |  |  |  |

| bit 10-8     | RCDIV<2:0>                                               | : FRC Postscal                        | er Select bits |                      |                 |                 |        |  |  |  |

|              | 111 <b>= 31.25</b>                                       | kHz (divide-by-                       | 256)           |                      |                 |                 |        |  |  |  |

|              | 110 = 125 kHz (divide-by-64)                             |                                       |                |                      |                 |                 |        |  |  |  |

|              | 101 = 250 kHz (divide-by-32)                             |                                       |                |                      |                 |                 |        |  |  |  |

|              | 100 = 500  kHz (divide-by-16)                            |                                       |                |                      |                 |                 |        |  |  |  |

|              | 011 = 1 MHz (divide-by-8)<br>010 = 2 MHz (divide-by-4)   |                                       |                |                      |                 |                 |        |  |  |  |

|              | 010 = 2  MHz (divide-by-4)<br>001 = 4  MHz (divide-by-2) |                                       |                |                      |                 |                 |        |  |  |  |

|              |                                                          | (divide-by-1)                         |                |                      |                 |                 |        |  |  |  |

| bit 7-6      | CPDIV<1:0>                                               | : USB System                          | Clock Select b | its (postscaler se   | elected from 3  | 2 MHz clock br  | anch)  |  |  |  |

|              | 11 = 4 MHz (divide-by-8) <sup>(2)</sup>                  |                                       |                |                      |                 |                 |        |  |  |  |

|              | $10 = 8 \text{ MHz} (divide-by-4)^{(2)}$                 |                                       |                |                      |                 |                 |        |  |  |  |

|              | 01 = 16  MHz  (divide-by-2)                              |                                       |                |                      |                 |                 |        |  |  |  |

|              |                                                          | (divide-by-1)                         |                |                      |                 |                 |        |  |  |  |

| bit 5        | PLLEN: PLL                                               |                                       |                |                      |                 |                 |        |  |  |  |

|              | 1 = PLL is er<br>0 = PLL is di                           |                                       |                |                      |                 |                 |        |  |  |  |

| bit 4-0      |                                                          | nted: Read as '                       | ∩ <b>'</b>     |                      |                 |                 |        |  |  |  |

| DIL 4-0      | ommplemen                                                | neu. nedu ds                          | U              |                      |                 |                 |        |  |  |  |

| Note 1: T    | his bit is autom                                         | atically cleared                      | when the ROI   | bit is set and an    | interrupt occu  | irs             |        |  |  |  |

**Note 1:** This bit is automatically cleared when the ROI bit is set and an interrupt occurs.

2: This setting is not allowed while the USB module is enabled.

# 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. In an application that needs to use more than one peripheral multiplexed on a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

The Peripheral Pin Select (PPS) feature provides an alternative to these choices by enabling the user's peripheral set selection and its placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of any one of many digital peripherals to any one of these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The PPS feature is used with a range of up to 44 pins, depending on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

PIC24FJ128GB204 family devices support a larger number of remappable input only pins than remappable input/output pins. In this device family, there are up to 25 remappable input/output pins, depending on the pin count of the particular device selected. These pins are numbered, RP0 through RP25.

See Table 1-3 for a summary of pinout options in each package offering.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals. PPS is not available for these peripherals:

- I<sup>2</sup>C<sup>™</sup> (input and output)

- USB (all module inputs and outputs)

- Change Notification Inputs

- RTCC Alarm Output(s)

- EPMP Signals (input and output)

- · Analog (inputs and outputs)

- INT0

A key difference between pin select and non-pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

#### 11.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (e.g., OC, UART transmit) will take priority over general purpose digital functions on a pin, such as EPMP and port I/O. Specialized digital outputs (e.g., USB on USB-enabled devices) will take priority over PPS outputs on the same pin. The pin diagrams list peripheral outputs in the order of priority. Refer to them for priority concerns on a particular pin.

Unlike PIC24F devices with fixed peripherals, pin-selectable peripheral inputs will never take ownership of a pin. The pin's output buffer will be controlled by the TRISx setting or by a fixed peripheral on the pin. If the pin is configured in Digital mode, then the PPS input will operate correctly. If an analog function is enabled on the pin, the PPS input will be disabled.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of Special Function Registers (SFRs): one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on if an input or an output is being mapped.

### 17.2 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator reload value, use Equation 17-1.

EQUATION 17-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1)</sup>

$$I2CxBRG = \left( \left( \frac{1}{FSCL} - PGDx \right) \times \frac{FCY}{2} \right) - 2$$

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

# 17.3 Slave Address Masking

The I2CxMSK register (Register 17-4) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond, whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '0010000000', the slave module will detect both addresses, '000000000' and '001000000'.

To enable address masking, the Intelligent Peripheral Management Interface (IPMI) must be disabled by clearing the STRICT bit (I2CxCONL<11>).

Note: As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 17-1 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| TABLE 17-1: | I <sup>2</sup> C <sup>™</sup> RESERVED ADDRESSES <sup>(1)</sup> |

|-------------|-----------------------------------------------------------------|

|-------------|-----------------------------------------------------------------|

| Slave Address | R/W Bit | Description                            |

|---------------|---------|----------------------------------------|

| 0000 000      | 0       | General Call Address <sup>(2)</sup>    |

| 0000 000      | 1       | Start Byte                             |

| 0000 001      | Х       | Cbus Address                           |

| 0000 01x      | х       | Reserved                               |

| 0000 1xx      | Х       | HS Mode Master Code                    |

| 1111 0xx      | х       | 10-Bit Slave Upper Byte <sup>(3)</sup> |

| 1111 1xx      | Х       | Reserved                               |

**Note 1:** The address bits listed here will never cause an address match independent of address mask settings.

2: The address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6       | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | <ul> <li>11 = Interrupt is set on an RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on an RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters</li> </ul> |

| bit 5         | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                                                                                                                                                                                    |

|               | <ul> <li>1 = Address Detect mode is enabled (if 9-bit mode is not selected, this does not take effect)</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                                                             |

| bit 4         | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                                                                                                                                                                                                       |

|               | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                                                                                                                                                                                                      |

| bit 3         | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                  |

|               | <ul> <li>1 = Parity error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                            |

| bit 2         | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                 |

|               | <ul> <li>1 = Framing error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>a = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                          |

| <b>h</b> :4 4 | 0 = Framing error has not been detected                                                                                                                                                                                                                                                                                                                                                                    |

| bit 1         | <b>OERR:</b> Receive Buffer Overrun Error Status bit (clear/read-only)<br>1 = Receive buffer has overflowed                                                                                                                                                                                                                                                                                                |

|               | 1 = Receive buffer has overflowed (clearing a previously set OERR bit (1 → 0 transition); will reset the receive buffer and the RSR to the empty state)                                                                                                                                                                                                                                                    |

| bit 0         | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                                                                                                                                                                                                                 |

|               | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                                              |

| Note 1        | : The value of this bit only affects the transmit properties of the module when the IrDA <sup>®</sup> encoder is enabled (IREN = 1).                                                                                                                                                                                                                                                                       |

2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

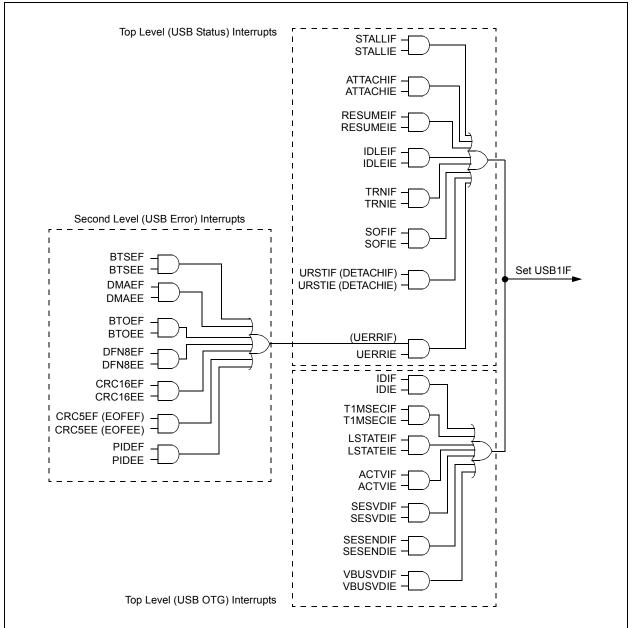

### **19.3 USB Interrupts**

The USB OTG module has many conditions that can be configured to cause an interrupt. All interrupt sources use the same interrupt vector.

Figure 19-9 shows the interrupt logic for the USB module. There are two layers of interrupt registers in the USB module. The top level consists of overall USB status interrupts; these are enabled and flagged in the U1IE and U1IR registers, respectively. The second

level consists of USB error conditions, which are enabled and flagged in the U1EIR and U1EIE registers. An interrupt condition in any of these triggers a USB Error Interrupt Flag (UERRIF) in the top level.

Interrupts may be used to trap routine events in a USB transaction. Figure 19-10 provides some common events within a USB frame and their corresponding interrupts.

#### FIGURE 19-9: USB OTG INTERRUPT FUNNEL

### REGISTER 19-18: U1IE: USB INTERRUPT ENABLE REGISTER (ALL USB MODES)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/K-0, HS   | R/K-0, HS               | R/K-0, HS | R/K-0, HS | R/K-0, HS | R/K-0, HS | R/K-0, HS | R/K-0, HS               |

|-------------|-------------------------|-----------|-----------|-----------|-----------|-----------|-------------------------|

| STALLIE     | ATTACHIE <sup>(1)</sup> | RESUMEIE  | IDLEIE    | TRNIE     | SOFIE     | UERRIE    | URSTIE                  |

|             |                         |           |           |           |           |           | DETACHIE <sup>(1)</sup> |

| bit 7 bit 0 |                         |           |           |           |           |           |                         |

| Legend:           |         | U = Unimplemented bit, re                    | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|---------|----------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readab        | ole bit | K = Write '1' to Clear bit                   | HS = Hardware Settabl              | e bit              |  |  |  |  |

| -n = Value at POR |         | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

|                   |         |                                              |                                    |                    |  |  |  |  |

| bit 15-8          | Unimple | mented: Read as '0'                          |                                    |                    |  |  |  |  |

| hit 7             | STALLE  | STALLE: STALL Handshake Interrunt Enable hit |                                    |                    |  |  |  |  |

|       | •                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit                                                                              |

|       | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                               |

| bit 6 | <b>ATTACHIE:</b> Peripheral Attach Interrupt bit (Host mode only) <sup>(1)</sup>                                           |

|       | 1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                      |

| bit 5 | RESUMEIE: Resume Interrupt bit                                                                                             |

|       | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                               |

| bit 4 | IDLEIE: Idle Detect Interrupt bit                                                                                          |

|       | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                               |

| bit 3 | TRNIE: Token Processing Complete Interrupt bit                                                                             |

|       | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                               |

| bit 2 | SOFIE: Start-of-Frame Token Interrupt bit                                                                                  |

|       | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                               |

| bit 1 | UERRIE: USB Error Condition Interrupt bit                                                                                  |

|       | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                               |

| bit 0 | <b>URSTIE or DETACHIE:</b> USB Reset Interrupt (Device mode) or USB Detach Interrupt (Host mode) Enable bit <sup>(1)</sup> |

|       | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                               |

|       |                                                                                                                            |

| Assembly<br>Mnemonic |       | Assembly Syntax | Description                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|-------|-----------------|------------------------------------------|---------------|----------------|--------------------------|

| ADD                  | ADD   | f               | f = f + WREG                             | 1             | 1              | C, DC, N, OV, Z          |

|                      | ADD   | f,WREG          | WREG = f + WREG                          | 1             | 1              | C, DC, N, OV, 2          |

|                      | ADD   | #lit10,Wn       | Wd = lit10 + Wd                          | 1             | 1              | C, DC, N, OV, 2          |

|                      | ADD   | Wb,Ws,Wd        | Wd = Wb + Ws                             | 1             | 1              | C, DC, N, OV, 2          |

|                      | ADD   | Wb,#lit5,Wd     | Wd = Wb + lit5                           | 1             | 1              | C, DC, N, OV, 2          |

| ADDC                 | ADDC  | f               | f = f + WREG + (C)                       | 1             | 1              | C, DC, N, OV, 2          |

|                      | ADDC  | f,WREG          | WREG = f + WREG + (C)                    | 1             | 1              | C, DC, N, OV, 2          |

|                      | ADDC  | #lit10,Wn       | Wd = lit10 + Wd + (C)                    | 1             | 1              | C, DC, N, OV, 2          |

|                      | ADDC  | Wb,Ws,Wd        | Wd = Wb + Ws + (C)                       | 1             | 1              | C, DC, N, OV, 2          |

|                      | ADDC  | Wb,#lit5,Wd     | Wd = Wb + lit5 + (C)                     | 1             | 1              | C, DC, N, OV, 2          |

| AND                  | AND   | f               | f = f .AND. WREG                         | 1             | 1              | N, Z                     |

|                      | AND   | f,WREG          | WREG = f .AND. WREG                      | 1             | 1              | N, Z                     |

|                      | AND   | #lit10,Wn       | Wd = lit10 .AND. Wd                      | 1             | 1              | N, Z                     |

|                      | AND   | Wb,Ws,Wd        | Wd = Wb .AND. Ws                         | 1             | 1              | N, Z                     |

|                      | AND   | Wb,#lit5,Wd     | Wd = Wb .AND. lit5                       | 1             | 1              | N, Z                     |

| ASR                  | ASR   | f               | f = Arithmetic Right Shift f             | 1             | 1              | C, N, OV, Z              |

|                      | ASR   | f,WREG          | WREG = Arithmetic Right Shift f          | 1             | 1              | C, N, OV, Z              |

|                      | ASR   | Ws,Wd           | Wd = Arithmetic Right Shift Ws           | 1             | 1              | C, N, OV, Z              |

|                      | ASR   | Wb,Wns,Wnd      | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1              | N, Z                     |