Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Betuils                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                      |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT         |

| Number of I/O              | 20                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb202t-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | Pin Num                         | per/Grid                        | Locator |     |                      |                                             |

|--------------|---------------------------------|---------------------------------|---------|-----|----------------------|---------------------------------------------|

| Pin Function | 28-Pin<br>SPDIP/SOIC/<br>SSOP   | 28-Pin 44-Pin<br>QFN-S TQFP/QFN |         | I/O | Input<br>Buffer      | Description                                 |

| RP0          | 4                               | 1                               | 21      | I/O | ST                   | Remappable Peripheral (input or output).    |

| RP1          | 5                               | 2                               | 22      | I/O | ST                   |                                             |

| RP2          | 6                               | 3                               | 23      | I/O | ST                   | ]                                           |

| RP3          | 7                               | 4                               | 24      | I/O | ST                   | ]                                           |

| RP5          | 2                               | 27                              | 19      | I/O | ST                   | ]                                           |

| RP6          | 3,15                            | 28                              | 20      | I/O | ST                   | 1                                           |

| RP7          | 16                              | 13                              | 43      | I/O | ST                   |                                             |

| RP8          | 17                              | 14                              | 44      | I/O | ST                   | 1                                           |

| RP9          | 18                              | 15                              | 1       | I/O | ST                   |                                             |

| RP10         | 21                              | 18                              | 8       | I/O | ST                   |                                             |

| RP11         | 22                              | 19                              | 9       | I/O | ST                   |                                             |

| RP13         | 24                              | 21                              | 11      | I/O | ST                   |                                             |

| RP14         | 25                              | 22                              | 14      | I/O | ST                   |                                             |

| RP15         | 26                              | 23                              | 15      | I/O | ST                   |                                             |

| RP16         | _                               |                                 | 25      | I/O | ST                   |                                             |

| RP17         | _                               |                                 | 26      | I/O | ST                   |                                             |

| RP18         | _                               |                                 | 27      | I/O | ST                   |                                             |

| RP19         | _                               | —                               | 36      | I/O | ST                   |                                             |

| RP20         | _                               |                                 | 37      | I/O | ST                   |                                             |

| RP21         | _                               |                                 | 38      | I/O | ST                   |                                             |

| RP22         | _                               |                                 | 2       | I/O | ST                   |                                             |

| RP23         | _                               |                                 | 3       | I/O | ST                   |                                             |

| RP24         |                                 |                                 | 4       | I/O | ST                   | 1                                           |

| RP25         |                                 |                                 | 5       | I/O | ST                   |                                             |

| RPI4         | 11                              | 8                               | 33      | Ι   | ST                   | Remappable Peripheral (input).              |

| RTCC         | 25                              | 22                              | 14      | 0   | —                    | Real-Time Clock Alarm/Seconds Pulse Output. |

| SCL1         | 17                              | 14                              | 44      | I/O | l <sup>2</sup> C     | I2C1 Synchronous Serial Clock Input/Output. |

| SCL2         | 7                               | 4                               | 24      | I/O | l <sup>2</sup> C     | I2C2 Synchronous Serial Clock Input/Output. |

| SCLKI        | 12                              | 9                               | 34      | Ι   | —                    | Secondary Oscillator Digital Clock Input.   |

| SDA1         | 18                              | 15                              | 1       | I/O | l <sup>2</sup> C     | I2C1 Data Input/Output.                     |

| SDA2         | 6                               | 3                               | 23      | I/O | l <sup>2</sup> C     | I2C2 Data Input/Output.                     |

| SOSCI        | 11                              | 8                               | 33      | Ι   | ANA                  | Secondary Oscillator/Timer1 Clock Input.    |

| SOSCO        | 12                              | 9                               | 34      | 0   | ANA                  | Secondary Oscillator/Timer1 Clock Output.   |

| ANA =        | Schmitt Trigger<br>Analog input | -                               |         |     | = TTL co<br>= Output | pompatible input I = Input<br>P = Power     |

#### **TABLE 1-3**: PIC24FJ128GB204 FAMILY PINOUT DESCRIPTION (CONTINUED)

$I^2C = ST$  with  $I^2C^{TM}$  or SMBus levels

NOTES:

### 6.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Program Memory"** (DS39715). The information in this data sheet supersedes the information in the FRM.

The PIC24FJ128GB204 family of devices contains internal Flash program memory for storing and executing application code. The program memory is readable, writable and erasable. The Flash memory can be programmed in four ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- JTAG

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FJ128GB204 family device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (Vss) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 64 instructions (192 bytes) at a time and erase program memory in blocks of 512 instructions (1536 bytes) at a time.

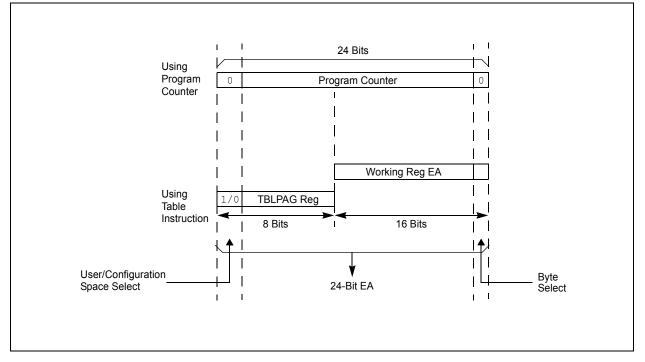

### 6.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 6-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 6-1: ADDRESSING FOR TABLE REGISTERS

#### 10.6 Clock Frequency and Clock Switching

In Run and Idle modes, all PIC24FJ devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in Section 9.0 "Oscillator Configuration".

### 10.7 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

#### 10.8 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing, with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- The Peripheral Enable bit, generically named, "XXXEN", located in the module's main control SFR.

- The Peripheral Module Disable (PMD) bit, generically named, "XXXMD", located in one of the PMDx Control registers (XXXMD bits are in the PMD1, PMD2, PMD3, PMD4, PMD6, PMD7, PMD8 registers).

Both bits have similar functions in enabling or disabling its associated module. Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect and read values will be invalid. Many peripheral modules have a corresponding PMD bit.

In contrast, disabling a module by clearing its XXXEN bit disables its functionality, but leaves its registers available to be read and written to. Power consumption is reduced, but not by as much as the use of the PMD bits. Most peripheral modules have an enable bit; exceptions include capture, compare and RTCC.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, "XXXSIDL". By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature disables the module while in Idle mode, allowing further reduction of power consumption during Idle mode, enhancing power savings for extremely critical power applications.

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| _      | —   | RP9R5 | RP9R4 | RP9R3 | RP9R2 | RP9R1 | RP9R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP8R5 | RP8R4 | RP8R3 | RP8R2 | RP8R1 | RP8R0 |

| bit 7  | ·   |       | •     |       | •     | •     | bit 0 |

|        |     |       |       |       |       |       |       |

#### REGISTER 11-27: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP9R<5:0>: RP9 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP9 (see Table 11-4 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | RP8R<5:0>: RP8 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP8 (see Table 11-4 for peripheral function numbers). |

### REGISTER 11-28: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      |     | RP11R5 | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| _      |     | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7  | •   |        | •      |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP11R<5:0>:** RP11 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP11 (see Table 11-4 for peripheral function numbers).

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **RP10R<5:0>:** RP10 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP10 (see Table 11-4 for peripheral function numbers).

### REGISTER 11-35: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12<sup>(1)</sup>

| U-0           | U-0                                      | R/W-0            | R/W-0          | R/W-0                | R/W-0            | R/W-0           | R/W-0          |

|---------------|------------------------------------------|------------------|----------------|----------------------|------------------|-----------------|----------------|

| —             | —                                        | RP25R5           | RP25R4         | RP25R3               | RP25R2           | RP25R1          | RP25R0         |

| bit 15        |                                          |                  |                | -<br>-               |                  |                 | bit 8          |

|               |                                          |                  |                |                      |                  |                 |                |

| U-0           | U-0                                      | R/W-0            | R/W-0          | R/W-0                | R/W-0            | R/W-0           | R/W-0          |

| —             | —                                        | RP24R5           | RP24R4         | RP24R3               | RP24R2           | RP24R1          | RP24R0         |

| bit 7         |                                          | •                |                |                      | •                |                 | bit 0          |

|               |                                          |                  |                |                      |                  |                 |                |

| Legend:       |                                          |                  |                |                      |                  |                 |                |

| R = Readable  | e bit                                    | W = Writable     | bit            | U = Unimplem         | nented bit, read | 1 as '0'        |                |

| -n = Value at | POR                                      | '1' = Bit is set |                | '0' = Bit is cleared |                  | x = Bit is unkr | nown           |

|               |                                          |                  |                |                      |                  |                 |                |

| bit 15-14     | Unimplemen                               | ted: Read as '   | )'             |                      |                  |                 |                |

| bit 13-8      | RP25R<5:0>:                              | RP25 Output      | Pin Mapping b  | its                  |                  |                 |                |

|               | Peripheral Ou                            | tput Number n    | is assigned to | pin, RP25 (see       | Table 11-4 for   | peripheral func | tion numbers). |

| bit 7-6       | Unimplemented: Read as '0'               |                  |                |                      |                  |                 |                |

| bit 5-0       | RP24R<5:0>: RP24 Output Pin Mapping bits |                  |                |                      |                  |                 |                |

5-0 **RP24R<5:0>:** RP24 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP24 (see Table 11-4 for peripheral function numbers).

Note 1: These pins are not available in 28-pin devices.

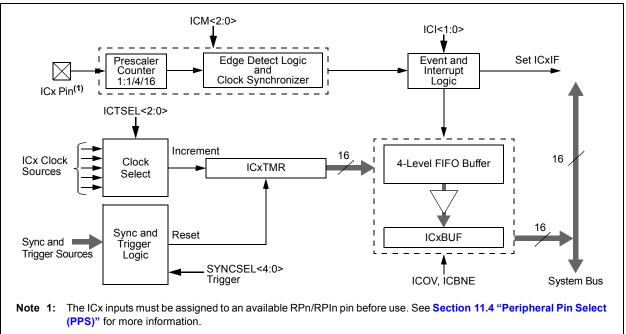

# 14.0 INPUT CAPTURE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Input Capture with Dedicated Timer" (DS39722). The information in this data sheet supersedes the information in the FRM.

Devices in the PIC24FJ128GB204 family contain six independent input capture modules. Each of the modules offers a wide range of configuration and operating options for capturing external pulse events and generating interrupts.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 30 user-selectable sync/trigger sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to 6 clock sources available for each module, driving a separate, internal 16-bit counter

The module is controlled through two registers: ICxCON1 (Register 14-1) and ICxCON2 (Register 14-2). A general block diagram of the module is shown in Figure 14-1.

### 14.1 General Operating Modes

#### 14.1.1 SYNCHRONOUS AND TRIGGER MODES

When the input capture module operates in a Free-Running mode, the internal 16-bit counter, ICxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow. Its period is synchronized to the selected external clock source. When a capture event occurs, the current 16-bit value of the internal counter is written to the FIFO buffer.

In Synchronous mode, the module begins capturing events on the ICx pin as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the internal counter to run.

Standard, free-running operation is selected by setting the SYNCSELx bits (ICxCON2<4:0>) to '00000' and clearing the ICTRIG bit (ICxCON2<7>). Synchronous and Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The ICTRIG bit selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the sync/trigger source.

When the SYNCSELx bits are set to '00000' and ICTRIG is set, the module operates in Software Trigger mode. In this case, capture operations are started by manually setting the TRIGSTAT bit (ICxCON2<6>).

#### FIGURE 14-1: INPUT CAPTURE x BLOCK DIAGRAM

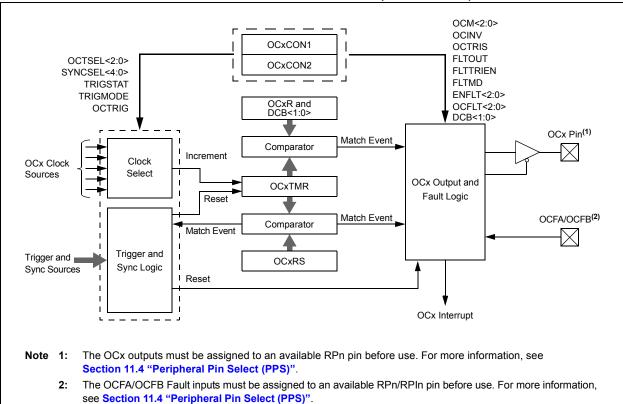

#### FIGURE 15-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

### 15.2 Compare Operations

In Compare mode (Figure 15-1), the output compare module can be configured for single-shot or continuous pulse generation. It can also repeatedly toggle an output pin on each timer event.

To set up the module for compare operations:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins.

- Calculate the required values for the OCxR and (for Double Compare modes) OCxRS Duty Cycle registers:

- a) Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- b) Calculate the time to the rising edge of the output pulse relative to the timer start value (0000h).

- c) Calculate the time to the falling edge of the pulse based on the desired pulse width and the time to the rising edge of the pulse.

- 3. Write the rising edge value to OCxR and the falling edge value to OCxRS.

- 4. Set the Timer Period register, PRy, to a value equal to or greater than the value in OCxRS.

- 5. Set the OCM<2:0> bits for the appropriate compare operation ('0xx').

- For Trigger mode operations, set OCTRIG to enable Trigger mode. Set or clear TRIGMODE to configure trigger operation and TRIGSTAT to select a hardware or software trigger. For Synchronous mode, clear OCTRIG.

- Set the SYNCSEL<4:0> bits to configure the trigger or synchronization source. If free-running timer operation is required, set the SYNCSELx bits to '00000' (no sync/trigger source).

- Select the time base source with the OCTSEL<2:0> bits. If necessary, set the TON bit for the selected timer, which enables the compare time base to count. Synchronous mode operation starts as soon as the time base is enabled; Trigger mode operation starts after a trigger source event occurs.

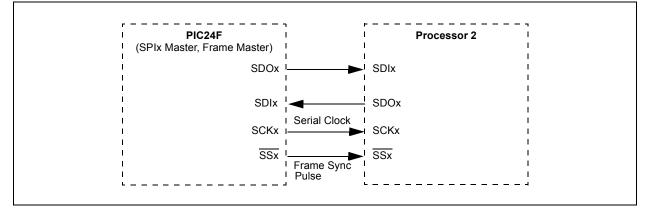

#### FIGURE 16-5: SPIX MASTER, FRAME MASTER CONNECTION DIAGRAM

### 17.2 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator reload value, use Equation 17-1.

EQUATION 17-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1)</sup>

$$I2CxBRG = \left( \left( \frac{1}{FSCL} - PGDx \right) \times \frac{FCY}{2} \right) - 2$$

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### 17.3 Slave Address Masking

The I2CxMSK register (Register 17-4) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond, whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '0010000000', the slave module will detect both addresses, '000000000' and '001000000'.

To enable address masking, the Intelligent Peripheral Management Interface (IPMI) must be disabled by clearing the STRICT bit (I2CxCONL<11>).

Note: As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 17-1 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| TABLE 17-1: | I <sup>2</sup> C <sup>™</sup> RESERVED ADDRESSES <sup>(1)</sup> |

|-------------|-----------------------------------------------------------------|

|-------------|-----------------------------------------------------------------|

| Slave Address | R/W Bit | Description                            |

|---------------|---------|----------------------------------------|

| 0000 000      | 0       | General Call Address <sup>(2)</sup>    |

| 0000 000      | 1       | Start Byte                             |

| 0000 001      | Х       | Cbus Address                           |

| 0000 01x      | х       | Reserved                               |

| 0000 1xx      | Х       | HS Mode Master Code                    |

| 1111 0xx      | х       | 10-Bit Slave Upper Byte <sup>(3)</sup> |

| 1111 1xx      | Х       | Reserved                               |

**Note 1:** The address bits listed here will never cause an address match independent of address mask settings.

2: The address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

NOTES:

| ALRMEN<br>bit 15 | CHIME                                          | AMASK3                          | AMASK2           | AMASK1             | AMASK0                       | ALRMPTR1                                                  | ALRMPTR0       |  |  |  |

|------------------|------------------------------------------------|---------------------------------|------------------|--------------------|------------------------------|-----------------------------------------------------------|----------------|--|--|--|

| bit 15           |                                                |                                 |                  |                    | 7 11/1 10/10                 |                                                           |                |  |  |  |

|                  |                                                |                                 |                  |                    |                              |                                                           | bit 8          |  |  |  |

| R/W-0            | R/W-0                                          | R/W-0                           | R/W-0            | R/W-0              | R/W-0                        | R/W-0                                                     | R/W-0          |  |  |  |

| ARPT7            | ARPT6                                          | ARPT5                           | ARPT4            | ARPT3              | ARPT2                        | ARPT1                                                     | ARPT0          |  |  |  |

| bit 7            |                                                |                                 |                  |                    |                              |                                                           | bit 0          |  |  |  |

| Legend:          |                                                |                                 |                  |                    |                              |                                                           |                |  |  |  |

| R = Readat       | ble bit                                        | W = Writable b                  | bit              | U = Unimplem       | nented bit, read             | as '0'                                                    |                |  |  |  |

| -n = Value a     | at POR                                         | '1' = Bit is set                |                  | '0' = Bit is clea  |                              | x = Bit is unkn                                           | own            |  |  |  |

|                  |                                                |                                 |                  |                    |                              |                                                           |                |  |  |  |

| bit 15           | ALRMEN: Ala                                    | arm Enable bit                  |                  |                    |                              |                                                           |                |  |  |  |

|                  | 1 = A larm is  e<br>0 = A larm is  e           | enabled (cleared a              | automatically af | ter an alarm eve   | nt whenever AR               | PT<7:0> = 00h a                                           | and CHIME = 0) |  |  |  |

| bit 14           | CHIME: Chim                                    |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | -                                              | enabled; ARPT<                  | <7·0> bits are a | illowed to roll ov | ver from 00h to              | FFh                                                       |                |  |  |  |

|                  |                                                | disabled; ARPT                  |                  |                    |                              |                                                           |                |  |  |  |

| bit 13-10        | AMASK<3:0>                                     | >: Alarm Mask C                 | onfiguration bi  | ts                 |                              |                                                           |                |  |  |  |

|                  | 0000 = Every                                   | / half second                   | -                |                    |                              |                                                           |                |  |  |  |

|                  | 0001 = Every                                   |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | 0010 = Every                                   |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | 0011 = Every minute<br>0100 = Every 10 minutes |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | 0101 = Every hour                              |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | 0110 = Once                                    |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | 0111 = Once<br>1000 = Once                     |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  |                                                | a year (except v                | when configure   | d for February     | 29 <sup>th</sup> . once ever | v 4 vears)                                                |                |  |  |  |

|                  |                                                | rved – do not us                |                  | ,                  | ,                            | <b>j</b> · <b>j</b> · · · · · · · · · · · · · · · · · · · |                |  |  |  |

|                  | 11xx = Rese                                    | rved – do not us                | e                |                    |                              |                                                           |                |  |  |  |

| bit 9-8          |                                                | :0>: Alarm Valu                 | -                |                    |                              |                                                           |                |  |  |  |

|                  |                                                | corresponding Al                |                  |                    |                              |                                                           |                |  |  |  |

|                  |                                                | R<1:0> value de                 | crements on ev   | ery read or write  | e of ALRMVALF                | I until it reaches                                        | .00′.          |  |  |  |

|                  | ALRMVAL<15:8>:<br>00 = ALRMMIN                 |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | 01 = ALRMWD                                    |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | 10 = ALRMMNTH                                  |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  |                                                |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | ALRMVAL<7:0>:<br>00 = ALRMSEC                  |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | 01 = ALRMBEC                                   |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | 10 = ALRMD                                     |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | 11 = PWCSA                                     | MP                              |                  |                    |                              |                                                           |                |  |  |  |

| bit 7-0          | ARPT<7:0>:                                     | Alarm Repeat C                  | ounter Value b   | its                |                              |                                                           |                |  |  |  |

|                  | 11111111 =                                     | Alarm will repea                | t 255 more time  | es                 |                              |                                                           |                |  |  |  |

|                  | •                                              |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  |                                                |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  | •                                              |                                 |                  |                    |                              |                                                           |                |  |  |  |

|                  |                                                | Alarm will not re decrements on |                  |                    |                              |                                                           |                |  |  |  |

NOTES:

### 24.1.3 DATA SHIFT DIRECTION

The LENDIAN bit (CRCCON1<3>) is used to control the shift direction. By default, the CRC will shift data through the engine, MSb first. Setting LENDIAN (= 1) causes the CRC to shift data, LSb first. This setting allows better integration with various communication schemes and removes the overhead of reversing the bit order in software. Note that this only changes the direction the data is shifted into the engine. The result of the CRC calculation will still be a normal CRC result, not a reverse CRC result.

#### 24.1.4 INTERRUPT OPERATION

The module generates an interrupt that is configurable by the user for either of two conditions.

If CRCISEL is '0', an interrupt is generated when the VWORD<4:0> bits make a transition from a value of '1' to '0'. If CRCISEL is '1', an interrupt will be generated after the CRC operation finishes and the module sets the CRCGO bit to '0'. Manually setting CRCGO to '0' will not generate an interrupt. Note that when an interrupt occurs, the CRC calculation would not yet be complete. The module will still need (PLEN + 1)/2 clock cycles, after the interrupt is generated, until the CRC calculation is finished.

### 24.1.5 TYPICAL OPERATION

To use the module for a typical CRC calculation:

- 1. Set the CRCEN bit to enable the module.

- Configure the module for desired operation:

a) Program the desired polynomial using the CRCXORL and CRCXORH registers, and the PLEN<4:0> bits.

b) Configure the data width and shift direction using the DWIDTHx and LENDIAN bits.c) Select the desired Interrupt mode using the

CRCISEL bit.

Preload the FIFO by writing to the CRCDATL and CRCDATH registers until the CRCFUL bit is set or no data is left.

- Clear old results by writing 00h to CRCWDATL and CRCWDATH. The CRCWDAT registers can also be left unchanged to resume a previously halted calculation.

- 5. Set the CRCGO bit to start calculation.

- 6. Write remaining data into the FIFO as space becomes available.

- When the calculation completes, CRCGO is automatically cleared. An interrupt will be generated if CRCISEL = 1.

- 8. Read CRCWDATL and CRCWDATH for the result of the calculation.

There are eight registers used to control programmable CRC operation:

- CRCCON1

- CRCCON2

- CRCXORL

- CRCXORH

- CRCDATL

- CRCDATH

- CRCWDATL

- CRCWDATH

The CRCCON1 and CRCCON2 registers (Register 24-1 and Register 24-2) control the operation of the module and configure the various settings.

The CRCXORL/H registers (Register 24-3 and Register 24-4) select the polynomial terms to be used in the CRC equation. The CRCDAT and CRCWDAT registers are each register pairs that serve as buffers for the double-word input data and CRC processed output, respectively.

| R/W-0      | U-0                                                                                                                               | R/W-0                                                                                                                      | R/W-0                | R/W-0                 | R/W-0            | R/W-0              | R/W-0         |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|------------------|--------------------|---------------|--|--|--|

| ADON       | _                                                                                                                                 | ADSIDL                                                                                                                     | DMABM <sup>(1)</sup> | DMAEN                 | MODE12           | FORM1              | FORM0         |  |  |  |

| bit 15     |                                                                                                                                   |                                                                                                                            |                      |                       |                  |                    | bit 8         |  |  |  |

|            | <b>D</b> # 44 A                                                                                                                   | <b>-</b>                                                                                                                   | 5444                 |                       | <b>-</b>         |                    | <u> </u>      |  |  |  |

| R/W-0      | R/W-0                                                                                                                             | R/W-0                                                                                                                      | R/W-0                | U-0                   | R/W-0            | R/W-0, HSC         | R/C-0, HSC    |  |  |  |

| SSRC3      | SSRC2                                                                                                                             | SSRC1                                                                                                                      | SSRC0                |                       | ASAM             | SAMP               | DONE          |  |  |  |

| bit 7      |                                                                                                                                   |                                                                                                                            |                      |                       |                  |                    | bit C         |  |  |  |

| Legend:    |                                                                                                                                   | C = Clearable                                                                                                              | bit                  | U = Unimplen          | nented bit, read | l as '0'           |               |  |  |  |

| R = Reada  | ble bit                                                                                                                           | W = Writable                                                                                                               |                      | •                     | /are Settable/C  |                    |               |  |  |  |

| -n = Value |                                                                                                                                   | '1' = Bit is set                                                                                                           |                      | '0' = Bit is clea     |                  | x = Bit is unkn    | own           |  |  |  |

| The Value  |                                                                                                                                   | - Bitle cot                                                                                                                |                      |                       |                  |                    | ••••          |  |  |  |

| bit 15     | ADON: ADC                                                                                                                         | 1 Operating Mo                                                                                                             | de bit               |                       |                  |                    |               |  |  |  |

|            | 1 = A/D Conv                                                                                                                      | verter module is                                                                                                           | operating            |                       |                  |                    |               |  |  |  |

|            | 0 = A/D Conv                                                                                                                      | verter is off                                                                                                              |                      |                       |                  |                    |               |  |  |  |

| bit 14     | Unimplemen                                                                                                                        | ted: Read as '                                                                                                             | )'                   |                       |                  |                    |               |  |  |  |

| bit 13     | ADSIDL: AD                                                                                                                        | C1 Stop in Idle                                                                                                            | Mode bit             |                       |                  |                    |               |  |  |  |

|            |                                                                                                                                   | ues module op<br>s module opera                                                                                            |                      |                       | e mode           |                    |               |  |  |  |

| bit 12     | DMABM: Ext                                                                                                                        | ended DMA Bu                                                                                                               | ffer Mode Sele       | ct bit <sup>(1)</sup> |                  |                    |               |  |  |  |

|            |                                                                                                                                   | Buffer mode: E<br>Buffer addres                                                                                            |                      |                       |                  |                    |               |  |  |  |

| bit 11     | DMAEN: Exte                                                                                                                       | 0 = PIA mode: Buffer addresses are defined by the DMA Controller and AD1CON4<2:0><br>DMAEN: Extended DMA/Buffer Enable bit |                      |                       |                  |                    |               |  |  |  |

|            |                                                                                                                                   | DMA and buffe                                                                                                              |                      | enabled               |                  |                    |               |  |  |  |

| bit 10     | MODE12: AD                                                                                                                        | OC1 12-Bit Ope                                                                                                             | ration Mode bit      |                       |                  |                    |               |  |  |  |

|            | 1 = 12-bit A/E<br>0 = 10-bit A/E                                                                                                  |                                                                                                                            |                      |                       |                  |                    |               |  |  |  |

| bit 9-8    |                                                                                                                                   | Data Output Fe                                                                                                             | ormat bits (see      | the following fo      | ormats)          |                    |               |  |  |  |

|            | 11 = Fraction                                                                                                                     | al result, signed                                                                                                          | d, left justified    |                       |                  |                    |               |  |  |  |

|            | 10 = Absolute fractional result, unsigned, left justified                                                                         |                                                                                                                            |                      |                       |                  |                    |               |  |  |  |

|            | <ul> <li>01 = Decimal result, signed, right justified</li> <li>00 = Absolute decimal result, unsigned, right justified</li> </ul> |                                                                                                                            |                      |                       |                  |                    |               |  |  |  |

| bit 7-4    | SSRC<3:0>:                                                                                                                        | Sample Clock                                                                                                               | Source Select I      | oits                  |                  |                    |               |  |  |  |

|            |                                                                                                                                   | plemented<br>1<br>U<br>5                                                                                                   |                      | tarts conversior      | n (auto-convert) | ; do not use in Aı | uto-Scan mode |  |  |  |

|            | 0001 = INTO<br>0000 = The S                                                                                                       | SAMP bit must                                                                                                              | be cleared by s      | oftware to star       | t conversion     |                    |               |  |  |  |

| bit 3      | Unimplemen                                                                                                                        | ted: Read as '                                                                                                             | )'                   |                       |                  |                    |               |  |  |  |

| bit 2      | ASAM: ADC                                                                                                                         | 1 Sample Auto-                                                                                                             | Start bit            |                       |                  |                    |               |  |  |  |

|            |                                                                                                                                   | begins immedi<br>begins when S                                                                                             |                      |                       | MP bit is auto-  | set                |               |  |  |  |

| Note di    | This hit is only a                                                                                                                | wailable when F                                                                                                            |                      | Duffer features       | ara availabla (  |                    |               |  |  |  |

#### REGISTER 25-1: AD1CON1: ADC1 CONTROL REGISTER 1

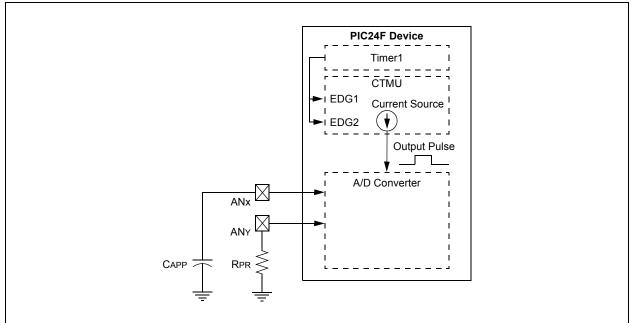

### FIGURE 28-1: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR CAPACITANCE MEASUREMENT

### 31.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 31.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 31.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 31.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

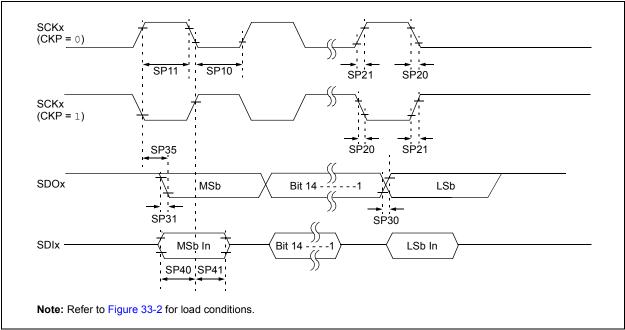

#### FIGURE 33-9: SPIX MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 33-32: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                                |  |

|--------------------|-----------------------|--------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|--------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>              | Min                                                   | Typ <sup>(2)</sup> | Max | Units | Conditions                     |  |

| SP10               | TscL                  | SCKx Output Low Time                       | Tcy/2                                                 | _                  | _   | ns    | (Note 3)                       |  |

| SP11               | TscH                  | SCKx Output High Time                      | Tcy/2                                                 | _                  | _   | ns    | (Note 3)                       |  |

| SP20               | TscF                  | SCKx Output Fall Time                      | —                                                     | —                  | _   | ns    | See Parameter DO32 (Note 4)    |  |

| SP21               | TscR                  | SCKx Output Rise Time                      | —                                                     | —                  | _   | ns    | See Parameter DO31<br>(Note 4) |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                 | —                                                     | —                  |     | ns    | See Parameter DO32 (Note 4)    |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                 | —                                                     | —                  |     | ns    | See Parameter DO31 (Note 4)    |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid After<br>SCKx Edge  | —                                                     | 6                  | 20  | ns    |                                |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge | 23                                                    | —                  | _   | ns    |                                |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge  | 30                                                    | —                  |     | ns    |                                |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

**4:** Assumes 50 pF load on all SPIx pins.

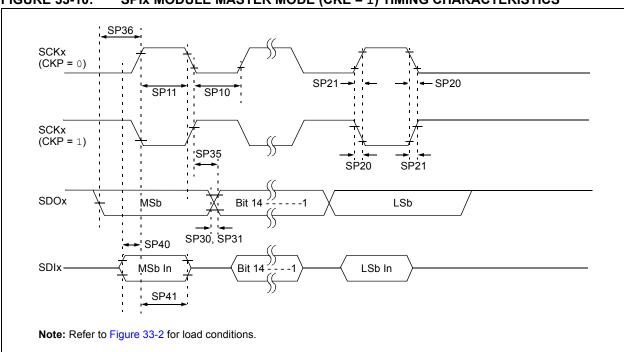

#### FIGURE 33-10: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

#### TABLE 33-33: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |     |       |                    |  |

|--------------------|-----------------------|-----------------------------------------------|------------------------------------------------------|--------------------|-----|-------|--------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                 | Min                                                  | Typ <sup>(2)</sup> | Max | Units | Conditions         |  |

| SP10               | TscL                  | SCKx Output Low Time <sup>(3)</sup>           | Tcy/2                                                | —                  |     | ns    |                    |  |

| SP11               | TscH                  | SCKx Output High Time <sup>(3)</sup>          | TCY/2                                                | _                  | _   | ns    |                    |  |

| SP20               | TscF                  | SCKx Output Fall Time <sup>(4)</sup>          | _                                                    | _                  | _   | ns    | See Parameter DO32 |  |

| SP21               | TscR                  | SCKx Output Rise Time <sup>(4)</sup>          | _                                                    | —                  | _   | ns    | See Parameter DO31 |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time <sup>(4)</sup>     | _                                                    | _                  | _   | ns    | See Parameter DO32 |  |

| SP31               | TdoR                  | SDOx Data Output Rise<br>Time <sup>(4)</sup>  | _                                                    | —                  |     | ns    | See Parameter DO31 |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid After<br>SCKx Edge     | _                                                    | 6                  | 20  | ns    |                    |  |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                                   | —                  | _   | ns    |                    |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 23                                                   | —                  | _   | ns    |                    |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30                                                   | —                  | _   | ns    |                    |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

**4:** Assumes 50 pF load on all SPIx pins.

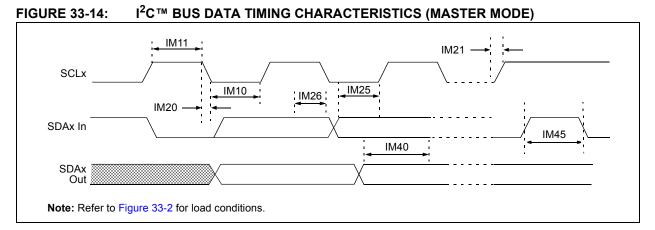

#### TABLE 33-37: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHARACTERISTICS |                   |                            |                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                                         |  |

|--------------------|-------------------|----------------------------|---------------------------|-------------------------------------------------------|------|-------|-----------------------------------------|--|

| Param<br>No.       | Symbol<br>TLO:SCL | Characteristic             |                           | Min <sup>(1)</sup>                                    | Max  | Units | Conditions                              |  |

| IM10               |                   | Clock Low Time             | 100 kHz mode              | Tcy (BRG + 1)                                         |      | μs    |                                         |  |

|                    |                   |                            | 400 kHz mode              | Tcy (BRG + 1)                                         |      | μs    |                                         |  |

|                    |                   |                            | 1 MHz mode <sup>(2)</sup> | Tcy (BRG + 1)                                         |      | μs    |                                         |  |

| IM11               | THI:SCL           | Clock High Time            | 100 kHz mode              | Tcy (BRG + 1)                                         |      | μs    |                                         |  |

|                    |                   |                            | 400 kHz mode              | Tcy (BRG + 1)                                         |      | μs    |                                         |  |

|                    |                   |                            | 1 MHz mode <sup>(2)</sup> | Tcy (BRG + 1)                                         |      | μs    |                                         |  |

| IM20               | TF:SCL            | SDAx and SCLx<br>Fall Time | 100 kHz mode              | —                                                     | 300  | ns    | CB is specified to be from 10 to 400 pF |  |

|                    |                   |                            | 400 kHz mode              | 20 + 0.1 Св                                           | 300  | ns    |                                         |  |

|                    |                   |                            | 1 MHz mode <sup>(2)</sup> | —                                                     | 100  | ns    | -                                       |  |

| IM21               | TR:SCL            | SDAx and SCLx<br>Rise Time | 100 kHz mode              | —                                                     | 1000 | ns    | CB is specified to be from 10 to 400 pF |  |

|                    |                   |                            | 400 kHz mode              | 20 + 0.1 Св                                           | 300  | ns    |                                         |  |

|                    |                   |                            | 1 MHz mode <sup>(2)</sup> | —                                                     | 300  | ns    |                                         |  |

| IM25               | TSU:DAT           | Data Input<br>Setup Time   | 100 kHz mode              | 250                                                   | —    | ns    |                                         |  |

|                    |                   |                            | 400 kHz mode              | 100                                                   | _    | ns    |                                         |  |

|                    |                   |                            | 1 MHz mode <sup>(2)</sup> | 40                                                    | _    | ns    |                                         |  |

| IM26               | Thd:dat           | Data Input<br>Hold Time    | 100 kHz mode              | 0                                                     | _    | ns    |                                         |  |

|                    |                   |                            | 400 kHz mode              | 0                                                     | 0.9  | μs    |                                         |  |

|                    |                   |                            | 1 MHz mode <sup>(2)</sup> | 0.2                                                   | _    | ns    |                                         |  |

| IM40               | TAA:SCL           | Output Valid<br>From Clock | 100 kHz mode              | —                                                     | 3500 | ns    |                                         |  |

|                    |                   |                            | 400 kHz mode              | —                                                     | 1000 | ns    |                                         |  |

|                    |                   |                            | 1 MHz mode <sup>(2)</sup> |                                                       | 400  | ns    |                                         |  |

| IM45               | Tbf:sda           | Bus Free Time              | 100 kHz mode              | 4.7                                                   | —    | μs    | Time the bus must be                    |  |

|                    |                   |                            | 400 kHz mode              | 1.3                                                   | —    | μs    | free before a new                       |  |

|                    |                   |                            | 1 MHz mode <sup>(2)</sup> | 0.5                                                   | —    | μs    | transmission can start                  |  |

| IM50               | Св                | Bus Capacitive Lo          | oading                    |                                                       | 400  | pF    |                                         |  |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator. Refer to **Section 17.2 "Setting Baud Rate When Operating as a Bus Master**" for details.

2: Maximum Pin Capacitance = 10 pF for all I<sup>2</sup>C pins (for 1 MHz mode only).