#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

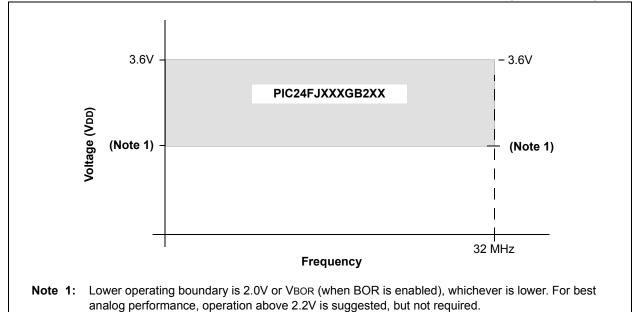

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                      |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT         |

| Number of I/O              | 20                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb202t-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ64GB202 PIC24FJ128GB202

- PIC24FJ64GB204 PIC24FJ128GB204

The PIC24FJ128GB204 family expands the capabilities of the PIC24F family by adding a complete selection of Cryptographic Engines, ISO 7816 support and I<sup>2</sup>S support to its existing features. This combination, along with its ultra low-power features, Direct Memory Access (DMA) for peripherals and USB On-The-Go, make this family the new standard for mixed-signal PIC<sup>®</sup> microcontrollers in one economical and power-saving package.

## 1.1 Core Features

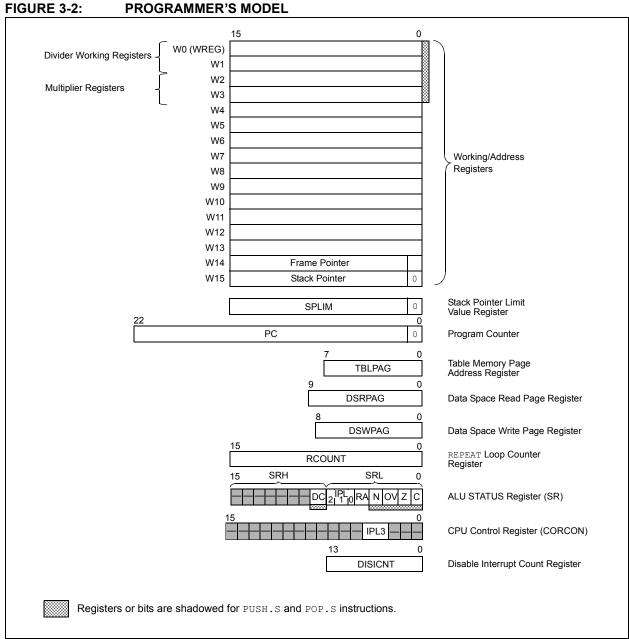

### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> Digital Signal Controllers (DSCs). The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 32 Kbytes (data)

- A 16-element Working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- Operational performance up to 16 MIPS

### 1.1.2 XLP POWER-SAVING TECHNOLOGY

The PIC24FJ128GB204 family of devices introduces a greatly expanded range of power-saving operating modes for the ultimate in power conservation. The new modes include:

- Retention Sleep with essential circuits being powered from a separate low-voltage regulator

- Deep Sleep without RTCC for the lowest possible power consumption under software control

- VBAT mode (with or without RTCC) to continue limited operation from a backup battery when VDD is removed

Many of these new low-power modes also support the continuous operation of the low-power, on-chip Real-Time Clock/Calendar (RTCC), making it possible for an application to keep time while the device is otherwise asleep.

Aside from these new features, PIC24FJ128GB204 family devices also include all of the legacy power-saving features of previous PIC24F microcontrollers, such as:

- On-the-Fly Clock Switching, allowing the selection of a lower power clock during run time

- Doze Mode Operation, for maintaining peripheral clock speed while slowing the CPU clock

- Instruction-Based Power-Saving Modes, for quick invocation of Idle and the many Sleep modes

# 1.1.3 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC24FJ128GB204 family offer five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes

- Two External Clock (EC) modes

- A Phase-Locked Loop (PLL) frequency multiplier, which allows clock speeds of up to 32 MHz

- A Fast Internal Oscillator (FRC) Nominal 8 MHz output with multiple frequency divider options and automatic frequency self-calibration during run time

- A separate Low-Power Internal RC Oscillator (LPRC) – 31 kHz nominal for low-power, timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

## 1.1.4 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve. This extends the ability of applications to grow from the relatively simple, to the powerful and complex, yet still selecting a Microchip device.

|              | Pin Num                       | Pin Number/Grid Locator |                    |     |                 |                                      |  |  |  |

|--------------|-------------------------------|-------------------------|--------------------|-----|-----------------|--------------------------------------|--|--|--|

| Pin Function | 28-Pin<br>SPDIP/SOIC/<br>SSOP | 28-Pin<br>QFN-S         | 44-Pin<br>TQFP/QFN | I/O | Input<br>Buffer | Description                          |  |  |  |

| AN0          | 2                             | 27                      | 19                 | I   | ANA             | 12-Bit SAR A/D Converter Inputs.     |  |  |  |

| AN1          | 3                             | 28                      | 20                 | Ι   | ANA             |                                      |  |  |  |

| AN2          | 4                             | 1                       | 21                 | Ι   | ANA             |                                      |  |  |  |

| AN3          | 5                             | 2                       | 22                 | Ι   | ANA             |                                      |  |  |  |

| AN4          | 6                             | 3                       | 23                 | Ι   | ANA             |                                      |  |  |  |

| AN5          | 7                             | 4                       | 24                 | Ι   | ANA             |                                      |  |  |  |

| AN6          | 25                            | 22                      | 14                 | I   | ANA             | ]                                    |  |  |  |

| AN7          | 24                            | 21                      | 11                 | I   | ANA             |                                      |  |  |  |

| AN9          | 26                            | 23                      | 15                 | Ι   | ANA             |                                      |  |  |  |

| AN10         | _                             |                         | 25                 | I   | ANA             |                                      |  |  |  |

| AN11         | _                             |                         | 26                 | Ι   | ANA             |                                      |  |  |  |

| AN12         | _                             |                         | 27                 | Ι   | ANA             |                                      |  |  |  |

| ASCL1        | 3                             | 28                      | 20                 | _   |                 |                                      |  |  |  |

| ASDA1        | 2                             | 27                      | 19                 | _   |                 |                                      |  |  |  |

| AVdd         | _                             |                         | 17                 | Р   | ANA             | Positive Supply for Analog modules.  |  |  |  |

| AVss         | _                             | 24                      | 16                 | Р   | ANA             | Ground Reference for Analog modules. |  |  |  |

| C1INA        | 7                             | 4                       | 24                 | I   | ANA             | Comparator 1 Input A.                |  |  |  |

| C1INB        | 6                             | 3                       | 23                 | I   | ANA             | Comparator 1 Input B.                |  |  |  |

| C1INC        | 24                            | 15                      | 1                  | Ι   | ANA             | Comparator 1 Input C.                |  |  |  |

| C1IND        | 9                             | 6                       | 30                 | I   | ANA             | Comparator 1 Input D.                |  |  |  |

| C2INA        | 5                             | 2                       | 22                 | I   | ANA             | Comparator 2 Input A.                |  |  |  |

| C2INB        | 4                             | 1                       | 21                 | I   | ANA             | Comparator 2 Input B.                |  |  |  |

| C2INC        | 18                            | 15                      | 1                  | Ι   | ANA             | Comparator 2 Input C.                |  |  |  |

| C2IND        | 10                            | 7                       | 31                 | I   | ANA             | Comparator 2 Input D.                |  |  |  |

| C3INA        | 26                            | 23                      | 15                 | I   | ANA             | Comparator 3 Input A.                |  |  |  |

| C3INB        | 25                            | 22                      | 14                 | I   | ANA             | Comparator 3 Input B.                |  |  |  |

| C3INC        | 2                             | 15                      | 1                  | I   | ANA             | Comparator 3 Input C.                |  |  |  |

| C3IND        | 3                             | 28                      | 20                 | I   | ANA             | Comparator 3 Input D.                |  |  |  |

| CLKI         | 9                             | 6                       | 30                 | I   | ANA             | Main Clock Input Connection.         |  |  |  |

| CLKO         | 10                            | 7                       | 31                 | 0   | —               | System Clock Output.                 |  |  |  |

| TABLE 1-3: | PIC24FJ128GB204 FAMILY PINOUT DESCRIPTION |

|------------|-------------------------------------------|

|            |                                           |

Legend: ST = Schmitt Trigge ANA = Analog input = Schmitt Trigger input

$$I^2C$$

= ST with  $I^2C^{TM}$  or SMBus levels

TTL = TTL compatible input  $\Omega = \Omega$ utput O = Output P = Power

## 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- · 8-bit unsigned x 8-bit unsigned

## 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided in Table 3-2.

### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE BIT AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |  |  |  |  |  |  |

|-------------|-------------------------------------------------------------|--|--|--|--|--|--|

| ASR         | Arithmetic Shift Right Source register by one or more bits. |  |  |  |  |  |  |

| SL          | Shift Left Source register by one or more bits.             |  |  |  |  |  |  |

| LSR         | Logical Shift Right Source register by one or more bits.    |  |  |  |  |  |  |

| TABI F 4-27 <sup>.</sup> | <b>CRC REGISTER MAP</b> |

|--------------------------|-------------------------|

| ADLL = -21.              |                         |

| © 20        | TABLE 4-2    | 27:  | CRC RE | GISTE  | R MAP  |         |         |         |         |             |   |

|-------------|--------------|------|--------|--------|--------|---------|---------|---------|---------|-------------|---|

| 2013-2015   | File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8       |   |

| 5 Microchin | CRCCON1      | 0158 | CRCEN  |        | CSIDL  | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0      | - |

|             | CRCCON2      | 015A | _      | _      | _      | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0     |   |

|             | CRCXORL      | 015C |        |        |        |         |         |         |         | X<15:1>     |   |

|             | CRCXORH      | 015E |        |        |        |         |         |         |         | X<31:       | 1 |

|             | CRCDATL      | 0160 |        |        |        |         |         |         | CRC     | Data Input  | F |

|             | CRCDATH      | 0162 |        |        |        |         |         |         | CRC     | Data Input  | F |

|             | CRCWDATL     | 0164 |        |        |        |         |         |         | CF      | RC Result R | e |

|             | CRCWDATH     | 0166 |        |        |        |         |         |         | CF      | RC Result R | e |

|             |              |      |        |        |        |         |         |         |         |             |   |

Legend: — = unimplemented, read as '0'; x = unknown value on Reset. Reset values are shown in hexadecimal.

### TABLE 4-28: PERIPHERAL PIN SELECT REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12     | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7 | Bit 6 | Bit 5       | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     | All<br>Resets |

|--------------|------|--------|--------|-----------|------------|-----------|-----------|-----------|-----------|-------|-------|-------------|-----------|-----------|-----------|-----------|-----------|---------------|

| RPINR0       | 038C | _      | _      | INT1R5    | INT1R4     | INT1R3    | INT1R2    | INT1R1    | INT1R0    | _     | _     | OCTRIG1R5   | OCTRIG1R4 | OCTRIG1R3 | OCTRIG1R2 | OCTRIG1R1 | OCTRIG1R0 | 3F3F          |

| RPINR1       | 038E | -      | -      | INT3R5    | INT3R4     | INT3R3    | INT3R2    | INT3R1    | INT3R0    | _     | _     | INT2R5      | INT2R4    | INT2R3    | INT2R2    | INT2R1    | INT2R0    | 3F3F          |

| RPINR2       | 0390 | -      | -      | OCTRIG2R5 | OCTRIG2R4  | OCTRIG2R3 | OCTRIG2R2 | OCTRIG2R1 | OCTRIG2R0 | _     | _     | INT4R5      | INT4R4    | INT4R3    | INT4R2    | INT4R1    | INT4R0    | 3F3F          |

| RPINR7       | 039A | _      | _      | IC2R5     | IC2R4      | IC2R3     | IC2R2     | IC2R1     | IC2R0     | _     | _     | IC1R5       | IC1R4     | IC1R3     | IC1R2     | IC1R1     | IC1R0     | 3F3F          |

| RPINR8       | 039C | —      | _      | IC4R5     | IC4R4      | IC4R3     | IC4R2     | IC4R1     | IC4R0     | _     | _     | IC3R5       | IC3R4     | IC3R3     | IC3R2     | IC3R1     | IC3R0     | 3F3F          |

| RPINR9       | 039E | _      | _      | IC6R5     | IC6R4      | IC6R3     | IC6R2     | IC6R1     | IC6R0     | _     | _     | IC5R5       | IC5R4     | IC5R3     | IC5R2     | IC5R1     | IC5R0     | 3F3F          |

| RPINR11      | 03A2 | —      | _      | OCFBR5    | OCFBR4     | OCFBR3    | OCFBR2    | OCFBR1    | OCFBR0    | —     | —     | OCFAR5      | OCFAR4    | OCFAR3    | OCFAR2    | OCFAR1    | OCFAR0    | 3F3F          |

| RPINR17      | 03AE | —      | _      |           | U3RXR<5:0> |           |           |           | _         | _     | _     | _           | _         | -         | _         | _         | 3F00      |               |

| RPINR18      | 03B0 | _      | _      | U1CTSR5   | U1CTSR4    | U1CTSR3   | U1CTSR2   | U1CTSR1   | U1CTSR0   | _     | _     | U1RXR5      | U1RXR4    | U1RXR3    | U1RXR2    | U1RXR1    | U1RXR0    | 3F3F          |

| RPINR19      | 03B2 | —      | _      | U2CTSR5   | U2CTSR4    | U2CTSR3   | U2CTSR2   | U2CTSR1   | U2CTSR0   | —     | —     | U2RXR5      | U2RXR4    | U2RXR3    | U2RXR2    | U2RXR1    | U2RXR0    | 3F3F          |

| RPINR20      | 03B4 | —      | —      | SCK1R5    | SCK1R4     | SCK1R3    | SCK1R2    | SCK1R1    | SCK1R0    | —     |       | SDI1R5      | SDI1R4    | SDI1R3    | SDI1R2    | SDI1R1    | SDI1R0    | 3F3F          |

| RPINR21      | 03B6 | _      | _      | U3CTSR5   | U3CTSR4    | U3CTSR3   | U3CTSR2   | U3CTSR1   | U3CTSR0   | _     | _     | SS1R5       | SS1R4     | SS1R3     | SS1R2     | SS1R1     | SS1R0     | 3F3F          |

| RPINR22      | 03B8 | —      | _      | SCK2R5    | SCK2R4     | SCK2R3    | SCK2R2    | SCK2R1    | SCK2R0    | —     | —     | SDI2R5      | SDI2R4    | SDI2R3    | SDI2R2    | SDI2R1    | SDI2R0    | 3F3F          |

| RPINR23      | 03BA | —      | —      | TMRCKR5   | TMRCKR4    | TMRCKR3   | TMRCKR2   | TMRCKR1   | TMRCKR0   | —     |       | SS2R5       | SS2R4     | SS2R3     | SS2R2     | SS2R1     | SS2R0     | 3F3F          |

| RPINR27      | 03C2 | _      | _      | U4CTSR5   | U4CTSR4    | U4CTSR3   | U4CTSR2   | U4CTSR1   | U4CTSR0   | _     | _     | U4RXR5      | U4RXR4    | U4RXR3    | U4RXR2    | U4RXR1    | U4RXR0    | 3F3F          |

| RPINR28      | 03C4 | _      | _      | SCK3R5    | SCK3R4     | SCK3R3    | SCK3R2    | SCK3R1    | SCK3R0    | _     | -     | SDI3R5      | SDI3R4    | SDI3R3    | SDI3R2    | SDI3R1    | SDI3R0    | 3F3F          |

| RPINR29      | 03C6 | _      | _      | _         | _          | _         | _         | _         | _         | _     |       | - SS3R<5:0> |           |           |           | 003F      |           |               |

| RPINR30      | 03C8 | _      | _      | _         | _          | _         | _         | _         | _         | _     | -     | MDMIR<5:0>  |           |           | 003F      |           |           |               |

| RPINR31      | 03CA | _      |        | MDC2R5    | MDC2R4     | MDC2R3    | MDC2R2    | MDC2R1    | MDC2R0    | _     | -     | MDC1R5      | MDC1R4    | MDC1R3    | MDC1R2    | MDC1R1    | MDC1R0    | 3F3F          |

X<31:16>

CRC Data Input Register Low

CRC Data Input Register High

CRC Result Register Low

CRC Result Register High

Bit 7

CRCFUL

\_

Bit 6

CRCMPT

Bit 5

CRCISEL

\_

Bit 4

CRCGO

PLEN4

Bit 3

LENDIAN

PLEN3

Bit 2

\_

PLEN2

Bit 1

\_

PLEN1

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All

Resets

0040

0000

0000

0000

XXXX

XXXX

XXXX

XXXX

Bit 0

\_

PLEN0

\_

NOTES:

### 11.4.3.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains two 6-bit fields, with each field being associated with one RPn pin (see Register 11-23 through Register 11-35). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-4).

Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '000000'. This permits any given pin to remain disconnected from the output of any of the pin-selectable peripherals.

| <b>TABLE 11-4</b> : | SELECTABLE OUTPUT SOURCES | (MAPS FUNCTION TO OUTPUT) |

|---------------------|---------------------------|---------------------------|

|                     |                           |                           |

| Output Function Number <sup>(1)</sup> | Function             | Output Name              |

|---------------------------------------|----------------------|--------------------------|

| 0                                     | NULL <sup>(2)</sup>  | Null                     |

| 1                                     | C1OUT                | Comparator 1 Output      |

| 2                                     | C2OUT                | Comparator 2 Output      |

| 3                                     | U1TX                 | UART1 Transmit           |

| 4                                     | U1RTS <sup>(3)</sup> | UART1 Request-to-Send    |

| 5                                     | U2TX                 | UART2 Transmit           |

| 6                                     | U2RTS <sup>(3)</sup> | UART2 Request-to-Send    |

| 7                                     | SDO1                 | SPI1 Data Output         |

| 8                                     | SCK10UT              | SPI1 Clock Output        |

| 9                                     | SS1OUT               | SPI1 Slave Select Output |

| 10                                    | SDO2                 | SPI2 Data Output         |

| 11                                    | SCK2OUT              | SPI2 Clock Output        |

| 12                                    | SS2OUT               | SPI2 Slave Select Output |

| 13                                    | OC1                  | Output Compare 1         |

| 14                                    | OC2                  | Output Compare 2         |

| 15                                    | OC3                  | Output Compare 3         |

| 16                                    | OC4                  | Output Compare 4         |

| 17                                    | OC5                  | Output Compare 5         |

| 18                                    | OC6                  | Output Compare 6         |

| 19                                    | U3TX                 | UART3 Transmit           |

| 20                                    | <b>U3RTS</b>         | UART3 Request-to-Send    |

| 21                                    | U4TX                 | UART4 Transmit           |

| 22                                    | U4RTS <sup>(3)</sup> | UART4 Request-to-Send    |

| 23                                    | SDO3                 | SPI3 Data Output         |

| 24                                    | SCK3OUT              | SPI3 Clock Output        |

| 25                                    | SS3OUT               | SPI3 Slave Select Output |

| 26                                    | C3OUT                | Comparator 3 Output      |

| 27                                    | MDOUT                | DSM Modulator Output     |

**Note 1:** Setting the RPORx register with the listed value assigns that output function to the associated RPn pin.

2: The NULL function is assigned to all RPn outputs at device Reset and disables the RPn output function.

**3:** IrDA<sup>®</sup> BCLK functionality uses this output.

For 32-bit cascaded operation, these steps are also necessary:

- Set the OC32 bits for both registers (OCyCON2<8>) and (OCxCON2<8>). Enable the even numbered module first to ensure the modules will start functioning in unison.

- Clear the OCTRIG bit of the even module (OCyCON2<7>), so the module will run in Synchronous mode.

- 3. Configure the desired output and Fault settings for OCy.

- 4. Force the output pin for OCx to the output state by clearing the OCTRIS bit.

- If Trigger mode operation is required, configure the trigger options in OCx by using the OCTRIG (OCxCON2<7>), TRIGMODE (OCxCON1<3>) and SYNCSELx (OCxCON2<4:0>) bits.

- Configure the desired Compare or PWM mode of operation (OCM<2:0>) for OCy first, then for OCx.

Depending on the output mode selected, the module holds the OCx pin in its default state and forces a transition to the opposite state when OCxR matches the timer. In Double Compare modes, OCx is forced back to its default state when a match with OCxRS occurs. The OCxIF interrupt flag is set after an OCxR match in Single Compare modes and after each OCxRS match in Double Compare modes.

Single-shot pulse events only occur once, but may be repeated by simply rewriting the value of the OCxCON1 register. Continuous pulse events continue indefinitely until terminated.

### 15.3 Pulse-Width Modulation (PWM) Mode

In PWM mode, the output compare module can be configured for edge-aligned or center-aligned pulse waveform generation. All PWM operations are double-buffered (buffer registers are internal to the module and are not mapped into SFR space).

To configure the output compare module for PWM operation:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins.

- 2. Calculate the desired duty cycles and load them into the OCxR register.

- 3. Calculate the desired period and load it into the OCxRS register.

- Select the current OCx as the synchronization source by writing '0x1F' to the SYNCSEL<4:0> bits (OCxCON2<4:0>) and '0' to the OCTRIG bit (OCxCON2<7>).

- 5. Select a clock source by writing to the OCTSEL<2:0> bits (OCxCON1<12:10>).

- 6. Enable interrupts, if required, for the timer and output compare modules. The output compare interrupt is required for PWM Fault pin utilization.

- 7. Select the desired PWM mode in the OCM<2:0> bits (OCxCON1<2:0>).

- Appropriate Fault inputs may be enabled by using the ENFLT<2:0> bits as described in Register 15-1.

- 9. If a timer is selected as a clock source, set the selected timer prescale value. The selected timer's prescaler output is used as the clock input for the OCx timer and not the selected timer output.

Note: This peripheral contains input and output functions that may need to be configured by the Peripheral Pin Select. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

# 21.0 ENHANCED PARALLEL MASTER PORT (EPMP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Enhanced Parallel Master Port (EPMP)" (DS39730). The information in this data sheet supersedes the information in the FRM.

The Enhanced Parallel Master Port (EPMP) module provides a parallel, 4-bit (Master mode only) and 8-bit (Master and Slave modes) data bus interface to communicate with off-chip modules, such as memories, FIFOs, LCD controllers and other microcontrollers. This module can serve as either the master or the slave on the communication bus.

For EPMP Master modes, all external addresses are mapped into the internal Extended Data Space (EDS). This is done by allocating a region of the EDS for each chip select and then assigning each chip select to a particular external resource, such as a memory or external controller. This region should not be assigned to another device resource, such as RAM or SFRs. To perform a write or read on an external resource, the CPU simply performs a write or read within the address range assigned for the EPMP. Key features of the EPMP module are:

- Extended Data Space (EDS) Interface allows Direct Access from the CPU

- Up to 10 Programmable Address Lines

- Up to 2 Chip Select Lines

- Up to 1 Acknowledgment Line (one per chip select)

- · 4-Bit and 8-Bit Wide Data Bus

- Programmable Strobe Options (per chip select)

- Individual Read and Write Strobes or;

- Read/Write Strobe with Enable Strobe

- Programmable Address/Data Multiplexing

- Programmable Address Wait States

- Programmable Data Wait States (per chip select)

- Programmable Polarity on Control Signals (per chip select)

- Legacy Parallel Slave Port (PSP) Support

- Enhanced Parallel Slave Port Support

- Address Support

- 4-Byte Deep Auto-Incrementing Buffer

### 21.1 Memory Addressable in Different Modes

The memory space addressable by the device depends on the address/data multiplexing selection; it varies from 1K to 2 MB. Refer to Table 21-1 for different Memory-Addressable modes.

| R/W-0                      | R/W-0                                                                                                                                                          | R/W-0                                                                                                                                 | R/W-0                                               | U-0                         | R/W-0            | R/W-0           | R/W-0  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------|------------------|-----------------|--------|--|--|

| PTWREN                     | PTRDEN                                                                                                                                                         | PTBE1EN                                                                                                                               | PTBE0EN                                             | _                           | AWAITM1          | AWAITM0         | AWAITE |  |  |

| bit 15                     |                                                                                                                                                                |                                                                                                                                       |                                                     |                             |                  |                 | bit 8  |  |  |

| U-0                        | U-0                                                                                                                                                            | U-0                                                                                                                                   | U-0                                                 | U-0                         | U-0              | U-0             | U-0    |  |  |

| _                          |                                                                                                                                                                | _                                                                                                                                     | _                                                   | _                           |                  |                 | _      |  |  |

| pit 7                      |                                                                                                                                                                |                                                                                                                                       |                                                     |                             |                  |                 | bit (  |  |  |

| Legend:                    |                                                                                                                                                                |                                                                                                                                       |                                                     |                             |                  |                 |        |  |  |

| R = Readable               | e bit                                                                                                                                                          | W = Writable                                                                                                                          | bit                                                 | U = Unimpler                | nented bit, read | l as '0'        |        |  |  |

| -n = Value at              | POR                                                                                                                                                            | '1' = Bit is set                                                                                                                      |                                                     | '0' = Bit is cle            | ared             | x = Bit is unkn | own    |  |  |

| bit 15<br>bit 14<br>bit 13 | 1 = PMWR pc<br>0 = PMWR pc<br>PTRDEN: PM<br>1 = PMRD/PM<br>0 = PMRD/PM<br>PTBE1EN: PH<br>1 = PMBE1 pc<br>0 = PMBE1 pc                                          | ort is disabled<br>IP Read/Write 3<br><u>AWR</u> port is en<br>AWR port is dis<br>MP High Nibble<br>ort is enabled<br>ort is disabled | Strobe Port En<br>abled<br>abled<br>e/Byte Enable F | able bit<br>Port Enable bit |                  |                 |        |  |  |

| bit 12                     | 1 = PMBE0 p                                                                                                                                                    | MP Low Nibble<br>ort is enabled<br>ort is disabled                                                                                    | /Byte Enable F                                      | Port Enable bit             |                  |                 |        |  |  |

| pit 11                     | Unimplemen                                                                                                                                                     | ted: Read as '                                                                                                                        | )'                                                  |                             |                  |                 |        |  |  |

| bit 10-9                   | AWAITM<1:0>: Address Latch Strobe Wait State bits<br>11 = Wait of 3½ Tcy<br>10 = Wait of 2½ Tcy<br>01 = Wait of 1½ Tcy<br>00 = Wait of ½ Tcy                   |                                                                                                                                       |                                                     |                             |                  |                 |        |  |  |

| bit 8                      | AWAITE: Address Hold After Address Latch Strobe Wait State bit<br>1 = Wait of 1 <sup>1</sup> / <sub>4</sub> Tcy<br>0 = Wait of <sup>1</sup> / <sub>4</sub> Tcy |                                                                                                                                       |                                                     |                             |                  |                 |        |  |  |

|                            | $0 = Walt of \frac{1}{4}$                                                                                                                                      | TCY                                                                                                                                   |                                                     |                             |                  |                 |        |  |  |

### REGISTER 21-3: PMCON3: EPMP CONTROL REGISTER 3

### **REGISTER 21-6: PMCSxBS: EPMP CHIP SELECT x BASE ADDRESS REGISTER<sup>(2)</sup>**

| R/W <sup>(1)</sup>                                                   | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup>                      | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> |

|----------------------------------------------------------------------|--------------------|--------------------|-----------------------------------------|--------------------|--------------------|--------------------|--------------------|

|                                                                      |                    |                    | BASE                                    | <23:16>            |                    |                    |                    |

| bit 15                                                               |                    |                    |                                         |                    |                    |                    | bit 8              |

|                                                                      |                    |                    |                                         |                    |                    |                    |                    |

| R/W <sup>(1)</sup>                                                   | U-0                | U-0                | U-0                                     | R/W <sup>(1)</sup> | U-0                | U-0                | U-0                |

| BASE15                                                               | _                  | —                  |                                         | BASE11             | _                  |                    | —                  |

| bit 7                                                                |                    |                    |                                         |                    |                    |                    | bit 0              |

|                                                                      |                    |                    |                                         |                    |                    |                    |                    |

| Legend:                                                              |                    |                    |                                         |                    |                    |                    |                    |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                    |                    |                                         |                    |                    |                    |                    |

| -n = Value at POR '1' = Bit is set                                   |                    |                    | '0' = Bit is cleared x = Bit is unknown |                    |                    |                    |                    |

bit 15-7 BASE<23:15>: Chip Select x Base Address bits<sup>(1)</sup>

bit 6-4 Unimplemented: Read as '0'

bit 3 BASE11: Chip Select x Base Address bit<sup>(1)</sup>

bit 2-0 Unimplemented: Read as '0'

Note 1: The value at POR is 0080h for PMCS1BS and 0880h for PMCS2BS.

2: If the whole PMCS2BS register is written together as 0x0000, then the last EDS address for Chip Select 1 will be FFFFFFh. In this case, Chip Select 2 should not be used. PMCS1BS has no such feature.

## 22.2 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- Alarm Value Registers

### 22.2.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value register window (RTCVALH and RTCVALL) uses the RTCPTRx bits (RCFGCAL<9:8>) to select the desired Timer register pair (see Table 22-1).

By writing the RTCVALH byte, the RTCPTR<1:0> bits (the RTCC Pointer value) decrement by one until they reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 22-1: RTCVAL REGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Window |             |  |  |  |  |  |

|-------------|----------------------------|-------------|--|--|--|--|--|

| RICPIRSI.02 | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |  |  |

| 00          | MINUTES                    | SECONDS     |  |  |  |  |  |

| 01          | WEEKDAY                    | HOURS       |  |  |  |  |  |

| 10          | MONTH                      | DAY         |  |  |  |  |  |

| 11          | —                          | YEAR        |  |  |  |  |  |

The Alarm Value register window (ALRMVALH and ALRMVALL) uses the ALRMPTRx bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 22-2).

By writing the ALRMVALH byte, the ALRMPTR<1:0> bits (the Alarm Pointer value) decrement by one until they reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL until the pointer value is manually changed.

#### TABLE 22-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |  |

|---------|-----------------------------|--------------|--|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |  |

| 00      | ALRMMIN                     | ALRMSEC      |  |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |  |

| 11      | _                           | _            |  |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes, the ALRMPTR<1:0> value will be decremented. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note:                 | This only applies to read operations and |  |  |  |  |  |  |

|-----------------------|------------------------------------------|--|--|--|--|--|--|

| not write operations. |                                          |  |  |  |  |  |  |

### 22.2.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RCFGCAL<13>) must be set (see Example 22-1).

| Note: | To avoid accidental writes to the timer, it is<br>recommended that the RTCWREN bit<br>(RCFGCAL<13>) is kept clear at any<br>other time. For the RTCWREN bit to be<br>set, there is only one instruction cycle time<br>window allowed between the 55h/AA<br>sequence and the setting of RTCWREN;<br>therefore, it is recommended that code |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | therefore, it is recommended that code follow the procedure in Example 22-1.                                                                                                                                                                                                                                                              |

## 22.2.3 SELECTING RTCC CLOCK SOURCE

The clock source for the RTCC module can be selected using the RTCLK<1:0> bits in the RTCPWC register. When the bits are set to '00', the Secondary Oscillator (SOSC) is used as the reference clock and when the bits are '01', LPRC is used as the reference clock. When RTCLK<1:0> = 10 and 11, the external power line (50 Hz and 60 Hz) is used as the clock source.

### EXAMPLE 22-1: SETTING THE RTCWREN BIT

```

asm volatile("push w7");

asm volatile("push w8");

asm volatile("disi #5");

asm volatile("mov #0x55, w7");

asm volatile("mov w7, _NVMKEY");

asm volatile("mov #0xAA, w8");

asm volatile("mov w8, _NVMKEY");

asm volatile("bset _RCFGCAL, #13"); //set the RTCWREN bit

asm volatile("pop w8");

asm volatile("pop w7");

```

## REGISTER 22-11: RTCCSWT: RTCC POWER CONTROL AND SAMPLE WINDOW TIMER REGISTER<sup>(1)</sup>

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSTAB7 | PWCSTAB6 | PWCSTAB5 | PWCSTAB4 | PWCSTAB3 | PWCSTAB2 | PWCSTAB1 | PWCSTAB0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R/W-x                   | R/W-x                   | R/W-x                   | R/W-x                   | R/W-x                   | R/W-x                   | R/W-x       | R/W-x                   |

|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------|-------------------------|

| PWCSAMP7 <sup>(2)</sup> | PWCSAMP6 <sup>(2)</sup> | PWCSAMP5 <sup>(2)</sup> | PWCSAMP4 <sup>(2)</sup> | PWCSAMP3 <sup>(2)</sup> | PWCSAMP2 <sup>(2)</sup> | PWCSAMP1(2) | PWCSAMP0 <sup>(2)</sup> |

| bit 7                   |                         |                         |                         |                         |                         |             | bit 0                   |

| Legend:             |        |                                                                |                                                   |                    |

|---------------------|--------|----------------------------------------------------------------|---------------------------------------------------|--------------------|

| R = Readable bit    |        | W = Writable bit                                               | U = Unimplemented bit,                            | , read as '0'      |

| -n = Value          | at POR | '1' = Bit is set                                               | '0' = Bit is cleared                              | x = Bit is unknown |

| bit 15-8            | PWCSTA | B<7:0>: Power Control Stat                                     | ility Window Timer bits                           |                    |

| 11111111 = Stabilit |        | 1 = Stability window is 255 T<br>0 = Stability window is 254 T | 1                                                 |                    |

|                     | •      |                                                                |                                                   |                    |

|                     | •      |                                                                |                                                   |                    |

|                     |        | 1 = Stability window is 1 TPv<br>0 = No stability window; sam  | VCCLK clock period uple window starts when the al | arm event triggers |

| bit 7-0 PWCSAMP     |        | IP<7:0>: Power Control Sar                                     | nple Window Timer bits <sup>(2)</sup>             |                    |

|                     |        | 1 = Sample window is alway<br>0 = Sample window is 254 T       | vs enabled, even when PWCE                        | <b>N</b> = 0       |

- 11111110 = Sample window is 254 TPWCCLK clock periods

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.</li

- **Note 1:** A write to this register is only allowed when RTCWREN = 1.

- 2: The sample window always starts when the stability window timer expires, except when its initial value is 00h.

### REGISTER 30-1: CW1: FLASH CONFIGURATION WORD 1 (CONTINUED)

- bit 4 FWPSA: WDT Prescaler Ratio Select bit

- 1 = Prescaler ratio of 1:128

- 0 = Prescaler ratio of 1:32

- bit 3-0 WDTPS<3:0>: Watchdog Timer Postscaler Select bits

- 1111 = 1:32,768 1110 = 1:16,384 1101 **= 1:8,192** 1100 = 1:4,096 1011 = 1:2,048 1010 = 1:1,024 1001 **= 1:512** 1000 **= 1:256** 0111 = 1:128 0110 = 1:64 0101 = 1:32 0100 = 1:16 0011 **= 1:8** 0010 = 1:4 0001 = 1:2 0000 = 1:1

### REGISTER 30-4: CW4: FLASH CONFIGURATION WORD 4

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | R/PO-1  | r-1 | R/PO-1 |

|---------|---------|---------|---------|---------|---------|-----|--------|

| IOL1WAY | I2C1SEL | PLLDIV3 | PLLDIV2 | PLLDIV1 | PLLDIV0 | —   | DSSWEN |

| bit 15  |         |         |         |         |         |     | bit 8  |

| R/PO-1    | R/PO-1  | R/PO-1   | R/PO-1   | R/PO-1   | R/PO-1   | R/PO-1   | R/PO-1   |

|-----------|---------|----------|----------|----------|----------|----------|----------|

| DSWDTEN   | DSBOREN | DSWDTOSC | DSWDTPS4 | DSWDTPS3 | DSWDTPS2 | DSWDTPS1 | DSWDTPS0 |

| bit 7 bit |         |          |          |          |          |          |          |

| Legend:           | r = Reserved bit | eserved bit PO = Program Once bit |                    |

|-------------------|------------------|-----------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit,            | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared              | x = Bit is unknown |

| bit 23-16 | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <ul> <li>IOL1WAY: IOLOCK One-Way Set Enable bit</li> <li>1 = The IOLOCK bit (OSCCON&lt;6&gt;) can be set once, provided the unlock sequence has been completed; once set, the Peripheral Pin Select registers cannot be written to a second time</li> <li>0 = The IOLOCK bit can be set and cleared as needed, provided the unlock sequence has been completed</li> </ul> |

| bit 14    | I2C1SEL: Alternate I2C1 Location Select bit                                                                                                                                                                                                                                                                                                                               |

|           | <ol> <li>I = I2C1 uses the SCL1 and SDA1 pins</li> <li>I2C1 uses the ASCL1 and ASDA1 pins</li> </ol>                                                                                                                                                                                                                                                                      |

| bit 13-10 | PLLDIV<3:0>: USB 96 MHz PLL Prescaler Select bits                                                                                                                                                                                                                                                                                                                         |

|           | 1111 = PLL is disabled                                                                                                                                                                                                                                                                                                                                                    |

|           | 1110 = 8x PLL is selected<br>1101 = 6x PLL is selected                                                                                                                                                                                                                                                                                                                    |

|           | 1100 = 4x PLL is selected                                                                                                                                                                                                                                                                                                                                                 |

|           | 1011                                                                                                                                                                                                                                                                                                                                                                      |

|           | = Reserved, do not use                                                                                                                                                                                                                                                                                                                                                    |

|           | 1000<br>0111 = Oscillator input divided by 12 (48 MHz input)                                                                                                                                                                                                                                                                                                              |

|           | 0110 = Oscillator input divided by 8 (32 MHz input)                                                                                                                                                                                                                                                                                                                       |

|           | 0101 = Oscillator input divided by 6 (24 MHz input)                                                                                                                                                                                                                                                                                                                       |

|           | 0100 = Oscillator input divided by 5 (20 MHz input)                                                                                                                                                                                                                                                                                                                       |

|           | 0011 = Oscillator input divided by 4 (16 MHz input)<br>0010 = Oscillator input divided by 3 (12 MHz input)                                                                                                                                                                                                                                                                |

|           | 0001 = Oscillator input divided by 2 (8 MHz input)                                                                                                                                                                                                                                                                                                                        |

|           | 0000 = Oscillator input used directly (4 MHz input)                                                                                                                                                                                                                                                                                                                       |

| bit 9     | Reserved: Always maintain as '1'                                                                                                                                                                                                                                                                                                                                          |

| bit 8     | DSSWEN: Deep Sleep Software Control Select bit                                                                                                                                                                                                                                                                                                                            |

|           | <ul> <li>1 = Deep Sleep operation is enabled and controlled by the DSEN bit</li> <li>0 = Deep Sleep operation is disabled</li> </ul>                                                                                                                                                                                                                                      |

| bit 7     | DSWDTEN: Deep Sleep Watchdog Timer Enable bit                                                                                                                                                                                                                                                                                                                             |

|           | 1 = Deep Sleep WDT is enabled                                                                                                                                                                                                                                                                                                                                             |

|           | 0 = Deep Sleep WDT is disabled                                                                                                                                                                                                                                                                                                                                            |

## 33.1 DC Characteristics

### FIGURE 33-1: PIC24FJ128GB204 FAMILY VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL)

### TABLE 33-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                  | Symbol | Min           | Тур | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-----|------|------|

| PIC24FJ128GB204:                                                                                                                                                                        |        |               |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                    | TJ     | -40           | _   | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                     | TA     | -40           | —   | +85  | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$PI/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | PINT + PI/O   |     |      | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                       | PDMAX  | (TJ – TA)/θJA |     |      | W    |

### TABLE 33-2: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                      | Symbol | Тур  | Max | Unit | Notes    |

|-----------------------------------------------------|--------|------|-----|------|----------|

| Package Thermal Resistance, 7.50 mm 28-Pin SOIC     | θJA    | 49   | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 6x6x0.9 mm 28-Pin QFN-S | θJA    | 33.7 | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 8x8 mm 44-Pin QFN       | θJA    | 28   | —   | °C/W | (Note 1) |

| Package Thermal Resistance, 10x10x1 mm 44-Pin TQFP  | θJA    | 39.3 | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 5.30 mm 28-Pin SSOP     | θJA    | _    | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 300 mil 28-Pin SPDIP    | θJA    | _    | _   | °C/W | (Note 1) |

**Note 1:** Junction to ambient thermal resistance; Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| DC CHARAC        | TERISTICS              |             | $ \begin{array}{ll} \mbox{Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array} $ |                            |                  |                                  |  |  |

|------------------|------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------|----------------------------------|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup> | Мах         | Units                                                                                                                                                                                                                                                                      | Operating<br>Temperature   | VDD              | Conditions                       |  |  |

| Incremental C    | Current Brow           | /n-out Rese | t (∆BOR) <sup>(2)</sup>                                                                                                                                                                                                                                                    |                            |                  |                                  |  |  |

| DC25             | 3.1                    | 5.0         | μA                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 2.0V             | 480R <sup>(2)</sup>              |  |  |

|                  | 4.3                    | 6.0         | μA                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 3.3V             |                                  |  |  |

| Incremental C    | Current Watc           | hdog Timer  | . (∆WDT) <sup>(2)</sup>                                                                                                                                                                                                                                                    |                            |                  |                                  |  |  |

| DC71             | 0.8                    | 1.5         | μA                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 2.0V             | ۵WDT <sup>(2)</sup>              |  |  |

|                  | 0.8                    | 1.5         | μA                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 3.3V             |                                  |  |  |

| Incremental C    | Current High           | Low-Voltag  | e Detect (Al                                                                                                                                                                                                                                                               | HLVD) <sup>(2)</sup>       |                  |                                  |  |  |

| DC75             | 4.2                    | 15          | μA                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 2.0V             | AHLVD <sup>(2)</sup>             |  |  |

|                  | 4.2                    | 15          | μA                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 3.3V             |                                  |  |  |

| Incremental C    | Current Real-          | Time Clock  | and Calend                                                                                                                                                                                                                                                                 | lar (∆RTCC) <sup>(2)</sup> |                  |                                  |  |  |

| DC77             | 0.3                    | 1.0         | μA                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 2.0V             | △RTCC (with SOSC) <sup>(2)</sup> |  |  |

|                  | 0.35                   | 1.0         | μA                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 3.3V             |                                  |  |  |

| DC77A            | 0.3                    | 1.0         | μA                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 2.0V             | ∆RTCC (with LPRC) <sup>(2)</sup> |  |  |

|                  | 0.35                   | 1.0         | μΑ                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 3.3V             |                                  |  |  |

| Incremental C    | Current Deep           | Sleep BOF   |                                                                                                                                                                                                                                                                            | (2)                        |                  |                                  |  |  |

| DC81             | 0.11                   | 0.40        | μΑ                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 2.0V             | ∆Deep Sleep BOR <sup>(2)</sup>   |  |  |

|                  | 0.12                   | 0.40        | μA                                                                                                                                                                                                                                                                         | -40°C to +125°C            | 3.3V             |                                  |  |  |

| Incremental C    | Current Deep           | Sleep Wat   | chdog Time                                                                                                                                                                                                                                                                 | r Reset (∆DSWDT            | ) <sup>(2)</sup> | •                                |  |  |