#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                                |

| Number of I/O              | 34                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 12x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb204-e-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

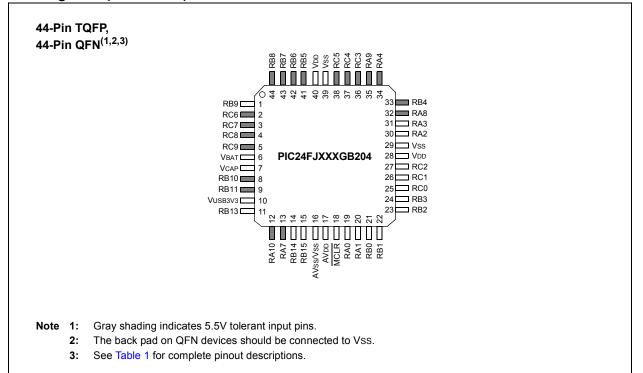

#### **Pin Diagrams (Continued)**

#### TABLE 1: PIC24FJXXXGB204 PIN FUNCTION DESCRIPTIONS

| Pin | Function                                                                   | Pin | Function                                         |

|-----|----------------------------------------------------------------------------|-----|--------------------------------------------------|

| 1   | C1INC/C2INC/C3INC/RP9/SDA1/T1CK/CTED4/PMD3/CN21/RB9                        | 23  | AN4/C1INB/RP2/SDA2/T5CK/T4CK/CTED13/CN6/PMD2/RB2 |

| 2   | RP22/PMA1/PMALH/CN18/RC6                                                   | 24  | AN5/C1INA/RP3/SCL2/CTED8/CN7/PMWR/RB3            |

| 3   | RP23/PMA0/PMALL/CN17/RC7                                                   | 25  | AN10/ <b>RP16</b> /PMBE1/CN8/RC0                 |

| 4   | RP24/PMA5/CN20/RC8                                                         | 26  | AN11/ <b>RP17</b> /CN9/RC1                       |

| 5   | RP25/CTED7/PMA6/CN19/RC9                                                   | 27  | AN12/RP18/PMACK1/CN10/RC2                        |

| 6   | VBAT                                                                       | 28  | VDD                                              |

| 7   | VCAP                                                                       | 29  | Vss                                              |

| 8   | RP10/CTED11/CN16/PGD2/D+/RB10                                              | 30  | OSCI/C1IND/CLKI/PMCS1/CN30/RA2                   |

| 9   | REFI/ <b>RP11</b> /CTED9/CN15/PGC2/D-/RB11                                 | 31  | OSCO/C2IND/CLKO/CN29/RA3                         |

| 10  | VUSB3V3                                                                    | 32  | TDO/PMA8/CN34/RA8                                |

| 11  | AN7/C1INC/REFO/RP13/CTPLS/PMRD/CN13/RB13                                   | 33  | SOSCI/CN1/ <b>RPI4</b> /RB4                      |

| 12  | TMS/PMA2/PMALU/CN36/RA10                                                   | 34  | SOSCO/SCLKI/CN0/RA4                              |

| 13  | TCK/PMA7/CN33/RA7                                                          | 35  | TDI/PMA9/CN35/RA9                                |

| 14  | CVREF/AN6/C3INB/RP14/RTCC/CTED5/CN12/RB14                                  | 36  | RP19/PMBE0/CN28/RC3                              |

| 15  | AN9/C3INA/ <b>RP15</b> /T3CK/T2CK/CTED6/PMA14/CS1/CN11/PMCS/<br>PMCS1/RB15 | 37  | RP20/PMA4/CN25/RC4                               |

| 16  | AVss/Vss                                                                   | 38  | RP21/PMA3/CN26/RC5                               |

| 17  | AVDD                                                                       | 39  | Vss                                              |

| 18  | MCLR                                                                       | 40  | Vdd                                              |

| 19  | CVREF+/VREF+/AN0/C3INC/RP5/ASDA1 <sup>(1)</sup> /CTED1/CN2/PMD7/PGD3/RA0   | 41  | CN27/USBID/RB5                                   |

| 20  | CVREF-/VREF-/AN1/C3IND/RP6/ASCL1 <sup>(1)</sup> /CTED2/CN3/PGC3/RA1        | 42  | PMD6/CN24/VBUS/RB6                               |

| 21  | AN2/CTCMP/C2INB/RP0/CN4/PGD1/HLVDIN/PMD0/RB0                               | 43  | RP7/CTED3/INT0/CN23/PMD5/RB7                     |

| 22  | AN3/C2INA/RP1/CTED12/CN5/PMD1/PGC1/RB1                                     | 44  | RP8/SCL1/CTED10/PMD4/CN22/USBOEN/RB8             |

Legend: RPn represents remappable peripheral pins.

Note 1: Alternative multiplexing for SDA1 and SCL1 when the I2C1SEL Configuration bit is set.

|              | Pin Numl                      | ber/Grid        | Locator            |     |                 |                                       |

|--------------|-------------------------------|-----------------|--------------------|-----|-----------------|---------------------------------------|

| Pin Function | 28-Pin<br>SPDIP/SOIC/<br>SSOP | 28-Pin<br>QFN-S | 44-Pin<br>TQFP/QFN | I/O | Input<br>Buffer | Description                           |

| CN0          | 12                            | 9               | 34                 | _   | _               | Interrupt-on-Change Inputs.           |

| CN1          | 11                            | 8               | 33                 |     |                 |                                       |

| CN2          | 2                             | 27              | 19                 | _   | _               |                                       |

| CN3          | 3                             | 28              | 20                 | _   |                 |                                       |

| CN4          | 4                             | 1               | 21                 |     |                 |                                       |

| CN5          | 5                             | 2               | 22                 | _   | _               |                                       |

| CN6          | 6                             | 3               | 23                 | _   |                 |                                       |

| CN7          | 7                             | 4               | 24                 | _   |                 |                                       |

| CN8          | _                             |                 | 25                 | _   | _               |                                       |

| CN9          | _                             | _               | 26                 | _   | _               | ]                                     |

| CN10         | _                             | _               | 27                 | _   |                 |                                       |

| CN11         | 26                            | 23              | 15                 | _   | _               |                                       |

| CN12         | 25                            | 22              | 14                 | _   |                 |                                       |

| CN13         | 24                            | 21              | 11                 |     |                 |                                       |

| CN15         | 22                            | 19              | 9                  | _   |                 |                                       |

| CN16         | 21                            | 18              | 8                  |     |                 |                                       |

| CN17         | _                             |                 | 3                  | _   | _               |                                       |

| CN18         | —                             |                 | 2                  |     |                 |                                       |

| CN19         | —                             |                 | 5                  | _   | _               |                                       |

| CN20         | _                             |                 | 4                  | _   | _               |                                       |

| CN21         | 18                            | 15              | 1                  | _   | _               |                                       |

| CN22         | 17                            | 14              | 44                 | _   | _               |                                       |

| CN23         | 16                            | 13              | 43                 | _   | _               |                                       |

| CN24         | 15                            | 12              | 42                 | _   | _               |                                       |

| CN25         | —                             |                 | 37                 | _   | _               |                                       |

| CN26         | —                             |                 | 38                 |     |                 | ]                                     |

| CN27         | 14                            | 11              | 41                 | _   |                 | ]                                     |

| CN28         | _                             |                 | 36                 | _   |                 | ]                                     |

| CN29         | 10                            | 7               | 31                 |     |                 | ]                                     |

| CN30         | 9                             | 6               | 30                 | _   |                 | ]                                     |

| CN33         | _                             |                 | 13                 |     |                 | ]                                     |

| CN34         | —                             |                 | 32                 | _   |                 |                                       |

| CN35         | —                             |                 | 35                 | _   |                 |                                       |

| CN36         | _                             | _               | 12                 | _   | —               | ]                                     |

|              | 4                             | 1               | 21                 | 1   | ANA             | CTMU Comparator 2 Input (Pulse mode). |

#### TABLE 1-3: PIC24FJ128GB204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|              | Pin Num                         | per/Grid        | Locator            |     |                      |                                             |

|--------------|---------------------------------|-----------------|--------------------|-----|----------------------|---------------------------------------------|

| Pin Function | 28-Pin<br>SPDIP/SOIC/<br>SSOP   | 28-Pin<br>QFN-S | 44-Pin<br>TQFP/QFN | I/O | Input<br>Buffer      | Description                                 |

| RP0          | 4                               | 1               | 21                 | I/O | ST                   | Remappable Peripheral (input or output).    |

| RP1          | 5                               | 2               | 22                 | I/O | ST                   |                                             |

| RP2          | 6                               | 3               | 23                 | I/O | ST                   |                                             |

| RP3          | 7                               | 4               | 24                 | I/O | ST                   |                                             |

| RP5          | 2                               | 27              | 19                 | I/O | ST                   |                                             |

| RP6          | 3,15                            | 28              | 20                 | I/O | ST                   | 1                                           |

| RP7          | 16                              | 13              | 43                 | I/O | ST                   |                                             |

| RP8          | 17                              | 14              | 44                 | I/O | ST                   | 1                                           |

| RP9          | 18                              | 15              | 1                  | I/O | ST                   |                                             |

| RP10         | 21                              | 18              | 8                  | I/O | ST                   |                                             |

| RP11         | 22                              | 19              | 9                  | I/O | ST                   |                                             |

| RP13         | 24                              | 21              | 11                 | I/O | ST                   |                                             |

| RP14         | 25                              | 22              | 14                 | I/O | ST                   |                                             |

| RP15         | 26                              | 23              | 15                 | I/O | ST                   |                                             |

| RP16         | _                               |                 | 25                 | I/O | ST                   |                                             |

| RP17         | _                               |                 | 26                 | I/O | ST                   |                                             |

| RP18         | _                               |                 | 27                 | I/O | ST                   |                                             |

| RP19         | _                               | —               | 36                 | I/O | ST                   |                                             |

| RP20         | _                               |                 | 37                 | I/O | ST                   |                                             |

| RP21         | _                               |                 | 38                 | I/O | ST                   |                                             |

| RP22         | _                               |                 | 2                  | I/O | ST                   |                                             |

| RP23         | _                               |                 | 3                  | I/O | ST                   |                                             |

| RP24         |                                 |                 | 4                  | I/O | ST                   | 1                                           |

| RP25         |                                 | —               | 5                  | I/O | ST                   |                                             |

| RPI4         | 11                              | 8               | 33                 | Ι   | ST                   | Remappable Peripheral (input).              |

| RTCC         | 25                              | 22              | 14                 | 0   | —                    | Real-Time Clock Alarm/Seconds Pulse Output. |

| SCL1         | 17                              | 14              | 44                 | I/O | l <sup>2</sup> C     | I2C1 Synchronous Serial Clock Input/Output. |

| SCL2         | 7                               | 4               | 24                 | I/O | l <sup>2</sup> C     | I2C2 Synchronous Serial Clock Input/Output. |

| SCLKI        | 12                              | 9               | 34                 | Ι   | —                    | Secondary Oscillator Digital Clock Input.   |

| SDA1         | 18                              | 15              | 1                  | I/O | l <sup>2</sup> C     | I2C1 Data Input/Output.                     |

| SDA2         | 6                               | 3               | 23                 | I/O | l <sup>2</sup> C     | I2C2 Data Input/Output.                     |

| SOSCI        | 11                              | 8               | 33                 | Ι   | ANA                  | Secondary Oscillator/Timer1 Clock Input.    |

| SOSCO        | 12                              | 9               | 34                 | 0   | ANA                  | Secondary Oscillator/Timer1 Clock Output.   |

| ANA =        | Schmitt Trigger<br>Analog input | -               |                    |     | = TTL co<br>= Output | pompatible input I = Input<br>P = Power     |

#### **TABLE 1-3**: PIC24FJ128GB204 FAMILY PINOUT DESCRIPTION (CONTINUED)

$I^2C = ST$  with  $I^2C^{TM}$  or SMBus levels

| REGISTER 3-2: CORCON: CPU CORE CONTROL REGISTER |

|-------------------------------------------------|

|-------------------------------------------------|

| U-0           | U-0   | U-0              | U-0 | U-0                 | U-0              | U-0             | U-0   |

|---------------|-------|------------------|-----|---------------------|------------------|-----------------|-------|

| —             | —     | —                | —   | —                   | —                | —               | —     |

| bit 15        |       | •                |     |                     |                  |                 | bit 8 |

|               |       |                  |     |                     |                  |                 |       |

| U-0           | U-0   | U-0              | U-0 | R/C-0               | r-1              | U-0             | U-0   |

| —             | _     | —                | —   | IPL3 <sup>(1)</sup> | —                | _               | —     |

| bit 7         |       |                  |     |                     |                  |                 | bit 0 |

|               |       |                  |     |                     |                  |                 |       |

| Legend:       |       | C = Clearable    | bit | r = Reserved        | bit              |                 |       |

| R = Readable  | e bit | W = Writable I   | oit | U = Unimplem        | nented bit, read | <b>i as</b> '0' |       |

| -n = Value at | POR   | '1' = Bit is set |     | '0' = Bit is clea   | ared             | x = Bit is unkr | nown  |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

bit 2 Reserved: Read as '1'

- bit 1-0 Unimplemented: Read as '0'

- **Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level; see Register 3-1 for bit description.

#### TABLE 4-11: SPI1 REGISTER MAP

| File      | Addr | Bit 15               | Bit 14    | Bit 13  | Bit 12   | Bit 11  | Bit 10 | Bit 9   | Bit 8    | Bit 7     | Bit 6        | Bit 5   | Bit 4  | Bit 3   | Bit 2   | Bit 1    | Bit 0    | All    |

|-----------|------|----------------------|-----------|---------|----------|---------|--------|---------|----------|-----------|--------------|---------|--------|---------|---------|----------|----------|--------|

| Name      |      |                      |           |         |          |         |        |         |          |           |              |         |        |         |         |          |          | Resets |

| SPI1CON1L | 0300 | SPIEN                | _         | SPISIDL | DISSDO   | MODE32  | MODE16 | SMP     | CKE      | SSEN      | CKP          | MSTEN   | DISSDI | DISSCK  | MCLKEN  | SPIFE    | ENHBUF   | 0000   |

| SPI1CON1H | 0302 | AUDEN                | SPISGNEXT | IGNROV  | IGNTUR   | AUDMONO | URDTEN | AUDMOD1 | AUDMOD0  | FRMEN     | FRMSYNC      | FRMPOL  | MSSEN  | FRMSYPW | FRMCNT2 | FRMCNT1  | FRMCNT0  | 0000   |

| SPI1CON2L | 0304 |                      | _         | -       |          |         |        |         |          |           |              | 0000    |        |         |         |          |          |        |

| SPI1STATL | 0308 | -                    | _         | _       | FRMERR   | SPIBUSY | _      | —       | SPITUR   | SRMT      | SPIROV       | SPIRBE  | _      | SPITBE  | _       | SPITBF   | SPIRBF   | 0028   |

| SPI1STATH | 030A | _                    | _         | RXELM5  | RXELM4   | RXELM3  | RXELM2 | RXELM1  | RXELM0   | _         | _            | TXELM5  | TXELM4 | TXELM3  | TXELM2  | TXELM1   | TXELM0   | 0000   |

| SPI1BUFL  | 030C |                      |           |         |          |         |        |         | SPI1BL   | JFL<15:0> |              |         |        |         |         |          |          | 0000   |

| SPI1BUFH  | 030E |                      |           |         |          |         |        |         | SPI1BU   | FH<31:16> |              |         |        |         |         |          |          | 0000   |

| SPI1BRGL  | 0310 |                      | _         |         |          |         |        |         |          | S         | SPI1BRG<12:0 | >       |        |         |         |          |          | 0000   |

| SPI1IMSKL | 0314 |                      | _         | -       | FRMERREN | BUSYEN  | _      | _       | SPITUREN | SRMTEN    | SPIROVEN     | SPIRBEN | _      | SPITBEN | _       | SPITBFEN | SPIRBFEN | 0000   |

| SPI1IMSKH | 0316 | RXWIEN               | _         | RXMSK5  | RXMSK4   | RXMSK3  | RXMSK2 | RXMSK1  | RXMSK0   | TXWIEN    | _            | TXMSK5  | TXMSK4 | TXMSK3  | TXMSK2  | TXMSK1   | TXMSK0   | 0000   |

| SPI1URDTL | 0318 | SPI1URDTL<15:0> 000  |           |         |          |         |        |         |          | 0000      |              |         |        |         |         |          |          |        |

| SPI1URDTH | 031A | SPI1URDTH<31:16> 000 |           |         |          |         |        |         |          |           | 0000         |         |        |         |         |          |          |        |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: SPI2 REGISTER MAP

| File<br>Name | Addr | Bit 15               | Bit 14    | Bit 13  | Bit 12              | Bit 11                          | Bit 10 | Bit 9   | Bit 8    | Bit 7   | Bit 6        | Bit 5   | Bit 4  | Bit 3   | Bit 2   | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|----------------------|-----------|---------|---------------------|---------------------------------|--------|---------|----------|---------|--------------|---------|--------|---------|---------|----------|----------|---------------|

| SPI2CON1L    | 031C | SPIEN                | —         | SPISIDL | DISSDO              | MODE32                          | MODE16 | SMP     | CKE      | SSEN    | CKP          | MSTEN   | DISSDI | DISSCK  | MCLKEN  | SPIFE    | ENHBUF   | 0000          |

| SPI2CON1H    | 031E | AUDEN                | SPISGNEXT | IGNROV  | IGNTUR              | AUDMONO                         | URDTEN | AUDMOD1 | AUDMOD0  | FRMEN   | FRMSYNC      | FRMPOL  | MSSEN  | FRMSYPW | FRMCNT2 | FRMCNT1  | FRMCNT0  | 0000          |

| SPI2CON2L    | 0320 | —                    | —         | _       | —                   | — — — — — — — — WLENGTH<4:0> 00 |        |         |          |         |              |         | 0000   |         |         |          |          |               |

| SPI2STATL    | 0324 | —                    | —         | _       | FRMERR              | SPIBUSY                         | _      | —       | SPITUR   | SRMT    | SPIROV       | SPIRBE  | _      | SPITBE  | _       | SPITBF   | SPIRBF   | 0028          |

| SPI2STATH    | 0326 | —                    | —         | RXELM5  | RXELM4              | RXELM3                          | RXELM2 | RXELM1  | RXELM0   | _       | _            | TXELM5  | TXELM4 | TXELM3  | TXELM2  | TXELM1   | TXELM0   | 0000          |

| SPI2BUFL     | 0328 |                      |           |         |                     |                                 |        |         | SPI2BUFL | <15:0>  |              |         |        |         |         |          |          | 0000          |

| SPI2BUFH     | 032A |                      |           |         |                     |                                 |        |         | SPI2BUFH | <31:16> |              |         |        |         |         |          |          | 0000          |

| SPI2BRGL     | 032C | _                    | _         | _       |                     |                                 |        |         |          | SI      | PI2BRG<12:0> | •       |        |         |         |          |          | 0000          |

| SPI2IMSKL    | 0330 | _                    | —         | _       | FRMERREN            | BUSYEN                          | _      | _       | SPITUREN | SRMTEN  | SPIROVEN     | SPIRBEN | _      | SPITBEN | _       | SPITBFEN | SPIRBFEN | 0000          |

| SPI2IMSKH    | 0332 | RXWIEN               | —         | RXMSK5  | RXMSK4              | RXMSK3                          | RXMSK2 | RXMSK1  | RXMSK0   | TXWIEN  | _            | TXMSK5  | TXMSK4 | TXMSK3  | TXMSK2  | TXMSK1   | TXMSK0   | 0000          |

| SPI2URDTL    | 0334 |                      |           |         | SPI2URDTL<15:0> 000 |                                 |        |         |          |         |              |         | 0000   |         |         |          |          |               |

| SPI2URDTH    | 0336 | SPI2URDTH<31:16> 000 |           |         |                     |                                 |        |         |          |         | 0000         |         |        |         |         |          |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2013-2015 Microchip Technology Inc.

**IFS2: INTERRUPT FLAG STATUS REGISTER 2**

**REGISTER 8-7:**

| U-0              | R/W-0          | R/W-0                              | U-0              | U-0               | R/W-0            | R/W-0            | R/W-0  |

|------------------|----------------|------------------------------------|------------------|-------------------|------------------|------------------|--------|

| _                | DMA4IF         | PMPIF                              | —                | —                 | OC6IF            | OC5IF            | IC6IF  |

| bit 15           |                |                                    |                  |                   |                  |                  | bit 8  |

|                  |                |                                    |                  |                   |                  |                  |        |

| R/W-0            | R/W-0          | R/W-0                              | R/W-0            | R/W-0             | R/W-0            | R/W-0            | R/W-0  |

| IC5IF            | IC4IF          | IC3IF                              | DMA3IF           | CRYROLLIF         | CRYFREEIF        | SPI2TXIF         | SPI2IF |

| bit 7            |                |                                    |                  |                   |                  |                  | bit 0  |

|                  |                |                                    |                  |                   |                  |                  |        |

| Legend:          |                |                                    |                  |                   |                  |                  |        |

| R = Readabl      |                | W = Writable                       |                  | •                 | nented bit, read |                  |        |

| -n = Value at    | PUR            | '1' = Bit is set                   |                  | '0' = Bit is clea | ared             | x = Bit is unkno | nwc    |

| bit 15           | Unimplemen     | nted: Read as '                    | ר <b>י</b>       |                   |                  |                  |        |

| bit 14           | -              | IA Channel 4 In                    |                  | tatus hit         |                  |                  |        |

| л 1 <del>4</del> |                | request has occ                    |                  |                   |                  |                  |        |

|                  |                | request has not                    |                  |                   |                  |                  |        |

| bit 13           | PMPIF: Para    | llel Master Port                   | Interrupt Flag   | Status bit        |                  |                  |        |

|                  |                | request has occ                    |                  |                   |                  |                  |        |

|                  | •              | request has not                    |                  |                   |                  |                  |        |

| oit 12-11        | -              | nted: Read as '                    |                  |                   |                  |                  |        |

| pit 10           | -              | request has occ                    |                  | upt Flag Status I | JIC              |                  |        |

|                  |                | request has oct                    |                  |                   |                  |                  |        |

| bit 9            | •              | •                                  |                  | upt Flag Status I | oit              |                  |        |

|                  | 1 = Interrupt  | request has occ                    | curred           |                   |                  |                  |        |

|                  |                | request has not                    |                  |                   |                  |                  |        |

| bit 8            |                | Capture Channe                     |                  | -lag Status bit   |                  |                  |        |

|                  |                | request has occ<br>request has not |                  |                   |                  |                  |        |

| bit 7            |                | Capture Channe                     |                  | -lag Status bit   |                  |                  |        |

|                  |                | request has occ                    | •                | lag clatac bit    |                  |                  |        |

|                  |                | request has not                    |                  |                   |                  |                  |        |

| bit 6            | IC4IF: Input ( | Capture Channe                     | el 4 Interrupt F | -lag Status bit   |                  |                  |        |

|                  |                | request has occ                    |                  |                   |                  |                  |        |

| L:1 F            |                | request has not                    |                  |                   |                  |                  |        |

| bit 5            | -              | Capture Channo<br>request has occ  | -                | lag Status bit    |                  |                  |        |

|                  |                | request has not                    |                  |                   |                  |                  |        |

| bit 4            | •              | IA Channel 3 In                    |                  | tatus bit         |                  |                  |        |

|                  | 1 = Interrupt  | request has occ                    | curred           |                   |                  |                  |        |

|                  |                | request has not                    |                  |                   |                  |                  |        |

| oit 3            |                | : Cryptographic                    |                  | us bit            |                  |                  |        |

|                  |                | request has occ<br>request has not |                  |                   |                  |                  |        |

|                  | -              | request lias 10                    |                  |                   |                  |                  |        |

| hit 2            | CRVEDEELE      | Cryptographia                      | Ruffer Fron 9    | tatus hit         |                  |                  |        |

| bit 2            |                | : Cryptographic<br>request has occ |                  | tatus bit         |                  |                  |        |

| U-0           | R/W-0                 | R/W-0                             | R/W-0           | R/W-0             | R/W-0            | U-0             | R/W-0    |

|---------------|-----------------------|-----------------------------------|-----------------|-------------------|------------------|-----------------|----------|

|               | RTCIE                 | DMA5IE                            | SPI3RXIE        | SPI2RXIE          | SPI1RXIE         |                 | KEYSTRIE |

| bit 15        |                       |                                   |                 |                   |                  |                 | bit 8    |

|               |                       |                                   |                 |                   |                  |                 |          |

| R/W-0         | R/W-0                 | R/W-0                             | U-0             | U-0               | R/W-0            | R/W-0           | U-0      |

| CRYDNIE       | INT4IE <sup>(1)</sup> | INT3IE <sup>(1)</sup>             | —               | _                 | MI2C2IE          | SI2C2IE         | —        |

| bit 7         |                       |                                   |                 |                   |                  |                 | bit 0    |

|               |                       |                                   |                 |                   |                  |                 |          |

| Legend:       | 1.11                  |                                   |                 |                   |                  | (0)             |          |

| R = Readable  |                       | W = Writable                      | bit             | •                 | nented bit, read |                 |          |

| -n = Value at | POR                   | '1' = Bit is set                  |                 | '0' = Bit is clea | ared             | x = Bit is unki | nown     |

| bit 15        | Unimplemen            | ted: Read as '                    | )'              |                   |                  |                 |          |

| bit 14        | -                     |                                   |                 | errupt Enable b   | it               |                 |          |

| bit i i       |                       | request is enab                   |                 |                   | it i             |                 |          |

|               | •                     | equest is not e                   |                 |                   |                  |                 |          |

| bit 13        | DMA5IE: DM            | A Channel 5 In                    | terrupt Enable  | bit               |                  |                 |          |

|               |                       | equest is enab                    |                 |                   |                  |                 |          |

|               | •                     | request is not e                  |                 |                   |                  |                 |          |

| bit 12        |                       | PI3 Receive Int                   | -               | bit               |                  |                 |          |

|               |                       | equest is enab<br>equest is not e |                 |                   |                  |                 |          |

| bit 11        | •                     | PI2 Receive Int                   |                 | h it              |                  |                 |          |

| DILTI         |                       | request is enab                   | •               | DIL               |                  |                 |          |

|               | •                     | request is enab                   |                 |                   |                  |                 |          |

| bit 10        | -                     | PI1 Receive Int                   |                 | bit               |                  |                 |          |

|               |                       | equest is enab                    | •               |                   |                  |                 |          |

|               |                       | equest is not e                   |                 |                   |                  |                 |          |

| bit 9         | Unimplemen            | ted: Read as '                    | )'              |                   |                  |                 |          |

| bit 8         | KEYSTRIE: (           | Cryptographic K                   | ey Store Progr  | am Done Inter     | rupt Enable bit  |                 |          |

|               |                       | request is enab                   |                 |                   |                  |                 |          |

|               | •                     | request is not e                  |                 |                   |                  |                 |          |

| bit 7         |                       |                                   |                 | Interrupt Enable  | e bit            |                 |          |

|               |                       | equest is enab<br>equest is not e |                 |                   |                  |                 |          |

| bit 6         | -                     | nal Interrupt 4                   |                 |                   |                  |                 |          |

| DILO          |                       | request is enab                   |                 |                   |                  |                 |          |

|               | •                     | request is not e                  |                 |                   |                  |                 |          |

| bit 5         | -                     | nal Interrupt 3                   |                 |                   |                  |                 |          |

|               |                       | equest is enab                    |                 |                   |                  |                 |          |

|               | 0 = Interrupt r       | request is not e                  | nabled          |                   |                  |                 |          |

| bit 4-3       | Unimplemen            | ted: Read as '                    | )'              |                   |                  |                 |          |

| bit 2         | MI2C2IE: Ma           | ster I2C2 Even                    | t Interrupt Ena | ble bit           |                  |                 |          |

|               |                       | equest is enab                    |                 |                   |                  |                 |          |

|               | 0 = Interrupt r       | request is not e                  | nabled          |                   |                  |                 |          |

|               |                       |                                   |                 |                   |                  |                 |          |

#### REGISTER 8-16: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

**Note 1:** If an external interrupt is enabled, the interrupt input must also be configured to an available RPn or RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

#### 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

**Note:** The Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

#### 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in CW2 must be programmed to '0'. (For more information, refer to **Section 30.1 "Configuration Bits"**.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC<2:0> bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC<2:0> bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM is enabled) or SOSC (if SOSCEN remains set).

- Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

#### REGISTER 11-16: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | SCK2R5 | SCK2R4 | SCK2R3 | SCK2R2 | SCK2R1 | SCK2R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | SCK2R<5:0>: Assign SPI2 Clock Input (SCK2IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | SDI2R<5:0>: Assign SPI2 Data Input (SDI2) to Corresponding RPn or RPIn Pin bits    |

#### REGISTER 11-17: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | TMRCKR5 | TMRCKR4 | TMRCKR3 | TMRCKR2 | TMRCKR1 | TMRCKR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS2R5 | SS2R4 | SS2R3 | SS2R2 | SS2R1 | SS2R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 TMRCKR<5:0>: Assign General Timer External Input (TMRCK) to Corresponding RPn or RPIn Pin bits bit 7-6 Unimplemented: Read as '0'

bit 5-0 SS2R<5:0>: Assign SPI2 Slave Select Input (SS2IN) to Corresponding RPn or RPIn Pin bits

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Synchronization/Trigger Source Selection bits

- 1111x = Reserved

- 11101 = Reserved

- 11100 = CTMU<sup>(1)</sup>

- 11011 = A/D<sup>(1)</sup>

- $11010 = \text{Comparator 3}^{(1)}$

- 11001 = Comparator 2<sup>(1)</sup>

- 11000 = Comparator 1<sup>(1)</sup>

- 10111 = Reserved

- 10110 = Reserved

- 10101 =Input Capture 6<sup>(2)</sup>

- 10100 =Input Capture 5<sup>(2)</sup>

- 10011 =Input Capture 4<sup>(2)</sup>

- 10010 =Input Capture  $3^{(2)}$

- 10001 =Input Capture  $2^{(2)}$

- 10000 = Input Capture 1<sup>(2)</sup>

- 01111 = Timer5

- 01110 = Timer4

- 01101 = Timer3

- 01100 = Timer2

- 01011 = Timer1

- 01010 = Reserved

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Output Compare 6

- 00101 = Output Compare 5

- 00100 = Output Compare 4

- 00011 = Output Compare 3

- 00010 = Output Compare 2

- 00001 = Output Compare 1

- 00000 = Not synchronized to any other module

- Note 1: Use these inputs as trigger sources only and never as sync sources.

- 2: Never use an IC module as its own trigger source by selecting this mode.

### 15.0 OUTPUT COMPARE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Output Compare with Dedicated Timer" (DS70005159). The information in this data sheet supersedes the information in the FRM.

Devices in the PIC24FJ128GB204 family all feature six independent output compare modules. Each of these modules offers a wide range of configuration and operating options for generating pulse trains on internal device events, and can produce Pulse-Width Modulated (PWM) waveforms for driving power applications.

Key features of the output compare module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 31 user-selectable trigger/sync sources available

- Two separate Period registers (a main register, OCxR, and a secondary register, OCxRS) for greater flexibility in generating pulses of varying widths

- Configurable for single pulse or continuous pulse generation on an output event, or continuous PWM waveform generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

#### 15.1 General Operating Modes

#### 15.1.1 SYNCHRONOUS AND TRIGGER MODES

When the output compare module operates in a Free-Running mode, the internal 16-bit counter, OCxTMR, runs counts up continuously, wrapping around from 0xFFFF to 0x0000 on each overflow. Its period is synchronized to the selected external clock source. Compare or PWM events are generated each time a match between the internal counter and one of the Period registers occurs.

In Synchronous mode, the module begins performing its compare or PWM operation as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the module's internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the counter to run.

Free-Running mode is selected by default or any time that the SYNCSELx bits (OCxCON2<4:0>) are set to '00000'. Synchronous or Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The OCTRIG bit (OCxCON2<7>) selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the sync/trigger source.

#### 15.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own set of 16-bit Timer and Duty Cycle registers. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module, Output Compare x (OCx), provides the Least Significant 16 bits of the 32-bit register pairs and the even numbered module, Output Compare y (OCy), provides the Most Significant 16 bits. Wrap arounds of the OCx registers cause an increment of their corresponding OCy registers.

Cascaded operation is configured in hardware by setting the OC32 bit (OCxCON2<8>) for both modules. For more information on cascading, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Output Compare with Dedicated Timer"** (DS70005159).

#### 16.3 Enhanced Slave Mode

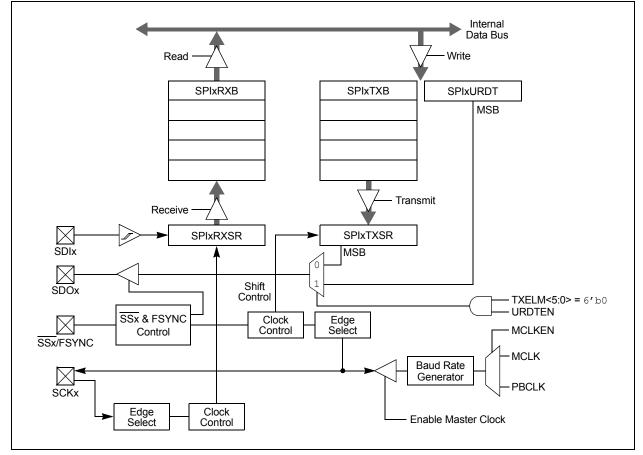

To set up the SPIx module for the Enhanced Buffer Master mode of operation:

- 1. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP<2:0> bits in the respective IPCx register.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with MSTEN (SPIxCON1L<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTATL<6>).

- 4. Select Enhanced Buffer mode by setting the ENHBUF bit (SPIxCON1L<0>).

- Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

#### 16.4 Enhanced Master Mode

To set up the SPIx module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP<2:0> bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with the MSTEN bit (SPIxCON1L<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- 7. Select Enhanced Buffer mode by setting the ENHBUF bit (SPIxCON1L<0>).

- 8. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

© 2013-2015 Microchip Technology Inc.

| R-0, HSC                | R-0, HSC                                                                                                                                                                                                                                                                                                                               | R-0, HSC                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                   | U-0                                                                                                            | R/C-0, HSC                                                | R-0, HSC         | R-0, HSC      |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------|---------------|--|

| ACKSTAT                 | TRSTAT                                                                                                                                                                                                                                                                                                                                 | ACKTIM                                                                                                                                                                                                                                            |                                                                                                                                                                                       |                                                                                                                | BCL                                                       | GCSTAT           | ADD10         |  |

| bit 15                  | 4                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                   |                                                                                                                                                                                       |                                                                                                                | •                                                         |                  | bit           |  |

|                         |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                   |                                                                                                                                                                                       |                                                                                                                |                                                           |                  |               |  |

| R/C-0, HS               | R/C-0, HS                                                                                                                                                                                                                                                                                                                              | R-0, HSC                                                                                                                                                                                                                                          | R/C-0, HSC                                                                                                                                                                            | R/C-0, HSC                                                                                                     | R-0, HSC                                                  | R-0, HSC         | R-0, HSC      |  |

| IWCOL                   | I2COV                                                                                                                                                                                                                                                                                                                                  | D/Ā                                                                                                                                                                                                                                               | Р                                                                                                                                                                                     | S                                                                                                              | R/W                                                       | RBF              | TBF           |  |

| bit 7                   |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                   |                                                                                                                                                                                       |                                                                                                                |                                                           |                  | bit           |  |

|                         |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                   |                                                                                                                                                                                       |                                                                                                                |                                                           |                  |               |  |

| Legend:                 |                                                                                                                                                                                                                                                                                                                                        | C = Clearable                                                                                                                                                                                                                                     |                                                                                                                                                                                       |                                                                                                                | are Settable/Cle                                          |                  |               |  |

| R = Readable            |                                                                                                                                                                                                                                                                                                                                        | HS = Hardware                                                                                                                                                                                                                                     | e Settable bit                                                                                                                                                                        | •                                                                                                              | nented bit, read                                          | <b>l as</b> '0'  |               |  |

| -n = Value at           | POR                                                                                                                                                                                                                                                                                                                                    | '1' = Bit is set                                                                                                                                                                                                                                  |                                                                                                                                                                                       | '0' = Bit is cle                                                                                               | ared                                                      | x = Bit is unkn  | own           |  |

| bit 15                  | ACKSTAT: A                                                                                                                                                                                                                                                                                                                             | cknowledge Stat                                                                                                                                                                                                                                   | us hit (undated                                                                                                                                                                       | d in all Master :                                                                                              | and Slave mod                                             | 29)              |               |  |

|                         |                                                                                                                                                                                                                                                                                                                                        | dge was not rec                                                                                                                                                                                                                                   |                                                                                                                                                                                       |                                                                                                                |                                                           |                  |               |  |

|                         |                                                                                                                                                                                                                                                                                                                                        | dge was receive                                                                                                                                                                                                                                   |                                                                                                                                                                                       |                                                                                                                |                                                           |                  |               |  |

| bit 14                  | TRSTAT: Trar                                                                                                                                                                                                                                                                                                                           | nsmit Status bit (                                                                                                                                                                                                                                | when operating                                                                                                                                                                        | g as l <sup>2</sup> C™ mas                                                                                     | ter; applicable t                                         | o master transı  | nit operatio  |  |

|                         |                                                                                                                                                                                                                                                                                                                                        | ansmit is in prog                                                                                                                                                                                                                                 | •                                                                                                                                                                                     | ACK)                                                                                                           |                                                           |                  |               |  |

|                         |                                                                                                                                                                                                                                                                                                                                        | ansmit is not in p                                                                                                                                                                                                                                | -                                                                                                                                                                                     | _                                                                                                              |                                                           |                  |               |  |

| bit 13                  |                                                                                                                                                                                                                                                                                                                                        | nowledge Time                                                                                                                                                                                                                                     | •                                                                                                                                                                                     |                                                                                                                | • •                                                       |                  |               |  |

|                         |                                                                                                                                                                                                                                                                                                                                        | I <sup>2</sup> C bus is in an                                                                                                                                                                                                                     |                                                                                                                                                                                       |                                                                                                                |                                                           |                  | ock           |  |

|                         | 0 = Not an Acknowledge sequence, cleared on 9th rising edge of SCLx clock                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                   |                                                                                                                                                                                       |                                                                                                                |                                                           |                  |               |  |

| bit 12-11               | Unimplemented: Read as '0'<br>BCL: Bus Collision Detect bit (Master/Slave mode; cleared when I <sup>2</sup> C module is disabled, I2                                                                                                                                                                                                   |                                                                                                                                                                                                                                                   |                                                                                                                                                                                       |                                                                                                                |                                                           |                  |               |  |