Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SmartCard, SPI, UART/USART             |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT         |

| Number of I/O              | 34                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

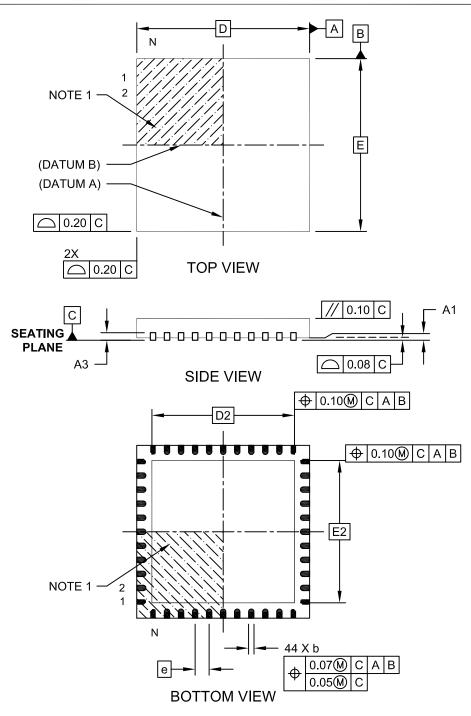

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb204t-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP (CONTINUED)

| File<br>Name | Addr | Bit 15 | Bit 14    | Bit 13    | Bit 12    | Bit 11 | Bit 10  | Bit 9      | Bit 8   | Bit 7   | Bit 6     | Bit 5       | Bit 4     | Bit 3   | Bit 2     | Bit 1       | Bit 0     | All<br>Resets |

|--------------|------|--------|-----------|-----------|-----------|--------|---------|------------|---------|---------|-----------|-------------|-----------|---------|-----------|-------------|-----------|---------------|

| IPC16        | 00C4 | _      | CRCIP2    | CRCIP1    | CRCIP0    | _      | U2ERIP2 | U2ERIP1    | U2ERIP0 | _       | U1ERIP2   | U1ERIP1     | U1ERIP0   | _       | _         | _           | _         | 4440          |

| IPC18        | 00C8 | -      | _         | _         | _         | _      | _       | _          | _       | _       |           | _           | _         | _       | I         | HLVDIP<2:0> |           | 0004          |

| IPC19        | 00CA | -      | _         | _         | _         | _      | _       | _          | _       | _       | (         | CTMUIP<2:0  | >         | _       | _         | _           | _         | 0040          |

| IPC20        | 00CC | -      | U3TXIP2   | U3TXIP1   | U3TXIP0   | _      | U3RXIP2 | U3RXIP1    | U3RXIP0 | _       | U3ERIP2   | U3ERIP1     | U3ERIP0   | _       | _         | _           | _         | 4440          |

| IPC21        | 00CE | _      | U4ERIP2   | U4ERIP1   | U4ERIP0   | _      | USB1IP2 | USB1IP1    | USB1IP0 | _       | I2C2BCIP2 | I2C2BCIP1   | I2C2BCIP0 | _       | I2C1BCIP2 | I2C1BCIP1   | I2C1BCIP0 | 4444          |

| IPC22        | 00D0 | _      | SPI3TXIP2 | SPI3TXIP1 | SPI3TXIP0 | _      | SPI3IP2 | SPI3IP1    | SPI3IP0 | _       | U4TXIP2   | U4TXIP1     | U4TXIP0   | _       | U4RXIP2   | U4RXIP1     | U4RXIP0   | 4444          |

| IPC26        | 00D8 | _      | _         | _         | _         | _      |         | FSTIP<2:0> |         | _       |           | _           | _         | _       | _         | _           | _         | 0400          |

| IPC29        | 00DE | _      | _         | _         | _         | _      | _       | _          | _       | _       |           | JTAGIP<2:0> | >         | _       | _         | _           | _         | 0040          |

| INTTREG      | 00E0 | CPUIRQ | r         | VHOLD     | —         | ILR3   | ILR2    | ILR1       | ILR0    | VECNUM7 | VECNUM6   | VECNUM5     | VECNUM4   | VECNUM3 | VECNUM2   | VECNUM1     | VECNUM0   | 0000          |

Legend: — = unimplemented, read as '0'; r = reserved bit, maintain as '0'. Reset values are shown in hexadecimal.

| DSRPAG<br>(Data Space Read<br>Register) | DSWPAG<br>(Data Space Write<br>Register) | Source/Destination<br>Address while<br>Indirect<br>Addressing | 24-Bit EA<br>Pointing to EDS | Comment                           |

|-----------------------------------------|------------------------------------------|---------------------------------------------------------------|------------------------------|-----------------------------------|

| x <sup>(1)</sup>                        | x <sup>(1)</sup>                         | 0000h to 1FFFh                                                | 000000h to<br>001FFFh        | Near Data Space <sup>(2)</sup>    |

| Χ. ,                                    | Χ',                                      | 2000h to 7FFFh                                                | 002000h to<br>007FFFh        |                                   |

| 001h                                    | 001h                                     |                                                               | 008000h to<br>00FFFEh        |                                   |

| 002h                                    | 002h                                     |                                                               | 010000h to<br>017FFEh        |                                   |

| 003h                                    | 003h                                     |                                                               | 018000h to<br>0187FEh        | EPMP Memory Space                 |

| •                                       | •                                        | 8000h to FFFFh                                                | •                            | Li wi wemory space                |

| •                                       | •                                        |                                                               | •                            |                                   |

| •<br>1FFh                               | •<br>1FFh                                |                                                               | FF8000h to<br>FFFFFEh        |                                   |

| 000h                                    | 000h                                     |                                                               | Invalid Address              | Address Error Trap <sup>(3)</sup> |

## TABLE 4-35: EDS MEMORY ADDRESS WITH DIFFERENT PAGES AND ADDRESSES

Note 1: If the source/destination address is below 8000h, the DSRPAG and DSWPAG registers are not considered.

2: This Data Space can also be accessed by Direct Addressing.

**3:** When the source/destination address is above 8000h and DSRPAG/DSWPAG are '0', an address error trap will occur.

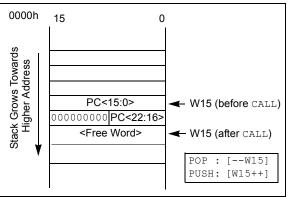

## 4.2.6 SOFTWARE STACK

Apart from its use as a Working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer (SSP). The pointer always points to the first available free word and grows from lower to higher addresses. It predecrements for stack pops and post-increments for stack pushes, as shown in Figure 4-7. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL Register to the |

|       | MSB of the PC prior to the push.         |

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated using W15 as a Source or Destination Pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address, 2000h in RAM, initialize the SPLIM with the value, 1FFEh.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the SFR space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

FIGURE 4-7: CALL STACK FRAME

### REGISTER 8-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

- bit 2 OC1IF: Output Compare Channel 1 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 1 IC1IF: Input Capture Channel 1 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 INTOIF: External Interrupt 0 Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

## REGISTER 8-13: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

| U-0           | R/W-0                                | R/W-0                             | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------------------------------|-----------------------------------|-----------------|------------------|------------------|-----------------|--------|

|               | DMA1IE                               | AD1IE                             | U1TXIE          | U1RXIE           | SPI1TXIE         | SPI1IE          | T3IE   |

| bit 15        |                                      |                                   |                 |                  |                  |                 | bit 8  |

| R/W-0         | R/W-0                                | R/W-0                             | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T2IE          | OC2IE                                | IC2IE                             | DMA0IE          | T1IE             | OC1IE            | IC1IE           | INTOIE |

| bit 7         | OOZIL                                | IOZIL                             | DIVIAUL         | 1112             | OUTIL            | IOTIL           | bit (  |

| Legend:       |                                      |                                   |                 |                  |                  |                 |        |

| R = Readabl   | le bit                               | W = Writable                      | bit             | U = Unimplen     | nented bit, read | l as '0'        |        |

| -n = Value at | t POR                                | '1' = Bit is set                  |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15        | Unimplemen                           | ted: Read as '                    | ר,              |                  |                  |                 |        |

| bit 14        | •                                    | A Channel 1 In                    |                 | bit              |                  |                 |        |

|               |                                      | equest is enab                    | •               |                  |                  |                 |        |

|               | 0 = Interrupt r                      | equest is not e                   | nabled          |                  |                  |                 |        |

| bit 13        |                                      | Interrupt Enal                    |                 |                  |                  |                 |        |

|               |                                      | equest is enab<br>equest is not e |                 |                  |                  |                 |        |

| bit 12        | •                                    | T1 Transmitter                    |                 | ole hit          |                  |                 |        |

|               |                                      | equest is enab                    | -               |                  |                  |                 |        |

|               | 0 = Interrupt request is not enabled |                                   |                 |                  |                  |                 |        |

| bit 11        |                                      | RT1 Receiver Ir                   | •               | e bit            |                  |                 |        |

|               |                                      | equest is enab<br>equest is not e |                 |                  |                  |                 |        |

| bit 10        | SPI1TXIE: SF                         | PI1 Transmit Co                   | omplete Interru | pt Enable bit    |                  |                 |        |

|               |                                      | equest is enab<br>equest is not e |                 |                  |                  |                 |        |

| bit 9         | •                                    | General Interr                    |                 |                  |                  |                 |        |

|               | 1 = Interrupt r                      | equest is enab<br>equest is not e | led             |                  |                  |                 |        |

| bit 8         | -                                    | Interrupt Enab                    |                 |                  |                  |                 |        |

|               | 1 = Interrupt r                      | equest is enab<br>equest is not e | led             |                  |                  |                 |        |

| bit 7         | •                                    | Interrupt Enab                    |                 |                  |                  |                 |        |

|               |                                      | equest is enab                    |                 |                  |                  |                 |        |

|               |                                      | equest is not e                   |                 |                  |                  |                 |        |

| bit 6         | •                                    | ut Compare Ch                     |                 | pt Enable bit    |                  |                 |        |

|               |                                      | equest is enab<br>equest is not e |                 |                  |                  |                 |        |

| bit 5         | •                                    | Capture Channe                    |                 | nable bit        |                  |                 |        |

| bit o         | 1 = Interrupt r                      | equest is enab<br>equest is not e | led             |                  |                  |                 |        |

| bit 4         | -                                    | A Channel 0 In                    |                 | hit              |                  |                 |        |

|               |                                      | equest is enab                    | -               |                  |                  |                 |        |

|               |                                      | equest is not e                   |                 |                  |                  |                 |        |

| bit 3         | T1IE: Timer1                         | Interrupt Enab                    | le bit          |                  |                  |                 |        |

|               |                                      | equest is enab<br>equest is not e |                 |                  |                  |                 |        |

© 2013-2015 Microchip Technology Inc.

| U-0           | R/W-0                 | R/W-0                             | R/W-0           | R/W-0             | R/W-0            | U-0             | R/W-0    |

|---------------|-----------------------|-----------------------------------|-----------------|-------------------|------------------|-----------------|----------|

|               | RTCIE                 | DMA5IE                            | SPI3RXIE        | SPI2RXIE          | SPI1RXIE         |                 | KEYSTRIE |

| bit 15        |                       |                                   |                 |                   |                  |                 | bit 8    |

|               |                       |                                   |                 |                   |                  |                 |          |

| R/W-0         | R/W-0                 | R/W-0                             | U-0             | U-0               | R/W-0            | R/W-0           | U-0      |

| CRYDNIE       | INT4IE <sup>(1)</sup> | INT3IE <sup>(1)</sup>             | —               | _                 | MI2C2IE          | SI2C2IE         | —        |

| bit 7         |                       |                                   |                 |                   |                  |                 | bit 0    |

|               |                       |                                   |                 |                   |                  |                 |          |

| Legend:       | 1.11                  |                                   |                 |                   |                  | (0)             |          |

| R = Readable  |                       | W = Writable                      | bit             | •                 | nented bit, read |                 |          |

| -n = Value at | POR                   | '1' = Bit is set                  |                 | '0' = Bit is clea | ared             | x = Bit is unki | nown     |

| bit 15        | Unimplemen            | ted: Read as '                    | )'              |                   |                  |                 |          |

| bit 14        | -                     |                                   |                 | errupt Enable b   | it               |                 |          |

| bit i i       |                       | request is enab                   |                 |                   | it i             |                 |          |

|               | •                     | equest is not e                   |                 |                   |                  |                 |          |

| bit 13        | DMA5IE: DM            | A Channel 5 In                    | terrupt Enable  | bit               |                  |                 |          |

|               |                       | equest is enab                    |                 |                   |                  |                 |          |

|               | •                     | request is not e                  |                 |                   |                  |                 |          |

| bit 12        |                       | PI3 Receive Int                   | -               | bit               |                  |                 |          |

|               |                       | equest is enab<br>equest is not e |                 |                   |                  |                 |          |

| bit 11        | •                     | PI2 Receive Int                   |                 | h it              |                  |                 |          |

| DILTI         |                       | request is enab                   | •               | DIL               |                  |                 |          |

|               | •                     | request is enab                   |                 |                   |                  |                 |          |

| bit 10        | -                     | PI1 Receive Int                   |                 | bit               |                  |                 |          |

|               |                       | equest is enab                    | •               |                   |                  |                 |          |

|               |                       | equest is not e                   |                 |                   |                  |                 |          |

| bit 9         | Unimplemen            | ted: Read as '                    | )'              |                   |                  |                 |          |

| bit 8         | KEYSTRIE: (           | Cryptographic K                   | ey Store Progr  | am Done Inter     | rupt Enable bit  |                 |          |

|               |                       | request is enab                   |                 |                   |                  |                 |          |

|               | •                     | request is not e                  |                 |                   |                  |                 |          |

| bit 7         |                       |                                   |                 | Interrupt Enable  | e bit            |                 |          |

|               |                       | equest is enab<br>equest is not e |                 |                   |                  |                 |          |

| bit 6         | -                     | nal Interrupt 4                   |                 |                   |                  |                 |          |

| DILO          |                       | request is enab                   |                 |                   |                  |                 |          |

|               | •                     | request is not e                  |                 |                   |                  |                 |          |

| bit 5         | -                     | nal Interrupt 3                   |                 |                   |                  |                 |          |

|               |                       | equest is enab                    |                 |                   |                  |                 |          |

|               | 0 = Interrupt r       | request is not e                  | nabled          |                   |                  |                 |          |

| bit 4-3       | Unimplemen            | ted: Read as '                    | )'              |                   |                  |                 |          |

| bit 2         | MI2C2IE: Ma           | ster I2C2 Even                    | t Interrupt Ena | ble bit           |                  |                 |          |

|               |                       | equest is enab                    |                 |                   |                  |                 |          |

|               | 0 = Interrupt r       | request is not e                  | nabled          |                   |                  |                 |          |

|               |                       |                                   |                 |                   |                  |                 |          |

#### REGISTER 8-16: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

**Note 1:** If an external interrupt is enabled, the interrupt input must also be configured to an available RPn or RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

## **REGISTER 10-1:** DSCON: DEEP SLEEP CONTROL REGISTER<sup>(1)</sup>

| R/W-0         | U-0                               | U-0                                | U-0                      | U-0                                         | U-0               | U-0                  | U-0           |  |  |  |

|---------------|-----------------------------------|------------------------------------|--------------------------|---------------------------------------------|-------------------|----------------------|---------------|--|--|--|

| DSEN          | —                                 | —                                  | —                        | _                                           | —                 | —                    | —             |  |  |  |

| bit 15        |                                   |                                    |                          |                                             |                   |                      | bit 8         |  |  |  |

|               |                                   |                                    |                          |                                             |                   |                      |               |  |  |  |

| U-0           | U-0                               | U-0                                | U-0                      | U-0                                         | r-0               | R/W-0                | R/C-0, HS     |  |  |  |

|               |                                   |                                    |                          |                                             |                   | DSBOR <sup>(2)</sup> | RELEASE       |  |  |  |

| bit 7         |                                   |                                    |                          |                                             |                   |                      | bit 0         |  |  |  |

|               |                                   |                                    |                          |                                             |                   |                      |               |  |  |  |

| Legend:       |                                   | C = Clearable                      | bit                      | U = Unimplem                                | nented bit, read  | as '0'               |               |  |  |  |

| R = Readabl   | R = Readable bit W = Writable bit |                                    |                          | HS = Hardware Settable bit r = Reserved bit |                   |                      |               |  |  |  |

| -n = Value at | t POR                             | '1' = Bit is set                   |                          | '0' = Bit is cleared x = Bit is unknown     |                   |                      |               |  |  |  |

|               |                                   |                                    |                          |                                             |                   |                      |               |  |  |  |

| bit 15        |                                   | Sleep Enable b                     |                          |                                             |                   |                      |               |  |  |  |

|               |                                   | ep Sleep on ex                     |                          |                                             |                   |                      |               |  |  |  |

|               |                                   | rmal Sleep on                      |                          | WRSAV #0                                    |                   |                      |               |  |  |  |

| bit 14-3      | •                                 | ted: Read as '                     | )'                       |                                             |                   |                      |               |  |  |  |

| bit 2         | Reserved: Ma                      |                                    |                          |                                             |                   |                      |               |  |  |  |

| bit 1         | DSBOR: Dee                        | p Sleep BOR E                      | Event bit <sup>(2)</sup> |                                             |                   |                      |               |  |  |  |

|               |                                   |                                    |                          |                                             | ed during Deep    | •                    |               |  |  |  |

|               | 0 = The DSB0                      | OR was not act                     | ive, or was act          | ive, but did not                            | t detect a BOR    | event during D       | eep Sleep     |  |  |  |

| bit 0         | RELEASE: 1/0                      | O Pin State Re                     | lease bit                |                                             |                   |                      |               |  |  |  |

|               |                                   | <b>U</b> 1                         |                          |                                             | ir states previou |                      |               |  |  |  |

|               |                                   | I/O pins from t<br>bits to control |                          | ious to Deep S                              | leep entry, and   | allows their res     | pective TRISx |  |  |  |

- **Note 1:** All register bits are reset only in the case of a POR event outside of Deep Sleep mode.

- **2:** Unlike all other events, a Deep Sleep BOR event will NOT cause a wake-up from Deep Sleep; this re-arms the POR.

## 11.1.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

## 11.1.2 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, each port pin can also be individually configured for either a digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V), on any desired digital only pins, by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

## 11.2 Configuring Analog Port Pins (ANSx)

The ANSx and TRISx registers control the operation of the pins with analog function. Each port pin with analog function is associated with one of the ANSx bits (see Register 11-1 through Register 11-3), which decides if the pin function should be analog or digital. Refer to Table 11-1 for detailed behavior of the pin for different ANSx and TRISx bit settings.

When reading the PORTx register, all pins configured as analog input channels will read as cleared (a low level).

### 11.2.1 ANALOG INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Most input pins are able to handle DC voltages of up to 5.5V, a level typical for digital logic circuits. However, several pins can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should always be avoided.

Table 11-2 summarizes the different voltage tolerances. For more information, refer to **Section 33.0 "Electrical Characteristics"** for more details.

| Pin Function   | ANSx Setting | TRISx Setting | Comments                                                                                                                                   |

|----------------|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Input   | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Analog Output  | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Digital Input  | 0            | 1             | Firmware must wait at least one instruction cycle<br>after configuring a pin as a digital input before a valid<br>input value can be read. |

| Digital Output | 0            | 0             | Make sure to disable the analog output function on the pin if any is present.                                                              |

## TABLE 11-1: CONFIGURING ANALOG/DIGITAL FUNCTION OF AN I/O PIN

## TABLE 11-2: INPUT VOLTAGE LEVELS FOR PORT OR PIN TOLERATED DESCRIPTION INPUT

| Port or Pin                  | Tolerated Input | Description                                                          |  |  |

|------------------------------|-----------------|----------------------------------------------------------------------|--|--|

| PORTA<10:7,4> <sup>(1)</sup> |                 |                                                                      |  |  |

| PORTB<11:10,8:4>             | 5.5V            | Tolerates input levels above VDD; useful<br>for most standard logic. |  |  |

| PORTC<9:3> <sup>(1)</sup>    |                 | for most standard logic.                                             |  |  |

| PORTA<3:0>                   |                 |                                                                      |  |  |

| PORTB<15:13,9,3:0>           | Vdd             | Only VDD input levels are tolerated.                                 |  |  |

| PORTC<2:0> <sup>(1)</sup>    |                 |                                                                      |  |  |

**Note 1:** Not all of these pins are implemented in 28-pin devices. Refer to **Section 1.0 "Device Overview**" for a complete description of port pin implementation.

#### REGISTER 16-3: SPIxCON2L: SPIx CONTROL REGISTER 2 LOW

| U-0          | U-0                                        | U-0              | U-0      | U-0                 | U-0              | U-0             | U-0   |

|--------------|--------------------------------------------|------------------|----------|---------------------|------------------|-----------------|-------|

| _            | _                                          | _                | _        | _                   | _                | _               | —     |

| bit 15       | ·                                          | ·                |          | ·                   | ·                | •               | bit 8 |

|              |                                            |                  |          |                     |                  |                 |       |

| U-0          | U-0                                        | U-0              | R/W-0    | R/W-0               | R/W-0            | R/W-0           | R/W-0 |

| _            | —                                          | —                |          | W                   | LENGTH<4:0>      | (1,2)           |       |

| bit 7        | ·                                          | ·                |          |                     |                  |                 | bit   |

|              |                                            |                  |          |                     |                  |                 |       |

| Legend:      |                                            |                  |          |                     |                  |                 |       |

| R = Readab   | ole bit                                    | W = Writable     | bit      | U = Unimpler        | nented bit, read | l as '0'        |       |

| -n = Value a | It POR                                     | '1' = Bit is set |          | '0' = Bit is cle    | ared             | x = Bit is unkn | own   |

|              |                                            |                  |          |                     |                  |                 |       |

| bit 15-5     | Unimplemen                                 | ted: Read as '   | )'       |                     |                  |                 |       |

| bit 4-0      | -                                          | 4:0>: Variable V |          | ts <sup>(1,2)</sup> |                  |                 |       |

|              | 11111 <b>= 32-</b> t                       |                  | <b>-</b> |                     |                  |                 |       |

|              | 11110 = <b>31-</b> k                       |                  |          |                     |                  |                 |       |

|              | 11101 <b>= 30-</b> b                       | oit data         |          |                     |                  |                 |       |

|              | 11100 <b>= 29-</b> k                       |                  |          |                     |                  |                 |       |

|              | 11011 <b>= 28-</b> k                       |                  |          |                     |                  |                 |       |

|              | 11010 = 27-b                               |                  |          |                     |                  |                 |       |

|              | 11001 = 26-b<br>11000 = 25-b               |                  |          |                     |                  |                 |       |

|              | 10111 <b>= 24-</b> k                       |                  |          |                     |                  |                 |       |

|              | 10110 <b>= 23-</b> k                       |                  |          |                     |                  |                 |       |

|              | 10101 <b>= 22-k</b>                        | oit data         |          |                     |                  |                 |       |

|              | 10100 <b>= 21-</b> k                       |                  |          |                     |                  |                 |       |

|              | 10011 <b>= 20-k</b>                        |                  |          |                     |                  |                 |       |

|              | 10010 = 19-k<br>10001 = 18-k               |                  |          |                     |                  |                 |       |

|              | 10000 = <b>17-</b> k                       |                  |          |                     |                  |                 |       |

|              | 01111 = <b>16-</b> k                       |                  |          |                     |                  |                 |       |

|              | 01110 <b>= 15-</b> k                       | oit data         |          |                     |                  |                 |       |

|              | 01101 <b>= 14-k</b>                        | oit data         |          |                     |                  |                 |       |

|              | 01100 = <b>13</b> -b                       |                  |          |                     |                  |                 |       |

|              | 01011 = <b>12-k</b>                        |                  |          |                     |                  |                 |       |

|              | 01010 = 11-b<br>01001 = 10-b               |                  |          |                     |                  |                 |       |

|              | 01000 = 9-bit                              |                  |          |                     |                  |                 |       |

|              | 00111 <b>= 8-bi</b>                        |                  |          |                     |                  |                 |       |

|              | 00110 <b>= 7-bi</b>                        | t data           |          |                     |                  |                 |       |

|              | 00101 <b>= 6-bi</b>                        |                  |          |                     |                  |                 |       |

|              | 00100 <b>= 5-bi</b>                        |                  |          |                     |                  |                 |       |

|              | 00011 = <b>4-bi</b><br>00010 = <b>3-bi</b> |                  |          |                     |                  |                 |       |

|              | 00010 = 3-01                               | i nala           |          |                     |                  |                 |       |

|              | 00001 = <b>2-bi</b>                        |                  |          |                     |                  |                 |       |

#### **Note 1:** These bits are effective when AUDEN = 0 only.

2: Varying the length by changing these bits does not affect the depth of the TX/RX FIFO.

| U-0        | U-0                                                                                                                                                       | U-0                                                    | U-0                                                                  | U-0                                             | U-0              | U-0               | U-0             |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------|------------------|-------------------|-----------------|--|--|--|--|--|

| _          | _                                                                                                                                                         | —                                                      | —                                                                    | —                                               | _                | _                 | _               |  |  |  |  |  |

| bit 15     | ·                                                                                                                                                         |                                                        |                                                                      | ·                                               |                  |                   | bit 8           |  |  |  |  |  |

|            |                                                                                                                                                           |                                                        |                                                                      |                                                 |                  |                   |                 |  |  |  |  |  |

| U-0        | R/W-0                                                                                                                                                     | R/W-0                                                  | R/W-0                                                                | R/W-0                                           | R/W-0            | R/W-0             | R/W-0           |  |  |  |  |  |

|            | PCIE                                                                                                                                                      | SCIE                                                   | BOEN                                                                 | SDAHT                                           | SBCDE            | AHEN              | DHEN            |  |  |  |  |  |

| bit 7      |                                                                                                                                                           |                                                        |                                                                      |                                                 |                  |                   | bit 0           |  |  |  |  |  |

| Legend:    |                                                                                                                                                           |                                                        |                                                                      |                                                 |                  |                   |                 |  |  |  |  |  |

| R = Reada  | ble bit                                                                                                                                                   | W = Writable I                                         | oit                                                                  | U = Unimplem                                    | nented bit, read | as '0'            |                 |  |  |  |  |  |

| -n = Value | at POR                                                                                                                                                    | '1' = Bit is set                                       |                                                                      | '0' = Bit is clea                               | ared             | x = Bit is unkn   | own             |  |  |  |  |  |

|            |                                                                                                                                                           |                                                        |                                                                      |                                                 |                  |                   |                 |  |  |  |  |  |

| bit 15-7   | •                                                                                                                                                         | ted: Read as 'C                                        |                                                                      |                                                 |                  |                   |                 |  |  |  |  |  |

| bit 6      |                                                                                                                                                           | ondition Interru                                       | •                                                                    |                                                 | de only).        |                   |                 |  |  |  |  |  |

|            |                                                                                                                                                           | nterrupt on dete                                       |                                                                      | condition                                       |                  |                   |                 |  |  |  |  |  |

| bit 5      | •                                                                                                                                                         | ection interrupts                                      |                                                                      | 2C Slove mode                                   |                  |                   |                 |  |  |  |  |  |

| DIL D      | <b>SCIE:</b> Start Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)<br>1 = Enables interrupt on detection of Start or Restart conditions |                                                        |                                                                      |                                                 |                  |                   |                 |  |  |  |  |  |

|            |                                                                                                                                                           | 0 = Start detection interrupts are disabled            |                                                                      |                                                 |                  |                   |                 |  |  |  |  |  |

| bit 4      |                                                                                                                                                           | r Overwrite Ena                                        |                                                                      | ve mode only)                                   |                  |                   |                 |  |  |  |  |  |

|            |                                                                                                                                                           | / is updated and                                       | 0                                                                    | nerated for a re                                | ceived address   | s/data byte, igno | oring the state |  |  |  |  |  |

|            |                                                                                                                                                           | COV bit only if the                                    |                                                                      | in elece                                        |                  |                   |                 |  |  |  |  |  |

| bit 3      |                                                                                                                                                           | / is only update<br>x Hold Time Se                     |                                                                      | is clear                                        |                  |                   |                 |  |  |  |  |  |

| DIL S      |                                                                                                                                                           | of 300 ns hold                                         |                                                                      | after the falling                               | edge of SCL x    |                   |                 |  |  |  |  |  |

|            |                                                                                                                                                           | of 100 ns hold                                         |                                                                      |                                                 |                  |                   |                 |  |  |  |  |  |

| bit 2      | SBCDE: Slav                                                                                                                                               | /e Mode Bus Co                                         | ollision Detect                                                      | Enable bit (I <sup>2</sup> C                    | Slave mode or    | nly)              |                 |  |  |  |  |  |

|            |                                                                                                                                                           | ng edge of SCL                                         |                                                                      |                                                 |                  |                   |                 |  |  |  |  |  |

|            |                                                                                                                                                           | t and the bus go                                       | pes Idle. This I                                                     | Detection mode                                  | is only valid d  | uring data and    | ACK transmit    |  |  |  |  |  |

|            | sequences.                                                                                                                                                | slave bus collisi                                      | on interrupts                                                        |                                                 |                  |                   |                 |  |  |  |  |  |

|            |                                                                                                                                                           | s collision interri                                    |                                                                      | ed                                              |                  |                   |                 |  |  |  |  |  |

| bit 1      | AHEN: Addre                                                                                                                                               | ess Hold Enable                                        | e bit (I <sup>2</sup> C Slave                                        | mode only)                                      |                  |                   |                 |  |  |  |  |  |

|            | 1 = Following                                                                                                                                             | n the 8th fallin                                       | a edge of SC                                                         | Ix for a mate                                   | ching received   | address byte;     | SCI REL bit     |  |  |  |  |  |

|            |                                                                                                                                                           |                                                        |                                                                      |                                                 |                  |                   | 001.111         |  |  |  |  |  |

|            | •                                                                                                                                                         | NL<12>) will be                                        | cleared and S                                                        |                                                 | d low            |                   |                 |  |  |  |  |  |

| bit 0      | 0 = Address                                                                                                                                               | NL<12>) will be holding is disab                       | cleared and S<br>led                                                 | SCLx will be hel                                | d low            |                   |                 |  |  |  |  |  |

| bit 0      | 0 = Address <b>DHEN:</b> Data                                                                                                                             | NL<12>) will be                                        | cleared and S<br>led<br>(I <sup>2</sup> C Slave mo                   | SCLx will be hel<br>de only)                    |                  | hardware clears   |                 |  |  |  |  |  |

| bit 0      | 0 = Address<br>DHEN: Data<br>1 = Following<br>bit (I2Cx)                                                                                                  | NL<12>) will be<br>holding is disab<br>Hold Enable bit | cleared and S<br>led<br>(I <sup>2</sup> C Slave mo<br>edge of SCLx f | CLx will be hel<br>de only)<br>or a received da |                  | hardware clears   |                 |  |  |  |  |  |

### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6       | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | <ul> <li>11 = Interrupt is set on an RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on an RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters</li> </ul> |

| bit 5         | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                                                                                                                                                                                    |

|               | <ul> <li>1 = Address Detect mode is enabled (if 9-bit mode is not selected, this does not take effect)</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                                                             |

| bit 4         | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                                                                                                                                                                                                       |

|               | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                                                                                                                                                                                                      |

| bit 3         | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                  |

|               | <ul> <li>1 = Parity error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                            |

| bit 2         | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                 |

|               | <ul> <li>1 = Framing error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>a = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                          |

| <b>h</b> :4 4 | 0 = Framing error has not been detected                                                                                                                                                                                                                                                                                                                                                                    |

| bit 1         | <b>OERR:</b> Receive Buffer Overrun Error Status bit (clear/read-only)<br>1 = Receive buffer has overflowed                                                                                                                                                                                                                                                                                                |

|               | 1 = Receive buffer has overflowed (clearing a previously set OERR bit (1 → 0 transition); will reset the receive buffer and the RSR to the empty state)                                                                                                                                                                                                                                                    |

| bit 0         | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                                                                                                                                                                                                                 |

|               | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                                              |

| Note 1        | : The value of this bit only affects the transmit properties of the module when the IrDA <sup>®</sup> encoder is enabled (IREN = 1).                                                                                                                                                                                                                                                                       |

2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

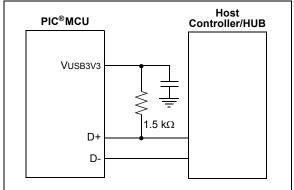

## 19.1 Hardware Configuration

## 19.1.1 DEVICE MODE

### 19.1.1.1 D+ Pull-up Resistor

PIC24FJ128GB204 family devices have a built-in 1.5 kΩ resistor on the D+ line that is available when the microcontroller is operating in Device mode. This is used to signal an external host that the device is operating in Full-Speed Device mode. It is engaged by setting the USBEN bit (U1CON<0>). If the OTGEN bit (U1OTGCON<2>) is set, then the D+ pull-up is enabled through the DPPULUP bit (U1OTGCON<7>).

Alternatively, an external resistor may be used on D+, as shown in Figure 19-2.

#### 19.1.1.2 Power Modes

Many USB applications will likely have several different sets of power requirements and configuration. The most common power modes encountered are:

- Bus Power Only mode

- · Self-Power Only mode

- Dual Power with Self-Power Dominance mode

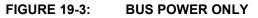

Bus Power Only mode (Figure 19-3) is effectively the simplest method. All power for the application is drawn from the USB.

To meet the inrush current requirements of the *"USB 2.0 Specification"*, the total effective capacitance appearing across VBUS and ground must be no more than 10  $\mu$ F.

In the USB Suspend mode, devices must consume no more than 2.5 mA from the 5V VBUS line of the USB cable. During the USB Suspend mode, the D+ or D-pull-up resistor must remain active, which will consume some of the allowed suspend current.

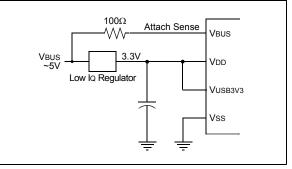

In Self-Power Only mode (Figure 19-4), the USB application provides its own power, with very little power being pulled from the USB. Note that an attach indication is added to indicate when the USB has been connected and the host is actively powering VBUS.

To meet compliance specifications, the USB module (and the D+ or D- pull-up resistor) should not be enabled until the host actively drives VBUS high. One of the 5.5V tolerant I/O pins may be used for this purpose.

The application should never source any current onto the 5V VBUS pin of the USB cable.

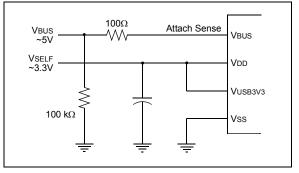

The Dual Power with Self-Power Dominance mode (Figure 19-5) allows the application to use internal power primarily, but switch to power from the USB when no internal power is available. Dual power devices must also meet all of the special requirements for inrush current and Suspend mode current previously described, and must not enable the USB module until VBUS is driven high.

FIGURE 19-4: SELF-POWER ONLY

FIGURE 19-5:

DUAL POWER EXAMPLE

#### 19.4.2 RECEIVING AN IN TOKEN IN DEVICE MODE

- 1. Attach to a USB host and enumerate as described in Chapter 9 of the "USB 2.0 Specification".

- 2. Create a data buffer and populate it with the data to send to the host.

- 3. In the appropriate (Even or Odd) TX BD for the desired endpoint:

- a) Set up the status register (BDnSTAT) with the correct data toggle (DATA0/1) value and the byte count of the data buffer.

- b) Set up the address register (BDnADR) with the starting address of the data buffer.

- c) Set the UOWN bit of the status register to '1'.

- When the USB module receives an IN token, it automatically transmits the data in the buffer. Upon completion, the module updates the status register (BDnSTAT) and sets the Transfer Done Interrupt Flag, TRNIF (U1IR<3>).

## 19.4.3 RECEIVING AN OUT TOKEN IN DEVICE MODE

- 1. Attach to a USB host and enumerate as described in Chapter 9 of the "USB 2.0 Specification".

- 2. Create a data buffer with the amount of data you are expecting from the host.

- 3. In the appropriate (Even or Odd) TX BD for the desired endpoint:

- a) Set up the status register (BDnSTAT) with the correct data toggle (DATA0/1) value and the byte count of the data buffer.

- b) Set up the address register (BDnADR) with the starting address of the data buffer.

- c) Set the UOWN bit of the status register to '1'.

- 4. When the USB module receives an OUT token, it automatically receives the data sent by the host to the buffer. Upon completion, the module updates the status register (BDnSTAT) and sets the Transfer Done Interrupt Flag, TRNIF (U1IR<3>).

## **19.5 Host Mode Operation**

The following sections describe how to perform common Host mode tasks. In Host mode, USB transfers are invoked explicitly by the host software. The host software is responsible for the Acknowledge portion of the transfer. Also, all transfers are performed using the USB Endpoint 0 Control register (U1EP0) and Buffer Descriptors.

#### 19.5.1 ENABLE HOST MODE AND DISCOVER A CONNECTED DEVICE

- Enable Host mode by setting the HOSTEN bit (U1CON<3>). This causes the Host mode control bits in other USB OTG registers to become available.

- Enable the D+ and D- pull-down resistors by setting the DPPULDWN and DMPULDWN bits (U10TGCON<5:4>). Disable the D+ and Dpull-up resistors by clearing the DPPULUP and DMPULUP bits (U10TGCON<7:6>).

- At this point, Start-of-Frame (SOF) generation begins with the SOF counter loaded with 12,000. Eliminate noise on the USB by clearing the SOFEN bit (U1CON<0>) to disable Start-of-Frame packet generation.

- 4. Enable the device attached interrupt by setting the ATTACHIE bit (U1IE<6>).

- Wait for the device attached interrupt (U1IR<6> = 1). This is signaled by the USB device changing the state of D+ or D- from '0' to '1' (SE0 to J-state). After it occurs, wait 100 ms for the device power to stabilize.

- Check the state of the JSTATE and SE0 bits in U1CON. If the JSTATE bit (U1CON<7>) is '0', the connecting device is low speed. If the connecting device is low speed, set the LSPDEN and LSPD bits (U1ADDR<7> and U1EP0<7>, respectively) to enable low-speed operation.

- Reset the USB device by setting the USBRST bit (U1CON<4>) for at least 50 ms, sending Reset signaling on the bus. After 50 ms, terminate the Reset by clearing USBRST.

- In order to keep the connected device from going into suspend, enable the SOF packet generation by setting the SOFEN bit.

- 9. Wait 10 ms for the device to recover from Reset.

- 10. Perform enumeration as described by Chapter 9 of the "USB 2.0 Specification".

## 19.5.3 SEND A FULL-SPEED BULK DATA TRANSFER TO A TARGET DEVICE

- Follow the procedure described in Section 19.5.1 "Enable Host Mode and Discover a Connected Device" and Section 19.5.2 "Complete a Control Transaction to a Connected Device" to discover and configure a device.

- To enable transmit and receive transfers with handshaking enabled, write 1Dh to U1EP0. If the target device is a low-speed device, also set the LSPD (U1EP0<7>) bit. If you want the hardware to automatically retry indefinitely, if the target device asserts a NAK on the transfer, clear the Retry Disable bit, RETRYDIS (U1EP0<6>).

- 3. Set up the BD for the current (Even or Odd) TX EP0 to transfer up to 64 bytes.

- 4. Set the USB device address of the target device in the USB Address register (U1ADDR<6:0>).

- 5. Write an OUT token to the desired endpoint to U1TOK. This triggers the module's transmit state machines to begin transmitting the token and the data.

- 6. Wait for the Transfer Done Interrupt Flag, TRNIF. This indicates that the BD has been released back to the microprocessor and the transfer has completed. If the Retry Disable bit (RETRYDIS) is set, the handshake (ACK, NAK, STALL or ERROR (0Fh)) is returned in the BD PID field. If a STALL interrupt occurs, the pending packet must be dequeued and the error condition in the target device cleared. If a detach interrupt occurs (SE0 for more than 2.5 µs), then the target has detached (U1IR<0> is set).

- 7. Once the Transfer Done Interrupt Flag occurs (TRNIF is set), the BD can be examined and the next data packet queued by returning to Step 2.

- **Note:** USB speed, transceiver and pull-ups should only be configured during the module setup phase. It is not recommended to change these settings while the module is enabled.

## 19.6 OTG Operation

### 19.6.1 SESSION REQUEST PROTOCOL (SRP)

An OTG A-device may decide to power down the VBUS supply when it is not using the USB link through the Session Request Protocol (SRP). Software may do this by clearing VBUSON (U10TGCON<3>). When the VBUS supply is powered down, the A-device is said to have ended a USB session.

An OTG A-device or embedded host may repower the VBUS supply at any time (initiate a new session). An OTG B-device may also request that the OTG A-device repower the VBUS supply (initiate a new session). This is accomplished via the Session Request Protocol (SRP).

Prior to requesting a new session, the B-device must first check that the previous session has definitely ended. To do this, the B-device must check for two conditions:

1. VBUS supply is below the session valid voltage.

2. Both D+ and D- have been low for at least 2 ms.

The B-device will be notified of Condition 1 by the SESENDIF (U1OTGIR<2>) interrupt. Software will have to manually check for Condition 2.

| Note: | When the A-device powers down the VBUS supply, the B-device must discon- |

|-------|--------------------------------------------------------------------------|

|       | nect its pull-up resistor from power. If the                             |

|       | device is self-powered, it can do this by                                |

|       | clearing DPPULUP (U1OTGCON<7>)                                           |

|       | and DMPULUP (U1OTGCON<6>).                                               |

The B-device may aid in achieving Condition 1 by discharging the VBUS supply through a resistor. Software may do this by setting VBUSDIS (U1OTGCON<0>).

After these initial conditions are met, the B-device may begin requesting the new session. The B-device begins by pulsing the D+ data line. Software should do this by setting DPPULUP (U10TGCON<7>). The data line should be held high for 5 to 10 ms.

The B-device then proceeds by pulsing the VBUS supply. Software should do this by setting PUVBUS (U1CNFG2<4>). When an A-device detects SRP signaling (either via the ATTACHIF (U1IR<6>) interrupt or via the SESVDIF (U1OTGIR<3>) interrupt), the A-device must restore the VBUS supply by either setting VBUSON (U1OTGCON<3>) or by setting the I/O port controlling the external power source.

The B-device should not monitor the state of the VBUS supply while performing VBUS supply pulsing. When the B-device does detect that the VBUS supply has been restored (via the SESVDIF (U1OTGIR<3>) interrupt), the B-device must reconnect to the USB link by pulling up D+ or D- (via the DPPULUP or DMPULUP bits).

The A-device must complete the SRP by driving USB Reset signaling.

## 21.0 ENHANCED PARALLEL MASTER PORT (EPMP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Enhanced Parallel Master Port (EPMP)" (DS39730). The information in this data sheet supersedes the information in the FRM.

The Enhanced Parallel Master Port (EPMP) module provides a parallel, 4-bit (Master mode only) and 8-bit (Master and Slave modes) data bus interface to communicate with off-chip modules, such as memories, FIFOs, LCD controllers and other microcontrollers. This module can serve as either the master or the slave on the communication bus.

For EPMP Master modes, all external addresses are mapped into the internal Extended Data Space (EDS). This is done by allocating a region of the EDS for each chip select and then assigning each chip select to a particular external resource, such as a memory or external controller. This region should not be assigned to another device resource, such as RAM or SFRs. To perform a write or read on an external resource, the CPU simply performs a write or read within the address range assigned for the EPMP. Key features of the EPMP module are:

- Extended Data Space (EDS) Interface allows Direct Access from the CPU

- Up to 10 Programmable Address Lines

- Up to 2 Chip Select Lines

- Up to 1 Acknowledgment Line (one per chip select)

- · 4-Bit and 8-Bit Wide Data Bus

- Programmable Strobe Options (per chip select)

- Individual Read and Write Strobes or;

- Read/Write Strobe with Enable Strobe

- Programmable Address/Data Multiplexing

- Programmable Address Wait States

- Programmable Data Wait States (per chip select)

- Programmable Polarity on Control Signals (per chip select)

- Legacy Parallel Slave Port (PSP) Support

- Enhanced Parallel Slave Port Support

- Address Support

- 4-Byte Deep Auto-Incrementing Buffer

## 21.1 Memory Addressable in Different Modes