Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                    |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT       |

| Number of I/O              | 20                                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb202-e-mm |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                      | Pin Num                       | per/Grid        | Locator            |     |                 |                                            |

|----------------------|-------------------------------|-----------------|--------------------|-----|-----------------|--------------------------------------------|

| Pin Function         | 28-Pin<br>SPDIP/SOIC/<br>SSOP | 28-Pin<br>QFN-S | 44-Pin<br>TQFP/QFN | I/O | Input<br>Buffer | Description                                |

| PMA0/PMALL           | _                             | —               | 3                  | 0   |                 | Parallel Master Port Address.              |

| PMA1/PMALH           |                               |                 | 2                  | 0   | _               |                                            |

| PMA14/PMCS/<br>PMCS1 | -                             | —               | 15                 | 0   | —               |                                            |

| PMA2/PMALU           | —                             |                 | 12                 | 0   | _               |                                            |

| PMA3                 | —                             |                 | 38                 | 0   | _               |                                            |

| PMA4                 |                               |                 | 37                 | 0   | _               |                                            |

| PMA5                 | _                             |                 | 4                  | 0   | _               |                                            |

| PMA6                 |                               |                 | 5                  | 0   | _               |                                            |

| PMA7                 | _                             | _               | 13                 | 0   | _               |                                            |

| PMA8                 |                               |                 | 32                 | 0   | _               |                                            |

| PMA9                 |                               | —               | 35                 | 0   | _               |                                            |

| PMACK1               |                               | —               | 27                 | Ι   | ST/TTL          | Parallel Master Port Acknowledge Input 1.  |

| PMBE0                |                               | _               | 36                 | 0   | _               | Parallel Master Port Byte Enable 0 Strobe. |

| PMBE1                |                               | —               | 25                 | 0   | _               | Parallel Master Port Byte Enable 1 Strobe. |

| PMCS1                |                               | _               | 30                 | I/O | ST/TTL          | Parallel Master Port Chip Select 1 Strobe. |

| PMD0                 |                               |                 | 21                 | I/O | ST/TTL          | Parallel Master Port Data (Demultiplexed   |

| PMD1                 | _                             |                 | 22                 | I/O | ST/TTL          | Master mode) or Address/Data (Multiplexed  |

| PMD2                 |                               |                 | 23                 | I/O | ST/TTL          | Master modes).                             |

| PMD3                 |                               |                 | 1                  | I/O | ST/TTL          |                                            |

| PMD4                 |                               | —               | 44                 | I/O | ST/TTL          |                                            |

| PMD5                 |                               |                 | 43                 | I/O | ST/TTL          |                                            |

| PMD6                 |                               |                 | 20                 | I/O | ST/TTL          |                                            |

| PMD7                 |                               |                 | 19                 | I/O | ST/TTL          |                                            |

| PMRD                 |                               |                 | 11                 | 0   | _               | Parallel Master Port Read Strobe.          |

| PMWR                 | _                             | —               | 24                 | 0   | —               | Parallel Master Port Write Strobe.         |

| RA0                  | 2                             | 27              | 19                 | I/O | ST              | PORTA Digital I/Os.                        |

| RA1                  | 3                             | 28              | 20                 | I/O | ST              |                                            |

| RA2                  | 9                             | 6               | 30                 | I/O | ST              |                                            |

| RA3                  | 10                            | 7               | 31                 | I/O | ST              |                                            |

| RA4                  | 12                            | 9               | 34                 | Ι   | ST              |                                            |

| RA7                  | _                             | —               | 13                 | I/O | ST              |                                            |

| RA8                  | _                             | —               | 32                 | I/O | ST              |                                            |

|                      |                               | —               | 35                 | I/O | ST              |                                            |

| RA9                  |                               |                 | 1                  |     | ST              | 1                                          |

## TABLE 1-3: PIC24FJ128GB204 FAMILY PINOUT DESCRIPTION (CONTINUED)

$I^2C$  = ST with  $I^2C^{TM}$  or SMBus levels

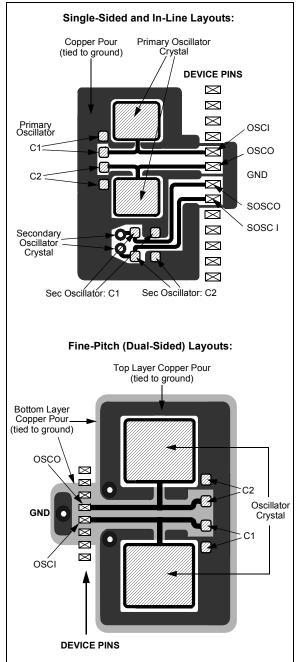

## 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator (refer to Section 9.0 "Oscillator Configuration" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### FIGURE 2-5:

### PLACEMENT OF THE OSCILLATOR CIRCUIT

SUGGESTED

| REGISTER 3-2: CORCON: CPU CORE CONTROL REGISTER |

|-------------------------------------------------|

|-------------------------------------------------|

| U-0           | U-0   | U-0              | U-0 | U-0                                     | U-0 | U-0 | U-0   |  |  |

|---------------|-------|------------------|-----|-----------------------------------------|-----|-----|-------|--|--|

| —             | —     | —                | —   | —                                       | —   | —   | —     |  |  |

| bit 15        |       | •                |     |                                         |     |     | bit 8 |  |  |

|               |       |                  |     |                                         |     |     |       |  |  |

| U-0           | U-0   | U-0              | U-0 | R/C-0                                   | r-1 | U-0 | U-0   |  |  |

| —             | _     | —                | —   | IPL3 <sup>(1)</sup>                     | —   | _   | —     |  |  |

| bit 7         |       |                  |     |                                         |     |     | bit 0 |  |  |

|               |       |                  |     |                                         |     |     |       |  |  |

| Legend:       |       | C = Clearable    | bit | r = Reserved                            | bit |     |       |  |  |

| R = Readable  | e bit | W = Writable I   | oit | U = Unimplemented bit, read as '0'      |     |     |       |  |  |

| -n = Value at | POR   | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |     |       |  |  |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

bit 2 Reserved: Read as '1'

- bit 1-0 Unimplemented: Read as '0'

- **Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level; see Register 3-1 for bit description.

### TABLE 4-28: PERIPHERAL PIN SELECT REGISTER MAP (CONTINUED)

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|---------------|

| RPOR0        | 03D6 | _      | —      | RP1R5  | RP1R4  | RP1R3  | RP1R2  | RP1R1  | RP1R0  | _     | _     | RP0R5  | RP0R4  | RP0R3  | RP0R2  | RP0R1  | RP0R0  | 0000          |

| RPOR1        | 03D8 |        | —      | RP3R5  | RP3R4  | RP3R3  | RP3R2  | RP3R1  | RP3R0  |       | _     | RP2R5  | RP2R4  | RP2R3  | RP2R2  | RP2R1  | RP2R0  | 0000          |

| RPOR2        | 03DA |        | _      |        |        | RP5R   | <5:0>  |        |        |       | -     |        | _      |        | _      | _      | _      | 0000          |

| RPOR3        | 03DC | _      | —      | RP7R5  | RP7R4  | RP7R3  | RP7R2  | RP7R1  | RP7R0  |       | —     | RP6R5  | RP6R4  | RP6R3  | RP6R2  | RP6R1  | RP6R0  | 0000          |

| RPOR4        | 03DE |        | —      | RP9R5  | RP9R4  | RP9R3  | RP9R2  | RP9R1  | RP9R0  |       | _     | RP8R5  | RP8R4  | RP8R3  | RP8R2  | RP8R1  | RP8R0  | 0000          |

| RPOR5        | 03E0 |        |        | RP11R5 | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 | -     | Ι     | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 | 0000          |

| RPOR6        | 03E2 | _      | —      |        |        | RP13F  | <5:0>  |        |        |       | —     | _      | _      | _      | _      | _      | _      | 0000          |

| RPOR7        | 03E4 |        | —      | RP15R5 | RP15R4 | RP15R3 | RP15R2 | RP15R1 | RP15R0 |       | _     | RP14R5 | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 | 0000          |

| RPOR8        | 03E6 | _      | —      | RP17R5 | RP17R4 | RP17R3 | RP17R2 | RP17R1 | RP17R0 |       | _     | RP16R5 | RP16R4 | RP16R3 | RP16R2 | RP16R1 | RP16R0 | 0000          |

| RPOR9        | 03E8 | _      | —      | RP19R5 | RP19R4 | RP19R3 | RP19R2 | RP19R1 | RP19R0 |       | —     | RP18R5 | RP18R4 | RP18R3 | RP18R2 | RP18R1 | RP18R0 | 0000          |

| RPOR10       | 03EA | _      | _      | RP21R5 | RP21R4 | RP21R3 | RP21R2 | RP21R1 | RP21R0 |       | -     | RP20R5 | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 | 0000          |

| RPOR11       | 03EC |        | —      | RP23R5 | RP23R4 | RP23R3 | RP23R2 | RP23R1 | RP23R0 |       | _     | RP22R5 | RP22R4 | RP22R3 | RP22R2 | RP22R1 | RP22R0 | 0000          |

| RPOR12       | 03EE | _      | —      | RP25R5 | RP25R4 | RP25R3 | RP25R2 | RP25R1 | RP25R0 | —     | _     | RP24R5 | RP24R4 | RP24R3 | RP24R2 | RP24R1 | RP24R0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-29: SYSTEM CONTROL (CLOCK AND RESET) REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9  | Bit 8    | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|------------|--------|--------|----------|---------|--------|--------|-------|--------|--------|--------|--------|---------------|

| RCON         | 0108 | TRAPR  | IOPUWR |        | RETEN  | _          | DPSLP  | CM     | VREGS    | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP  | IDLE   | BOR    | POR    | Note 1        |

| OSCCON       | 0100 | _      | COSC2  | COSC1  | COSC0  |            | NOSC2  | NOSC1  | NOSC0    | CLKLOCK | IOLOCK | LOCK   | -     | CF     | POSCEN | SOSCEN | OSWEN  | Note 2        |

| CLKDIV       | 0102 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN      | RCDIV2 | RCDIV1 | RCDIV0   | CPDIV1  | CPDIV0 | PLLEN  | _     | _      | _      | _      | _      | 0100          |

| OSCTUN       | 0106 | STEN   | _      | STSIDL | STSRC  | STLOCK     | STLPOL | STOR   | STORPOL  | _       | _      | TUN5   | TUN4  | TUN3   | TUN2   | TUN1   | TUN0   | 0000          |

| REFOCONL     | 0168 | ROEN   | _      | ROSIDL | ROOUT  | ROSLP      | _      | ROSWEN | ROACTIVE | _       | _      | _      | _     | ROSEL3 | ROSEL2 | ROSEL1 | ROSEL0 | 0000          |

| REFOCONH     | 016A |        |        |        |        |            |        |        | RODIV    | <14:0>  |        |        |       |        |        |        |        | 0000          |

| REFOTRIML    | 016C |        |        |        | R      | DTRIM<15:7 | >      |        |          |         | _      | _      | _     | _      | _      | _      | _      | 0000          |

| HLVDCON      | 010C | HLVDEN | _      | LSIDL  | —      | —          | —      | _      | —        | VDIR    | BGVST  | IRVST  | _     | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 0000          |

| RCON2        | 010A | _      | —      | _      | _      | -          | _      | —      | —        | —       | _      | _      | r     | VDDBOR | VDDPOR | VBPOR  | VBAT   | Note 1        |

Legend: — = unimplemented, read as '0'; r = reserved bit. Reset values are shown in hexadecimal.

Note 1: The Reset value of the RCON register is dependent on the type of Reset event. For more information, refer to Section 7.0 "Resets".

2: The Reset value of the OSCCON register is dependent on both the type of Reset event and the device configuration. For more information, refer to Section 9.0 "Oscillator Configuration".

#### REGISTER 5-3: DMAINTn: DMA CHANNEL n INTERRUPT REGISTER

| R-0                     | U-0                                                | R/W-0                            | R/W-0                 | R/W-0                     | R/W-0           | R/W-0           | R/W-0               |

|-------------------------|----------------------------------------------------|----------------------------------|-----------------------|---------------------------|-----------------|-----------------|---------------------|

| DBUFWF <sup>(1)</sup>   |                                                    | CHSEL5                           | CHSEL4                | CHSEL3                    | CHSEL2          | CHSEL1          | CHSEL0              |

| bit 15                  |                                                    |                                  |                       |                           |                 |                 | bit 8               |

|                         |                                                    |                                  |                       |                           |                 |                 |                     |

| R/W-0                   | R/W-0                                              | R/W-0                            | R/W-0                 | R/W-0                     | U-0             | U-0             | R/W-0               |

| HIGHIF <sup>(1,2)</sup> | LOWIF <sup>(1,2)</sup>                             | DONEIF <sup>(1)</sup>            | HALFIF <sup>(1)</sup> | OVRUNIF <sup>(1)</sup>    | —               | —               | HALFEN              |

| bit 7                   |                                                    |                                  |                       |                           |                 |                 | bit (               |

| Legend:                 |                                                    |                                  |                       |                           |                 |                 |                     |

| R = Readable            | bit                                                | W = Writable I                   | nit                   | U = Unimplem              | ented hit read  | 1 as '0'        |                     |

| -n = Value at           |                                                    | '1' = Bit is set                 |                       | '0' = Bit is clea         |                 | x = Bit is unkr | nwn                 |

|                         |                                                    |                                  |                       |                           | licu            |                 |                     |

| bit 15                  | DBUEWE: DI                                         | MA Buffered Da                   | ta Write Flag I       | <sub>Dit</sub> (1)        |                 |                 |                     |

|                         |                                                    | tent of the DM/                  | •                     |                           | to the location | on specified in | DMADSTn o           |

|                         |                                                    | Cn in Null Write                 |                       |                           |                 |                 |                     |

|                         |                                                    | tent of the DN                   |                       | been written t            | the location    | n specified in  | DMADSTn o           |

|                         | _                                                  | Cn in Null Write                 |                       |                           |                 |                 |                     |

| bit 14                  | •                                                  | ited: Read as '0                 |                       |                           |                 |                 |                     |

| bit 13-8                |                                                    | : DMA Channe                     |                       | tion bits                 |                 |                 |                     |

|                         |                                                    | 1 for a complete                 |                       | <b>E 1 1 1 2</b>          |                 |                 |                     |

| bit 7                   |                                                    | A High Address                   |                       | -                         | bioboxthop F    |                 | un on lineit of the |

|                         | data RA                                            | A channel has a<br>M space       | liempled to ac        | cess an address           | s nigher than L | DIMAR of the up | per limit of the    |

|                         |                                                    | A channel has n                  | ot invoked the        | high address li           | mit interrupt   |                 |                     |

| bit 6                   | LOWIF: DMA                                         | A Low Address L                  | imit Interrupt        | Flag bit <sup>(1,2)</sup> |                 |                 |                     |

|                         |                                                    | A channel has a                  |                       |                           | R address low   | er than DMAL,   | but above the       |

|                         |                                                    | ge (07FFh)                       |                       |                           |                 |                 |                     |

|                         |                                                    | A channel has n                  |                       |                           | nit interrupt   |                 |                     |

| bit 5                   |                                                    | IA Complete Op                   | eration Interru       | ipt Flag bit              |                 |                 |                     |

|                         | $\frac{\text{If CHEN} = 1:}{1 = \text{The previ}}$ | ious DMA sessi                   | on has ended          | with completion           |                 |                 |                     |

|                         |                                                    | ent DMA session                  |                       |                           |                 |                 |                     |

|                         | If CHEN = 0:                                       |                                  |                       |                           |                 |                 |                     |

|                         | •                                                  | ious DMA sessi                   |                       | •                         |                 |                 |                     |

|                         | -                                                  | ious DMA sessi                   |                       |                           | ion             |                 |                     |

| bit 4                   |                                                    | A 50% Waterma                    |                       |                           |                 |                 |                     |

|                         |                                                    | n has reached f<br>has not reach |                       |                           |                 |                 |                     |

| bit 3                   |                                                    | MA Channel Ov                    |                       |                           |                 |                 |                     |

|                         |                                                    | channel is trigg                 | 0                     |                           | the operation   | based on the p  | revious triage      |

|                         |                                                    | run condition ha                 |                       |                           |                 |                 |                     |

| bit 2-1                 | Unimplemen                                         | nted: Read as 'o                 | )'                    |                           |                 |                 |                     |

| bit 0                   | HALFEN: Ha                                         | Ifway Completio                  | on Watermark          | bit                       |                 |                 |                     |

|                         |                                                    | are invoked wh                   |                       |                           |                 | t and at comple | etion               |

|                         | 0 = An interru                                     | upt is invoked or                | nly at the com        | oletion of the tra        | nsfer           |                 |                     |

| Note 1: Se              | tting these flag                                   | na in aaffwara da                | oo not gonor          | to on intervent           |                 |                 |                     |

|                         | ung those had                                      | i sollwale u                     |                       | ate an interrupt.         |                 |                 |                     |

2: Testing for address limit violations (DMASRCn or DMADSTn is either greater than DMAH or less than DMAL) is NOT done before the actual access.

| U-0          | U-0                                                                                                                                                                                                                | U-0                                    | U-0                         | U-0                   | U-0                     | U-0                    | U-0                 |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------|-----------------------|-------------------------|------------------------|---------------------|--|--|

|              | —                                                                                                                                                                                                                  | —                                      |                             | —                     | —                       | _                      |                     |  |  |

| bit 15       |                                                                                                                                                                                                                    |                                        |                             |                       |                         |                        | bit 8               |  |  |

|              |                                                                                                                                                                                                                    |                                        |                             |                       |                         |                        |                     |  |  |

| U-0          | U-0                                                                                                                                                                                                                | U-0                                    | r-0                         | R/CO-1                | R/CO-1                  | R/CO-1                 | R/CO-0              |  |  |

| —            | —                                                                                                                                                                                                                  | —                                      |                             | VDDBOR <sup>(1)</sup> | VDDPOR <sup>(1,2)</sup> | VBPOR <sup>(1,3)</sup> | VBAT <sup>(1)</sup> |  |  |

| bit 7        |                                                                                                                                                                                                                    |                                        |                             |                       |                         |                        | bit 0               |  |  |

| Legend:      |                                                                                                                                                                                                                    | CO = Clearabl                          | e Onlv bit                  | r = Reserved          | bit                     |                        |                     |  |  |

| R = Readab   | le bit                                                                                                                                                                                                             | W = Writable b                         | 5                           | U = Unimpler          | nented bit, read        | 1 as '0'               |                     |  |  |

| -n = Value a | t POR                                                                                                                                                                                                              | '1' = Bit is set                       |                             | '0' = Bit is cle      |                         | x = Bit is unkn        | own                 |  |  |

|              |                                                                                                                                                                                                                    |                                        |                             |                       |                         |                        |                     |  |  |

| bit 15-5     | Unimpleme                                                                                                                                                                                                          | nted: Read as '0                       | ,                           |                       |                         |                        |                     |  |  |

| bit 4        | Reserved: N                                                                                                                                                                                                        | <b>/aintain as</b> '0'                 |                             |                       |                         |                        |                     |  |  |

| bit 3        | VDDBOR: V                                                                                                                                                                                                          | DD Brown-out Re                        | eset Flag bit <sup>(1</sup> | )                     |                         |                        |                     |  |  |

|              |                                                                                                                                                                                                                    | rown-out Reset ł<br>rown-out Reset ł   |                             |                       | e)                      |                        |                     |  |  |

| bit 2        | VDDPOR: V                                                                                                                                                                                                          | DD Power-on Re                         | set Flag bit <sup>(1,</sup> | 2)                    |                         |                        |                     |  |  |

|              |                                                                                                                                                                                                                    | ower-on Reset h<br>ower-on Reset h     |                             |                       | e)                      |                        |                     |  |  |

| bit 1        | VBPOR: VB                                                                                                                                                                                                          | POR Flag bit <sup>(1,3)</sup>          |                             |                       |                         |                        |                     |  |  |

|              | <ul> <li>1 = A VBAT POR has occurred (no battery is connected to the VBAT pin or VBAT power below the Deep Sleep Semaphore retention level is set by hardware)</li> <li>0 = A VBAT POR has not occurred</li> </ul> |                                        |                             |                       |                         |                        |                     |  |  |

| bit 0        | <b>VBAT:</b> VBAT                                                                                                                                                                                                  | Flag bit <sup>(1)</sup>                |                             |                       |                         |                        |                     |  |  |

|              |                                                                                                                                                                                                                    | exit has occurred<br>exit from VBAT ha |                             |                       | the VBAT pin (se        | et by hardware)        |                     |  |  |

| Note 1: ⊺    | his bit is set in l                                                                                                                                                                                                | hardware onlv: it                      | can only be o               | cleared in softw      | are.                    |                        |                     |  |  |

### REGISTER 7-2: RCON2: RESET AND SYSTEM CONTROL REGISTER 2

- **Note 1:** This bit is set in hardware only; it can only be cleared in software.

- 2: This bit indicates a VDD Power-on Reset. Setting the POR bit (RCON<0>) indicates a VCORE Power-on Reset.

- 3: This bit is set when the device is originally powered up, even if power is present on VBAT.

| Flag Bit          | Setting Event                                     | Clearing Event                   |

|-------------------|---------------------------------------------------|----------------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                              |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                              |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                              |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                              |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                              |

| WDTO (RCON<4>)    | WDT Time-out                                      | CLRWDT, PWRSAV Instructions, POR |

| SLEEP (RCON<3>)   | PWRSAV #0 Instruction                             | POR                              |

| DPSLP (RCON<10>)  | PWRSAV #0 Instruction while DSEN bit is Set       | POR                              |

| IDLE (RCON<2>)    | PWRSAV #1 Instruction                             | POR                              |

| BOR (RCON<1>)     | POR, BOR                                          |                                  |

| POR (RCON<0>)     | POR                                               |                                  |

#### TABLE 7-1: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits may be set or cleared by the user software.

|               | R/W-1               | R/W-0                                     | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0     |

|---------------|---------------------|-------------------------------------------|------------------|------------------|------------------|-----------------|-----------|

| —             | U1RXIP2             | U1RXIP1                                   | U1RXIP0          | _                | SPI1TXIP2        | SPI1TXIP1       | SPI1TXIP0 |

| bit 15        |                     |                                           |                  |                  |                  |                 | bit       |

|               |                     |                                           |                  |                  |                  |                 |           |

| U-0           | R/W-1               | R/W-0                                     | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0     |

|               | SPI1IP2             | SPI1IP1                                   | SPI1IP0          | —                | T3IP2            | T3IP1           | T3IP0     |

| bit 7         |                     |                                           |                  |                  |                  |                 | bit (     |

| Legend:       |                     |                                           |                  |                  |                  |                 |           |

| R = Readabl   | e bit               | W = Writable                              | bit              | U = Unimple      | mented bit, read | l as '0'        |           |

| -n = Value at | POR                 | '1' = Bit is set                          |                  | ʻ0' = Bit is cle | eared            | x = Bit is unkr | nown      |

| bit 15        | Unimplomon          | ted: Read as '                            | ۰ <b>،</b>       |                  |                  |                 |           |

| bit 14-12     | -                   | : UART1 Rece                              |                  | Priority hits    |                  |                 |           |

| 51(1412       |                     | ot is Priority 7 (                        | -                | -                |                  |                 |           |

|               | •                   | , , ,                                     | 5 , ,            | 1 /              |                  |                 |           |

|               | •                   |                                           |                  |                  |                  |                 |           |

|               | •<br>001 = Interrug | ot is Priority 1                          |                  |                  |                  |                 |           |

|               |                     | ot source is dis                          | abled            |                  |                  |                 |           |

| bit 11        | Unimplement         | ted: Read as '                            | ) <b>'</b>       |                  |                  |                 |           |

| bit 10-8      | SPI1TXIP<2:0        | 0>: SPI1 Trans                            | mit Interrupt P  | riority bits     |                  |                 |           |

|               | 111 = Interrup      | ot is Priority 7 (                        | highest priority | interrupt)       |                  |                 |           |

|               | •                   |                                           |                  |                  |                  |                 |           |

|               | •                   |                                           |                  |                  |                  |                 |           |

|               | 001 = Interrup      | ot is Priority 1<br>ot source is dis      | abled            |                  |                  |                 |           |

| bit 7         |                     | ted: Read as '                            |                  |                  |                  |                 |           |

| bit 6-4       | -                   | SPI1 General                              |                  | itv bits         |                  |                 |           |

|               |                     | ot is Priority 7 (                        | •                | •                |                  |                 |           |

|               | •                   |                                           |                  | • •              |                  |                 |           |

|               | •                   |                                           |                  |                  |                  |                 |           |

|               | 001 = Interrup      |                                           | ablad            |                  |                  |                 |           |

| bit 3         | -                   | ot source is dis<br><b>ted:</b> Read as ' |                  |                  |                  |                 |           |

| bit 2-0       | -                   | imer3 Interrupt                           |                  |                  |                  |                 |           |

| 011 Z-0       |                     | ot is Priority 7 (                        | -                | (interrunt)      |                  |                 |           |

|               | •                   |                                           | gilloot priority |                  |                  |                 |           |

|               | •                   |                                           |                  |                  |                  |                 |           |

|               |                     |                                           |                  |                  |                  |                 |           |

|               | •<br>001 = Interrup | ot is Priority 1                          |                  |                  |                  |                 |           |

### REGISTER 8-23: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| R/W-0        | U-0           | R/W-0                                       | R/W-0                | R-0               | R/W-0            | R-0            | R/W-0   |

|--------------|---------------|---------------------------------------------|----------------------|-------------------|------------------|----------------|---------|

| STEN         |               | STSIDL                                      | STSRC <sup>(1)</sup> | STLOCK            | STLPOL           | STOR           | STORPOL |

| bit 15       |               |                                             |                      |                   |                  |                | bit     |

| U-0          | U-0           | R/W-0                                       | R/W-0                | R/W-0             | R/W-0            | R/W-0          | R/W-0   |

| _            | _             | TUN5                                        | TUN4                 | TUN3              | TUN2             | TUN1           | TUN0    |

| bit 7        |               | ·                                           |                      |                   |                  |                | bit (   |

| Legend:      |               |                                             |                      |                   |                  |                |         |

| R = Readab   | le bit        | W = Writable                                | bit                  | U = Unimplem      | nented bit, read | as '0'         |         |

| -n = Value a | t POR         | '1' = Bit is set                            |                      | '0' = Bit is clea | ared             | x = Bit is unk | nown    |

| bit 15       | STEN: FRC     | Self-Tune Enab                              | le bit               |                   |                  |                |         |

|              |               | f-tuning is enabl                           |                      |                   | •                | hito           |         |

| bit 14       |               | f-tuning is disab<br><b>nted:</b> Read as ' |                      | may optionally    |                  | DIIS           |         |

| bit 13       | -             | C Self-Tune Sto                             |                      |                   |                  |                |         |

| bit 10       | 1 = Self-tuni | ng stops during                             | Idle mode            |                   |                  |                |         |

| bit 12       |               | ng continues du<br>C Self-Tune Ref          | -                    | ource hit(1)      |                  |                |         |

|              |               | uned to approxi                             |                      |                   | ock tolerance    |                |         |

|              |               | uned to approxi                             |                      |                   |                  | e              |         |

| bit 11       | STLOCK: FI    | RC Self-Tune Lo                             | ock Status bit       |                   |                  |                |         |

|              |               | curacy is current<br>curacy may not l       | •                    |                   |                  | •              |         |

| bit 10       | STLPOL: FF    | RC Self-Tune Lo                             | ock Interrupt Po     | larity bit        |                  | -              |         |

|              |               | ne lock interrup<br>ne lock interrup        |                      |                   |                  |                |         |

| bit 9        |               | Self-Tune Out                               | -                    |                   |                  |                |         |

|              |               | reference clock<br>reference clock          |                      |                   |                  |                | med     |

| bit 8        |               | FRC Self-Tune                               |                      | •                 | •                |                |         |

|              | 1 = A self-tu | ne out of range<br>ne out of range          | interrupt is gen     | erated when S     | TOR is = 0       |                |         |

| bit 7-6      |               | nted: Read as '                             |                      |                   |                  |                |         |

| bit 5-0      | -             | FRC Oscillator 1                            |                      |                   |                  |                |         |

|              |               | laximum freque                              | -                    |                   |                  |                |         |

|              | •             |                                             |                      |                   |                  |                |         |

|              | •             |                                             |                      |                   |                  |                |         |

|              | •<br>000001 = |                                             |                      |                   |                  |                |         |

|              |               | enter frequency                             | , oscillator is ru   | nning at factory  | calibrated free  | quency         |         |

|              | •             |                                             |                      |                   |                  |                |         |

|              | •             |                                             |                      |                   |                  |                |         |

|              | •<br>100001 = |                                             |                      |                   |                  |                |         |

|              | T0000T -      | linimum frequen                             |                      |                   |                  |                |         |

### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

Note 1: Use of either clock recovery source has specific application requirements. For more information, see Section 9.5 "FRC Self-Tuning".

NOTES:

### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

| R/W-0        | R/W-0                            | R/W-0                               | R/W-0                        | U-0               | R/W-0               | R/W-0               | R/W-0         |

|--------------|----------------------------------|-------------------------------------|------------------------------|-------------------|---------------------|---------------------|---------------|

| FLTMD        | FLTOUT                           | FLTTRIEN                            | OCINV                        | —                 | DCB1 <sup>(3)</sup> | DCB0 <sup>(3)</sup> | OC32          |

| bit 15       |                                  |                                     | •                            | •                 | •                   | •                   | bit 8         |

|              |                                  |                                     |                              |                   |                     |                     |               |

| R/W-0        | R/W-0, HS                        | R/W-0                               | R/W-0                        | R/W-1             | R/W-1               | R/W-0               | R/W-0         |

| OCTRIG       | TRIGSTAT                         | OCTRIS                              | SYNCSEL4                     | SYNCSEL3          | SYNCSEL2            | SYNCSEL1            | SYNCSEL0      |

| bit 7        |                                  |                                     |                              |                   |                     |                     | bit (         |

|              |                                  |                                     |                              |                   |                     |                     |               |

| Legend:      |                                  | HS = Hardwa                         | re Settable bit              |                   |                     |                     |               |

| R = Readal   | ble bit                          | W = Writable                        | bit                          | U = Unimplen      | nented bit, read    | d as '0'            |               |

| -n = Value a | at POR                           | '1' = Bit is set                    |                              | '0' = Bit is clea | ared                | x = Bit is unkn     | nown          |

|              |                                  |                                     |                              |                   |                     |                     |               |

| bit 15       | FLTMD: Faul                      | t Mode Select I                     | oit                          |                   |                     |                     |               |

|              |                                  |                                     | ed until the Fau             | It source is ren  | noved and the       | corresponding       | OCFLT0 bit i  |

|              |                                  | n software<br>de is maintaine       | d until the Faul             | lt source is rem  | oved and a ne       | w PWM period        | etarte        |

| bit 14       | FLTOUT: Fau                      |                                     |                              |                   |                     |                     | 510/15        |

|              |                                  | put is driven hig                   | oh on a Fault                |                   |                     |                     |               |

|              |                                  | put is driven lov                   |                              |                   |                     |                     |               |

| bit 13       | FLTTRIEN: F                      | ault Output Sta                     | te Select bit                |                   |                     |                     |               |

|              |                                  |                                     | t on a Fault cor             |                   |                     |                     |               |

|              |                                  |                                     | ected by a Fau               | llt               |                     |                     |               |

| bit 12       |                                  | ut Compare x I                      | nvert bit                    |                   |                     |                     |               |

|              | 1 = OCx outp                     | ut is inverted<br>ut is not inverte | d                            |                   |                     |                     |               |

| bit 11       | •                                | ted: Read as '                      |                              |                   |                     |                     |               |

| bit 10-9     | •                                |                                     | e Least Signific             | ant hite(3)       |                     |                     |               |

| DIL 10-9     |                                  |                                     | e by $\frac{3}{4}$ of the ir |                   | <b>`</b>            |                     |               |

|              |                                  |                                     | e by $\frac{1}{2}$ of the ir |                   |                     |                     |               |

|              |                                  |                                     | e by ¼ of the in             |                   |                     |                     |               |

|              |                                  |                                     | s at the start of            |                   | -                   |                     |               |

| bit 8        |                                  |                                     | odules Enable b              | oit (32-bit opera | ation)              |                     |               |

|              |                                  | module operati<br>module operati    |                              |                   |                     |                     |               |

| bit 7        |                                  | -                                   | Trigger/Sync S               | Select hit        |                     |                     |               |

|              |                                  |                                     | ource designate              |                   | CSELx bits          |                     |               |

|              |                                  |                                     | the source desi              |                   |                     | s                   |               |

| bit 6        | TRIGSTAT: ⊺                      | imer Trigger St                     | atus bit                     |                   |                     |                     |               |

|              |                                  |                                     | riggered and is              | •                 |                     |                     |               |

|              |                                  |                                     | en triggered an              | -                 |                     |                     |               |

| bit 5        |                                  |                                     | Output Pin Dir               | ection Select b   | vit                 |                     |               |

|              | 1 = OCx pin is<br>0 = Output Co  |                                     | eral x is connec             | ted to an OCx     | pin                 |                     |               |

|              | Never use an OC                  | x module as its                     |                              |                   | -                   | mode or anothe      | er equivalent |

|              | SYNCSELx settir Use these inputs | -                                   | ces only and n               | aver se evine or  |                     |                     |               |

| 2:           |                                  | as ingger sour                      | Ces only and the             | ever as sync st   |                     |                     |               |

3: The DCB<1:0> bits are double-buffered in PWM modes only (OCM<2:0> (OCxCON1<2:0>) = 111, 110).

## 16.3 Enhanced Slave Mode

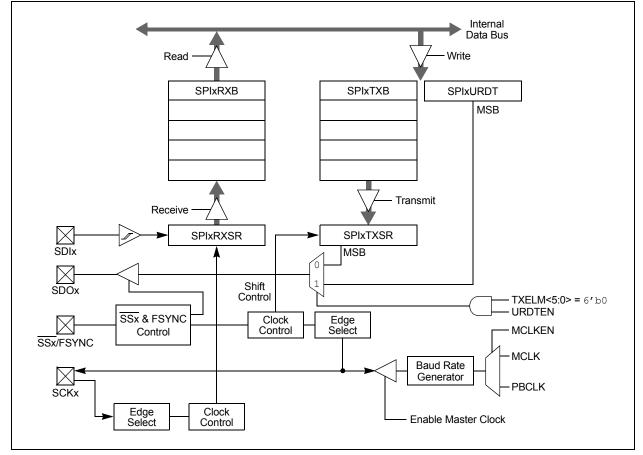

To set up the SPIx module for the Enhanced Buffer Master mode of operation:

- 1. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP<2:0> bits in the respective IPCx register.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with MSTEN (SPIxCON1L<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTATL<6>).

- 4. Select Enhanced Buffer mode by setting the ENHBUF bit (SPIxCON1L<0>).

- Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 6. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

### 16.4 Enhanced Master Mode

To set up the SPIx module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP<2:0> bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with the MSTEN bit (SPIxCON1L<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- 7. Select Enhanced Buffer mode by setting the ENHBUF bit (SPIxCON1L<0>).

- 8. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

© 2013-2015 Microchip Technology Inc.

## REGISTER 18-5: UxSCCON: UARTx SMART CARD CONTROL REGISTER<sup>(1)</sup>

| U-0          | U-0                                                       | U-0                                  | U-0                   | U-0                         | U-0                 | U-0             | U-0   |

|--------------|-----------------------------------------------------------|--------------------------------------|-----------------------|-----------------------------|---------------------|-----------------|-------|

| —            | _                                                         | _                                    | —                     | —                           | —                   | —               | —     |

| bit 15       | 5                                                         |                                      |                       |                             |                     |                 |       |

|              |                                                           |                                      |                       |                             |                     |                 |       |

| U-0          | U-0                                                       | R/W-0                                | R/W-0                 | R/W-0                       | R/W-0               | R/W-0           | R/W-0 |

|              | —                                                         | TXRPT1 <sup>(2)</sup>                | TXRPT0 <sup>(2)</sup> | CONV                        | T0PD <sup>(2)</sup> | PTRCL           | SCEN  |

| bit 7        |                                                           |                                      |                       |                             |                     |                 | bit 0 |

| Legend:      |                                                           |                                      |                       |                             |                     |                 |       |

| R = Readat   | ole bit                                                   | W = Writable                         | oit                   | U = Unimplem                | nented bit, read    | l as '0'        |       |

| -n = Value a | at POR                                                    | '1' = Bit is set                     |                       | '0' = Bit is clea           |                     | x = Bit is unkn | own   |

|              |                                                           |                                      |                       |                             |                     |                 |       |

| bit 15-6     | Unimplemen                                                | ted: Read as '                       | )'                    |                             |                     |                 |       |

| bit 5-4      | TXRPT<1:0>                                                | : Transmit Rep                       | eat Selection b       | its <sup>(2)</sup>          |                     |                 |       |

|              | 11 = Retrans                                              | mits the error b                     | yte four times        |                             |                     |                 |       |

|              |                                                           | mits the error b                     |                       | i                           |                     |                 |       |

|              |                                                           | mits the error b<br>mits the error b |                       |                             |                     |                 |       |

| bit 3        |                                                           | Convention Se                        |                       |                             |                     |                 |       |

| DILS         | •                                                         | gic convention                       |                       |                             |                     |                 |       |

|              | 0 = Direct log                                            | •                                    |                       |                             |                     |                 |       |

| bit 2        | -                                                         | own Duration fo                      | or T = 0 Error H      | landling bit <sup>(2)</sup> |                     |                 |       |

|              | 1 = 2 ETU                                                 |                                      |                       | 5                           |                     |                 |       |

|              | 0 = 1 ETU                                                 |                                      |                       |                             |                     |                 |       |

| bit 1        | PTRCL: Sma                                                | rt Card Protoco                      | I Selection bit       |                             |                     |                 |       |

|              | 1 <b>= T =</b> 1                                          |                                      |                       |                             |                     |                 |       |

|              | 0 = T = 0                                                 |                                      |                       |                             |                     |                 |       |

| bit 0        | SCEN: Smart Card Mode Enable bit                          |                                      |                       |                             |                     |                 |       |

|              | 1 = Smart Card mode is enabled if UARTEN (UxMODE<15>) = 1 |                                      |                       |                             |                     |                 |       |

|              | 0 = Smart Ca                                              | rd mode is disa                      | DIEG                  |                             |                     |                 |       |

| Note 1: 1    | This register is or                                       | nly available for                    | UART1 and U           | ART2.                       |                     |                 |       |

| <b>2:</b> 7  | These bits are ap                                         | plicable to T =                      | 0 only, see PTI       | RCL (UxSCCO                 | N<1>).              |                 |       |

#### 19.7.1 USB OTG MODULE CONTROL REGISTERS

## REGISTER 19-3: U10TGSTAT: USB OTG STATUS REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   |     | -   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| R-0, HSC | U-0 | R-0, HSC | U-0 | R-0, HSC | R-0, HSC | U-0 | R-0, HSC |

|----------|-----|----------|-----|----------|----------|-----|----------|

| ID       | —   | LSTATE   | —   | SESVD    | SESEND   | —   | VBUSVD   |

| bit 7    |     |          |     |          |          |     | bit 0    |

| Legend:           | U = Unimplemented bit, read as '0' |                                       |                    |  |  |  |

|-------------------|------------------------------------|---------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                   | HSC = Hardware Settable/Clearable bit |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                   |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | ID: ID Pin State Indicator bit                                                                                                                                                               |

|          | <ul> <li>1 = No plug is attached or a Type B cable has been plugged into the USB receptacle</li> <li>0 = A Type A plug has been plugged into the USB receptacle</li> </ul>                   |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                   |

| bit 5    | LSTATE: Line State Stable Indicator bit                                                                                                                                                      |

|          | <ul> <li>1 = The USB line state (as defined by SE0 and JSTATE) has been stable for the previous 1 ms</li> <li>0 = The USB line state has not been stable for the previous 1 ms</li> </ul>    |

| bit 4    | Unimplemented: Read as '0'                                                                                                                                                                   |

| bit 3    | SESVD: Session Valid Indicator bit                                                                                                                                                           |

|          | <ul> <li>1 = The VBUS voltage is above VA_SESS_VLD (as defined in the "USB 2.0 Specification") on the A or<br/>B-device</li> </ul>                                                           |

|          | 0 = The VBUS voltage is below VA_SESS_VLD on the A or B-device                                                                                                                               |

| bit 2    | SESEND: B Session End Indicator bit                                                                                                                                                          |

|          | <ul> <li>1 = The VBUS voltage is below VB_SESS_END (as defined in the "USB 2.0 Specification") on the B-device</li> <li>0 = The VBUS voltage is above VB_SESS_END on the B-device</li> </ul> |

| bit 1    | Unimplemented: Read as '0'                                                                                                                                                                   |

| bit 0    | VBUSVD: A VBUS Valid Indicator bit                                                                                                                                                           |

|          | <ul> <li>1 = The VBUS voltage is above VA_VBUS_VLD (as defined in the "USB 2.0 Specification") on the A-device</li> <li>0 = The VBUS voltage is below VA_VBUS_VLD on the A-device</li> </ul> |

|          |                                                                                                                                                                                              |

### REGISTER 21-5: PMCSxCF: EPMP CHIP SELECT x CONFIGURATION REGISTER

| R/W-0        | R/W-0          | R/W-0                                  | R/W-0              | U-0              | R/W-0            | R/W-0           | R/W-0 |

|--------------|----------------|----------------------------------------|--------------------|------------------|------------------|-----------------|-------|

| CSDIS        | CSP            | CSPTEN                                 | BEP                | —                | WRSP             | RDSP            | SM    |

| bit 15       |                |                                        |                    | -                | •                | •               | bit 8 |

|              |                |                                        |                    |                  |                  |                 |       |

| R/W-0        | R/W-0          | R/W-0                                  | U-0                | U-0              | U-0              | U-0             | U-0   |

| ACKP         | PTSZ1          | PTSZ0                                  | <u> </u>           |                  |                  |                 | _     |

| bit 7        |                |                                        |                    |                  |                  |                 | bit ( |

| Legend:      |                |                                        |                    |                  |                  |                 |       |

| R = Readat   | ole bit        | W = Writable                           | bit                | U = Unimpler     | nented bit, read | t as '0'        |       |

| -n = Value a |                | '1' = Bit is set                       |                    | '0' = Bit is cle |                  | x = Bit is unkr | lown  |

|              |                |                                        |                    |                  |                  |                 |       |

| bit 15       | CSDIS: Chip    | Select x Disab                         | le bit             |                  |                  |                 |       |