# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                    |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT       |

| Number of I/O              | 20                                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

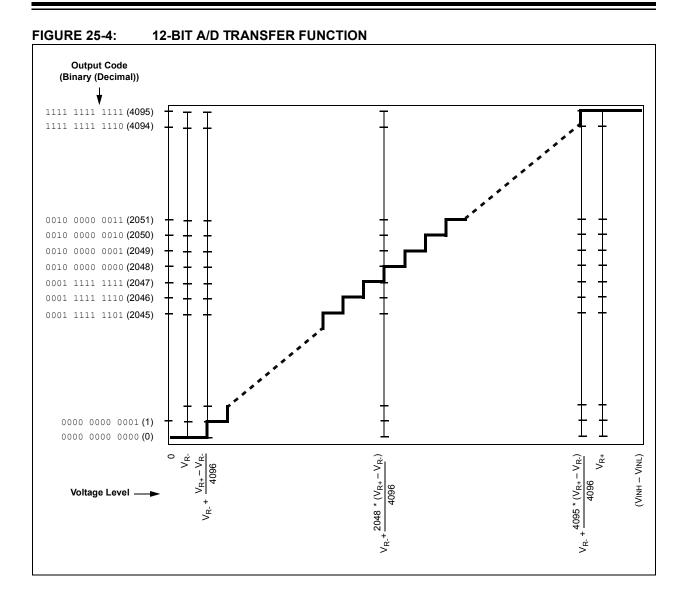

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb202-e-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

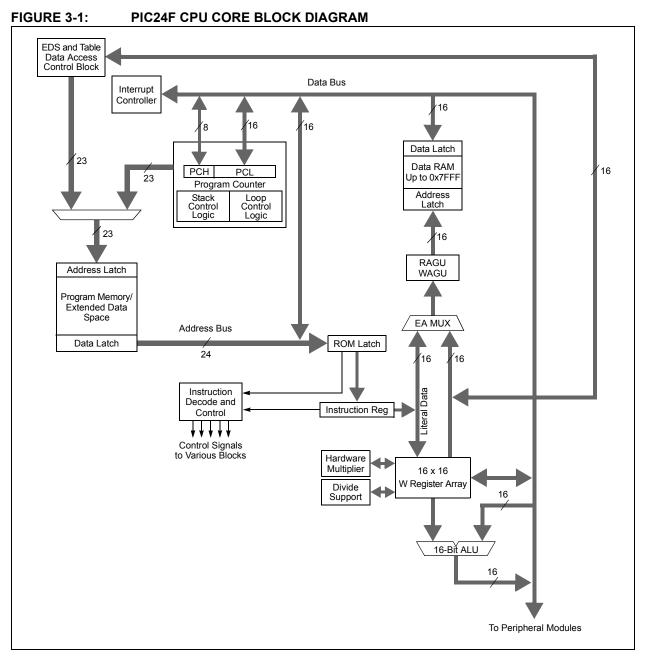

| TABLE 3-1:CPU CORE REGISTERS |

|------------------------------|

|------------------------------|

| Register(s) Name | Description                        |  |  |  |  |  |  |

|------------------|------------------------------------|--|--|--|--|--|--|

| W0 through W15   | Working Register Array             |  |  |  |  |  |  |

| PC               | 23-Bit Program Counter             |  |  |  |  |  |  |

| SR               | ALU STATUS Register                |  |  |  |  |  |  |

| SPLIM            | Stack Pointer Limit Value Register |  |  |  |  |  |  |

| TBLPAG           | Table Memory Page Address Register |  |  |  |  |  |  |

| RCOUNT           | REPEAT Loop Counter Register       |  |  |  |  |  |  |

| CORCON           | CPU Control Register               |  |  |  |  |  |  |

| DISICNT          | Disable Interrupt Count Register   |  |  |  |  |  |  |

| DSRPAG           | Data Space Read Page Register      |  |  |  |  |  |  |

| DSWPAG           | Data Space Write Page Register     |  |  |  |  |  |  |

### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP (CONTINUED)

| File<br>Name | Addr | Bit 15 | Bit 14    | Bit 13    | Bit 12    | Bit 11 | Bit 10  | Bit 9      | Bit 8   | Bit 7   | Bit 6     | Bit 5       | Bit 4     | Bit 3   | Bit 2     | Bit 1       | Bit 0     | All<br>Resets |

|--------------|------|--------|-----------|-----------|-----------|--------|---------|------------|---------|---------|-----------|-------------|-----------|---------|-----------|-------------|-----------|---------------|

| IPC16        | 00C4 | _      | CRCIP2    | CRCIP1    | CRCIP0    | _      | U2ERIP2 | U2ERIP1    | U2ERIP0 | _       | U1ERIP2   | U1ERIP1     | U1ERIP0   | _       | _         | _           | _         | 4440          |

| IPC18        | 00C8 | _      | _         | _         | _         | _      | _       | _          | _       | _       |           | _           | _         | _       | I         | HLVDIP<2:0> |           | 0004          |

| IPC19        | 00CA | _      | _         | _         | _         | _      | _       | _          | _       | _       | (         | CTMUIP<2:0  | >         | _       | _         | _           | _         | 0040          |

| IPC20        | 00CC | _      | U3TXIP2   | U3TXIP1   | U3TXIP0   | _      | U3RXIP2 | U3RXIP1    | U3RXIP0 | _       | U3ERIP2   | U3ERIP1     | U3ERIP0   | _       | _         | _           | _         | 4440          |

| IPC21        | 00CE | _      | U4ERIP2   | U4ERIP1   | U4ERIP0   | _      | USB1IP2 | USB1IP1    | USB1IP0 | _       | I2C2BCIP2 | I2C2BCIP1   | I2C2BCIP0 | _       | I2C1BCIP2 | I2C1BCIP1   | I2C1BCIP0 | 4444          |

| IPC22        | 00D0 | _      | SPI3TXIP2 | SPI3TXIP1 | SPI3TXIP0 | _      | SPI3IP2 | SPI3IP1    | SPI3IP0 | _       | U4TXIP2   | U4TXIP1     | U4TXIP0   | _       | U4RXIP2   | U4RXIP1     | U4RXIP0   | 4444          |

| IPC26        | 00D8 | _      | _         | _         | _         | _      |         | FSTIP<2:0> |         | _       |           | _           | _         | _       | _         | _           | _         | 0400          |

| IPC29        | 00DE | _      | _         | _         | _         | _      | _       | _          | _       | _       |           | JTAGIP<2:0> | >         | _       | _         | _           | _         | 0040          |

| INTTREG      | 00E0 | CPUIRQ | r         | VHOLD     | —         | ILR3   | ILR2    | ILR1       | ILR0    | VECNUM7 | VECNUM6   | VECNUM5     | VECNUM4   | VECNUM3 | VECNUM2   | VECNUM1     | VECNUM0   | 0000          |

Legend: — = unimplemented, read as '0'; r = reserved bit, maintain as '0'. Reset values are shown in hexadecimal.

| TABI F 4-27 <sup>.</sup> | <b>CRC REGISTER MAP</b> |

|--------------------------|-------------------------|

| ADLL = -21.              |                         |

| © 20        | TABLE 4-2    | 27:  | CRC RE | GISTE  | R MAP  |         |         |         |         |             |   |

|-------------|--------------|------|--------|--------|--------|---------|---------|---------|---------|-------------|---|

| 2013-2015   | File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8       |   |

| 5 Microchin | CRCCON1      | 0158 | CRCEN  |        | CSIDL  | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0      | - |

|             | CRCCON2      | 015A | _      | _      | _      | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0     | 1 |

|             | CRCXORL      | 015C |        |        |        |         |         |         |         | X<15:1>     |   |

|             | CRCXORH      | 015E |        |        |        |         |         |         |         | X<31:       | 1 |

|             | CRCDATL      | 0160 |        |        |        |         |         |         | CRC     | Data Input  | F |

|             | CRCDATH      | 0162 |        |        |        |         |         |         | CRC     | Data Input  | F |

|             | CRCWDATL     | 0164 |        |        |        |         |         |         | CF      | RC Result R | e |

|             | CRCWDATH     | 0166 |        |        |        |         |         |         | CF      | RC Result R | e |

|             |              |      |        |        |        |         |         |         |         |             |   |

Legend: — = unimplemented, read as '0'; x = unknown value on Reset. Reset values are shown in hexadecimal.

### TABLE 4-28: PERIPHERAL PIN SELECT REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12     | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7 | Bit 6 | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     | All<br>Resets |

|--------------|------|--------|--------|-----------|------------|-----------|-----------|-----------|-----------|-------|-------|-----------|-----------|-----------|-----------|-----------|-----------|---------------|

| RPINR0       | 038C | _      | _      | INT1R5    | INT1R4     | INT1R3    | INT1R2    | INT1R1    | INT1R0    | _     | _     | OCTRIG1R5 | OCTRIG1R4 | OCTRIG1R3 | OCTRIG1R2 | OCTRIG1R1 | OCTRIG1R0 | 3F3F          |

| RPINR1       | 038E | -      | -      | INT3R5    | INT3R4     | INT3R3    | INT3R2    | INT3R1    | INT3R0    | _     | _     | INT2R5    | INT2R4    | INT2R3    | INT2R2    | INT2R1    | INT2R0    | 3F3F          |

| RPINR2       | 0390 | -      | -      | OCTRIG2R5 | OCTRIG2R4  | OCTRIG2R3 | OCTRIG2R2 | OCTRIG2R1 | OCTRIG2R0 | _     | _     | INT4R5    | INT4R4    | INT4R3    | INT4R2    | INT4R1    | INT4R0    | 3F3F          |

| RPINR7       | 039A | _      | _      | IC2R5     | IC2R4      | IC2R3     | IC2R2     | IC2R1     | IC2R0     | _     | _     | IC1R5     | IC1R4     | IC1R3     | IC1R2     | IC1R1     | IC1R0     | 3F3F          |

| RPINR8       | 039C | —      | _      | IC4R5     | IC4R4      | IC4R3     | IC4R2     | IC4R1     | IC4R0     | _     | _     | IC3R5     | IC3R4     | IC3R3     | IC3R2     | IC3R1     | IC3R0     | 3F3F          |

| RPINR9       | 039E | _      | _      | IC6R5     | IC6R4      | IC6R3     | IC6R2     | IC6R1     | IC6R0     | _     | _     | IC5R5     | IC5R4     | IC5R3     | IC5R2     | IC5R1     | IC5R0     | 3F3F          |

| RPINR11      | 03A2 | —      | _      | OCFBR5    | OCFBR4     | OCFBR3    | OCFBR2    | OCFBR1    | OCFBR0    | —     | —     | OCFAR5    | OCFAR4    | OCFAR3    | OCFAR2    | OCFAR1    | OCFAR0    | 3F3F          |

| RPINR17      | 03AE | —      | —      |           | U3RXR<5:0> |           |           |           |           | _     | —     | _         | _         | _         | -         | _         | _         | 3F00          |

| RPINR18      | 03B0 | _      | _      | U1CTSR5   | U1CTSR4    | U1CTSR3   | U1CTSR2   | U1CTSR1   | U1CTSR0   | _     | _     | U1RXR5    | U1RXR4    | U1RXR3    | U1RXR2    | U1RXR1    | U1RXR0    | 3F3F          |

| RPINR19      | 03B2 | —      | _      | U2CTSR5   | U2CTSR4    | U2CTSR3   | U2CTSR2   | U2CTSR1   | U2CTSR0   | —     | —     | U2RXR5    | U2RXR4    | U2RXR3    | U2RXR2    | U2RXR1    | U2RXR0    | 3F3F          |

| RPINR20      | 03B4 | —      | —      | SCK1R5    | SCK1R4     | SCK1R3    | SCK1R2    | SCK1R1    | SCK1R0    | —     |       | SDI1R5    | SDI1R4    | SDI1R3    | SDI1R2    | SDI1R1    | SDI1R0    | 3F3F          |

| RPINR21      | 03B6 | _      | _      | U3CTSR5   | U3CTSR4    | U3CTSR3   | U3CTSR2   | U3CTSR1   | U3CTSR0   | _     | _     | SS1R5     | SS1R4     | SS1R3     | SS1R2     | SS1R1     | SS1R0     | 3F3F          |

| RPINR22      | 03B8 | —      | _      | SCK2R5    | SCK2R4     | SCK2R3    | SCK2R2    | SCK2R1    | SCK2R0    | —     | —     | SDI2R5    | SDI2R4    | SDI2R3    | SDI2R2    | SDI2R1    | SDI2R0    | 3F3F          |

| RPINR23      | 03BA | —      | —      | TMRCKR5   | TMRCKR4    | TMRCKR3   | TMRCKR2   | TMRCKR1   | TMRCKR0   | —     |       | SS2R5     | SS2R4     | SS2R3     | SS2R2     | SS2R1     | SS2R0     | 3F3F          |

| RPINR27      | 03C2 | _      | _      | U4CTSR5   | U4CTSR4    | U4CTSR3   | U4CTSR2   | U4CTSR1   | U4CTSR0   | _     | _     | U4RXR5    | U4RXR4    | U4RXR3    | U4RXR2    | U4RXR1    | U4RXR0    | 3F3F          |

| RPINR28      | 03C4 | _      | _      | SCK3R5    | SCK3R4     | SCK3R3    | SCK3R2    | SCK3R1    | SCK3R0    | _     | -     | SDI3R5    | SDI3R4    | SDI3R3    | SDI3R2    | SDI3R1    | SDI3R0    | 3F3F          |

| RPINR29      | 03C6 | _      | _      | _         | _          | _         | _         | _         | _         | _     |       |           |           | SS3R      | <5:0>     |           |           | 003F          |

| RPINR30      | 03C8 | _      | _      | _         | _          | _         | _         | _         | _         | _     | -     |           |           | MDMIF     | <5:0>     |           |           | 003F          |

| RPINR31      | 03CA | _      |        | MDC2R5    | MDC2R4     | MDC2R3    | MDC2R2    | MDC2R1    | MDC2R0    | _     | -     | MDC1R5    | MDC1R4    | MDC1R3    | MDC1R2    | MDC1R1    | MDC1R0    | 3F3F          |

X<31:16>

CRC Data Input Register Low

CRC Data Input Register High

CRC Result Register Low

CRC Result Register High

Bit 7

CRCFUL

\_

Bit 6

CRCMPT

Bit 5

CRCISEL

\_

Bit 4

CRCGO

PLEN4

Bit 3

LENDIAN

PLEN3

Bit 2

\_

PLEN2

Bit 1

\_

PLEN1

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All

Resets

0040

0000

0000

0000

XXXX

XXXX

XXXX

XXXX

Bit 0

\_

PLEN0

\_

### REGISTER 8-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

- bit 2 OC1IF: Output Compare Channel 1 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 1 IC1IF: Input Capture Channel 1 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 INTOIF: External Interrupt 0 Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

|               | R/W-1                                                                                                                          | R/W-0                                      | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0     |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------|------------------|------------------|-----------------|-----------|--|--|--|--|--|--|

| —             | U1RXIP2                                                                                                                        | U1RXIP1                                    | U1RXIP0          | _                | SPI1TXIP2        | SPI1TXIP1       | SPI1TXIP0 |  |  |  |  |  |  |

| bit 15        |                                                                                                                                |                                            |                  |                  |                  |                 | bit       |  |  |  |  |  |  |

|               |                                                                                                                                |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

| U-0           | R/W-1                                                                                                                          | R/W-0                                      | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0     |  |  |  |  |  |  |

|               | SPI1IP2                                                                                                                        | SPI1IP1                                    | SPI1IP0          | —                | T3IP2            | T3IP1           | T3IP0     |  |  |  |  |  |  |

| bit 7         |                                                                                                                                |                                            |                  |                  |                  |                 | bit (     |  |  |  |  |  |  |

| Legend:       |                                                                                                                                |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                                          | W = Writable                               | bit              | U = Unimple      | mented bit, read | l as '0'        |           |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                            | '1' = Bit is set                           |                  | ʻ0' = Bit is cle | eared            | x = Bit is unkr | nown      |  |  |  |  |  |  |

| bit 15        | Unimplomon                                                                                                                     | ted: Read as '                             | ۰ <b>،</b>       |                  |                  |                 |           |  |  |  |  |  |  |

| bit 14-12     | -                                                                                                                              |                                            |                  | Priority hits    |                  |                 |           |  |  |  |  |  |  |

| 51(1412       | <b>U1RXIP&lt;2:0&gt;:</b> UART1 Receiver Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               | •                                                                                                                              | , , ,                                      | 5 , ,            | 1 /              |                  |                 |           |  |  |  |  |  |  |

|               | •                                                                                                                              |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               | •<br>001 = Interrug                                                                                                            | ot is Priority 1                           |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               |                                                                                                                                | ot source is dis                           | abled            |                  |                  |                 |           |  |  |  |  |  |  |

| bit 11        | Unimplement                                                                                                                    | ted: Read as '                             | ) <b>'</b>       |                  |                  |                 |           |  |  |  |  |  |  |

| bit 10-8      | SPI1TXIP<2:0>: SPI1 Transmit Interrupt Priority bits                                                                           |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> <li>•</li> </ul>                                      |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               | •                                                                                                                              |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               | •                                                                                                                              |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               | 001 = Interrup                                                                                                                 | ot is Priority 1<br>ot source is dis       | abled            |                  |                  |                 |           |  |  |  |  |  |  |

| bit 7         |                                                                                                                                | ted: Read as '                             |                  |                  |                  |                 |           |  |  |  |  |  |  |

| bit 6-4       | -                                                                                                                              |                                            |                  | itv bits         |                  |                 |           |  |  |  |  |  |  |

|               | <b>SPI1IP&lt;2:0&gt;:</b> SPI1 General Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)   |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               | •                                                                                                                              |                                            |                  | • •              |                  |                 |           |  |  |  |  |  |  |

|               | •                                                                                                                              |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               | 001 = Interrup                                                                                                                 |                                            | ablad            |                  |                  |                 |           |  |  |  |  |  |  |

| bit 3         | -                                                                                                                              | ot source is dis<br><b>ted:</b> Read as 'i |                  |                  |                  |                 |           |  |  |  |  |  |  |

| bit 2-0       | -                                                                                                                              |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

| 011 Z-0       | <b>T3IP&lt;2:0&gt;:</b> Timer3 Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)           |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               | •                                                                                                                              |                                            | gilloot priority |                  |                  |                 |           |  |  |  |  |  |  |

|               | •                                                                                                                              |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               |                                                                                                                                |                                            |                  |                  |                  |                 |           |  |  |  |  |  |  |

|               | •<br>001 = Interrup                                                                                                            | ot is Priority 1                           |                  |                  |                  |                 |           |  |  |  |  |  |  |

### REGISTER 8-23: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

If a MCLR Reset event occurs during Deep Sleep, the DSGPRx, DSCON and DSWAKE registers will remain valid, and the RELEASE bit will remain set. The state of the SOSC will also be retained. The I/O pins, however, will be reset to their MCLR Reset state. Since RELEASE is still set, changes to the SOSCEN bit (OSCCON<1>) cannot take effect until the RELEASE bit is cleared.

In all other Deep Sleep wake-up cases, application firmware must clear the RELEASE bit in order to reconfigure the I/O pins.

### 10.4.5 DEEP SLEEP WDT

To enable the DSWDT in Deep Sleep mode, program the Configuration bit, DSWDTEN (CW4<7>). The device WDT need not be enabled for the DSWDT to function. Entry into Deep Sleep modes automatically resets the DSWDT.

The DSWDT clock source is selected by the DSWDTOSC Configuration bit (CW4<5>). The postscaler options are programmed by the DSWDTPS<4:0> Configuration bits (CW4<4:0>). The minimum time-out period that can be achieved is 1 ms and the maximum is 25.7 days. For more information on the CW4 Configuration register and DSWDT configuration options, refer to Section 30.0 "Special Features".

### 10.4.5.1 Switching Clocks in Deep Sleep Mode

Both the RTCC and the DSWDT may run from either SOSC or the LPRC clock source. This allows both the RTCC and DSWDT to run without requiring both the LPRC and SOSC to be enabled together, reducing power consumption.

Running the RTCC from LPRC will result in a loss of accuracy in the RTCC of approximately 5 to 10%. If a more accurate RTCC is required, it must be run from the SOSC clock source. The RTCC clock source is selected with the RTCLK<1:0> bits (RTCPWC<11:10>).

Under certain circumstances, it is possible for the DSWDT clock source to be off when entering Deep Sleep mode. In this case, the clock source is turned on automatically (if DSWDT is enabled), without the need for software intervention. However, this can cause a delay in the start of the DSWDT counters. In order to avoid this delay when using SOSC as a clock source, the application can activate SOSC prior to entering Deep Sleep mode.

## 10.4.6 CHECKING AND CLEARING THE STATUS OF DEEP SLEEP

Upon entry into Deep Sleep mode, the status bit, DPSLP (RCON<10>), becomes set and must be cleared by the software.

On power-up, the software should read this status bit to determine if the Reset was due to an exit from Deep Sleep mode and clear the bit if it is set. Of the four possible combinations of DPSLP and POR bit states, the following three cases can be considered:

- Both the DPSLP and POR bits are cleared. In this case, the Reset was due to some event other than a Deep Sleep mode exit.

- The DPSLP bit is clear, but the POR bit is set; this is a normal Power-on Reset.

- Both the DPSLP and POR bits are set. This means that Deep Sleep mode was entered, the device was powered down and Deep Sleep mode was exited.

### 10.4.7 POWER-ON RESETS (PORs)

VDD voltage is monitored to produce PORs. Since exiting from Deep Sleep mode functionally looks like a POR, the technique described in Section 10.4.6 "Checking and Clearing the Status of Deep Sleep" should be used to distinguish between Deep Sleep and a true POR event. When a true POR occurs, the entire device, including all Deep Sleep logic (Deep Sleep registers, RTCC, DSWDT, etc.) is reset.

### 10.5 VBAT Mode

This mode represents the lowest power state that the microcontroller can achieve and still resume operation. VBAT mode is automatically triggered when the micro-controller's main power supply on VDD fails. When this happens, the microcontroller's on-chip power switch connects to a backup power source, such as a battery, supplied to the VBAT pin. This maintains a few key systems at an extremely low-power draw until VDD is restored.

The power supplied on VBAT only runs two systems: the RTCC and the Deep Sleep Semaphore registers (DSGPR0 and DSGPR1). To maintain these systems during a sudden loss of VDD, it is essential to connect a power source, other than VDD or AVDD, to the VBAT pin.

When the RTCC is enabled, it continues to operate with the same clock source (SOSC or LPRC) that was selected prior to entering VBAT mode. There is no provision to switch to a lower power clock source after the mode switch.

Since the loss of VDD is usually an unforeseen event, it is recommended that the contents of the Deep Sleep Semaphore registers be loaded with the data to be retained at an early point in code execution.

### 10.5.1 VBAT MODE WITH NO RTCC

By disabling RTCC operation during VBAT mode, power consumption is reduced to the lowest of all power-saving modes. In this mode, only the Deep Sleep Semaphore registers are maintained.

### **REGISTER 12-1:** T1CON: TIMER1 CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 2 **TSYNC:** Timer1 External Clock Input Synchronization Select bit  $\frac{When TCS = 1:}{1 = Synchronizes external clock input}$  0 = Does not synchronize external clock input  $\frac{When TCS = 0:}{This bit is ignored.}$

- bit 1 **TCS:** Timer1 Clock Source Select bit 1 = Extended clock selected by the TECS<1:0> bits 0 = Internal clock (Fosc/2)

- bit 0 Unimplemented: Read as '0'

- **Note 1:** Changing the value of T1CON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

NOTES:

### REGISTER 16-1: SPIxCON1L: SPIx CONTROL REGISTER 1 LOW (CONTINUED)

| bit 7   | SSEN: Slave Select Enable bit (Slave mode) <sup>(2)</sup>                                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = $\overline{SSx}$ pin is used by the macro in Slave mode; $\overline{SSx}$ pin is used as the slave select inpu 0 = SSx pin is not used by the macro (SSx pin will be controlled by the port I/O) |

| bit 6   | CKP: Clock Polarity Select bit                                                                                                                                                                       |

|         | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                             |

| bit 5   | MSTEN: Master Mode Enable bit                                                                                                                                                                        |

|         | 1 = Master mode<br>0 = Slave mode                                                                                                                                                                    |

| bit 4   | DISSDI: Disable SDIx Input Port bit                                                                                                                                                                  |

|         | <ul> <li>1 = SDIx pin is not used by the module; pin is controlled by the port function</li> <li>0 = SDIx pin is controlled by the module</li> </ul>                                                 |

| bit 3   | DISSCK: Disable SCKx Output Port bit                                                                                                                                                                 |

|         | <ul> <li>1 = SCKx pin is not used by the module; pin is controlled by the port function</li> <li>0 = SCKx pin is controlled by the module</li> </ul>                                                 |

| bit 2   | MCLKEN: Master Clock Enable bit <sup>(3)</sup>                                                                                                                                                       |

|         | <ul> <li>1 = MCLK is used by the BRG</li> <li>0 = PBCLK is used by the BRG</li> </ul>                                                                                                                |

| bit 1   | SPIFE: Frame Sync Pulse Edge Select bit                                                                                                                                                              |

|         | <ul> <li>1 = Frame Sync pulse (Idle-to-active edge) coincides with the first bit clock</li> <li>0 = Frame Sync pulse (Idle-to-active edge) precedes the first bit clock</li> </ul>                   |

| bit 0   | ENHBUF: Enhanced Buffer Mode Enable bit                                                                                                                                                              |

|         | <ol> <li>1 = Enhanced Buffer mode is enabled</li> <li>0 = Enhanced Buffer mode is disabled</li> </ol>                                                                                                |

| Note 1: | When AUDEN = 1, this module functions as if CKE = 0, regardless of its actual value.                                                                                                                 |

- **2:** When FRMEN = 1, SSEN is not used.

- **3:** MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

REGISTER 16-4: SPIxSTATL: SPIx STATUS REGISTER LOW

| U-0           | U-0                                                                                                                                                            | U-0                                 | R/C-0, HS       | R-0, HSC         | U-0             | U-0           | R-0, HSC              |  |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|------------------|-----------------|---------------|-----------------------|--|--|--|--|--|--|

|               | _                                                                                                                                                              | _                                   | FRMERR          | SPIBUSY          |                 | _             | SPITUR <sup>(1)</sup> |  |  |  |  |  |  |

| bit 15        |                                                                                                                                                                |                                     |                 |                  |                 |               | bit 8                 |  |  |  |  |  |  |

|               |                                                                                                                                                                |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

| R-0, HSC      | R/C-0, HS                                                                                                                                                      | R-1, HSC                            | U-0             | R-1, HSC         | U-0             | R-0, HSC      | R-0, HSC              |  |  |  |  |  |  |

| SRMT          | SPIROV                                                                                                                                                         | SPIRBE                              | —               | SPITBE           | —               | SPITBF        | SPIRBF                |  |  |  |  |  |  |

| bit 7         |                                                                                                                                                                |                                     |                 |                  |                 |               | bit 0                 |  |  |  |  |  |  |

| r             |                                                                                                                                                                |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

| Legend:       |                                                                                                                                                                | C = Clearable                       | e bit           | HSC = Hardw      | vare Settable/  | Clearable bit |                       |  |  |  |  |  |  |

| R = Readabl   |                                                                                                                                                                | x = Bit is unkr                     |                 |                  | nented bit, rea |               |                       |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                            | '1' = Bit is set                    |                 | '0' = Bit is cle | ared            | HS = Hardwar  | e Settable bit        |  |  |  |  |  |  |

|               |                                                                                                                                                                |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

| bit 15-13     | Unimplemented: Read as '0'<br>FRMERR: SPIx Frame Error Status bit                                                                                              |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

| bit 12        |                                                                                                                                                                |                                     | Status bit      |                  |                 |               |                       |  |  |  |  |  |  |

|               | 1 = Frame err                                                                                                                                                  | or is detected<br>error is detected | he              |                  |                 |               |                       |  |  |  |  |  |  |

| bit 11        |                                                                                                                                                                |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

|               | <b>SPIBUSY:</b> SPIx Activity Status bit<br>1 = Module is currently busy with some transactions                                                                |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

|               | 0 = No ongoing transactions (at time of read)                                                                                                                  |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

| bit 10-9      | Unimplement                                                                                                                                                    | Unimplemented: Read as '0'          |                 |                  |                 |               |                       |  |  |  |  |  |  |

| bit 8         | SPITUR: SPIx Transmit Underrun (TUR) Status bit <sup>(1)</sup>                                                                                                 |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

|               | <ul> <li>1 = Transmit buffer has encountered a Transmit Underrun condition</li> <li>0 = Transmit buffer does not have a Transmit Underrun condition</li> </ul> |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

| 1.11.7        |                                                                                                                                                                |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

| bit 7         | <b>SRMT:</b> Shift Register Empty Status bit<br>1 = No current or pending transactions (i.e., neither SPIxTXB or SPIxTXSR contains data to transmit)           |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

|               | 0 = Current or pending transactions                                                                                                                            |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

| bit 6         | SPIROV: SPIx Receive Overflow (ROV) Status bit                                                                                                                 |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

|               |                                                                                                                                                                | e/half-word/wo                      |                 |                  | ived when the   | SPIxRXB was f | ull                   |  |  |  |  |  |  |

| bit 5         | SPIRBE: SPI                                                                                                                                                    | x RX Buffer En                      | npty Status bit |                  |                 |               |                       |  |  |  |  |  |  |

|               | 1 = RX buffer is empty<br>0 = RX buffer is not empty                                                                                                           |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

|               | Standard Buffer Mode:                                                                                                                                          |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

|               | Automatically set in hardware when SPIxBUF is read from, reading SPIxRXB. Automatically cleared in hardware when SPIx transfers data from SPIxRXSR to SPIxRXB. |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

|               | Enhanced Buffer Mode:<br>Indicates RXELM<5:0> = 6' b000000.                                                                                                    |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

| bit 4         | Unimplement                                                                                                                                                    | ted: Read as '                      | o <b>'</b>      |                  |                 |               |                       |  |  |  |  |  |  |

| bit 3         | SPITBE: SPIx Transmit Buffer Empty Status bit                                                                                                                  |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

|               | 1 = SPIxTXB is empty<br>0 = SPIxTXB is not empty                                                                                                               |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

|               |                                                                                                                                                                | Standard Buffer Mode:               |                 |                  |                 |               |                       |  |  |  |  |  |  |

|               |                                                                                                                                                                |                                     |                 |                  |                 | B to SPIxTXSR | Automatically         |  |  |  |  |  |  |

|               | cleared in har<br>Enhanced But                                                                                                                                 |                                     | FIXBUF IS Writt | en, loading SP   | IXI AB.         |               |                       |  |  |  |  |  |  |

|               |                                                                                                                                                                | LM<5:0> = 6'                        | b000000.        |                  |                 |               |                       |  |  |  |  |  |  |

|               |                                                                                                                                                                |                                     |                 |                  |                 |               |                       |  |  |  |  |  |  |

## **Note 1:** SPITUR is cleared when SPIEN = 0. When IGNTUR = 1, SPITUR provides dynamic status of the underrun condition, but does not stop RX/TX operation and does not need to be cleared by software.

### REGISTER 17-1: I2CxCONL: I2Cx CONTROL REGISTER LOW (CONTINUED)

| bit 7  | GCEN: General Call Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                       |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <ul> <li>1 = Enables interrupt when a general call address is received in I2CxRSR; module is enabled for reception</li> <li>0 = General call address is disabled</li> </ul>                                                            |

| bit 6  | STREN: SCLx Clock Stretch Enable bit                                                                                                                                                                                                   |

|        | In I <sup>2</sup> C Slave mode only; used in conjunction with the SCLREL bit.<br>1 = Enables clock stretching<br>0 = Disables clock stretching                                                                                         |

| bit 5  | ACKDT: Acknowledge Data bit                                                                                                                                                                                                            |

|        | In I <sup>2</sup> C Master mode, during Master Receive mode – The value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.                                                              |

|        | In I <sup>2</sup> C Slave mode when AHEN = 1 or DHEN = 1 – The value that the slave will transmit when it initiates<br>an Acknowledge sequence at the end of an address or data reception.<br>1 = A NACK is sent<br>0 = An ACK is sent |

| bit 4  | ACKEN: Acknowledge Sequence Enable bit                                                                                                                                                                                                 |

|        | In I <sup>2</sup> C Master mode only; applicable during Master Receive mode.<br>1 = Initiates Acknowledge sequence on SDAx and SCLx pins, and transmits ACKDT data bit<br>0 = Acknowledge sequence is Idle                             |

| bit 3  | <b>RCEN:</b> Receive Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                    |

|        | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C, automatically cleared by hardware at the end of the 8-bit receive data byte</li> <li>0 = Receive sequence is not in progress</li> </ul>                                          |

| bit 2  | PEN: Stop Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                     |

| DIL 2  | 1 = Initiates Stop condition on the SDAx and SCLx pins<br>0 = Stop condition is Idle                                                                                                                                                   |

| bit 1  | <b>RSEN:</b> Restart Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                          |

|        | <ul> <li>1 = Initiates Restart condition on the SDAx and SCLx pins</li> <li>0 = Restart condition is Idle</li> </ul>                                                                                                                   |

| bit 0  | SEN: Start Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                    |

|        | <ul> <li>1 = Initiates Start condition on the SDAx and SCLx pins</li> <li>0 = Start condition is Idle</li> </ul>                                                                                                                       |

| Note 1 | : Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.                                                                                                     |

**2:** Automatically cleared to '0' at the beginning of slave transmission.

### 19.1.2 HOST AND OTG MODES

### 19.1.2.1 D+ and D- Pull-Down Resistors

PIC24FJ128GB204 family devices have a built-in 15 kΩ pull-down resistor on the D+ and D- lines. These are used in tandem to signal to the bus that the microcontroller is operating in Host mode. They are engaged by setting the HOSTEN bit (U1CON<3>). If the OTGEN bit (U1OTGCON<2>) is set, then these pull-downs are enabled by setting the DPPULDWN and DMPULDWN bits (U1OTGCON<5:4>).

### 19.1.2.2 Power Configurations

In Host mode, as well as Host mode in On-The-Go operation, the "USB 2.0 Specification" requires that the host application should supply power on VBUS. Since the microcontroller is running below VBUS, and is not able to source sufficient current, a separate power supply must be provided.

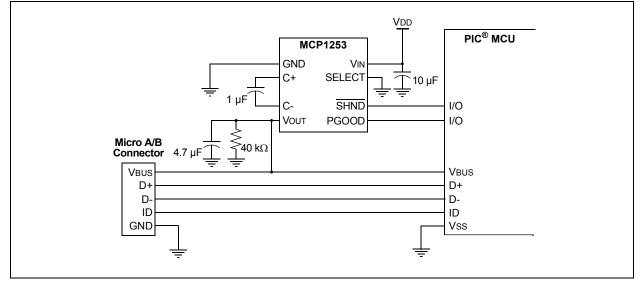

When the application is always operating in Host mode, a simple circuit can be used to supply VBUS and regulate current on the bus (Figure 19-6). For OTG operation, it is necessary to be able to turn VBUS on or off as needed, as the microcontroller switches between Device and Host modes. A typical example using an external charge pump is shown in Figure 19-7.

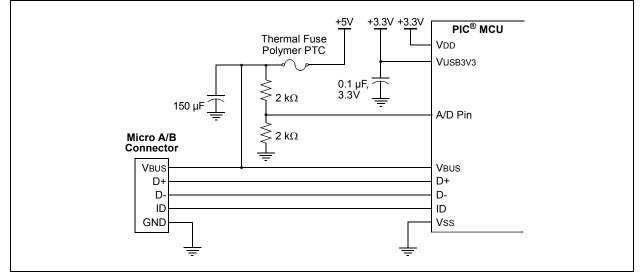

### FIGURE 19-6: USB HOST INTERFACE EXAMPLE

### FIGURE 19-7: USB OTG INTERFACE EXAMPLE

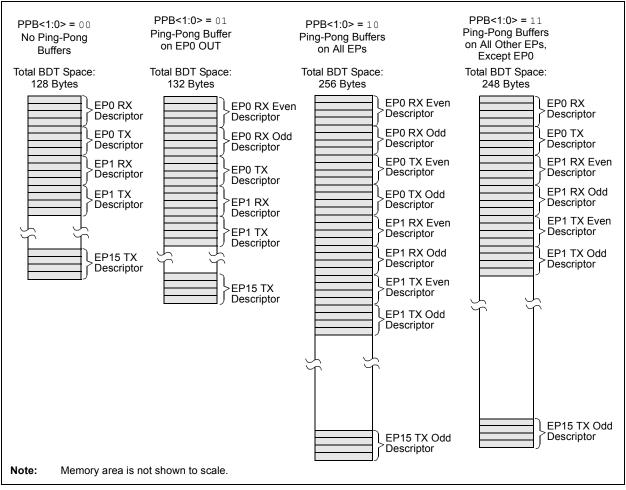

## 19.2 USB Buffer Descriptors and the BDT

Endpoint buffer control is handled through a structure called the Buffer Descriptor Table (BDT). This provides a flexible method for users to construct and control endpoint buffers of various lengths and configurations.

The BDT can be located in any available, 512-byte aligned block of data RAM. The BDT Pointer (U1BDTP1) contains the upper address byte of the BDT and sets the location of the BDT in RAM. The user must set this pointer to indicate the table's location.

The BDT is composed of Buffer Descriptors (BDs) which are used to define and control the actual buffers in the USB RAM space. Each BD consists of two, 16-bit "soft" (non-fixed address) registers, BDnSTAT and BDnADR, where n represents one of the 64 possible BDs (range of 0 to 63). BDnSTAT is the status register for BDn, while BDnADR specifies the starting address for the buffer associated with BDn.

Note: Since BDnADR is a 16-bit register, only the first 64 Kbytes of RAM can be accessed by the USB module.

Depending on the endpoint buffering configuration used, there are up to 64 sets of Buffer Descriptors, for a total of 256 bytes. At a minimum, the BDT must be at least 8 bytes long. This is because the *"USB 2.0 Specification"* mandates that every device must have Endpoint 0 with both input and output for initial setup.

Endpoint mapping in the BDT is dependent on three variables:

- Endpoint number (0 to 15)

- Endpoint direction (RX or TX)

- Ping-pong settings (U1CNFG1<1:0>)

Figure 19-8 illustrates how these variables are used to map endpoints in the BDT.

In Host mode, only Endpoint 0 Buffer Descriptors are used. All transfers utilize the Endpoint 0 Buffer Descriptor and USB Endpoint Control register (U1EP0). For received packets, the attached device's source endpoint is indicated by the value of ENDPT<3:0> in the USB Status register (U1STAT<7:4>). For transmitted packets, the attached device's destination endpoint is indicated by the value written to the USB Token register (U1TOK).

### FIGURE 19-8: BDT MAPPING FOR ENDPOINT BUFFERING MODES

| R/W-0            | R/W-0                                                                              | R/W-0                                                                 | R/W-0                   | U-0               | R/W-0            | R/W-0           | R/W-0  |

|------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------|-------------------|------------------|-----------------|--------|

| PTWREN           | PTRDEN                                                                             | PTBE1EN                                                               | PTBE0EN                 |                   | AWAITM1          | AWAITM0         | AWAITE |

| bit 15           |                                                                                    | •                                                                     |                         |                   | •                |                 | bit    |

|                  |                                                                                    |                                                                       |                         |                   |                  |                 |        |

| U-0              | U-0                                                                                | U-0                                                                   | U-0                     | U-0               | U-0              | U-0             | U-0    |

| _                |                                                                                    | —                                                                     | —                       | —                 |                  |                 |        |

| bit 7            |                                                                                    |                                                                       |                         |                   |                  |                 | bit    |

| Legend:          |                                                                                    |                                                                       |                         |                   |                  |                 |        |

| R = Readable     | e bit                                                                              | W = Writable                                                          | bit                     | U = Unimplen      | nented bit, read | l as '0'        |        |

| -n = Value at    | POR                                                                                | '1' = Bit is set                                                      |                         | '0' = Bit is clea | ared             | x = Bit is unkn | own    |

| bit 15<br>bit 14 | 1 = PMWR pc<br>0 = PMWR pc<br><b>PTRDEN:</b> PM<br>1 = PMRD/ <u>PN</u>             | ort is disabled<br>IP Read/Write :<br><u>/WR</u> port is en           | Strobe Port En<br>abled |                   |                  |                 |        |

| bit 13           | <b>PTBE1EN:</b> PI<br>1 = PMBE1 p                                                  | ort is enabled                                                        |                         | Port Enable bit   |                  |                 |        |

| bit 12           | <b>PTBE0EN:</b> PI<br>1 = PMBE0 p                                                  | ort is disabled<br>MP Low Nibble<br>ort is enabled<br>ort is disabled | /Byte Enable F          | Port Enable bit   |                  |                 |        |

| bit 11           | Unimplemen                                                                         | ted: Read as '                                                        | )'                      |                   |                  |                 |        |

| bit 10-9         | AWAITM<1:0<br>11 = Wait of 3<br>10 = Wait of 2<br>01 = Wait of 1<br>00 = Wait of 1 | 2½ TCY<br>1½ TCY                                                      | ch Strobe Wait          | State bits        |                  |                 |        |

| bit 8            | <b>AWAITE:</b> Add<br>1 = Wait of 11<br>0 = Wait of 14                             | ¼ TCY                                                                 | r Address Latc          | h Strobe Wait S   | State bit        |                 |        |

|                  | 0 <b>Wait 01 /4</b>                                                                | 101                                                                   |                         |                   |                  |                 |        |

### REGISTER 21-3: PMCON3: EPMP CONTROL REGISTER 3

| R/W-0                        | R-0                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0                                      | R/W-0 | R/W-0                | R/W-0            | R/W-0              | R/W-0 |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------|----------------------|------------------|--------------------|-------|--|--|

| ADRC                         | EXTSAM                                                                                                                                                                                                                                                                                                                                                                                                                | PUMPEN                                     | SAMC4 | SAMC3                | SAMC2            | SAMC1              | SAMC0 |  |  |

| bit 15                       |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |       |                      |                  |                    | bit 8 |  |  |

| R/W-0                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                      | R/W-0 | R/W-0                | R/W-0            | R/W-0              | R/W-0 |  |  |

| ADCS7                        | ADCS6                                                                                                                                                                                                                                                                                                                                                                                                                 | ADCS5                                      | ADCS4 | ADCS3                | ADCS2            | ADCS1              | ADCS0 |  |  |

| bit 7                        |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |       |                      |                  |                    | bit ( |  |  |

| Legend:                      |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |       |                      |                  |                    |       |  |  |

| R = Readab                   | le bit                                                                                                                                                                                                                                                                                                                                                                                                                | W = Writable                               | bit   | U = Unimplem         | nented bit, read | d as '0'           |       |  |  |

| -n = Value at POR            |                                                                                                                                                                                                                                                                                                                                                                                                                       | '1' = Bit is set                           |       | '0' = Bit is cleared |                  | x = Bit is unknown |       |  |  |

| bit 14<br>bit 13<br>bit 12-8 | <ul> <li>0 = Clock derived from system clock</li> <li>EXTSAM: Extended Sampling Time bit</li> <li>1 = A/D is still sampling after SAMP = 0</li> <li>0 = A/D is finished sampling</li> <li>PUMPEN: Charge Pump Enable bit</li> <li>1 = Charge pump for switches is enabled</li> <li>0 = Charge pump for switches is disabled</li> <li>SAMC&lt;4:0&gt;: Auto-Sample Time Select bits</li> <li>11111 = 31 TAD</li> </ul> |                                            |       |                      |                  |                    |       |  |  |

| bit 7-0                      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                                                                                                                                           | AD<br>AD<br>ADC1 Convers<br>256 • TCY = TA |       | ect bits             |                  |                    |       |  |  |

### REGISTER 25-3: AD1CON3: ADC1 CONTROL REGISTER 3

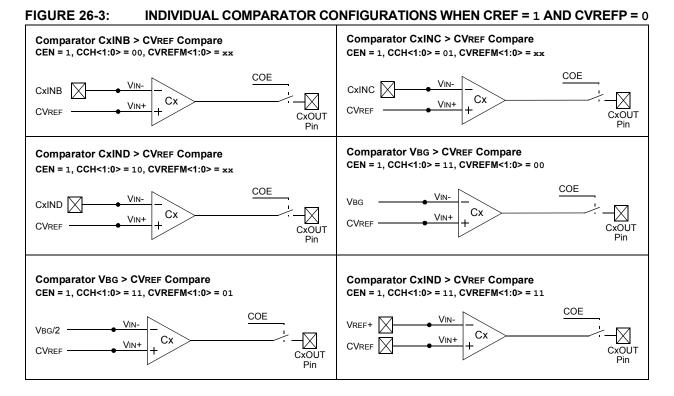

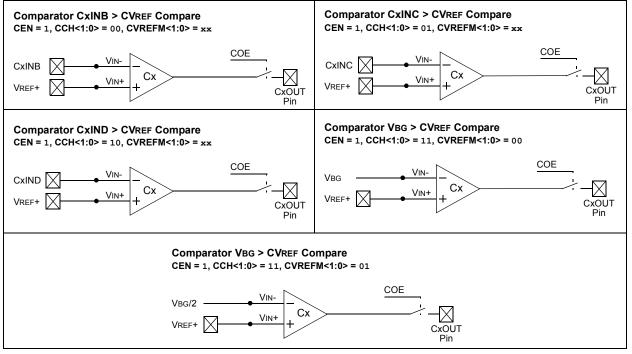

### FIGURE 26-4: INDIVIDUAL COMPARATOR CONFIGURATIONS WHEN CREF = 1 AND CVREFP = 1

### REGISTER 30-1: CW1: FLASH CONFIGURATION WORD 1 (CONTINUED)

- bit 4 FWPSA: WDT Prescaler Ratio Select bit

- 1 = Prescaler ratio of 1:128

- 0 = Prescaler ratio of 1:32

- bit 3-0 WDTPS<3:0>: Watchdog Timer Postscaler Select bits

- 1111 = 1:32,768 1110 = 1:16,384 1101 **= 1:8,192** 1100 = 1:4,096 1011 = 1:2,048 1010 = 1:1,024 1001 **= 1:512** 1000 **= 1:256** 0111 = 1:128 0110 **= 1:64** 0101 = 1:32 0100 = 1:16 0011 **= 1:8** 0010 = 1:4 0001 **= 1:2** 0000 = 1:1

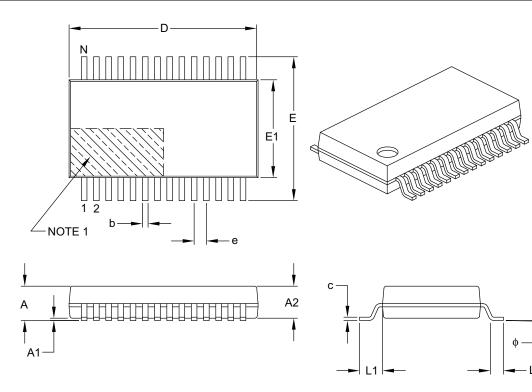

### 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |          | MILLIMETERS | 5     |

|--------------------------|-------|----------|-------------|-------|

| Dimension Limits         |       | MIN      | NOM         | MAX   |

| Number of Pins           | N     | 28       |             |       |

| Pitch                    | е     | 0.65 BSC |             |       |

| Overall Height           | А     | -        | -           | 2.00  |

| Molded Package Thickness | A2    | 1.65     | 1.75        | 1.85  |

| Standoff                 | A1    | 0.05     | -           | -     |

| Overall Width            | E     | 7.40     | 7.80        | 8.20  |

| Molded Package Width     | E1    | 5.00     | 5.30        | 5.60  |

| Overall Length           | D     | 9.90     | 10.20       | 10.50 |

| Foot Length              | L     | 0.55     | 0.75        | 0.95  |

| Footprint                |       | 1.25 REF |             |       |

| Lead Thickness           | С     | 0.09     | -           | 0.25  |

| Foot Angle               | ф     | 0°       | 4°          | 8°    |

| Lead Width               | b     | 0.22     | -           | 0.38  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

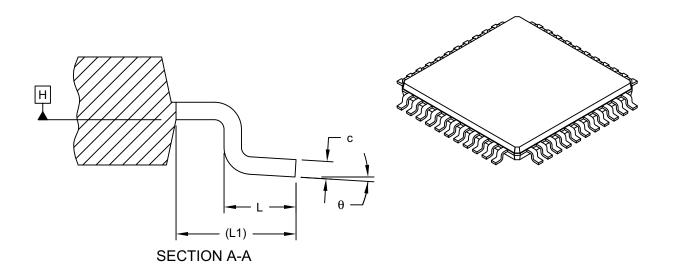

### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |     | MILLIMETERS |      |      |  |

|--------------------------|-----|-------------|------|------|--|

| Dimension                | MIN | NOM         | MAX  |      |  |

| Number of Leads          | N   | 44          |      |      |  |

| Lead Pitch               | е   | 0.80 BSC    |      |      |  |

| Overall Height           | Α   | -           | -    | 1.20 |  |

| Standoff                 | A1  | 0.05        | -    | 0.15 |  |

| Molded Package Thickness | A2  | 0.95        | 1.00 | 1.05 |  |

| Overall Width            | E   | 12.00 BSC   |      |      |  |

| Molded Package Width     | E1  | 10.00 BSC   |      |      |  |

| Overall Length           | D   | 12.00 BSC   |      |      |  |

| Molded Package Length    | D1  | 10.00 BSC   |      |      |  |

| Lead Width               | b   | 0.30        | 0.37 | 0.45 |  |

| Lead Thickness           | С   | 0.09        | -    | 0.20 |  |

| Lead Length              | L   | 0.45        | 0.60 | 0.75 |  |

| Footprint                | L1  | 1.00 REF    |      |      |  |

| Foot Angle               | θ   | 0°          | 3.5° | 7°   |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Exact shape of each corner is optional.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2