#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

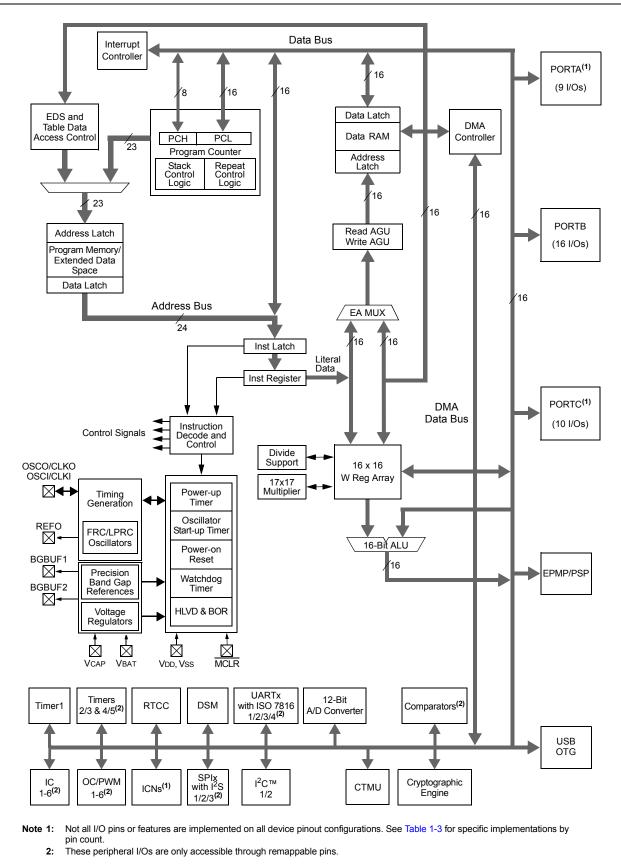

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                     |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT        |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb202t-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

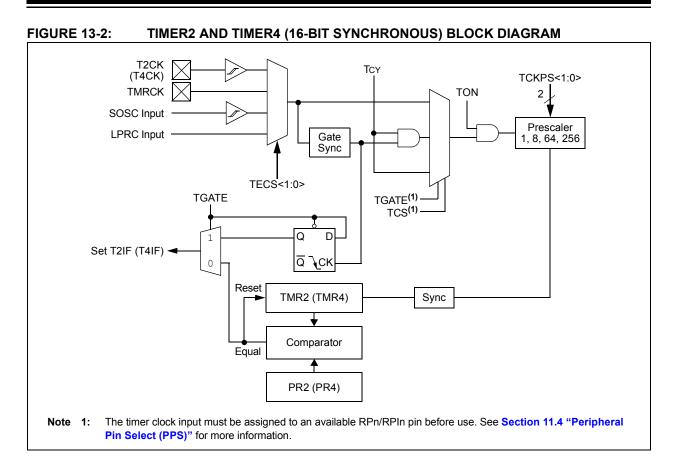

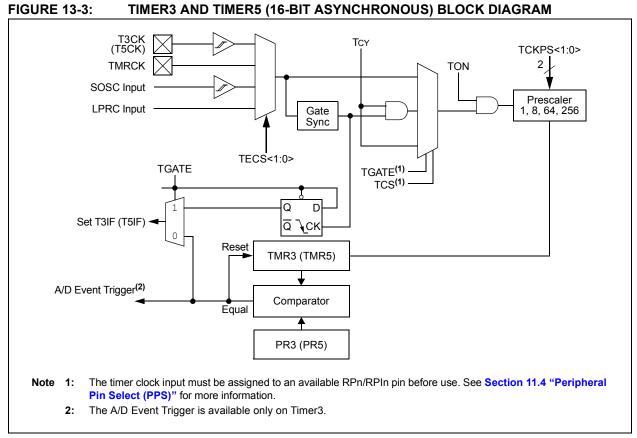

| TABLE 4      | 4-6: | TIMER  | REGIS  | TER MA | Р      |        |        |              |               |               |              |        |        |       |       |       |       |               |

|--------------|------|--------|--------|--------|--------|--------|--------|--------------|---------------|---------------|--------------|--------|--------|-------|-------|-------|-------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8         | Bit 7         | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1         | 024C |        |        |        |        |        |        |              | Timer1 I      | Register      |              |        |        |       |       |       |       | 0000          |

| PR1          | 024E |        |        |        |        |        |        |              | Timer1 Peri   | od Register   | -            |        |        |       |       |       |       | FFFF          |

| T1CON        | 0250 | TON    | _      | TSIDL  | _      | _      | _      | TECS1        | TECS0         | _             | TGATE        | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000          |

| TMR2         | 0252 |        |        |        |        |        |        |              | Timer2        | Register      |              |        |        |       |       |       |       | 0000          |

| TMR3HLD      | 0254 |        |        |        |        |        | Timer  | 3 Holding F  | Register (for | 32-bit time   | r operations | only)  |        |       |       |       |       | 0000          |

| TMR3         | 0256 |        |        |        |        |        |        |              | Timer3 I      | Register      |              |        |        |       |       |       |       | 0000          |

| PR2          | 0258 |        |        |        |        |        |        |              | Timer2 Peri   | od Register   |              |        |        |       |       |       |       | FFFF          |

| PR3          | 025A |        |        |        |        |        |        |              | Timer3 Peri   | od Register   |              |        |        |       |       |       |       | FFFF          |

| T2CON        | 025C | TON    | _      | TSIDL  | _      | _      | _      | TECS1        | TECS0         | _             | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T3CON        | 025E | TON    | _      | TSIDL  | _      | _      | _      | TECS1        | TECS0         | _             | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4         | 0260 |        |        |        |        |        |        |              | Timer4 I      | Register      |              |        |        |       |       |       |       | 0000          |

| TMR5HLD      | 0262 |        |        |        |        |        | Tin    | ner5 Holding | g Register (  | for 32-bit op | perations or | ıly)   |        |       |       |       |       | 0000          |

| TMR5         | 0264 |        |        |        |        |        |        |              | Timer5 I      | Register      |              |        |        |       |       |       |       | 0000          |

| PR4          | 0266 |        |        |        |        |        |        |              | Timer4 Peri   | od Register   |              |        |        |       |       |       |       | FFFF          |

| PR5          | 0268 |        |        |        |        |        |        |              | Timer5 Peri   | od Register   | •            |        |        |       |       |       |       | FFFF          |

| T4CON        | 026A | TON    |        | TSIDL  | _      | _      | _      | TECS1        | TECS0         | _             | TGATE        | TCKPS1 | TCKPS0 | T45   | _     | TCS   |       | 0000          |

| T5CON        | 026C | TON    | —      | TSIDL  |        | _      | _      | TECS1        | TECS0         | _             | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

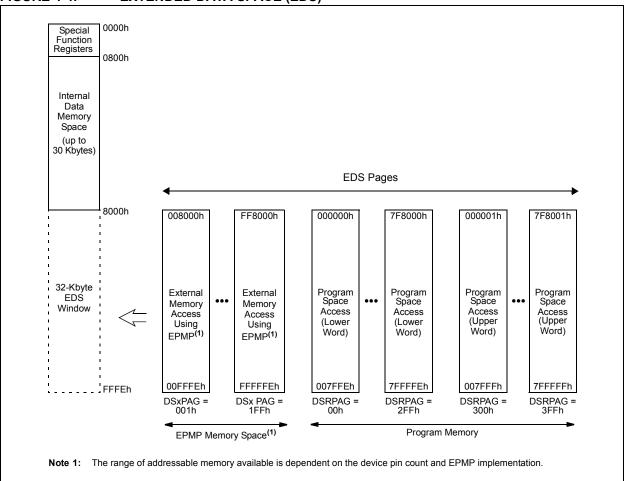

### 4.2.5 EXTENDED DATA SPACE (EDS)

The Extended Data Space (EDS) allows PIC24F devices to address a much larger range of data than would otherwise be possible with a 16-bit address range. EDS includes any additional internal data memory not directly accessible by the lower 32-Kbyte data address space and any external memory through the Enhanced Parallel Master Port (EPMP).

In addition, EDS also allows read access to the program memory space. This feature is called Program Space Visibility (PSV) and is discussed in detail in Section 4.3.3 "Reading Data from Program Memory Using EDS".

Figure 4-4 displays the entire EDS space. The EDS is organized as pages, called EDS pages, with one page equal to the size of the EDS window (32 Kbytes). A particular EDS page is selected through the Data Space Read register (DSRPAG) or Data Space Write register (DSWPAG). For PSV, only the DSRPAG register is used. The combination of the DSRPAG register value and the 16-bit wide data address forms a 24-bit Effective Address (EA). The data addressing range of PIC24FJ128GB204 family devices depends on the version of the Enhanced Parallel Master Port implemented on a particular device; this is, in turn, a function of device pin count. Table 4-34 lists the total memory accessible by each of the devices in this family. For more details on accessing external memory using EPMP, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Enhanced Parallel Master Port (EPMP)"** (DS39730).

| <b>TABLE 4-34:</b> | TOTAL ACCESSIBLE DATA |

|--------------------|-----------------------|

|                    | MEMORY                |

| Family          | Internal<br>RAM | External RAM<br>Access Using<br>EPMP |

|-----------------|-----------------|--------------------------------------|

| PIC24FJXXXGB204 | 8K              | Up to 16 Mbytes                      |

| PIC24FJXXXGB202 | 8K              | Up to 64K                            |

**Note:** Accessing Page 0 in the EDS window will generate an address error trap as Page 0 is the base data memory (data locations, 0800h to 7FFFh, in the lower Data Space).

### FIGURE 4-4: EXTENDED DATA SPACE (EDS)

### 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit wide program space and 16-bit wide Data Space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the PIC24F architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. It can only access the least significant word of the program word.

## 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the MSbs of TBLPAG are used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 10-bit Extended Data Space Read register (DSRPAG) is used to define a 16K word page in the program space. When the Most Significant bit (MSb) of the EA is '1', and the MSb (bit 9) of DSRPAG is '1', the lower 8 bits of DSRPAG are concatenated with the lower 15 bits of the EA to form a 23-bit program space address. The DSRPAG<8> bit decides whether the lower word (when the bit is '0') or the higher word (when the bit is '1') of program memory is mapped. Unlike table operations, this strictly limits remapping operations to the user memory area.

Table 4-36 and Figure 4-8 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refer to a program space word, whereas D<15:0> refer to a Data Space word.

| Access Type              | Access        | Program Space Address |            |                     |             |                     |  |  |  |

|--------------------------|---------------|-----------------------|------------|---------------------|-------------|---------------------|--|--|--|

|                          | Space         | <23>                  | <22:16>    | <15>                | <14:1>      | <0>                 |  |  |  |

| Instruction Access       | User          | 0 PC<22:1>            |            |                     |             | 0                   |  |  |  |

| (Code Execution)         |               |                       | 0xx xxxx x | XXX XXXX            | x xxxx xxx0 |                     |  |  |  |

| TBLRD/TBLWT              | User          | TB                    | LPAG<7:0>  | Data EA<15:0>       |             |                     |  |  |  |

| (Byte/Word Read/Write)   |               | 0:                    | XXX XXXX   | XXXX XXXX XXXX XXXX |             |                     |  |  |  |

|                          | Configuration | TB                    | LPAG<7:0>  | Data EA<15:0>       |             |                     |  |  |  |

|                          |               | 1xxx xxxx             |            | XXXX XXXX XXXX XXXX |             |                     |  |  |  |

| Program Space Visibility | User          | 0 DSRPAG<7:           |            | 0> <sup>(2)</sup>   | Data EA<1   | 4:0> <sup>(1)</sup> |  |  |  |

| (Block Remap/Read)       |               | 0                     | XXXX XXX   | XX                  | XXX XXXX XX | XX XXXX             |  |  |  |

#### TABLE 4-36: PROGRAM SPACE ADDRESS CONSTRUCTION

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is DSRPAG<0>.

2: DSRPAG<9> is always '1' in this case. DSRPAG<8> decides whether the lower word or higher word of program memory is read. When DSRPAG<8> is '0', the lower word is read and when it is '1', the higher word is read.

| U-0           | R/W-0          | R/W-0                              | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|----------------|------------------------------------|------------------|------------------|------------------|-----------------|--------|

|               | DMA1IF         | AD1IF                              | U1TXIF           | U1RXIF           | SPI1TXIF         | SPI1IF          | T3IF   |

| bit 15        |                |                                    |                  |                  |                  |                 | bit 8  |

| R/W-0         | R/W-0          | R/W-0                              | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T2IF          | OC2IF          | IC2IF                              | DMA0IF           | T1IF             | OC1IF            | IC1IF           | INT0IF |

| bit 7         |                |                                    | ·                | ·                | · · · ·          |                 | bit C  |

| Legend:       |                |                                    |                  |                  |                  |                 |        |

| R = Readabl   |                | W = Writable                       |                  | -                | mented bit, read |                 |        |

| -n = Value at | t POR          | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkn | iown   |

| bit 15        | Unimplemen     | ted: Read as '                     | 0'               |                  |                  |                 |        |

| bit 14        | -              | A Channel 1 Ir                     |                  | atus bit         |                  |                 |        |

|               | 1 = Interrupt  | request has oc                     | curred           |                  |                  |                 |        |

| L:1 40        | •              | request has no                     |                  |                  |                  |                 |        |

| bit 13        |                | 1 Event Interrup<br>request has oc | •                | л                |                  |                 |        |

|               |                | request has oc                     |                  |                  |                  |                 |        |

| bit 12        | U1TXIF: UAF    | RT1 Transmitte                     | r Interrupt Flag | Status bit       |                  |                 |        |

|               |                | request has oc<br>request has no   |                  |                  |                  |                 |        |

| pit 11        | U1RXIF: UAF    | RT1 Receiver I                     | nterrupt Flag St | tatus bit        |                  |                 |        |

|               |                | request has oc<br>request has no   |                  |                  |                  |                 |        |

| bit 10        | SPI1TXIF: SI   | PI1 Transmit In                    | terrupt Flag Sta | atus bit         |                  |                 |        |

|               |                | request has oc<br>request has no   |                  |                  |                  |                 |        |

| bit 9         | SPI1IF: SPI1   | General Interr                     | upt Flag Status  | bit              |                  |                 |        |

|               |                | request has oc<br>request has no   |                  |                  |                  |                 |        |

| bit 8         |                | Interrupt Flag                     |                  |                  |                  |                 |        |

|               |                | request has oc<br>request has no   |                  |                  |                  |                 |        |

| bit 7         | T2IF: Timer2   | Interrupt Flag                     | Status bit       |                  |                  |                 |        |

|               |                | request has oc<br>request has no   |                  |                  |                  |                 |        |

| bit 6         | OC2IF: Outp    | ut Compare Ch                      | annel 2 Interru  | pt Flag Status   | bit              |                 |        |

|               |                | request has oc<br>request has no   |                  |                  |                  |                 |        |

| bit 5         | IC2IF: Input ( | Capture Chann                      | el 2 Interrupt F | lag Status bit   |                  |                 |        |

|               |                | request has oc<br>request has no   |                  |                  |                  |                 |        |

| bit 4         | DMA0IF: DM     | A Channel 0 Ir                     | terrupt Flag Sta | atus bit         |                  |                 |        |

|               |                | request has oc<br>request has no   |                  |                  |                  |                 |        |

| bit 3         | -              | Interrupt Flag                     |                  |                  |                  |                 |        |

|               |                | request has oc                     | curred           |                  |                  |                 |        |

#### REGISTER 8-13: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

| U-0           | R/W-0           | R/W-0                             | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|-----------------|-----------------------------------|-----------------|------------------|------------------|-----------------|--------|

|               | DMA1IE          | AD1IE                             | U1TXIE          | U1RXIE           | SPI1TXIE         | SPI1IE          | T3IE   |

| bit 15        |                 |                                   |                 |                  |                  |                 | bit 8  |

| R/W-0         | R/W-0           | R/W-0                             | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T2IE          | OC2IE           | IC2IE                             | DMA0IE          | T1IE             | OC1IE            | IC1IE           | INTOIE |

| bit 7         | OOZIL           | IOZIL                             | DIVIAUL         | 1112             | OUTIL            | IOTIL           | bit (  |

| Legend:       |                 |                                   |                 |                  |                  |                 |        |

| R = Readabl   | le bit          | W = Writable                      | bit             | U = Unimplen     | nented bit, read | l as '0'        |        |

| -n = Value at | t POR           | '1' = Bit is set                  |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15        | Unimplemen      | ted: Read as '                    | ר,              |                  |                  |                 |        |

| bit 14        | •               | A Channel 1 In                    |                 | bit              |                  |                 |        |

|               |                 | equest is enab                    | •               |                  |                  |                 |        |

|               | 0 = Interrupt r | equest is not e                   | nabled          |                  |                  |                 |        |

| bit 13        |                 | Interrupt Enal                    |                 |                  |                  |                 |        |

|               |                 | equest is enab<br>equest is not e |                 |                  |                  |                 |        |

| bit 12        | •               | T1 Transmitter                    |                 | ole hit          |                  |                 |        |

|               |                 | equest is enab                    | -               |                  |                  |                 |        |

|               | 0 = Interrupt r | equest is not e                   | nabled          |                  |                  |                 |        |

| bit 11        |                 | RT1 Receiver Ir                   | •               | e bit            |                  |                 |        |

|               |                 | equest is enab<br>equest is not e |                 |                  |                  |                 |        |

| bit 10        | SPI1TXIE: SF    | PI1 Transmit Co                   | omplete Interru | pt Enable bit    |                  |                 |        |

|               |                 | equest is enab<br>equest is not e |                 |                  |                  |                 |        |

| bit 9         | •               | General Interr                    |                 |                  |                  |                 |        |

|               | 1 = Interrupt r | equest is enab<br>equest is not e | led             |                  |                  |                 |        |

| bit 8         | -               | Interrupt Enab                    |                 |                  |                  |                 |        |

|               | 1 = Interrupt r | equest is enab<br>equest is not e | led             |                  |                  |                 |        |

| bit 7         | •               | Interrupt Enab                    |                 |                  |                  |                 |        |

|               |                 | equest is enab                    |                 |                  |                  |                 |        |

|               |                 | equest is not e                   |                 |                  |                  |                 |        |

| bit 6         | •               | ut Compare Ch                     |                 | pt Enable bit    |                  |                 |        |

|               |                 | equest is enab<br>equest is not e |                 |                  |                  |                 |        |

| bit 5         | •               | Capture Channe                    |                 | nable bit        |                  |                 |        |

| bit o         | 1 = Interrupt r | equest is enab<br>equest is not e | led             |                  |                  |                 |        |

| bit 4         | -               | A Channel 0 In                    |                 | hit              |                  |                 |        |

|               |                 | equest is enab                    | -               |                  |                  |                 |        |

|               |                 | equest is not e                   |                 |                  |                  |                 |        |

| bit 3         | T1IE: Timer1    | Interrupt Enab                    | le bit          |                  |                  |                 |        |

|               |                 | equest is enab<br>equest is not e |                 |                  |                  |                 |        |

© 2013-2015 Microchip Technology Inc.

### 8.4 Interrupt Setup Procedures

#### 8.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS (INTCON1<15>) control bit if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |

|-------|-------------------------------------------|

|       | initialized, such that all user interrupt |

|       | sources are assigned to Priority Level 4. |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

### 8.4.2 INTERRUPT SERVICE ROUTINE (ISR)

The method that is used to declare an Interrupt Service Routine (ISR) and initialize the IVT with the correct vector address will depend on the programming language (i.e., 'C' or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles; otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

### 8.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 8.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, 0Eh, with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

| R/W-0        | U-0           | R/W-0                                       | R/W-0                | R-0               | R/W-0            | R-0            | R/W-0   |

|--------------|---------------|---------------------------------------------|----------------------|-------------------|------------------|----------------|---------|

| STEN         |               | STSIDL                                      | STSRC <sup>(1)</sup> | STLOCK            | STLPOL           | STOR           | STORPOL |

| bit 15       |               |                                             |                      |                   |                  |                | bit     |

| U-0          | U-0           | R/W-0                                       | R/W-0                | R/W-0             | R/W-0            | R/W-0          | R/W-0   |

|              | _             | TUN5                                        | TUN4                 | TUN3              | TUN2             | TUN1           | TUN0    |

| bit 7        |               | ·                                           |                      |                   |                  |                | bit (   |

| Legend:      |               |                                             |                      |                   |                  |                |         |

| R = Readab   | le bit        | W = Writable                                | bit                  | U = Unimplem      | nented bit, read | as '0'         |         |

| -n = Value a | t POR         | '1' = Bit is set                            |                      | '0' = Bit is clea | ared             | x = Bit is unk | nown    |

| bit 15       | STEN: FRC     | Self-Tune Enab                              | le bit               |                   |                  |                |         |

|              |               | f-tuning is enabl                           |                      |                   | •                | hito           |         |

| bit 14       |               | f-tuning is disab<br><b>nted:</b> Read as ' |                      | may optionally    |                  | DIIS           |         |

| bit 13       | -             | C Self-Tune Sto                             |                      |                   |                  |                |         |

| bit 10       | 1 = Self-tuni | ng stops during                             | Idle mode            |                   |                  |                |         |

| bit 12       |               | ng continues du<br>C Self-Tune Ref          | -                    | ource hit(1)      |                  |                |         |

|              |               | uned to approxi                             |                      |                   | ock tolerance    |                |         |

|              |               | uned to approxi                             |                      |                   |                  | e              |         |

| bit 11       | STLOCK: FI    | RC Self-Tune Lo                             | ock Status bit       |                   |                  |                |         |

|              |               | curacy is current<br>curacy may not l       | •                    |                   |                  | •              |         |

| bit 10       | STLPOL: FF    | RC Self-Tune Lo                             | ock Interrupt Po     | larity bit        |                  | -              |         |

|              |               | ne lock interrup<br>ne lock interrup        |                      |                   |                  |                |         |

| bit 9        |               | Self-Tune Out                               | -                    |                   |                  |                |         |

|              |               | reference clock<br>reference clock          |                      |                   |                  |                | med     |

| bit 8        |               | FRC Self-Tune                               |                      | •                 | •                |                |         |

|              | 1 = A self-tu | ne out of range<br>ne out of range          | interrupt is gen     | erated when S     | TOR is = 0       |                |         |

| bit 7-6      |               | nted: Read as '                             |                      |                   |                  |                |         |

| bit 5-0      | -             | FRC Oscillator 1                            |                      |                   |                  |                |         |

|              |               | laximum freque                              | -                    |                   |                  |                |         |

|              | •             |                                             |                      |                   |                  |                |         |

|              | •             |                                             |                      |                   |                  |                |         |

|              | •<br>000001 = |                                             |                      |                   |                  |                |         |

|              |               | enter frequency                             | , oscillator is ru   | nning at factory  | calibrated free  | quency         |         |

|              | •             |                                             |                      |                   |                  |                |         |

|              | •             |                                             |                      |                   |                  |                |         |

|              | •<br>100001 = |                                             |                      |                   |                  |                |         |

|              | T0000T -      | linimum frequen                             |                      |                   |                  |                |         |

#### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

Note 1: Use of either clock recovery source has specific application requirements. For more information, see Section 9.5 "FRC Self-Tuning".

#### REGISTER 11-23: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | RP1R5 | RP1R4 | RP1R3 | RP1R2 | RP1R1 | RP1R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP0R5 | RP0R4 | RP0R3 | RP0R2 | RP0R1 | RP0R0 |

| bit 7  |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP1R<5:0>: RP1 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP1 (see Table 11-4 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | RP0R<5:0>: RP0 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP0 (see Table 11-4 for peripheral function numbers). |

#### REGISTER 11-24: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | RP3R5 | RP3R4 | RP3R3 | RP3R2 | RP3R1 | RP3R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| _      | —   | RP2R5 | RP2R4 | RP2R3 | RP2R2 | RP2R1 | RP2R0 |

| bit 7  | ·   | -     |       |       | •     | •     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP3R<5:0>:** RP3 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP3 (see Table 11-4 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP2R<5:0>:** RP2 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP2 (see Table 11-4 for peripheral function numbers).

## 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC24FJ128GB204 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Serial Peripheral Interface (SPI) with Audio Codec Support" (DS70005136) which is available from the Microchip web site (www.microchip.com).

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces. All devices in the PIC24FJ128GB204 family include three SPI modules.

The module supports operation in two Buffer modes. In Standard Buffer mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through a FIFO buffer. The FIFO level depends on the configured mode.

Variable length data can be transmitted and received, from 2 to 32 bits.

| Note: | Do not perform Read-Modify-Write opera-      |

|-------|----------------------------------------------|

|       | tions (such as bit-oriented instructions) on |

|       | the SPIxBUF register in either Standard or   |

|       | Enhanced Buffer mode.                        |

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The module also supports Audio modes. Four different Audio modes are available.

- I<sup>2</sup>S mode

- · Left Justified

- Right Justified

- PCM/DSP

In each of these modes, the serial clock is free-running and audio data is always transferred.

If an audio protocol data transfer takes place between two devices, then usually one device is the master and the other is the slave. However, audio data can be transferred between two slaves. Because the audio protocols require free-running clocks, the master can be a third party controller. In either case, the master generates two free-running clocks: SCKx and LRC (Left, Right Channel Clock/SSx/FSYNC). The SPI serial interface consists of four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

The SPI module has the ability to generate three interrupts, reflecting the events that occur during the data communication. The following types of interrupts can be generated:

- 1. Receive interrupts are signalled by SPIxRXIF. This event occurs when:

- RX watermark interrupt

- SPIROV = 1

- SPIRBF = 1

- SPIRBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 2. Transmit interrupts are signalled by SPIxTXIF. This event occurs when:

- TX watermark interrupt

- SPITUR = 1

- SPITBF = 1

- SPITBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 3. General interrupts are signalled by SPIxIF. This event occurs when

- FRMERR = 1

- SPIBUSY = 1

- SRMT = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 16-1 and Figure 16-2.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1, SPI2 or SPI3. Special Function Registers will follow a similar notation. For example, SPIxCON1L and SPIxCON1H refer to the control registers for any of the three SPI modules.

## 16.5 Audio Mode

To set up the SPIx module for the Audio mode:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- a) Write the SPIxIP<2:0> bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with AUDEN (SPIxCON1H<15>) = 1.

- 4. Clear the SPIROV bit (SPIxSTATL<6>).

- 5. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

## 16.6 Registers

The SPI module consists of the following Special Function Registers (SFRs):

- SPIxCON1L, SPIxCON1H and SPIxCON2L: SPIx Control Registers (Register 16-1 through Register 16-3)

- SPIxSTATL and SPIxSTATH: SPIx Status Registers (Register 16-4 and Register 16-5)

- SPIxBUFL and SPIxBUFH: SPIx Buffer Registers

- SPIxBRGL: SPIx Baud Rate Register

- SPIxIMSKL and SPIxIMSKH: SPIx Interrupt Mask Registers (Register 16-6 and Register 16-7)

- SPIxURDTL and SPIxURDTH: SPIx Underrun Data Registers

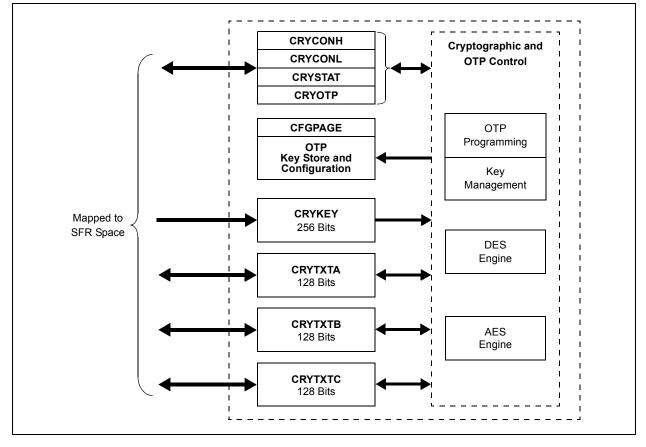

## 23.0 CRYPTOGRAPHIC ENGINE

Note: This data sheet summarizes the features of the PIC24FJ128GB204 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Cryptographic Engine" (DS70005133), which is available from the Microchip web site (www.microchip.com).

The Cryptographic Engine provides a new set of data security options. Using its own free-standing state machines, the engine can independently perform NIS standard encryption and decryption of data independently of the CPU. This eliminates the concerns of excessive CPU or program memory overhead that encryption and decryption would otherwise require, while enhancing the application's security.

The primary features of the Cryptographic Engine are:

- Memory-mapped 128-bit and 256-bit memory spaces for encryption/decryption data

- Multiple options for key storage, selection and management

- · Support for internal context saving

- · Session key encryption and loading

- · Half-duplex operation

- DES and Triple DES (3DES) encryption and decryption (64-bit block size):

- Supports 64-bit keys and 2-key or 3-key Triple DES

- AES encryption and decryption (128-bit block size):

- Supports key sizes of 128, 192 or 256 bits

- Supports ECB, CBC, CFB, OFB and CTR modes for both DES and AES standards

- Programmatically secure key storage:

- 512-bit OTP array for key storage, not readable from other memory spaces

- 32-bit Configuration Page

- Simple in-module programming interface

- Supports Key Encryption Key (KEK)

- Support for True and Psuedorandom Number Generation (PRNG), NIST SP800-90 compliant

A simplified block diagram of the Cryptographic Engine is shown in Figure 23-1.

### FIGURE 23-1: CRYPTOGRAPHIC ENGINE BLOCK DIAGRAM

#### REGISTER 24-3: CRCXORL: CRC XOR POLYNOMIAL REGISTER, LOW BYTE

| R/W-0                              | R/W-0 | R/W-0        | R/W-0             | R/W-0    | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|--------------|-------------------|----------|-----------------|-------|-------|

|                                    |       |              | Χ<                | :15:8>   |                 |       |       |

| bit 15                             |       |              |                   |          |                 |       | bit 8 |

|                                    |       |              |                   |          |                 |       |       |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0             | R/W-0    | R/W-0           | R/W-0 | U-0   |

|                                    |       |              | X<7:1>            |          |                 |       | —     |

| bit 7                              |       |              |                   |          |                 |       | bit 0 |

| Legend:                            |       |              |                   |          |                 |       |       |

| R = Readable bit W = Writable bit  |       | U = Unimplem | nented bit, read  | d as '0' |                 |       |       |

| -n = Value at POR '1' = Bit is set |       |              | '0' = Bit is clea | ared     | x = Bit is unkr | nown  |       |

bit 15-1 X<15:1>: XOR of Polynomial Term x<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '0'

#### REGISTER 24-4: CRCXORH: CRC XOR POLYNOMIAL REGISTER, HIGH BYTE

| R/W-0                             | R/W-0 | R/W-0            | R/W-0        | R/W-0             | R/W-0     | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|--------------|-------------------|-----------|-----------------|-------|

|                                   |       |                  | Χ<           | 31:24>            |           |                 |       |

| bit 15                            |       |                  |              |                   |           |                 | bit 8 |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0        | R/W-0             | R/W-0     | R/W-0           | R/W-0 |

|                                   |       |                  | Χ<           | 23:16>            |           |                 |       |

| bit 7                             |       |                  |              |                   |           |                 | bit C |

| Legend:                           |       |                  |              |                   |           |                 |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplem | nented bit, rea   | ad as '0' |                 |       |

| -n = Value at POR '1' =           |       | '1' = Bit is set |              | '0' = Bit is clea | ared      | x = Bit is unkr | nown  |

bit 15-0 X<31:16>: XOR of Polynomial Term x<sup>n</sup> Enable bits

#### REGISTER 30-3: CW3: FLASH CONFIGURATION WORD 3 (CONTINUED)

- bit 7

Reserved: Always maintain as '1'

bit 6-0

WPFP<6:0>: Write-Protected Code Segment Boundary Page bits<sup>(3)</sup>

Designates the 512 instruction words page boundary of the protected Code Segment.

If WPEND = 1:

Specifies the lower page boundary of the protected Code Segment; the last page being the last implemented page in the device.

If WPEND = 0:

Specifies the upper page boundary of the protected Code Segment; Page 0 being the lower boundary.

- **Note 1:** Regardless of WPCFG status, if WPEND = 1 or if the WPFP<6:0> bits correspond to the Configuration Word page, the Configuration Word page is protected.

- 2: Ensure that the SCLKI pin is made a digital input while using this configuration (see Table 11-1).

- 3: For the 64K devices (PIC24FJ64GB2XX), maintain WPFP6 as '0'.

- 4: This Configuration bit only takes effect when PLL is not being used.

## 31.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 31.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

| Assembly<br>Mnemonic |        | Assembly Syntax | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-----------------|------------------------------|---------------|----------------|--------------------------|

| TBLRDH               | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>  | 1             | 2              | None                     |

| TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd        | 1             | 2              | None                     |

| TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| ULNK                 | ULNK   |                 | Unlink Frame Pointer         | 1             | 1              | None                     |

| XOR                  | XOR    | f               | f = f .XOR. WREG             | 1             | 1              | N, Z                     |

|                      | XOR    | f,WREG          | WREG = f .XOR. WREG          | 1             | 1              | N, Z                     |

|                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd          | 1             | 1              | N, Z                     |

|                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws             | 1             | 1              | N, Z                     |

|                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5           | 1             | 1              | N, Z                     |

| ZE                   | ZE     | Ws,Wnd          | Wnd = Zero-Extend Ws         | 1             | 1              | C, Z, N                  |

## TABLE 32-2: INSTRUCTION SET OVERVIEW (CONTINUED)

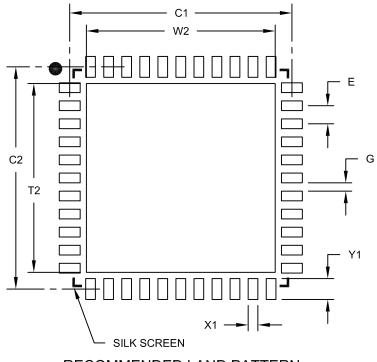

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | N N | <b>/ILLIMETER</b> | S        |      |

|----------------------------|-----|-------------------|----------|------|

| Dimension Limits           |     | MIN               | NOM      | MAX  |

| Contact Pitch E            |     |                   | 0.65 BSC |      |

| Optional Center Pad Width  | W2  |                   |          | 6.60 |

| Optional Center Pad Length | T2  |                   |          | 6.60 |

| Contact Pad Spacing        | C1  |                   | 8.00     |      |

| Contact Pad Spacing        | C2  |                   | 8.00     |      |

| Contact Pad Width (X44)    | X1  |                   |          | 0.35 |

| Contact Pad Length (X44)   | Y1  |                   |          | 0.85 |

| Distance Between Pads      | G   | 0.25              |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

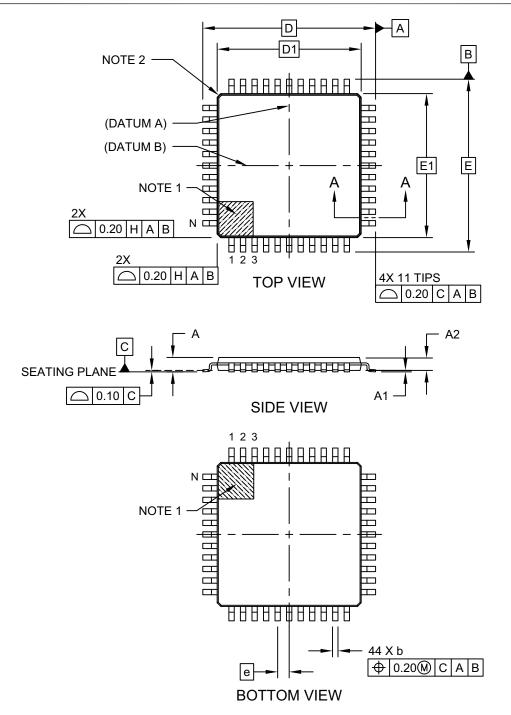

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2

### С

| C Compilers                                                                                                                                                                                  |                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPLAB XC                                                                                                                                                                                     | 404                                                                                                                                                                              |

| Charge Time Measurement Unit. See CTMU.                                                                                                                                                      |                                                                                                                                                                                  |

| Code Examples                                                                                                                                                                                |                                                                                                                                                                                  |

| Basic Clock Switching Sequence                                                                                                                                                               | 154                                                                                                                                                                              |

| Configuring UART1 Input/Output Functions                                                                                                                                                     |                                                                                                                                                                                  |

| EDS Read from Program Memory in Assembly                                                                                                                                                     |                                                                                                                                                                                  |

|                                                                                                                                                                                              |                                                                                                                                                                                  |

| EDS Read in Assembly                                                                                                                                                                         |                                                                                                                                                                                  |

| EDS Write in Assembly                                                                                                                                                                        |                                                                                                                                                                                  |

| Erasing a Program Memory Block (Assembly)                                                                                                                                                    |                                                                                                                                                                                  |

| Erasing a Program Memory Block (C Language)                                                                                                                                                  |                                                                                                                                                                                  |

| Initiating a Programming Sequence                                                                                                                                                            | 83                                                                                                                                                                               |

| Loading the Write Buffers                                                                                                                                                                    | 83                                                                                                                                                                               |

| Port Read/Write in Assembly                                                                                                                                                                  | 177                                                                                                                                                                              |

| Port Read/Write in C                                                                                                                                                                         | 177                                                                                                                                                                              |

| PWRSAV Instruction Syntax                                                                                                                                                                    |                                                                                                                                                                                  |

| Repeat Sequence                                                                                                                                                                              |                                                                                                                                                                                  |

| Setting the RTCWREN Bit                                                                                                                                                                      |                                                                                                                                                                                  |

| 5                                                                                                                                                                                            |                                                                                                                                                                                  |

| Single-Word Flash Programming                                                                                                                                                                |                                                                                                                                                                                  |

| Single-Word Flash Programming (C Language)                                                                                                                                                   |                                                                                                                                                                                  |

| Code Protection                                                                                                                                                                              |                                                                                                                                                                                  |

| Code Segment Protection                                                                                                                                                                      | 401                                                                                                                                                                              |

| Configuration Options                                                                                                                                                                        | 401                                                                                                                                                                              |

| Configuration Register Protection                                                                                                                                                            | 402                                                                                                                                                                              |

| General Segment Protection                                                                                                                                                                   |                                                                                                                                                                                  |

| Comparator Voltage Reference                                                                                                                                                                 |                                                                                                                                                                                  |

| Configuring                                                                                                                                                                                  |                                                                                                                                                                                  |

|                                                                                                                                                                                              |                                                                                                                                                                                  |

| Configuration Bits                                                                                                                                                                           |                                                                                                                                                                                  |

| Core Features                                                                                                                                                                                | 9                                                                                                                                                                                |

| CPU                                                                                                                                                                                          |                                                                                                                                                                                  |

| Arithmetic Logic Unit (ALU)                                                                                                                                                                  |                                                                                                                                                                                  |

| Control Registers                                                                                                                                                                            | 22                                                                                                                                                                               |

|                                                                                                                                                                                              | JZ                                                                                                                                                                               |

|                                                                                                                                                                                              |                                                                                                                                                                                  |

| Core Registers                                                                                                                                                                               | 30                                                                                                                                                                               |

| Core Registers<br>Programmer's Model                                                                                                                                                         | 30                                                                                                                                                                               |

| Core Registers<br>Programmer's Model<br>CRC                                                                                                                                                  | 30<br>29                                                                                                                                                                         |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation                                                                                                                           | 30<br>29<br>347                                                                                                                                                                  |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials                                                                                                            | 30<br>29<br>347<br>346                                                                                                                                                           |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials                                                                | 30<br>29<br>347<br>346<br>346                                                                                                                                                    |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation                                           | 30<br>29<br>347<br>346<br>346<br>347                                                                                                                                             |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface                         | 30<br>29<br>347<br>346<br>346<br>347<br>346                                                                                                                                      |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation                                           | 30<br>29<br>347<br>346<br>346<br>347<br>346                                                                                                                                      |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface                         | 30<br>29<br>347<br>346<br>346<br>347<br>346<br>), 329                                                                                                                            |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface<br>Cryptographic Engine | 30<br>29<br>347<br>346<br>346<br>347<br>346<br>), 329<br>335                                                                                                                     |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface<br>Cryptographic Engine | 30<br>29<br>347<br>346<br>346<br>347<br>346<br>), 329<br>335<br>330                                                                                                              |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface<br>Cryptographic Engine | 30<br>29<br>347<br>346<br>346<br>347<br>346<br>), 329<br>335<br>330<br>331                                                                                                       |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface<br>Cryptographic Engine | 30<br>29<br>347<br>346<br>346<br>347<br>346<br>), 329<br>335<br>330<br>331<br>330                                                                                                |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface<br>Cryptographic Engine | 30<br>29<br>347<br>346<br>346<br>347<br>346<br>), 329<br>335<br>330<br>331<br>330                                                                                                |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface<br>Cryptographic Engine | 30<br>29<br>347<br>346<br>346<br>347<br>346<br>), 329<br>335<br>330<br>331<br>331                                                                                                |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface<br>Cryptographic Engine | 30<br>29<br>347<br>346<br>347<br>346<br>0, 329<br>335<br>330<br>331<br>331<br>331<br>343                                                                                         |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface<br>Cryptographic Engine | 30<br>29<br>347<br>346<br>347<br>346<br>0, 329<br>335<br>330<br>331<br>331<br>343<br>343<br>342                                                                                  |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface<br>Cryptographic Engine | 30<br>29<br>347<br>346<br>346<br>347<br>346<br>0, 329<br>335<br>330<br>331<br>331<br>343<br>342<br>330                                                                           |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface<br>Cryptographic Engine | 30<br>29<br>347<br>346<br>346<br>347<br>346<br>347<br>346<br>347<br>330<br>331<br>333<br>343<br>342<br>330<br>330                                                                |

| Core Registers<br>Programmer's Model<br>CRC<br>Interrupt Operation<br>Polynomials<br>Setup Examples for 16/32-Bit Polynomials<br>Typical Operation<br>User Interface<br>Cryptographic Engine | 30<br>29<br>347<br>346<br>346<br>347<br>346<br>347<br>346<br>347<br>330<br>331<br>333<br>343<br>342<br>330<br>330                                                                |