#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SmartCard, SPI, UART/USART           |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT       |

| Number of I/O              | 34                                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 12x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

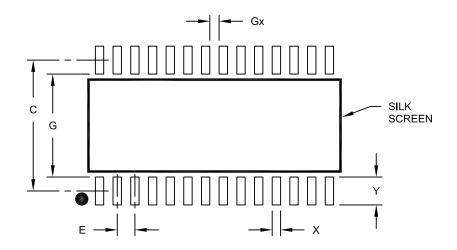

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb204-e-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14     | Bit 13     | Bit 12          | Bit 11          | Bit 10     | Bit 9      | Bit 8      | Bit 7   | Bit 6     | Bit 5     | Bit 4     | Bit 3         | Bit 2         | Bit 1         | Bit 0         | All<br>Resets |

|--------------|------|--------|------------|------------|-----------------|-----------------|------------|------------|------------|---------|-----------|-----------|-----------|---------------|---------------|---------------|---------------|---------------|

| INTCON1      | 0080 | NSTDIS | _          | —          | _               | —               | _          | —          | _          | —       | -         | -         | MATHERR   | ADDRERR       | STKERR        | OSCFAIL       | —             | 0000          |

| INTCON2      | 0082 | ALTIVT | DISI       | —          | _               | —               | _          | _          | _          | -       | —         | —         | INT4EP    | INT3EP        | INT2EP        | INT1EP        | INT0EP        | 0000          |

| IFS0         | 0084 | _      | DMA1IF     | AD1IF      | U1TXIF          | U1RXIF          | SPI1TXIF   | SPI1IF     | T3IF       | T2IF    | OC2IF     | IC2IF     | DMA0IF    | T1IF          | OC1IF         | IC1IF         | INTOIF        | 0000          |

| IFS1         | 0086 | U2TXIF | U2RXIF     | INT2IF     | T5IF            | T4IF            | OC4IF      | OC3IF      | DMA2IF     | _       | —         | —         | INT1IF    | CNIF          | CMIF          | MI2C1IF       | SI2C1IF       | 0000          |

| IFS2         | 0088 | —      | DMA4IF     | PMPIF      | —               |                 | OC6IF      | OC5IF      | IC6IF      | IC5IF   | IC4IF     | IC3IF     | DMA3IF    | CRYROLLIF     | CRYFREEIF     | SPI2TXIF      | SPI2IF        | 0000          |

| IFS3         | 008A | —      | RTCIF      | DMA5IF     | <b>SPI3RXIF</b> | SPI2RXIF        | SPI1RXIF   | —          | KEYSTRIF   | CRYDNIF | INT4IF    | INT3IF    | —         | —             | MI2C2IF       | SI2C2IF       |               | 0000          |

| IFS4         | 008C | —      | _          | CTMUIF     | —               |                 |            | _          | HLVDIF     |         | _         | —         | —         | CRCIF         | U2ERIF        | U1ERIF        |               | 0000          |

| IFS5         | 008E | —      | —          |            | —               | <b>SPI3TXIF</b> | SPI3IF     | U4TXIF     | U4RXIF     | U4ERIF  | USB1IF    | I2C2BCIF  | I2C1BCIF  | <b>U3TXIF</b> | <b>U3RXIF</b> | <b>U3ERIF</b> |               | 0000          |

| IFS6         | 0090 | —      | —          |            | —               |                 | FSTIF      | —          | _          |         | —         | —         | —         | —             | —             | —             |               | 0000          |

| IFS7         | 0092 | —      | —          |            | —               |                 |            | —          | _          |         | —         | JTAGIF    | —         | —             | —             | —             |               | 0000          |

| IEC0         | 0094 | —      | DMA1IE     | AD1IE      | U1TXIE          | U1RXIE          | SPI1TXIE   | SPI1IE     | T3IE       | T2IE    | OC2IE     | IC2IE     | DMA0IE    | T1IE          | OC1IE         | IC1IE         | <b>INTOIE</b> | 0000          |

| IEC1         | 0096 | U2TXIE | U2RXIE     | INT2IE     | T5IE            | T4IE            | OC4IE      | OC3IE      | DMA2IE     |         | _         | —         | INT1IE    | CNIE          | CMIE          | MI2C1IE       | SI2C1IE       | 0000          |

| IEC2         | 0098 | —      | DMA4IE     | PMPIE      | —               |                 | OC6IE      | OC5IE      | IC6IE      | IC5IE   | IC4IE     | IC3IE     | DMA3IE    | CRYROLLIE     | CRYFREEIE     | SPI2TXIE      | SPI2IE        | 0000          |

| IEC3         | 009A | —      | RTCIE      | DMA5IE     | <b>SPI3RXIE</b> | SPI2RXIE        | SPI1RXIE   | —          | KEYSTRIE   | CRYDNIE | INT4IE    | INT3IE    | —         | —             | MI2C2IE       | SI2C2IE       |               | 0000          |

| IEC4         | 009C | —      | —          | CTMUIE     | —               |                 |            | —          | HLVDIE     |         | —         | —         | —         | CRCIE         | U2ERIE        | U1ERIE        |               | 0000          |

| IEC5         | 009E | —      | —          |            | —               | SPI3TXIE        | SPI3IE     | U4TXIE     | U4RXIE     | U4ERIE  | USB1IE    | I2C2BCIE  | I2C1BCIE  | <b>U3TXIE</b> | <b>U3RXIE</b> | <b>U3ERIE</b> |               | 0000          |

| IEC6         | 00A0 | _      | _          | _          | _               | _               | FSTIE      | _          | _          | _       | _         | _         | _         | _             | _             | _             | _             | 0000          |

| IEC7         | 00A2 | —      |            | -          | —               | -               | -          | —          |            |         | —         | JTAGIE    | —         | _             | —             | —             | -             | 0000          |

| IPC0         | 00A4 | _      | T1IP2      | T1IP1      | T1IP0           | _               | OC1IP2     | OC1IP1     | OC1IP0     | _       | IC1IP2    | IC1IP1    | IC1IP0    | _             | INT0IP2       | INT0IP1       | INT0IP0       | 4444          |

| IPC1         | 00A6 | _      | T2IP2      | T2IP1      | T2IP0           | _               | OC2IP2     | OC2IP1     | OC2IP0     | _       | IC2IP2    | IC2IP1    | IC2IP0    | _             | DMA0IP2       | DMA0IP1       | DMA0IP0       | 4444          |

| IPC2         | 00A8 | _      | U1RXIP2    | U1RXIP1    | U1RXIP0         | _               | SPI1TXIP2  | SPI1TXIP1  | SPI1TXIP0  | _       | SPI1IP2   | SPI1IP1   | SPI1IP0   | _             | T3IP2         | T3IP1         | T3IP0         | 4444          |

| IPC3         | 00AA | _      | _          | _          | _               | _               | DMA1IP2    | DMA1IP1    | DMA1IP0    | _       | AD1IP2    | AD1IP1    | AD1IP0    | _             | U1TXIP2       | U1TXIP1       | U1TXIP0       | 0444          |

| IPC4         | 00AC | _      | CNIP2      | CNIP1      | CNIP0           | _               | CMIP2      | CMIP1      | CMIP0      | _       | MI2C1IP2  | MI2C1IP1  | MI2C1IP0  | _             | SI2C1IP2      | SI2C1IP1      | SI2C1IP0      | 4444          |

| IPC5         | 00AE | _      | _          | _          | _               | _               | _          | _          | _          | _       | _         | _         | _         | _             |               | INT1IP<2:0>   |               | 0004          |

| IPC6         | 00B0 | _      | T4IP2      | T4IP1      | T4IP0           | _               | OC4IP2     | OC4IP1     | OC4IP0     | _       | OC3IP2    | OC3IP1    | OC3IP0    | _             | DMA2IP2       | DMA2IP1       | DMA2IP0       | 4444          |

| IPC7         | 00B2 | _      | U2TXIP2    | U2TXIP1    | U2TXIP0         | _               | U2RXIP2    | U2RXIP1    | U2RXIP0    | _       | INT2IP2   | INT2IP1   | INT2IP0   | _             | T5IP2         | T5IP1         | T5IP0         | 4444          |

| IPC8         | 00B4 | _      | CRYROLLIP2 | CRYROLLIP1 | CRYROLLIP0      | _               | CRYFREEIP2 | CRYFREEIP1 | CRYFREEIP0 | _       | SPI2TXIP2 | SPI2TXIP1 | SPI2TXIP0 | _             | SPI2IP2       | SPI2IP1       | SPI2IP0       | 4444          |

| IPC9         | 00B6 | _      | IC5IP2     | IC5IP1     | IC5IP0          | _               | IC4IP2     | IC4IP1     | IC4IP0     | _       | IC3IP2    | IC3IP1    | IC3IP0    | —             | DMA3IP2       | DMA3IP1       | DMA3IP0       | 4444          |

| IPC10        | 00B8 | _      | _          | —          | _               | _               | OC6IP2     | OC6IP1     | OC6IP0     | -       | OC5IP2    | OC5IP1    | OC5IP0    | —             | IC6IP2        | IC6IP1        | IC6IP0        | 0444          |

| IPC11        | 00BA | _      | _          | —          | _               | _               | DMA4IP2    | DMA4IP1    | DMA4IP0    | -       | PMPIP2    | PMPIP1    | PMPIP0    | _             |               |               | _             | 0440          |

| IPC12        | 00BC | _      | _          | —          | —               | _               | MI2C2IP2   | MI2C2IP1   | MI2C2IP0   | —       | SI2C2IP2  | SI2C2IP1  | SI2C2IP0  | —             | —             | _             | —             | 0440          |

| IPC13        | 00BE | _      | CRYDNIP2   | CRYDNIP1   | CRYDNIP0        | —               | INT4IP2    | INT4IP1    | INT4IP0    | —       | INT3IP2   | INT3IP1   | INT3IP0   | —             | —             | _             | —             | 4440          |

| IPC14        | 00CO | _      | SPI2RXIP2  | SPI2RXIP1  | SPI2RXIP0       | _               | SPI1RXIP2  | SPI1RXIP1  | SPI1RXIP0  | —       | —         | —         | —         | —             | KEYSTRIP2     | KEYSTRIP1     | KEYSTRIP0     | 4404          |

| IPC15        | 00C2 | _      | _          | _          | _               | _               | RTCIP2     | RTCIP1     | RTCIP0     | _       | DMA5IP2   | DMA5IP1   | DMA5IP0   | _             | SPI3RXIP2     | SPI3RXIP1     | SPI3RXIP0     | 0444          |

Legend: — = unimplemented, read as '0'; r = reserved bit, maintain as '0'. Reset values are shown in hexadecimal.

#### REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 (CONTINUED)

- bit 1 SPI2TXIF: SPI2 Transmit Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SPI2IF: SPI2 General Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| U-0          | U-0                | R/W-0                               | U-0             | U-0               | U-0              | U-0             | R/W-0  |

|--------------|--------------------|-------------------------------------|-----------------|-------------------|------------------|-----------------|--------|

| _            | —                  | CTMUIF                              |                 | —                 | _                | —               | HLVDIF |

| bit 15       | ·                  |                                     |                 |                   |                  |                 | bit 8  |

|              |                    |                                     |                 |                   |                  |                 |        |

| U-0          | U-0                | U-0                                 | U-0             | R/W-0             | R/W-0            | R/W-0           | U-0    |

| —            | —                  | —                                   |                 | CRCIF             | U2ERIF           | U1ERIF          | —      |

| bit 7        |                    |                                     |                 |                   |                  |                 | bit    |

|              |                    |                                     |                 |                   |                  |                 |        |

| Legend:      |                    |                                     |                 |                   |                  |                 |        |

| R = Readab   |                    | W = Writable b                      | it              | •                 | nented bit, read |                 |        |

| -n = Value a | at POR             | '1' = Bit is set                    |                 | '0' = Bit is clea | ared             | x = Bit is unkn | own    |

|              |                    |                                     |                 |                   |                  |                 |        |

| bit 15-14    | -                  | ted: Read as '0                     |                 |                   |                  |                 |        |

| bit 13       |                    | MU Interrupt Fla                    | •               |                   |                  |                 |        |

|              |                    | request has occu<br>request has not |                 |                   |                  |                 |        |

| bit 12-9     | Unimplemen         | ted: Read as '0                     | 1               |                   |                  |                 |        |

| bit 8        | HLVDIF: High       | n/Low-Voltage D                     | etect Interrupt | t Flag Status bi  | t                |                 |        |

|              |                    | request has occu<br>request has not |                 |                   |                  |                 |        |

| bit 7-4      | Unimplemen         | ted: Read as '0                     | ,               |                   |                  |                 |        |

| bit 3        | CRCIF: CRC         | Generator Inter                     | rupt Flag State | us bit            |                  |                 |        |

|              |                    | request has occu                    |                 |                   |                  |                 |        |

|              | 0 = Interrupt      | request has not                     | occurred        |                   |                  |                 |        |

| bit 2        |                    | RT2 Error Interru                   |                 | s bit             |                  |                 |        |

|              |                    | request has occu                    |                 |                   |                  |                 |        |

|              | $\cap = interrint$ | request has not                     | occurrea        |                   |                  |                 |        |

| L:4 4        | •                  | •                                   |                 |                   |                  |                 |        |

| bit 1        | U1ERIF: UAF        | RT1 Error Interru                   |                 | s bit             |                  |                 |        |

| bit 1        | U1ERIF: UAF        | •                                   | urred           | s bit             |                  |                 |        |

### REGISTER 8-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| U-0           | R/W-0                 | R/W-0                             | R/W-0           | R/W-0             | R/W-0            | U-0             | R/W-0    |

|---------------|-----------------------|-----------------------------------|-----------------|-------------------|------------------|-----------------|----------|

|               | RTCIE                 | DMA5IE                            | SPI3RXIE        | SPI2RXIE          | SPI1RXIE         |                 | KEYSTRIE |

| bit 15        |                       |                                   |                 |                   |                  |                 | bit 8    |

|               |                       |                                   |                 |                   |                  |                 |          |

| R/W-0         | R/W-0                 | R/W-0                             | U-0             | U-0               | R/W-0            | R/W-0           | U-0      |

| CRYDNIE       | INT4IE <sup>(1)</sup> | INT3IE <sup>(1)</sup>             | —               | _                 | MI2C2IE          | SI2C2IE         | —        |

| bit 7         |                       |                                   |                 |                   |                  |                 | bit 0    |

|               |                       |                                   |                 |                   |                  |                 |          |

| Legend:       | 1.11                  |                                   |                 |                   |                  | (0)             |          |

| R = Readable  |                       | W = Writable                      | bit             | •                 | nented bit, read |                 |          |

| -n = Value at | POR                   | '1' = Bit is set                  |                 | '0' = Bit is clea | ared             | x = Bit is unki | nown     |

| bit 15        | Unimplemen            | ted: Read as '                    | )'              |                   |                  |                 |          |

| bit 14        | -                     |                                   |                 | errupt Enable b   | it               |                 |          |

| bit i i       |                       | request is enab                   |                 |                   | it i             |                 |          |

|               | •                     | equest is not e                   |                 |                   |                  |                 |          |

| bit 13        | DMA5IE: DM            | A Channel 5 In                    | terrupt Enable  | bit               |                  |                 |          |

|               |                       | equest is enab                    |                 |                   |                  |                 |          |

|               | •                     | request is not e                  |                 |                   |                  |                 |          |

| bit 12        |                       | PI3 Receive Int                   | -               | bit               |                  |                 |          |

|               |                       | equest is enab<br>equest is not e |                 |                   |                  |                 |          |

| bit 11        | •                     | PI2 Receive Int                   |                 | h it              |                  |                 |          |

| DILTI         |                       | request is enab                   | •               | DIL               |                  |                 |          |

|               | •                     | request is enab                   |                 |                   |                  |                 |          |

| bit 10        | -                     | PI1 Receive Int                   |                 | bit               |                  |                 |          |

|               |                       | equest is enab                    | •               |                   |                  |                 |          |

|               |                       | equest is not e                   |                 |                   |                  |                 |          |

| bit 9         | Unimplemen            | ted: Read as '                    | )'              |                   |                  |                 |          |

| bit 8         | KEYSTRIE: (           | Cryptographic K                   | ey Store Progr  | am Done Inter     | rupt Enable bit  |                 |          |

|               |                       | request is enab                   |                 |                   |                  |                 |          |

|               | •                     | request is not e                  |                 |                   |                  |                 |          |

| bit 7         |                       |                                   |                 | Interrupt Enable  | e bit            |                 |          |

|               |                       | equest is enab<br>equest is not e |                 |                   |                  |                 |          |

| bit 6         | -                     | nal Interrupt 4                   |                 |                   |                  |                 |          |

| DILO          |                       | request is enab                   |                 |                   |                  |                 |          |

|               | •                     | request is not e                  |                 |                   |                  |                 |          |

| bit 5         | -                     | nal Interrupt 3                   |                 |                   |                  |                 |          |

|               |                       | equest is enab                    |                 |                   |                  |                 |          |

|               | 0 = Interrupt r       | request is not e                  | nabled          |                   |                  |                 |          |

| bit 4-3       | Unimplemen            | ted: Read as '                    | )'              |                   |                  |                 |          |

| bit 2         | MI2C2IE: Ma           | ster I2C2 Even                    | t Interrupt Ena | ble bit           |                  |                 |          |

|               |                       | equest is enab                    |                 |                   |                  |                 |          |

|               | 0 = Interrupt r       | request is not e                  | nabled          |                   |                  |                 |          |

|               |                       |                                   |                 |                   |                  |                 |          |

#### REGISTER 8-16: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

**Note 1:** If an external interrupt is enabled, the interrupt input must also be configured to an available RPn or RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

#### 9.6.1 CONSIDERATIONS FOR USB OPERATION

When using the USB On-The-Go module in PIC24FJ128GB204 family devices, users must always observe these rules in configuring the system clock:

- The Oscillator modes listed in Table 9-3 are the only oscillator configurations that permit USB operation. There is no provision to provide a separate external clock source to the USB module.

- For USB operation, the selected clock source (EC, HS or XT) must meet the USB clock tolerance requirements.

- When the FRCPLL Oscillator mode is used for USB applications, the FRC self-tune system should be used as well. While the FRC is accurate, the only two ways to ensure the level of accuracy required by the *"USB 2.0 Specification"*, throughout the application's operating range, are either the self-tune system or manually changing the TUNx bits.

- The user must always ensure that the FRC source is configured to provide a frequency of 4 MHz or 8 MHz (RCDIV<2:0> = 001 or 000) and that the USB PLL prescaler is configured appropriately.

- All other Oscillator modes are available; however, USB operation is not possible when these modes are selected. They may still be useful in cases where other power levels of operation are desirable and the USB module is not needed (for example, the application is Sleeping and waiting for a bus attachment).

# 9.7 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain Oscillator modes, the device clock in the PIC24FJ128GB204 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCONL, REFOCONH and REFOTRIML registers (Register 9-4, Register 9-5 and Register 9-6). Setting the ROEN bit (REFOCONL<15>) enables the module. Setting the ROOUT bit (REFOCONL<12>) makes the clock signal available on the REFO pin.

The RODIVx bits (REFOCONH<14:0>) enable the selection of 32768 different clock divider options.

#### 9.7.1 CLOCK SOURCE REQUEST

The ROSELx bits determine different base clock sources for the module.

If the selected clock source has a global device enable (via device Configuration fuse settings), the user must enable the clock source before selecting it as a base clock source.

The ROACTIVE bit (REFOCONL<8>) synchronizes the REFO module during the turn-on and turn-off of the module.

| Note: | Once the ROEN bit is set, it should not be     |

|-------|------------------------------------------------|

|       | cleared until the ROACTIVE bit is read as '1'. |

#### 9.7.2 CLOCK SWITCHING

The base clock to the module can be switched. First, turn off the module by clearing the ROEN bit (REFOCONL<15> = 0) and wait for the ROACTIVE (REFOCONL<8>) bit to be cleared by the hardware. This avoids a glitch in the REFO output.

The ROTRIMx and RODIVx bits can be changed on-the-fly. Follow the below mentioned steps before changing the ROTRIMx and RODIVx bits.

- REFO is not actively performing the divider switch (ROSWEN = 0).

- Update the ROTRIMx and RODIVx bits with the latest values.

- · Set the ROSWEN bit.

- Wait for the ROSWEN bit to be cleared by hardware.

The ROTRIMx bits allow a fractional divisor to be added to the integer divisor, specified in the RODIVx register bits.

#### EQUATION 9-1: FRACTIONAL DIVISOR FOR ROTRIMX BITS

For RODIV<14:0> = 0, No Divide: RODIV<14:0> > 0, Period = 2 \* (RODIVx + ROTRIMx)

## 9.7.3 OPERATION IN SLEEP MODE

The ROSLP and ROSELx bits (REFOCONL<11,3:0>) control the availability of the reference output during Sleep mode.

The ROSLP bit determines if the reference source is available on the REFO pin when the device is in Sleep mode.

To use the reference clock output in Sleep mode, the ROSLP bit must be set and the reference base clock should not be the system clock or peripheral clock (ROSELx bits should not be '0b0000' or '0b0001').

The device clock must also be configured for either:

- One of the Primary modes (EC, HS or XT); the POSCEN bit should be set

- The Secondary Oscillator bit (SOSCEN) should be set

- The LPRC Oscillator

If one of the above conditions is not met, then the oscillators on OSC1, OSC2 and SOSCI will be powered down when the device enters Sleep mode.

# 10.4 Deep Sleep Mode

Deep Sleep mode provides the lowest levels of power consumption available from the instruction-based modes.

Deep Sleep modes have these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Deep Sleep mode if the WDT, or RTCC with LPRC as the clock source, is enabled.

- The dedicated Deep Sleep WDT and BOR systems, if enabled, are used.

- The RTCC and its clock source continue to run, if enabled. All other peripherals are disabled.

Entry into Deep Sleep mode is completely under software control. Exit from the Deep Sleep modes can be triggered from any of the following events:

- POR event

- MCLR event

- RTCC alarm (If the RTCC is present)

- External Interrupt 0

- Deep Sleep Watchdog Timer (DSWDT) time-out

#### 10.4.1 ENTERING DEEP SLEEP MODE

Deep Sleep mode is entered by setting the DSEN bit in the DSCON register and then executing a Sleep command (PWRSAV #SLEEP\_MODE), within one instruction cycle, to minimize the chance that Deep Sleep will be spuriously entered.

If the PWRSAV command is not given within one instruction cycle, the DSEN bit will be cleared by the hardware and must be set again by the software before entering Deep Sleep mode. The DSEN bit is also automatically cleared when exiting Deep Sleep mode.

**Note:** To re-enter Deep Sleep after a Deep Sleep wake-up, allow a delay of at least 3 TcY after clearing the RELEASE bit.

The sequence to enter Deep Sleep mode is:

- If the application requires the Deep Sleep WDT, enable it and configure its clock source. For more information on Deep Sleep WDT, see Section 10.4.5 "Deep Sleep WDT".

- If the application requires Deep Sleep BOR, enable it by programming the DSBOREN Configuration bit (CW4<6>).

- 3. If the application requires wake-up from Deep Sleep on RTCC alarm, enable and configure the RTCC module. For more information on RTCC, see Section 22.0 "Real-Time Clock and Calendar (RTCC)".

- If needed, save any critical application context data by writing it to the DSGPR0 and DSGPR1 registers (optional).

- 5. Enable Deep Sleep mode by setting the DSEN bit (DSCON<15>).

- Note: A repeat sequence is required to set the DSEN bit. The repeat sequence (repeating the instruction twice) is required to write into any of the Deep Sleep registers (DSCON, DSWAKE, DSGPR0, DSGPR1). This is required to prevent the user from entering Deep Sleep by mistake. Any write to these registers has to be done twice to actually complete the write (see Example 10-2).

- 6. Enter Deep Sleep mode by issuing 3 NOP commands and then a PWRSAV #0 instruction.

Any time the DSEN bit is set, all bits in the DSWAKE register will be automatically cleared.

#### EXAMPLE 10-2: THE REPEAT SEQUENCE

| Example 1:<br>mov #8000, w2<br>mov w2, DSCON       | ; enable DS                                        |

|----------------------------------------------------|----------------------------------------------------|

| mov w2, DSCON                                      | ; second write required to actually write to DSCON |

| Example 2:<br>bset DSCON, #15<br>nop<br>nop<br>nop |                                                    |

| bset DSCON, #15                                    | ; enable DS (two writes required)                  |

### 11.1.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 11.1.2 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, each port pin can also be individually configured for either a digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V), on any desired digital only pins, by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

# 11.2 Configuring Analog Port Pins (ANSx)

The ANSx and TRISx registers control the operation of the pins with analog function. Each port pin with analog function is associated with one of the ANSx bits (see Register 11-1 through Register 11-3), which decides if the pin function should be analog or digital. Refer to Table 11-1 for detailed behavior of the pin for different ANSx and TRISx bit settings.

When reading the PORTx register, all pins configured as analog input channels will read as cleared (a low level).

#### 11.2.1 ANALOG INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Most input pins are able to handle DC voltages of up to 5.5V, a level typical for digital logic circuits. However, several pins can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should always be avoided.

Table 11-2 summarizes the different voltage tolerances. For more information, refer to **Section 33.0 "Electrical Characteristics"** for more details.

| Pin Function   | ANSx Setting | TRISx Setting | Comments                                                                                                                                   |

|----------------|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Input   | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Analog Output  | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Digital Input  | 0            | 1             | Firmware must wait at least one instruction cycle<br>after configuring a pin as a digital input before a valid<br>input value can be read. |

| Digital Output | 0            | 0             | Make sure to disable the analog output function on the pin if any is present.                                                              |

### TABLE 11-1: CONFIGURING ANALOG/DIGITAL FUNCTION OF AN I/O PIN

#### TABLE 11-2: INPUT VOLTAGE LEVELS FOR PORT OR PIN TOLERATED DESCRIPTION INPUT

| Port or Pin                  | Tolerated Input | Description                                                       |  |  |

|------------------------------|-----------------|-------------------------------------------------------------------|--|--|

| PORTA<10:7,4> <sup>(1)</sup> |                 |                                                                   |  |  |

| PORTB<11:10,8:4>             | 5.5V            | Tolerates input levels above VDD; useful for most standard logic. |  |  |

| PORTC<9:3> <sup>(1)</sup>    |                 | for most standard logic.                                          |  |  |

| PORTA<3:0>                   |                 |                                                                   |  |  |

| PORTB<15:13,9,3:0>           | VDD             | Only VDD input levels are tolerated.                              |  |  |

| PORTC<2:0> <sup>(1)</sup>    |                 |                                                                   |  |  |

**Note 1:** Not all of these pins are implemented in 28-pin devices. Refer to **Section 1.0 "Device Overview**" for a complete description of port pin implementation.

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

| R/W-0        | R/W-0                            | R/W-0                               | R/W-0                        | U-0               | R/W-0               | R/W-0               | R/W-0         |

|--------------|----------------------------------|-------------------------------------|------------------------------|-------------------|---------------------|---------------------|---------------|

| FLTMD        | FLTOUT                           | FLTTRIEN                            | OCINV                        | —                 | DCB1 <sup>(3)</sup> | DCB0 <sup>(3)</sup> | OC32          |

| bit 15       |                                  |                                     | •                            | •                 | •                   | •                   | bit 8         |

|              |                                  |                                     |                              |                   |                     |                     |               |

| R/W-0        | R/W-0, HS                        | R/W-0                               | R/W-0                        | R/W-1             | R/W-1               | R/W-0               | R/W-0         |

| OCTRIG       | TRIGSTAT                         | OCTRIS                              | SYNCSEL4                     | SYNCSEL3          | SYNCSEL2            | SYNCSEL1            | SYNCSEL0      |

| bit 7        |                                  |                                     |                              |                   |                     |                     | bit (         |

|              |                                  |                                     |                              |                   |                     |                     |               |

| Legend:      |                                  | HS = Hardwa                         | re Settable bit              |                   |                     |                     |               |

| R = Readal   | ble bit                          | W = Writable                        | bit                          | U = Unimplen      | nented bit, read    | d as '0'            |               |

| -n = Value a | at POR                           | '1' = Bit is set                    |                              | '0' = Bit is clea | ared                | x = Bit is unkn     | nown          |

|              |                                  |                                     |                              |                   |                     |                     |               |

| bit 15       | FLTMD: Faul                      | t Mode Select I                     | oit                          |                   |                     |                     |               |

|              |                                  |                                     | ed until the Fau             | It source is ren  | noved and the       | corresponding       | OCFLT0 bit i  |

|              |                                  | n software<br>de is maintaine       | d until the Faul             | lt source is rem  | oved and a ne       | w PWM period        | etarte        |

| bit 14       | FLTOUT: Fau                      |                                     |                              |                   |                     |                     | 510/15        |

|              |                                  | put is driven hig                   | oh on a Fault                |                   |                     |                     |               |

|              |                                  | put is driven lov                   |                              |                   |                     |                     |               |

| bit 13       | FLTTRIEN: F                      | ault Output Sta                     | te Select bit                |                   |                     |                     |               |

|              |                                  |                                     | t on a Fault cor             |                   |                     |                     |               |

|              |                                  |                                     | ected by a Fau               | llt               |                     |                     |               |

| bit 12       |                                  | ut Compare x I                      | nvert bit                    |                   |                     |                     |               |

|              | 1 = OCx outp                     | ut is inverted<br>ut is not inverte | d                            |                   |                     |                     |               |

| bit 11       | •                                | ted: Read as '                      |                              |                   |                     |                     |               |

| bit 10-9     | •                                |                                     | e Least Signific             | ant hite(3)       |                     |                     |               |

| DIL 10-9     |                                  |                                     | e by $\frac{3}{4}$ of the ir |                   | <b>`</b>            |                     |               |

|              |                                  |                                     | e by $\frac{1}{2}$ of the ir |                   |                     |                     |               |

|              |                                  |                                     | e by ¼ of the in             |                   |                     |                     |               |

|              |                                  |                                     | s at the start of            |                   | -                   |                     |               |

| bit 8        |                                  |                                     | odules Enable b              | oit (32-bit opera | ation)              |                     |               |

|              |                                  | module operati<br>module operati    |                              |                   |                     |                     |               |

| bit 7        |                                  | -                                   | Trigger/Sync S               | Select hit        |                     |                     |               |

|              |                                  |                                     | ource designate              |                   | CSELx bits          |                     |               |

|              |                                  |                                     | the source desi              |                   |                     | s                   |               |

| bit 6        | TRIGSTAT: ⊺                      | imer Trigger St                     | atus bit                     |                   |                     |                     |               |

|              |                                  |                                     | riggered and is              | •                 |                     |                     |               |

|              |                                  |                                     | en triggered an              | -                 |                     |                     |               |

| bit 5        |                                  |                                     | Output Pin Dir               | ection Select b   | vit                 |                     |               |

|              | 1 = OCx pin is<br>0 = Output Co  |                                     | eral x is connec             | ted to an OCx     | pin                 |                     |               |

|              | Never use an OC                  | x module as its                     |                              |                   | -                   | mode or anothe      | er equivalent |

|              | SYNCSELx settir Use these inputs | -                                   | ces only and n               | aver se evine or  |                     |                     |               |

| 2:           |                                  | as ingger sour                      | Ces only and the             | ever as sync st   |                     |                     |               |

3: The DCB<1:0> bits are double-buffered in PWM modes only (OCM<2:0> (OCxCON1<2:0>) = 111, 110).

#### 19.7.1 USB OTG MODULE CONTROL REGISTERS

# REGISTER 19-3: U10TGSTAT: USB OTG STATUS REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   |     | -   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| R-0, HSC | U-0 | R-0, HSC | U-0 | R-0, HSC | R-0, HSC | U-0 | R-0, HSC |

|----------|-----|----------|-----|----------|----------|-----|----------|

| ID       | —   | LSTATE   | —   | SESVD    | SESEND   | —   | VBUSVD   |

| bit 7    |     |          |     |          |          |     | bit 0    |

| Legend:           | U = Unimplemented bit, read as '0' |                                         |  |  |  |  |

|-------------------|------------------------------------|-----------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                   | HSC = Hardware Settable/Clearable bit   |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                   |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | ID: ID Pin State Indicator bit                                                                                                                                                               |

|          | <ul> <li>1 = No plug is attached or a Type B cable has been plugged into the USB receptacle</li> <li>0 = A Type A plug has been plugged into the USB receptacle</li> </ul>                   |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                   |

| bit 5    | LSTATE: Line State Stable Indicator bit                                                                                                                                                      |

|          | <ul> <li>1 = The USB line state (as defined by SE0 and JSTATE) has been stable for the previous 1 ms</li> <li>0 = The USB line state has not been stable for the previous 1 ms</li> </ul>    |

| bit 4    | Unimplemented: Read as '0'                                                                                                                                                                   |

| bit 3    | SESVD: Session Valid Indicator bit                                                                                                                                                           |

|          | <ul> <li>1 = The VBUS voltage is above VA_SESS_VLD (as defined in the "USB 2.0 Specification") on the A or<br/>B-device</li> </ul>                                                           |

|          | 0 = The VBUS voltage is below VA_SESS_VLD on the A or B-device                                                                                                                               |

| bit 2    | SESEND: B Session End Indicator bit                                                                                                                                                          |

|          | <ul> <li>1 = The VBUS voltage is below VB_SESS_END (as defined in the "USB 2.0 Specification") on the B-device</li> <li>0 = The VBUS voltage is above VB_SESS_END on the B-device</li> </ul> |

| bit 1    | Unimplemented: Read as '0'                                                                                                                                                                   |

| bit 0    | VBUSVD: A VBUS Valid Indicator bit                                                                                                                                                           |

|          | <ul> <li>1 = The VBUS voltage is above VA_VBUS_VLD (as defined in the "USB 2.0 Specification") on the A-device</li> <li>0 = The VBUS voltage is below VA_VBUS_VLD on the A-device</li> </ul> |

|          |                                                                                                                                                                                              |

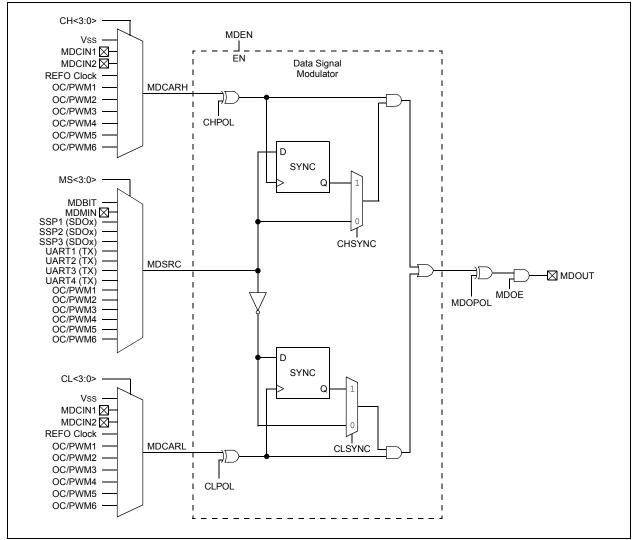

# 20.0 DATA SIGNAL MODULATOR (DSM)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Data Signal Modulator (DSM)" (DS39744). The information in this data sheet supersedes the information in the FRM.

The Data Signal Modulator (DSM) allows the user to mix a digital data stream (the "modulator signal") with a carrier signal to produce a modulated output. Both the carrier and the modulator signals are supplied to the DSM module, either internally from the output of a peripheral, or externally through an input pin. The modulated output signal is generated by performing a logical AND operation of both the carrier and modulator signals, and then it is provided to the MDOUT pin. Using this method, the DSM can generate the following types of key modulation schemes:

- Frequency Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Figure 20-1 shows a simplified block diagram of the Data Signal Modulator peripheral.

#### FIGURE 20-1: SIMPLIFIED BLOCK DIAGRAM OF THE DATA SIGNAL MODULATOR

# 23.1 Data Register Spaces

There are four register spaces used for cryptographic data and key storage:

- CRYTXTA

- CRYTXTB

- CRYTXTC

- CRYKEY

Although mapped into the SFR space, all of these Data Spaces are actually implemented as 128-bit or 256-bit wide arrays, rather than groups of 16-bit wide Data registers. Reads and writes to and from these arrays are automatically handled as if they were any other register in the SFR space.

CRYTXTA through CRYTXTC are 128-bit wide spaces; they are used for writing data to and reading from the Cryptographic Engine. Additionally, they are also used for storing intermediate results of the encryption/decryption operation. None of these registers may be written to when the module is performing an operation (CRYGO = 1).

CRYTXTA and CRYTXTB normally serve as inputs to the encryption/decryption process.

CRYTXTA usually contains the initial plaintext or ciphertext to be encrypted or decrypted. Depending on the mode of operation, CRYTXTB may contain the ciphertext output or intermediate cipher data. It may also function as a programmable length counter in certain operations.

CRYTXTC is primarily used to store the final output of an encryption/decryption operation. It is also used as the input register for data to be programmed to the secure OTP array.

CRYKEY is a 256-bit wide space, used to store cryptographic keys for the selected operation. It is writable from both the SFR space and the secure OTP array. Although mapped into the SFR space, it is a write-only memory area; any data placed here, regardless of its source, cannot be read back by any run-time operations. This feature helps to ensure the security of any key data.

## 23.2 Modes of Operation

The Cryptographic Engine supports the following modes of operation, determined by the OPMOD<3:0> bits:

- Block Encryption

- Block Decryption

- AES Decryption Key Expansion

- Random Number Generation

- Session Key Generation

- Session Key Encryption

- Session Key Loading

The OPMODx bits may be changed while CRYON is set. They should only be changed when a cryptographic operation is not being done (CRYGO = 0).

Once the encryption operation, and the appropriate and valid key configuration is selected, the operation is performed by setting the CRYGO bit. This bit is automatically cleared by hardware when the operation is complete. The CRYGO bit can also be manually cleared by software; this causes any operation in progress to terminate immediately. Clearing this bit in software also sets the CRYABRT bit (CRYSTAT<5>).

For most operations, CRYGO can only be set when an OTP operation is not being performed and there are no other error conditions. CRYREAD, CRYWR, CRYABRT, ROLLOVR, MODFAIL and KEYFAIL must all be '0'.

Setting CRYWR and CRYGO simultaneously will not initiate an OTP programming operation or any other operation. Setting CRYGO when the module is disabled (CRYON = 0) also has no effect.

# 23.3 Enabling the Engine

The Cryptographic Engine is enabled by setting the CRYON bit. Clearing this bit disables both the DES and AES engines, as well as causing the following register bits to be held in Reset:

- CRYGO (CRYCONL<8>)

- TXTABSY (CRYSTAT<6>)

- CRYWR (CRYOTP<0>)

All other register bits and registers may be read and written while CRYON = 0.

### 23.4 Operation During Sleep and Idle Modes

#### 23.4.1 OPERATION DURING SLEEP MODES

Whenever the device enters any Sleep or Deep Sleep mode, all operation engine state machines are reset. This feature helps to preserve the integrity, or any data being encrypted or decrypted, by discarding any intermediate text that might be used to break the key.

Any OTP programming operations under way when a Sleep mode is entered are also halted. Depending on what is being programmed, this may result in permanent loss of a memory location or potentially, the use of the entire secure OTP array. Users are advised to perform OTP programming only when entry into power-saving modes is disabled.

### 23.4.2 OPERATION DURING IDLE MODE

When the CRYSIDL bit (CRYCONL<13>) is '0', the engine will continue any ongoing operations without interruption when the device enters Idle mode.

When CRYSIDL is '1', the module behaves as in Sleep modes.

**Note:** OTP programming errors, regardless of the source, are not recoverable errors. Users should ensure that all foreseeable interruptions to the programming operation, including device interrupts and entry into power-saving modes, are disabled.

### REGISTER 25-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

- bit 1 SAMP: ADC1 Sample Enable bit 1 = A/D Sample-and-Hold amplifiers are sampling 0 = A/D Sample-and-Hold amplifiers are holding

- bit 0 DONE: ADC1 Conversion Status bit 1 = A/D conversion cycle has completed 0 = A/D conversion cycle has not started or is in progress

- Note 1: This bit is only available when Extended DMA/Buffer features are available (DMAEN = 1).

| R/W-0         | R/W-0                          | R/W-0                                 | R/W-0           | U-0                               | U-0              | R/W-0              | R/W-0           |

|---------------|--------------------------------|---------------------------------------|-----------------|-----------------------------------|------------------|--------------------|-----------------|

| ASEN          | LPEN                           | CTMREQ                                | BGREQ           |                                   |                  | ASINT1             | ASINT0          |

| bit 15        |                                |                                       |                 |                                   |                  |                    | bit 8           |

| U-0           | U-0                            | U-0                                   | U-0             | R/W-0                             | R/W-0            | R/W-0              | R/W-0           |

| 0-0           | 0-0                            | 0-0                                   | 0-0             | WM1                               | WM0              | CM1                | CM0             |

| <br>bit 7     |                                | _                                     |                 | VVIVII                            | VIVIO            | CIVIT              | bit 0           |

|               |                                |                                       |                 |                                   |                  |                    |                 |

| Legend:       |                                |                                       |                 |                                   |                  |                    |                 |

| R = Readabl   | e bit                          | W = Writable                          | oit             | U = Unimplem                      | ented bit, rea   | d as '0'           |                 |

| -n = Value at | POR                            | '1' = Bit is set                      |                 | '0' = Bit is clea                 | ared             | x = Bit is unkr    | lown            |

| bit 15        | ASEN: Auto-S                   | Scan Enable bi                        | :               |                                   |                  |                    |                 |

|               | 1 = Auto-scan<br>0 = Auto-scan |                                       |                 |                                   |                  |                    |                 |

| oit 14        | LPEN: Low-P                    | ower Enable bi                        | t               |                                   |                  |                    |                 |

|               |                                | er is enabled aft<br>r is enabled aft |                 |                                   |                  |                    |                 |

| bit 13        | CTMREQ: CT                     | MU Request b                          | it              |                                   |                  |                    |                 |

|               |                                | enabled when t<br>not enabled by      |                 | oled and active                   |                  |                    |                 |

| bit 12        | BGREQ: Ban                     | d Gap Request                         | bit             |                                   |                  |                    |                 |

|               |                                | is enabled whe                        |                 | nabled and acti                   | ve               |                    |                 |

| bit 11-10     | Unimplement                    | ted: Read as '                        | )'              |                                   |                  |                    |                 |

| bit 9-8       | ASINT<1:0>:                    | Auto-Scan (Th                         | reshold Detect  | i) Interrupt Mod                  | e bits           |                    |                 |

|               | 10 = Interrupt                 | after valid com<br>after Threshol     | pare has occu   |                                   |                  | npare has occu     | rred            |

| bit 7-4       | Unimplement                    | ted: Read as '                        | )'              |                                   |                  |                    |                 |

| bit 3-2       | WM<1:0>: Wr                    | rite Mode bits                        |                 |                                   |                  |                    |                 |

|               | 11 = Reserve                   |                                       |                 |                                   |                  |                    |                 |

|               |                                |                                       |                 | s are not saved<br>and ASINTx bit |                  | s are generated    | d when a valid  |

|               |                                |                                       |                 |                                   |                  | etermined by th    | e reaister bits |

|               | when a r                       | match occurs, a                       | as defined by t | he CMx bits)                      |                  |                    |                 |

|               |                                |                                       |                 | saved to a loca                   | tion determine   | ed by the buffer   | register bits)  |

| bit 1-0       |                                | mpare Mode bi                         |                 |                                   |                  |                    |                 |

|               |                                | Window mode<br>by the correspo        |                 |                                   | conversion res   | sult is outside of | of the window   |

|               | 10 = Inside W                  |                                       | alid match occ  | ,                                 | ersion result is | inside the wind    | low defined by  |

|               |                                | Than mode (va                         |                 | rs if the result is               | greater than t   | he value in the    | corresponding   |

|               |                                | an mode (valid                        | match occurs i  | f the result is lea               | ss than the val  | ue in the corres   | ponding buffer  |

#### REGISTER 25-8: AD1CHITL: ADC1 SCAN COMPARE HIT REGISTER (LOW WORD)

| U-0                    | U-0           | U-0                                   | R/W-0                   | R/W-0             | R/W-0                | R/W-0           | U-0   |

|------------------------|---------------|---------------------------------------|-------------------------|-------------------|----------------------|-----------------|-------|

| _                      | _             | _                                     |                         | CHH<              | 12:9> <sup>(1)</sup> |                 | _     |

| bit 15                 |               |                                       |                         |                   |                      |                 | bit 8 |

|                        |               |                                       |                         |                   |                      |                 |       |

| R/W-0                  | R/W-0         | R/W-0                                 | R/W-0                   | R/W-0             | R/W-0                | R/W-0           | R/W-0 |

|                        |               |                                       | CHH                     | <7:0>             |                      |                 |       |

| bit 7                  |               |                                       |                         |                   |                      |                 | bit C |

| 1                      |               |                                       |                         |                   |                      |                 |       |

| Legend:<br>R = Readabl | le bit        | W = Writable bit                      |                         | U = Unimplen      | nented bit. rea      | ad as '0'       |       |

| -n = Value at          | t POR         | '1' = Bit is set                      |                         | '0' = Bit is clea |                      | x = Bit is unkn | own   |

|                        |               |                                       |                         |                   |                      |                 | -     |

| bit 15-13              | Unimplemen    | ted: Read as '0'                      |                         |                   |                      |                 |       |

| bit 12-9               | CHH<12:9>:    | ADC1 Compare I                        | Hit bits <sup>(1)</sup> |                   |                      |                 |       |

|                        | If CM<1:0> =  | 11:                                   |                         |                   |                      |                 |       |

|                        |               | It Buffer n has be                    |                         |                   | atch has occu        | rred            |       |

|                        |               | It Buffer n has no                    |                         | n with data       |                      |                 |       |

|                        |               | Values of CM<1:0<br>has occurred on A |                         | hannol n          |                      |                 |       |

|                        |               | has occurred on P                     |                         |                   |                      |                 |       |

| bit 8                  | Unimplemen    | ted: Read as '0'                      |                         |                   |                      |                 |       |

| bit 7-0                | CHH<8:0>: A   | ADC1 Compare Hi                       | it bits                 |                   |                      |                 |       |

|                        | If CM<1:0> =  | 11:                                   |                         |                   |                      |                 |       |

|                        |               | ult Buffer n has be                   |                         |                   | atch has occu        | rred            |       |

|                        |               | It Buffer n has no                    |                         | n with data       |                      |                 |       |

|                        |               | Values of CM<1:0<br>has occurred on A |                         | hannal n          |                      |                 |       |

|                        |               | has occurred on A                     |                         |                   |                      |                 |       |

|                        |               |                                       |                         |                   |                      |                 |       |

| Note 4. T              | ha 0111140.40 | In the second construction of a       |                         | •                 |                      |                 |       |

Note 1: The CHH<12:10> bits are unimplemented in 28-pin devices, read as '0'.

### 31.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 31.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# 32.0 INSTRUCTION SET SUMMARY

**Note:** This chapter is a brief summary of the PIC24F Instruction Set Architecture (ISA) and is not intended to be a comprehensive reference source.

The PIC24F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from previous PIC MCU instruction sets. Most instructions are a single program memory word. Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction. The instruction set is highly orthogonal and is grouped into four basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

Table 32-1 shows the general symbols used in describing the instructions. The PIC24F instruction set summary in Table 32-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register, 'Wb', without any address modifier

- The second source operand, which is typically a register, 'Ws', with or without an address modifier

- The destination of the result, which is typically a register, 'Wd', with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value, 'f'

- The destination, which could either be the file register, 'f', or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register, 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register, 'Wb', without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register, 'Wd', with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the Table Read and Table Write instructions

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all Table Reads and Table Writes, and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles.

Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

# 33.2 AC Characteristics and Timing Parameters

The information contained in this section defines the PIC24FJ128GB204 family AC characteristics and timing parameters.

#### TABLE 33-18: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)          |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial    |  |  |  |  |  |

| AC CHARACTERISTICS | $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended                           |  |  |  |  |  |

|                    | Operating voltage VDD range as described in Section 33.1 "DC Characteristics". |  |  |  |  |  |

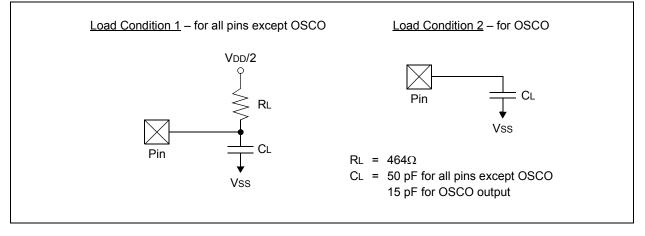

#### FIGURE 33-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 33-19: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                                         |

|--------------|--------|-----------------------|-----|--------------------|-----|-------|--------------------------------------------------------------------|

| DO50         | Cosco  | OSCO/CLKO Pin         | _   | —                  | 15  | pF    | In XT and HS modes when<br>external clock is used to drive<br>OSCI |

| DO56         | Сю     | All I/O Pins and OSCO | —   | —                  | 50  | pF    | EC mode                                                            |

| DO58         | Св     | SCLx, SDAx            | —   | —                  | 400 | pF    | In I <sup>2</sup> C™ mode                                          |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.