Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SmartCard, SPI, UART/USART            |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT        |

| Number of I/O              | 34                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 12x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

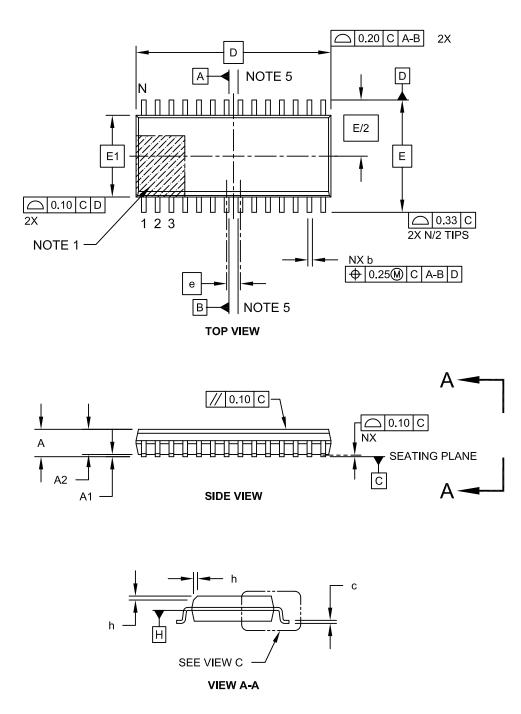

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb204t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14     | Bit 13     | Bit 12          | Bit 11          | Bit 10     | Bit 9      | Bit 8      | Bit 7   | Bit 6     | Bit 5     | Bit 4     | Bit 3         | Bit 2         | Bit 1         | Bit 0         | All<br>Resets |

|--------------|------|--------|------------|------------|-----------------|-----------------|------------|------------|------------|---------|-----------|-----------|-----------|---------------|---------------|---------------|---------------|---------------|

| INTCON1      | 0080 | NSTDIS | _          | —          | _               | —               | _          | —          | _          | —       | -         | -         | MATHERR   | ADDRERR       | STKERR        | OSCFAIL       | —             | 0000          |

| INTCON2      | 0082 | ALTIVT | DISI       | —          | _               | —               | _          | _          | _          | -       | —         | —         | INT4EP    | INT3EP        | INT2EP        | INT1EP        | INT0EP        | 0000          |

| IFS0         | 0084 | _      | DMA1IF     | AD1IF      | U1TXIF          | U1RXIF          | SPI1TXIF   | SPI1IF     | T3IF       | T2IF    | OC2IF     | IC2IF     | DMA0IF    | T1IF          | OC1IF         | IC1IF         | INTOIF        | 0000          |

| IFS1         | 0086 | U2TXIF | U2RXIF     | INT2IF     | T5IF            | T4IF            | OC4IF      | OC3IF      | DMA2IF     | -       | —         | —         | INT1IF    | CNIF          | CMIF          | MI2C1IF       | SI2C1IF       | 0000          |

| IFS2         | 0088 | —      | DMA4IF     | PMPIF      | —               |                 | OC6IF      | OC5IF      | IC6IF      | IC5IF   | IC4IF     | IC3IF     | DMA3IF    | CRYROLLIF     | CRYFREEIF     | SPI2TXIF      | SPI2IF        | 0000          |

| IFS3         | 008A | —      | RTCIF      | DMA5IF     | <b>SPI3RXIF</b> | SPI2RXIF        | SPI1RXIF   | —          | KEYSTRIF   | CRYDNIF | INT4IF    | INT3IF    | —         | —             | MI2C2IF       | SI2C2IF       |               | 0000          |

| IFS4         | 008C | —      | _          | CTMUIF     | —               |                 |            | _          | HLVDIF     |         | _         | —         | —         | CRCIF         | U2ERIF        | U1ERIF        |               | 0000          |

| IFS5         | 008E | —      | —          |            | —               | <b>SPI3TXIF</b> | SPI3IF     | U4TXIF     | U4RXIF     | U4ERIF  | USB1IF    | I2C2BCIF  | I2C1BCIF  | <b>U3TXIF</b> | <b>U3RXIF</b> | <b>U3ERIF</b> |               | 0000          |

| IFS6         | 0090 | —      | —          |            | —               |                 | FSTIF      | —          | _          |         | —         | —         | —         | —             | —             | —             |               | 0000          |

| IFS7         | 0092 | —      | —          |            | —               |                 |            | —          | _          |         | —         | JTAGIF    | —         | —             | —             | —             |               | 0000          |

| IEC0         | 0094 | —      | DMA1IE     | AD1IE      | U1TXIE          | U1RXIE          | SPI1TXIE   | SPI1IE     | T3IE       | T2IE    | OC2IE     | IC2IE     | DMA0IE    | T1IE          | OC1IE         | IC1IE         | <b>INTOIE</b> | 0000          |

| IEC1         | 0096 | U2TXIE | U2RXIE     | INT2IE     | T5IE            | T4IE            | OC4IE      | OC3IE      | DMA2IE     |         | _         | —         | INT1IE    | CNIE          | CMIE          | MI2C1IE       | SI2C1IE       | 0000          |

| IEC2         | 0098 | —      | DMA4IE     | PMPIE      | —               |                 | OC6IE      | OC5IE      | IC6IE      | IC5IE   | IC4IE     | IC3IE     | DMA3IE    | CRYROLLIE     | CRYFREEIE     | SPI2TXIE      | SPI2IE        | 0000          |

| IEC3         | 009A | —      | RTCIE      | DMA5IE     | <b>SPI3RXIE</b> | SPI2RXIE        | SPI1RXIE   | —          | KEYSTRIE   | CRYDNIE | INT4IE    | INT3IE    | —         | —             | MI2C2IE       | SI2C2IE       |               | 0000          |

| IEC4         | 009C | —      | —          | CTMUIE     | —               |                 |            | —          | HLVDIE     |         | —         | —         | —         | CRCIE         | U2ERIE        | U1ERIE        |               | 0000          |

| IEC5         | 009E | —      | —          |            | —               | SPI3TXIE        | SPI3IE     | U4TXIE     | U4RXIE     | U4ERIE  | USB1IE    | I2C2BCIE  | I2C1BCIE  | <b>U3TXIE</b> | <b>U3RXIE</b> | <b>U3ERIE</b> |               | 0000          |

| IEC6         | 00A0 | _      | _          | _          | _               | _               | FSTIE      | _          | _          | _       | _         | _         | _         | _             | _             | _             | _             | 0000          |

| IEC7         | 00A2 | —      |            | -          | —               | -               | -          | —          |            |         | —         | JTAGIE    | —         | _             | —             | —             | -             | 0000          |

| IPC0         | 00A4 | _      | T1IP2      | T1IP1      | T1IP0           | _               | OC1IP2     | OC1IP1     | OC1IP0     | _       | IC1IP2    | IC1IP1    | IC1IP0    | _             | INT0IP2       | INT0IP1       | INT0IP0       | 4444          |

| IPC1         | 00A6 | _      | T2IP2      | T2IP1      | T2IP0           | _               | OC2IP2     | OC2IP1     | OC2IP0     | _       | IC2IP2    | IC2IP1    | IC2IP0    | _             | DMA0IP2       | DMA0IP1       | DMA0IP0       | 4444          |

| IPC2         | 00A8 | _      | U1RXIP2    | U1RXIP1    | U1RXIP0         | _               | SPI1TXIP2  | SPI1TXIP1  | SPI1TXIP0  | _       | SPI1IP2   | SPI1IP1   | SPI1IP0   | _             | T3IP2         | T3IP1         | T3IP0         | 4444          |

| IPC3         | 00AA | _      | _          | _          | _               | _               | DMA1IP2    | DMA1IP1    | DMA1IP0    | _       | AD1IP2    | AD1IP1    | AD1IP0    | _             | U1TXIP2       | U1TXIP1       | U1TXIP0       | 0444          |

| IPC4         | 00AC | _      | CNIP2      | CNIP1      | CNIP0           | _               | CMIP2      | CMIP1      | CMIP0      | _       | MI2C1IP2  | MI2C1IP1  | MI2C1IP0  | _             | SI2C1IP2      | SI2C1IP1      | SI2C1IP0      | 4444          |

| IPC5         | 00AE | _      | _          | _          | _               | _               | _          | _          | _          | _       | _         | _         | _         | _             |               | INT1IP<2:0>   |               | 0004          |

| IPC6         | 00B0 | _      | T4IP2      | T4IP1      | T4IP0           | _               | OC4IP2     | OC4IP1     | OC4IP0     | _       | OC3IP2    | OC3IP1    | OC3IP0    | _             | DMA2IP2       | DMA2IP1       | DMA2IP0       | 4444          |

| IPC7         | 00B2 | _      | U2TXIP2    | U2TXIP1    | U2TXIP0         | _               | U2RXIP2    | U2RXIP1    | U2RXIP0    | _       | INT2IP2   | INT2IP1   | INT2IP0   | _             | T5IP2         | T5IP1         | T5IP0         | 4444          |

| IPC8         | 00B4 | _      | CRYROLLIP2 | CRYROLLIP1 | CRYROLLIP0      | _               | CRYFREEIP2 | CRYFREEIP1 | CRYFREEIP0 | _       | SPI2TXIP2 | SPI2TXIP1 | SPI2TXIP0 | _             | SPI2IP2       | SPI2IP1       | SPI2IP0       | 4444          |

| IPC9         | 00B6 | _      | IC5IP2     | IC5IP1     | IC5IP0          | _               | IC4IP2     | IC4IP1     | IC4IP0     | _       | IC3IP2    | IC3IP1    | IC3IP0    | —             | DMA3IP2       | DMA3IP1       | DMA3IP0       | 4444          |

| IPC10        | 00B8 | _      | _          | —          | _               | _               | OC6IP2     | OC6IP1     | OC6IP0     |         | OC5IP2    | OC5IP1    | OC5IP0    | —             | IC6IP2        | IC6IP1        | IC6IP0        | 0444          |

| IPC11        | 00BA | _      | _          | —          | _               | _               | DMA4IP2    | DMA4IP1    | DMA4IP0    |         | PMPIP2    | PMPIP1    | PMPIP0    | _             |               |               | _             | 0440          |

| IPC12        | 00BC | _      | _          | —          | —               | _               | MI2C2IP2   | MI2C2IP1   | MI2C2IP0   | —       | SI2C2IP2  | SI2C2IP1  | SI2C2IP0  | —             | —             | _             | —             | 0440          |

| IPC13        | 00BE | _      | CRYDNIP2   | CRYDNIP1   | CRYDNIP0        | —               | INT4IP2    | INT4IP1    | INT4IP0    | —       | INT3IP2   | INT3IP1   | INT3IP0   | —             | —             | _             | —             | 4440          |

| IPC14        | 00CO | _      | SPI2RXIP2  | SPI2RXIP1  | SPI2RXIP0       | _               | SPI1RXIP2  | SPI1RXIP1  | SPI1RXIP0  | —       | —         | —         | —         | —             | KEYSTRIP2     | KEYSTRIP1     | KEYSTRIP0     | 4404          |

| IPC15        | 00C2 | _      | _          | _          | _               | _               | RTCIP2     | RTCIP1     | RTCIP0     | _       | DMA5IP2   | DMA5IP1   | DMA5IP0   | _             | SPI3RXIP2     | SPI3RXIP1     | SPI3RXIP0     | 0444          |

Legend: — = unimplemented, read as '0'; r = reserved bit, maintain as '0'. Reset values are shown in hexadecimal.

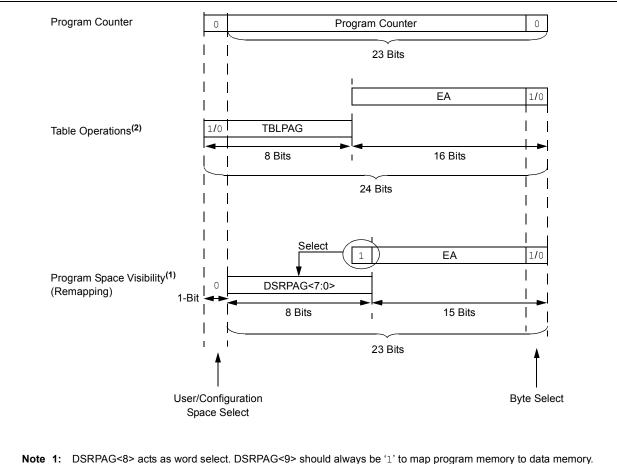

2: The instructions, TBLRDH/TBLWTH/TBLRDL/TBLWTL, decide if the higher or lower word of program memory is accessed. TBLRDH/TBLWTH instructions access the higher word and TBLRDL/TBLWTL instructions access the lower word. Table read operations are permitted in the configuration memory space.

**IFS2: INTERRUPT FLAG STATUS REGISTER 2**

**REGISTER 8-7:**

| U-0              | R/W-0                                                                                                  | R/W-0                                                 | U-0              | U-0               | R/W-0            | R/W-0            | R/W-0  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-------------------|------------------|------------------|--------|--|--|--|--|--|

| _                | DMA4IF                                                                                                 | PMPIF                                                 | —                | —                 | OC6IF            | OC5IF            | IC6IF  |  |  |  |  |  |

| bit 15           |                                                                                                        |                                                       |                  |                   |                  |                  | bit 8  |  |  |  |  |  |

|                  |                                                                                                        |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| R/W-0            | R/W-0                                                                                                  | R/W-0                                                 | R/W-0            | R/W-0             | R/W-0            | R/W-0            | R/W-0  |  |  |  |  |  |

| IC5IF            | IC4IF                                                                                                  | IC3IF                                                 | DMA3IF           | CRYROLLIF         | CRYFREEIF        | SPI2TXIF         | SPI2IF |  |  |  |  |  |

| bit 7            |                                                                                                        |                                                       |                  |                   |                  |                  | bit 0  |  |  |  |  |  |

|                  |                                                                                                        |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| Legend:          |                                                                                                        |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| R = Readabl      |                                                                                                        | W = Writable                                          |                  | •                 | nented bit, read |                  |        |  |  |  |  |  |

| -n = Value at    | PUR                                                                                                    | '1' = Bit is set                                      |                  | '0' = Bit is clea | ared             | x = Bit is unkno | nwc    |  |  |  |  |  |

| bit 15           | Unimplemen                                                                                             | nted: Read as '                                       | ר <b>י</b>       |                   |                  |                  |        |  |  |  |  |  |

| bit 14           | -                                                                                                      | IA Channel 4 In                                       |                  | tatus hit         |                  |                  |        |  |  |  |  |  |

| л 1 <del>4</del> |                                                                                                        | request has occ                                       |                  |                   |                  |                  |        |  |  |  |  |  |

|                  |                                                                                                        | request has not                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| bit 13           | PMPIF: Para                                                                                            | PMPIF: Parallel Master Port Interrupt Flag Status bit |                  |                   |                  |                  |        |  |  |  |  |  |

|                  | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

|                  | •                                                                                                      | •                                                     |                  |                   |                  |                  |        |  |  |  |  |  |

| oit 12-11        | -                                                                                                      | nted: Read as '                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| pit 10           | <b>OC6IF:</b> Output Compare Channel 6 Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

|                  |                                                                                                        | 0 = Interrupt request has not occurred                |                  |                   |                  |                  |        |  |  |  |  |  |

| bit 9            | OC5IF: Output Compare Channel 5 Interrupt Flag Status bit                                              |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

|                  | 1 = Interrupt                                                                                          | request has occ                                       | curred           |                   |                  |                  |        |  |  |  |  |  |

|                  |                                                                                                        | request has not                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| bit 8            | IC6IF: Input Capture Channel 6 Interrupt Flag Status bit                                               |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

|                  | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| bit 7            | IC5IF: Input Capture Channel 5 Interrupt Flag Status bit                                               |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

|                  | 1 = Interrupt request has occurred                                                                     |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

|                  |                                                                                                        | request has not                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| bit 6            | IC4IF: Input (                                                                                         | Capture Channe                                        | el 4 Interrupt F | -lag Status bit   |                  |                  |        |  |  |  |  |  |

|                  | 1 = Interrupt request has occurred                                                                     |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| L:1 F            |                                                                                                        | request has not                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| bit 5            | IC3IF: Input Capture Channel 3 Interrupt Flag Status bit<br>1 = Interrupt request has occurred         |                                                       |                  |                   |                  |                  |        |  |  |  |  |  |

|                  |                                                                                                        | request has not                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| bit 4            | •                                                                                                      | IA Channel 3 In                                       |                  | tatus bit         |                  |                  |        |  |  |  |  |  |

|                  | 1 = Interrupt                                                                                          | request has occ                                       | curred           |                   |                  |                  |        |  |  |  |  |  |

|                  |                                                                                                        | request has not                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| oit 3            |                                                                                                        | : Cryptographic                                       |                  | us bit            |                  |                  |        |  |  |  |  |  |

|                  |                                                                                                        | request has occ<br>request has not                    |                  |                   |                  |                  |        |  |  |  |  |  |

|                  | -                                                                                                      | request lias 10                                       |                  |                   |                  |                  |        |  |  |  |  |  |

| hit 2            | CRVEDEELE                                                                                              | Cryptographia                                         | Ruffer Fron 9    | tatus hit         |                  |                  |        |  |  |  |  |  |

| bit 2            |                                                                                                        | : Cryptographic<br>request has occ                    |                  | tatus bit         |                  |                  |        |  |  |  |  |  |

## 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

- Fast Internal RC (FRC) Oscillator

- · Low-Power Internal RC (LPRC) Oscillator

The Primary Oscillator and FRC sources have the option of using the internal USB PLL block, which generates both the USB module clock and a separate system clock from the 96 MHz PLL. Refer to **Section 9.6 "Oscillator Modes and USB Operation"** for additional information.

The internal FRC provides an 8 MHz clock source. It can optionally be reduced by the programmable clock divider to provide a range of system clock frequencies.

The selected clock source generates the processor and peripheral clock sources. The processor clock source is divided by two to produce the internal instruction cycle clock, FcY. In this document, the instruction cycle clock is also denoted by FOSC/2. The internal instruction cycle clock, FOSC/2, can be provided on the OSCO I/O pin for some operating modes of the Primary Oscillator.

## 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in program memory (for more information, refer to **Section 30.1 "Configuration Bits"**). The Primary Oscillator Configuration bits, POSCMD<1:0> (Configuration Word 2<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (Configuration Word 2<10:8>), select the oscillator source that is used at a Power-on Reset. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations.

The Configuration bits allow users to choose between the various clock modes, as shown in Table 9-1.

#### 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (Configuration Word 2<7:6>) are used to jointly configure device clock switching and the Fail-Safe Clock Monitor (FSCM). Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION |                   |             |            |       |  |  |  |  |  |  |  |  |

|---------------------------------------------------------|-------------------|-------------|------------|-------|--|--|--|--|--|--|--|--|

| Oscillator Mode                                         | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |  |  |  |  |  |  |  |  |

| Fast RC Oscillator with Postscaler (FRCDIV)             | Internal          | 11          | 111        | 1, 2  |  |  |  |  |  |  |  |  |

| (Reserved)                                              | Internal          | XX          | 110        | 1     |  |  |  |  |  |  |  |  |

| Low-Power RC Oscillator (LPRC)                          | Internal          | 11          | 101        | 1     |  |  |  |  |  |  |  |  |

| Secondary (Timer1) Oscillator<br>(SOSC)                 | Secondary         | 11          | 100        | 1     |  |  |  |  |  |  |  |  |

| Primary Oscillator (XT) with PLL<br>Module (XTPLL)      | Primary           | 01          | 011        |       |  |  |  |  |  |  |  |  |

| Primary Oscillator (EC) with PLL<br>Module (ECPLL)      | Primary           | 00          | 011        |       |  |  |  |  |  |  |  |  |

| Primary Oscillator (HS)                                 | Primary           | 10          | 010        |       |  |  |  |  |  |  |  |  |

| Primary Oscillator (XT)                                 | Primary           | 01          | 010        |       |  |  |  |  |  |  |  |  |

| Primary Oscillator (EC)                                 | Primary           | 00          | 010        |       |  |  |  |  |  |  |  |  |

| Fast RC Oscillator with PLL Module (FRCPLL)             | Internal          | 11          | 001        | 1     |  |  |  |  |  |  |  |  |

| Fast RC Oscillator (FRC)                                | Internal          | 11          | 000        | 1     |  |  |  |  |  |  |  |  |

## TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

**Note 1:** OSCO pin function is determined by the OSCIOFCN Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

| U-0          | R/W-1 | R/W-1   | R/W-1                            | R/W-1                                                                                               | R/W-1                                                                                                                           | R/W-1                                                                                                                                                       |  |  |  |  |  |

|--------------|-------|---------|----------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| —            | IC4R5 | IC4R4   | IC4R3                            | IC4R2                                                                                               | IC4R1                                                                                                                           | IC4R0                                                                                                                                                       |  |  |  |  |  |

| bit 15 bit 8 |       |         |                                  |                                                                                                     |                                                                                                                                 |                                                                                                                                                             |  |  |  |  |  |

|              |       |         |                                  |                                                                                                     |                                                                                                                                 |                                                                                                                                                             |  |  |  |  |  |

| U-0          | R/W-1 | R/W-1   | R/W-1                            | R/W-1                                                                                               | R/W-1                                                                                                                           | R/W-1                                                                                                                                                       |  |  |  |  |  |

| —            | IC3R5 | IC3R4   | IC3R3                            | IC3R2                                                                                               | IC3R1                                                                                                                           | IC3R0                                                                                                                                                       |  |  |  |  |  |

| bit 7 bit 0  |       |         |                                  |                                                                                                     |                                                                                                                                 |                                                                                                                                                             |  |  |  |  |  |

|              | _     | — IC4R5 | — IC4R5 IC4R4<br>U-0 R/W-1 R/W-1 | —         IC4R5         IC4R4         IC4R3           U-0         R/W-1         R/W-1         R/W-1 | —         IC4R5         IC4R4         IC4R3         IC4R2           U-0         R/W-1         R/W-1         R/W-1         R/W-1 | —         IC4R5         IC4R4         IC4R3         IC4R2         IC4R1           U-0         R/W-1         R/W-1         R/W-1         R/W-1         R/W-1 |  |  |  |  |  |

#### REGISTER 11-8: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                    |

|-----------|-------------------------------------------------------------------------------|

| bit 13-8  | IC4R<5:0>: Assign Input Capture 4 (IC4) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                    |

| bit 5-0   | IC3R<5:0>: Assign Input Capture 3 (IC3) to Corresponding RPn or RPIn Pin bits |

#### REGISTER 11-9: RPINR9: PERIPHERAL PIN SELECT INPUT REGISTER 9

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| _      | —   | IC6R5 | IC6R4 | IC6R3 | IC6R2 | IC6R1 | IC6R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IC5R5 | IC5R4 | IC5R3 | IC5R2 | IC5R1 | IC5R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 IC6R<5:0>: Assign Input Capture 6 (IC6) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IC5R<5:0>: Assign Input Capture 5 (IC5) to Corresponding RPn or RPIn Pin bits

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U-0                                                                                                     | R/W-0            | U-0               | U-0              | U-0             | R/W-0                | R/W-0                |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------|-------------------|------------------|-----------------|----------------------|----------------------|--|--|--|--|--|

| TON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                         | TSIDL            |                   | _                | _               | TECS1 <sup>(2)</sup> | TECS0 <sup>(2)</sup> |  |  |  |  |  |

| bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                         |                  |                   |                  |                 |                      | bit 8                |  |  |  |  |  |

| 11-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W_0                                                                                                   | R/W_0            | R/M/-0            | R/M/_0           | 11-0            | R/W/-0               | 11-0                 |  |  |  |  |  |

| 0-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                         | 1                |                   |                  | 0-0             |                      | 0-0                  |  |  |  |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IGATE                                                                                                   | ICKF31           | TCKFSU            | 132.7            |                 | 103.7                | bit (                |  |  |  |  |  |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                         |                  |                   |                  |                 |                      |                      |  |  |  |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | able bit                                                                                                | W = Writable     | bit               | U = Unimplen     | nented hit rea  | ud as '0'            |                      |  |  |  |  |  |

| TON-TSIDLTECS1 <sup>(2)</sup> TECS0 <sup>(2)</sup> bit 15IU-0R/W-0R/W-0R/W-0U-0R/W-0U-0-TGATETCKPS1TCKPS0T32 <sup>(3)</sup> -TCS <sup>(2)</sup> -bit 7IIIIIILagend:<br>R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<br>- n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 15TON: Timerx On bit<br>When TXCON43> = 1;<br>1 = Starts 32-bit Timerxy<br>0 = Stops 32-bit Timerxy<br>0 = Stops 32-bit Timerxy<br>0 = Stops 16-bit Timerx<br>0 = Stops 16-bit Timerx<br>10 = LPR Oscillator<br>0 = TECS-10>: Timerx Extended Clock Source Select bits (selected when TCS = 1) <sup>(2)</sup><br>Mhen TCS = 1:<br>These bits are ignored; Timerx is clocked from the internal system clock (Fosc/2).bit 7Unimplemented: Read as '0'<br>Hener CS = 1:<br>These bits is ignored.<br>When TCS = 1:<br>This bit is ignored.<br>When TCS = 1:<br>This bit is ignored.<br>When TCS = 1:<br>This bit is ignored.<br>When TCS | own                                                                                                     |                  |                   |                  |                 |                      |                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                         |                  |                   |                  | areu            |                      | IOWIT                |  |  |  |  |  |

| bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TON: Timerx                                                                                             | On bit           |                   |                  |                 |                      |                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                         |                  |                   |                  |                 |                      |                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 = Starts 32-bit Timerx/y                                                                              |                  |                   |                  |                 |                      |                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 = Stops 32-bit Timerx/y                                                                               |                  |                   |                  |                 |                      |                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                         |                  |                   |                  |                 |                      |                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                         |                  |                   |                  |                 |                      |                      |  |  |  |  |  |

| bit 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                       |                  | O <b>'</b>        |                  |                 |                      |                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                       |                  |                   |                  |                 |                      |                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                         |                  |                   |                  |                 |                      |                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                         | •                |                   |                  |                 |                      |                      |  |  |  |  |  |

| bit 12-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Unimplemen                                                                                              | nted: Read as '  | 0'                |                  |                 |                      |                      |  |  |  |  |  |

| bit 9-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>TECS&lt;1:0&gt;:</b> Timerx Extended Clock Source Select bits (selected when TCS = 1) <sup>(2)</sup> |                  |                   |                  |                 |                      |                      |  |  |  |  |  |