Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Active                                                                   |

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 18432                                                                    |

| Number of I/O                  | 71                                                                       |

| Number of Gates                | 60000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 100-TQFP                                                                 |

| Supplier Device Package        | 100-VQFP (14x14)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p060-1vqg100 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ProASIC3 Devices               | A3P015 <sup>1</sup> | A3P030                            | A3P060                  | A3P125                  | A3P250                 | A3P400            | A3P600            | A3P1000           |

|--------------------------------|---------------------|-----------------------------------|-------------------------|-------------------------|------------------------|-------------------|-------------------|-------------------|

| Cortex-M1 Devices <sup>2</sup> |                     |                                   |                         |                         | M1A3P250               | M1A3P400          | M1A3P600          | M1A3P1000         |

| Package Pins<br>QFN            | QN68                | QN48, QN68,<br>QN132 <sup>7</sup> | QN132 <sup>7</sup>      | QN132 <sup>7</sup>      | QN132 <sup>7</sup>     |                   |                   |                   |

| CS<br>VQFP<br>TQFP<br>PQFP     |                     | VQ100                             | CS121<br>VQ100<br>TQ144 | VQ100<br>TQ144<br>PQ208 | VQ100<br>PQ208         | PQ208             | PQ208             | PQ208             |

| FBGA                           |                     |                                   | FG144                   | FG144                   | FG144/256 <sup>5</sup> | FG144/256/<br>484 | FG144/256/<br>484 | FG144/256/<br>484 |

- A3P015 is not recommended for new designs.

Refer to the Cortex-M1 product brief for more information.

AES is not available for Cortex-M1 ProASIC3 devices.

Six chip (main) and three quadrant global networks are available for A3P060 and above.

The M1A3P250 device does not support this package.

For higher densities and support of additional features, refer to the ProASIC3E Flash Family FPGAs datasheet.

Package not available.

Revision 18

# I/Os Per Package <sup>1</sup>

| ProASIC3<br>Devices  | A3P015 <sup>2</sup> | A3P030           | A3P060           | A3P125           | A3P                           | 250 <sup>3</sup>       | A3P                           | 400 <sup>3</sup>       | A3F                           | P600                   | A3P                           | 1000                   |

|----------------------|---------------------|------------------|------------------|------------------|-------------------------------|------------------------|-------------------------------|------------------------|-------------------------------|------------------------|-------------------------------|------------------------|

| Cortex-M1<br>Devices |                     |                  |                  |                  | M1A3F                         | 250 <sup>3,5</sup>     | M1A3                          | P400 <sup>3</sup>      | M1A3                          | 3P600                  | M1A3                          | P1000                  |

|                      |                     |                  |                  |                  | I/C                           | ) Type                 |                               |                        |                               |                        |                               |                        |

| Package              | Single-Ended I/O    | Single-Ended I/O | Single-Ended I/O | Single-Ended I/O | Single-Ended I/O <sup>4</sup> | Differential I/O Pairs |

| QN48                 | _                   | 34               | _                | _                | -                             | _                      |                               | _                      | _                             | _                      | _                             | _                      |

| QN68                 | 49                  | 49               | _                | _                | _                             | _                      | _                             | _                      |                               | _                      | _                             | _                      |

| QN132 <sup>7</sup>   | _                   | 81               | 80               | 84               | 87                            | 19                     | _                             | -                      |                               | _                      | _                             | _                      |

| CS121                | _                   | _                | 96               | _                | -                             | _                      | _                             | _                      | _                             | _                      | _                             | _                      |

| VQ100                | _                   | 77               | 71               | 71               | 68                            | 13                     | _                             | _                      |                               | _                      | _                             | _                      |

| TQ144                | _                   | _                | 91               | 100              | -                             | _                      | _                             | _                      | _                             | _                      | _                             | _                      |

| PQ208                | _                   | -                | -                | 133              | 151                           | 34                     | 151                           | 34                     | 154                           | 35                     | 154                           | 35                     |

| FG144                | _                   | _                | 96               | 97               | 97                            | 24                     | 97                            | 25                     | 97                            | 25                     | 97                            | 25                     |

| FG256 <sup>5,6</sup> | _                   | _                | -                | -                | 157                           | 38                     | 178                           | 38                     | 177                           | 43                     | 177                           | 44                     |

| FG484 <sup>6</sup>   | _                   | _                | _                | _                | -                             | _                      | 194                           | 38                     | 235                           | 60                     | 300                           | 74                     |

#### Notes

- 1. When considering migrating your design to a lower- or higher-density device, refer to the ProASIC3 FPGA Fabric User Guide to ensure complying with design and board migration requirements.

- 2. A3P015 is not recommended for new designs.

- 3. For A3P250 and A3P400 devices, the maximum number of LVPECL pairs in east and west banks cannot exceed 15. Refer to the ProASIC3 FPGA Fabric Users Guide for position assignments of the 15 LVPECL pairs.

- 4. Each used differential I/O pair reduces the number of single-ended I/Os available by two.

- 5. The M1A3P250 device does not support FG256 package.

- 6. FG256 and FG484 are footprint-compatible packages.

- 7. Package not available.

Table 1 • ProASIC3 FPGAs Package Sizes Dimensions

| Package                            | CS121 | QN48  | QN68  | QN132 * | VQ100   | TQ144   | PQ208   | FG144   | FG256   | FG484   |

|------------------------------------|-------|-------|-------|---------|---------|---------|---------|---------|---------|---------|

| Length × Width (mm × mm)           | 6 × 6 | 6 × 6 | 8 × 8 | 8 × 8   | 14 × 14 | 20 × 20 | 28 × 28 | 13 × 13 | 17 × 17 | 23 × 23 |

| Nominal Area<br>(mm <sup>2</sup> ) | 36    | 36    | 64    | 64      | 196     | 400     | 784     | 169     | 289     | 529     |

| Pitch (mm)                         | 0.5   | 0.4   | 0.4   | 0.5     | 0.5     | 0.5     | 0.5     | 1.0     | 1.0     | 1.0     |

| Height (mm)                        | 0.99  | 0.90  | 0.90  | 0.75    | 1.00    | 1.40    | 3.40    | 1.45    | 1.60    | 2.23    |

Note: \* Package not available

Revision 18 III

#### User Nonvolatile FlashROM

ProASIC3 devices have 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications:

- · Internet protocol addressing (wireless or fixed)

- System calibration settings

- · Device serialization and/or inventory control

- Subscription-based business models (for example, set-top boxes)

- · Secure key storage for secure communications algorithms

- Asset management/tracking

- Date stamping

- · Version management

The FlashROM is written using the standard ProASIC3 IEEE 1532 JTAG programming interface. The core can be individually programmed (erased and written), and on-chip AES decryption can be used selectively to securely load data over public networks (except in the A3P015 and A3P030 devices), as in security keys stored in the FlashROM for a user design.

The FlashROM can be programmed via the JTAG programming interface, and its contents can be read back either through the JTAG programming interface or via direct FPGA core addressing. Note that the FlashROM can only be programmed from the JTAG interface and cannot be programmed from the internal logic array.

The FlashROM is programmed as 8 banks of 128 bits; however, reading is performed on a byte-by-byte basis using a synchronous interface. A 7-bit address from the FPGA core defines which of the 8 banks and which of the 16 bytes within that bank are being read. The three most significant bits (MSBs) of the FlashROM address determine the bank, and the four least significant bits (LSBs) of the FlashROM address define the byte.

The ProASIC3 development software solutions, Libero<sup>®</sup> System-on-Chip (SoC) and Designer, have extensive support for the FlashROM. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. Another feature allows the inclusion of static data for system version control. Data for the FlashROM can be generated quickly and easily using Libero SoC and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FlashROM contents.

#### SRAM and FIFO

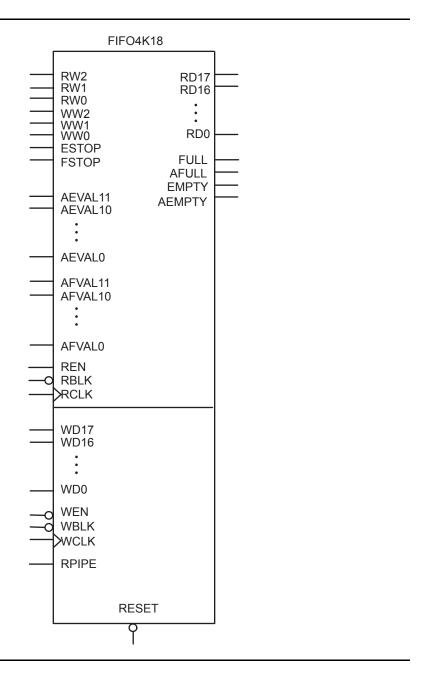

ProASIC3 devices (except the A3P015 and A3P030 devices) have embedded SRAM blocks along their north and south sides. Each variable-aspect-ratio SRAM block is 4,608 bits in size. Available memory configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1 bits. The individual blocks have independent read and write ports that can be configured with different bit widths on each port. For example, data can be sent through a 4-bit port and read as a single bitstream. The embedded SRAM blocks can be initialized via the device JTAG port (ROM emulation mode) using the UJTAG macro (except in A3P015 and A3P030 devices).

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using additional core VersaTiles. The FIFO width and depth are programmable. The FIFO also features programmable Almost Empty (AEMPTY) and Almost Full (AFULL) flags in addition to the normal Empty and Full flags. The embedded FIFO control unit contains the counters necessary for generation of the read and write address pointers. The embedded SRAM/FIFO blocks can be cascaded to create larger configurations.

#### PLL and CCC

ProASIC3 devices provide designers with very flexible clock conditioning capabilities. Each member of the ProASIC3 family contains six CCCs. One CCC (center west side) has a PLL. The A3P015 and A3P030 devices do not have a PLL.

The six CCC blocks are located at the four corners and the centers of the east and west sides.

All six CCC blocks are usable; the four corner CCCs and the east CCC allow simple clock delay operations as well as clock spine access.

The inputs of the six CCC blocks are accessible from the FPGA core or from one of several inputs located near the CCC that have dedicated connections to the CCC block.

1-5 Revision 18

Table 2-32 • I/O Short Currents IOSH/IOSL

Applicable to Advanced I/O Banks

|                                      | Drive Strength              | IOSL (mA) <sup>1</sup>          | IOSH (mA) <sup>1</sup>          |

|--------------------------------------|-----------------------------|---------------------------------|---------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS           | 2 mA                        | 27                              | 25                              |

|                                      | 4 mA                        | 27                              | 25                              |

|                                      | 6 mA                        | 54                              | 51                              |

|                                      | 8 mA                        | 54                              | 51                              |

|                                      | 12 mA                       | 109                             | 103                             |

|                                      | 16 mA                       | 127                             | 132                             |

|                                      | 24 mA                       | 181                             | 268                             |

| 3.3 V LVCMOS Wide Range <sup>2</sup> | 100 μΑ                      | Same as regular 3.3 V<br>LVCMOS | Same as regular 3.3 V<br>LVCMOS |

| 2.5 V LVCMOS                         | 2 mA                        | 18                              | 16                              |

|                                      | 4 mA                        | 18                              | 16                              |

|                                      | 6 mA                        | 37                              | 32                              |

|                                      | 8 mA                        | 37                              | 32                              |

|                                      | 12 mA                       | 74                              | 65                              |

|                                      | 16 mA                       | 87                              | 83                              |

|                                      | 24 mA                       | 124                             | 169                             |

| 1.8 V LVCMOS                         | 2 mA                        | 11                              | 9                               |

|                                      | 4 mA                        | 22                              | 17                              |

|                                      | 6 mA                        | 44                              | 35                              |

|                                      | 8 mA                        | 51                              | 45                              |

|                                      | 12 mA                       | 74                              | 91                              |

|                                      | 16 mA                       | 74                              | 91                              |

| 1.5 V LVCMOS                         | 2 mA                        | 16                              | 13                              |

|                                      | 4 mA                        | 33                              | 25                              |

|                                      | 6 mA                        | 39                              | 32                              |

|                                      | 8 mA                        | 55                              | 66                              |

|                                      | 12 mA                       | 55                              | 66                              |

| 3.3 V PCI/PCI-X                      | Per PCI/PCI-X specification | 109                             | 103                             |

2-29 Revision 18

<sup>1.</sup>  $T_J = 100^{\circ}C$

<sup>2.</sup> Applicable to 3.3 V LVCMOS Wide Range. I<sub>OSL</sub>/I<sub>OSH</sub> dependent on the I/O buffer drive strength selected for wide range applications. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

Table 2-44 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus I/O Banks

|                   | , .bb          | DIE 10 OI         |                 |                  |                 |                   |                 |                 |                 |                 |                  |                  |       |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

| 2 mA              | Std.           | 0.66              | 9.68            | 0.04             | 1.00            | 0.43              | 9.86            | 8.42            | 2.28            | 2.21            | 12.09            | 10.66            | ns    |

|                   | -1             | 0.56              | 8.23            | 0.04             | 0.85            | 0.36              | 8.39            | 7.17            | 1.94            | 1.88            | 10.29            | 9.07             | ns    |

|                   | -2             | 0.49              | 7.23            | 0.03             | 0.75            | 0.32              | 7.36            | 6.29            | 1.70            | 1.65            | 9.03             | 7.96             | ns    |

| 4 mA              | Std.           | 0.66              | 9.68            | 0.04             | 1.00            | 0.43              | 9.86            | 8.42            | 2.28            | 2.21            | 12.09            | 10.66            | ns    |

|                   | -1             | 0.56              | 8.23            | 0.04             | 0.85            | 0.36              | 8.39            | 7.17            | 1.94            | 1.88            | 10.29            | 9.07             | ns    |

|                   | -2             | 0.49              | 7.23            | 0.03             | 0.75            | 0.32              | 7.36            | 6.29            | 1.70            | 1.65            | 9.03             | 7.96             | ns    |

| 6 mA              | Std.           | 0.66              | 6.70            | 0.04             | 1.00            | 0.43              | 6.82            | 5.89            | 2.58            | 2.74            | 9.06             | 8.12             | ns    |

|                   | -1             | 0.56              | 5.70            | 0.04             | 0.85            | 0.36              | 5.80            | 5.01            | 2.20            | 2.33            | 7.71             | 6.91             | ns    |

|                   | -2             | 0.49              | 5.00            | 0.03             | 0.75            | 0.32              | 5.10            | 4.40            | 1.93            | 2.05            | 6.76             | 6.06             | ns    |

| 8 mA              | Std.           | 0.66              | 6.70            | 0.04             | 1.00            | 0.43              | 6.82            | 5.89            | 2.58            | 2.74            | 9.06             | 8.12             | ns    |

|                   | -1             | 0.56              | 5.70            | 0.04             | 0.85            | 0.36              | 5.80            | 5.01            | 2.20            | 2.33            | 7.71             | 6.91             | ns    |

|                   | -2             | 0.49              | 5.00            | 0.03             | 0.75            | 0.32              | 5.10            | 4.40            | 1.93            | 2.05            | 6.76             | 6.06             | ns    |

| 12 mA             | Std.           | 0.66              | 5.05            | 0.04             | 1.00            | 0.43              | 5.14            | 4.51            | 2.79            | 3.08            | 7.38             | 6.75             | ns    |

|                   | -1             | 0.56              | 4.29            | 0.04             | 0.85            | 0.36              | 4.37            | 3.84            | 2.38            | 2.62            | 6.28             | 5.74             | ns    |

|                   | -2             | 0.49              | 3.77            | 0.03             | 0.75            | 0.32              | 3.84            | 3.37            | 2.09            | 2.30            | 5.51             | 5.04             | ns    |

| 16 mA             | Std.           | 0.66              | 5.05            | 0.04             | 1.00            | 0.43              | 5.14            | 4.51            | 2.79            | 3.08            | 7.38             | 6.75             | ns    |

|                   | -1             | 0.56              | 4.29            | 0.04             | 0.85            | 0.36              | 4.37            | 3.84            | 2.38            | 2.62            | 6.28             | 5.74             | ns    |

|                   | -2             | 0.49              | 3.77            | 0.03             | 0.75            | 0.32              | 3.84            | 3.37            | 2.09            | 2.30            | 5.51             | 5.04             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-45 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

Applicable to Standard I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | <b>–</b> 1     | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2             | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 4 mA              | Std.           | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | -1             | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2             | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 6 mA              | Std.           | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | -1             | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

|                   | -2             | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns    |

| 8 mA              | Std.           | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | -1             | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

2-37 Revision 18

#### 3.3 V LVCMOS Wide Range

Table 2-47 • Minimum and Maximum DC Input and Output Levels

Applicable to Advanced I/O Banks

| 3.3 V<br>LVCMOS<br>Wide Range | Equiv.<br>Software<br>Default            | ٧        | IL       | V        | IH       | VOL      | VOH       | IOL | ЮН  | IOSL                   | юѕн                    | IIL <sup>2</sup> | IIH <sup>3</sup>        |

|-------------------------------|------------------------------------------|----------|----------|----------|----------|----------|-----------|-----|-----|------------------------|------------------------|------------------|-------------------------|

| Drive<br>Strength             | Drive<br>Strength<br>Option <sup>1</sup> | Min<br>V | Max<br>V | Min<br>V | Max<br>V | Max<br>V | Min<br>V  | μΑ  | μΑ  | Max<br>mA <sup>4</sup> | Max<br>mA <sup>4</sup> | μΑ <sup>5</sup>  | μ <b>Α</b> <sup>5</sup> |

| 100 μΑ                        | 2 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 25                     | 27                     | 10               | 10                      |

| 100 μΑ                        | 4 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 25                     | 27                     | 10               | 10                      |

| 100 μΑ                        | 6 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 51                     | 54                     | 10               | 10                      |

| 100 μΑ                        | 8 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 51                     | 54                     | 10               | 10                      |

| 100 μΑ                        | 12 mA                                    | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 103                    | 109                    | 10               | 10                      |

| 100 μΑ                        | 16 mA                                    | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 132                    | 127                    | 10               | 10                      |

| 100 μΑ                        | 24 mA                                    | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 268                    | 181                    | 10               | 10                      |

#### Notes:

- 1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 4. Currents are measured at 85°C junction temperature.

- 5. All LVMCOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

- 6. Software default selection highlighted in gray.

Table 2-48 • Minimum and Maximum DC Input and Output Levels

Applicable to Standard Plus I/O Banks

| 3.3 V LVCMOS<br>Wide Range | Equiv.<br>Software                                  | VI       | L        | ٧        | IH       | VOL      | VOH       | IOL | ЮН  | IOSL                   | IOSH                   | IIL <sup>2</sup>        | IIH <sup>3</sup>        |

|----------------------------|-----------------------------------------------------|----------|----------|----------|----------|----------|-----------|-----|-----|------------------------|------------------------|-------------------------|-------------------------|

| Drive Strength             | Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Min<br>V | Max<br>V | Min<br>V | Max<br>V | Max<br>V | Min<br>V  | μΑ  | μА  | Max<br>mA <sup>4</sup> | Max<br>mA <sup>4</sup> | μ <b>Α</b> <sup>5</sup> | μ <b>Α</b> <sup>5</sup> |

| 100 µA                     | 2 mA                                                | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 25                     | 27                     | 10                      | 10                      |

| 100 μΑ                     | 4 mA                                                | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 25                     | 27                     | 10                      | 10                      |

| 100 µA                     | 6 mA                                                | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 51                     | 54                     | 10                      | 10                      |

| 100 μΑ                     | 8 mA                                                | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 51                     | 54                     | 10                      | 10                      |

| 100 μΑ                     | 12 mA                                               | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 103                    | 109                    | 10                      | 10                      |

| 100 μΑ                     | 16 mA                                               | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 103                    | 109                    | 10                      | 10                      |

#### Notes:

- 1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 4. Currents are measured at 85°C junction temperature.

- 5. All LVMCOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

- 6. Software default selection highlighted in gray.

2-39 Revision 18

Table 2-52 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

Applicable to Standard Plus I/O Banks

| Drive<br>Strength | Equiv.<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zнs</sub> | Units |

|-------------------|---------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 100 μΑ            | 2 mA                                                                      | Std.           | 0.60              | 11.14           | 0.04             | 1.52            | 0.43              | 11.14           | 9.54            | 3.51            | 3.61            | 14.53            | 12.94            | ns    |

|                   |                                                                           | <b>–1</b>      | 0.51              | 9.48            | 0.04             | 1.29            | 0.36              | 9.48            | 8.12            | 2.99            | 3.07            | 12.36            | 11.00            | ns    |

|                   |                                                                           | -2             | 0.45              | 8.32            | 0.03             | 1.14            | 0.32              | 8.32            | 7.13            | 2.62            | 2.70            | 10.85            | 9.66             | ns    |

| 100 μΑ            | 4 mA                                                                      | Std.           | 0.60              | 6.96            | 0.04             | 1.52            | 0.43              | 6.96            | 5.79            | 3.99            | 4.45            | 10.35            | 9.19             | ns    |

|                   |                                                                           | <b>–1</b>      | 0.51              | 5.92            | 0.04             | 1.29            | 0.36              | 5.92            | 4.93            | 3.39            | 3.78            | 8.81             | 7.82             | ns    |

|                   |                                                                           | -2             | 0.45              | 5.20            | 0.03             | 1.14            | 0.32              | 5.20            | 4.33            | 2.98            | 3.32            | 7.73             | 6.86             | ns    |

| 100 μΑ            | 6 mA                                                                      | Std.           | 0.60              | 6.96            | 0.04             | 1.52            | 0.43              | 6.96            | 5.79            | 3.99            | 4.45            | 10.35            | 9.19             | ns    |

|                   |                                                                           | -1             | 0.51              | 5.92            | 0.04             | 1.29            | 0.36              | 5.92            | 4.93            | 3.39            | 3.78            | 8.81             | 7.82             | ns    |

|                   |                                                                           | -2             | 0.45              | 5.20            | 0.03             | 1.14            | 0.32              | 5.20            | 4.33            | 2.98            | 3.32            | 7.73             | 6.86             | ns    |

| 100 μΑ            | 8 mA                                                                      | Std.           | 0.60              | 4.89            | 0.04             | 1.52            | 0.43              | 4.89            | 3.92            | 4.31            | 4.98            | 8.28             | 7.32             | ns    |

|                   |                                                                           | -1             | 0.51              | 4.16            | 0.04             | 1.29            | 0.36              | 4.16            | 3.34            | 3.67            | 4.24            | 7.04             | 6.22             | ns    |

|                   |                                                                           | -2             | 0.45              | 3.65            | 0.03             | 1.14            | 0.32              | 3.65            | 2.93            | 3.22            | 3.72            | 6.18             | 5.46             | ns    |

| 100 μΑ            | 16 mA                                                                     | Std.           | 0.60              | 4.89            | 0.04             | 1.52            | 0.43              | 4.89            | 3.92            | 4.31            | 4.98            | 8.28             | 7.32             | ns    |

|                   |                                                                           | -1             | 0.51              | 4.16            | 0.04             | 1.29            | 0.36              | 4.16            | 3.34            | 3.67            | 4.24            | 7.04             | 6.22             | ns    |

|                   |                                                                           | -2             | 0.45              | 3.65            | 0.03             | 1.14            | 0.32              | 3.65            | 2.93            | 3.22            | 3.72            | 6.18             | 5.46             | ns    |

- 1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is  $\pm 100~\mu$ A. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. Software default selection highlighted in gray.

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-43 Revision 18

Table 2-53 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus I/O Banks

|                   | Equiv.<br>Software                                  |                |                   |                 |                  |                 |                   |                 |                 |                 |                 |                  |                  |       |

|-------------------|-----------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zhs</sub> | Units |

| 100 μΑ            | 2 mA                                                | Std.           | 0.60              | 14.97           | 0.04             | 1.52            | 0.43              | 14.97           | 12.79           | 3.52            | 3.41            | 18.36            | 16.18            | ns    |

|                   |                                                     | <b>–1</b>      | 0.51              | 12.73           | 0.04             | 1.29            | 0.36              | 12.73           | 10.88           | 2.99            | 2.90            | 15.62            | 13.77            | ns    |

|                   |                                                     | -2             | 0.45              | 11.18           | 0.03             | 1.14            | 0.32              | 11.18           | 9.55            | 2.63            | 2.55            | 13.71            | 12.08            | ns    |

| 100 μΑ            | 4 mA                                                | Std.           | 0.60              | 10.36           | 0.04             | 1.52            | 0.43              | 10.36           | 8.93            | 3.99            | 4.24            | 13.75            | 12.33            | ns    |

|                   |                                                     | <b>–1</b>      | 0.51              | 8.81            | 0.04             | 1.29            | 0.36              | 8.81            | 7.60            | 3.39            | 3.60            | 11.70            | 10.49            | ns    |

|                   |                                                     | -2             | 0.45              | 7.74            | 0.03             | 1.14            | 0.32              | 7.74            | 6.67            | 2.98            | 3.16            | 10.27            | 9.21             | ns    |

| 100 μΑ            | 6 mA                                                | Std.           | 0.60              | 10.36           | 0.04             | 1.52            | 0.43              | 10.36           | 8.93            | 3.99            | 4.24            | 13.75            | 12.33            | ns    |

|                   |                                                     | -1             | 0.51              | 8.81            | 0.04             | 1.29            | 0.36              | 8.81            | 7.60            | 3.39            | 3.60            | 11.70            | 10.49            | ns    |

|                   |                                                     | -2             | 0.45              | 7.74            | 0.03             | 1.14            | 0.32              | 7.74            | 6.67            | 2.98            | 3.16            | 10.27            | 9.21             | ns    |

| 100 μΑ            | 8 mA                                                | Std.           | 0.60              | 7.81            | 0.04             | 1.52            | 0.43              | 7.81            | 6.85            | 4.32            | 4.76            | 11.20            | 10.24            | ns    |

|                   |                                                     | <b>–1</b>      | 0.51              | 6.64            | 0.04             | 1.29            | 0.36              | 6.64            | 5.82            | 3.67            | 4.05            | 9.53             | 8.71             | ns    |

|                   |                                                     | -2             | 0.45              | 5.83            | 0.03             | 1.14            | 0.32              | 5.83            | 5.11            | 3.22            | 3.56            | 8.36             | 7.65             | ns    |

| 100 μΑ            | 16 mA                                               | Std.           | 0.60              | 7.81            | 0.04             | 1.52            | 0.43              | 7.81            | 6.85            | 4.32            | 4.76            | 11.20            | 10.24            | ns    |

|                   |                                                     | <b>–1</b>      | 0.51              | 6.64            | 0.04             | 1.29            | 0.36              | 6.64            | 5.82            | 3.67            | 4.05            | 9.53             | 8.71             | ns    |

|                   |                                                     | -2             | 0.45              | 5.83            | 0.03             | 1.14            | 0.32              | 5.83            | 5.11            | 3.22            | 3.56            | 8.36             | 7.65             | ns    |

<sup>1.</sup> The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

<sup>2.</sup> For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-64 • 2.5 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

Applicable to Standard I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 8.20            | 0.04             | 1.29            | 0.43              | 7.24            | 8.20            | 2.03            | 1.91            | ns    |

|                   | <b>–</b> 1     | 0.56              | 6.98            | 0.04             | 1.10            | 0.36              | 6.16            | 6.98            | 1.73            | 1.62            | ns    |

|                   | -2             | 0.49              | 6.13            | 0.03             | 0.96            | 0.32              | 5.41            | 6.13            | 1.52            | 1.43            | ns    |

| 4 mA              | Std.           | 0.66              | 8.20            | 0.04             | 1.29            | 0.43              | 7.24            | 8.20            | 2.03            | 1.91            | ns    |

|                   | -1             | 0.56              | 6.98            | 0.04             | 1.10            | 0.36              | 6.16            | 6.98            | 1.73            | 1.62            | ns    |

|                   | -2             | 0.49              | 6.13            | 0.03             | 0.96            | 0.32              | 5.41            | 6.13            | 1.52            | 1.43            | ns    |

| 6 mA              | Std.           | 0.66              | 4.77            | 0.04             | 1.29            | 0.43              | 4.55            | 4.77            | 2.38            | 2.55            | ns    |

|                   | -1             | 0.56              | 4.05            | 0.04             | 1.10            | 0.36              | 3.87            | 4.05            | 2.03            | 2.17            | ns    |

|                   | -2             | 0.49              | 3.56            | 0.03             | 0.96            | 0.32              | 3.40            | 3.56            | 1.78            | 1.91            | ns    |

| 8 mA              | Std.           | 0.66              | 4.77            | 0.04             | 1.29            | 0.43              | 4.55            | 4.77            | 2.38            | 2.55            | ns    |

|                   | -1             | 0.56              | 4.05            | 0.04             | 1.10            | 0.36              | 3.87            | 4.05            | 2.03            | 2.17            | ns    |

|                   | -2             | 0.49              | 3.56            | 0.03             | 0.96            | 0.32              | 3.40            | 3.56            | 1.78            | 1.91            | ns    |

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-65 • 2.5 V LVCMOS Low Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

Applicable to Standard I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 11.00           | 0.04             | 1.29            | 0.43              | 10.37           | 11.00           | 2.03            | 1.83            | ns    |

|                   | <b>–</b> 1     | 0.56              | 9.35            | 0.04             | 1.10            | 0.36              | 8.83            | 9.35            | 1.73            | 1.56            | ns    |

|                   | -2             | 0.49              | 8.21            | 0.03             | 0.96            | 0.32              | 7.75            | 8.21            | 1.52            | 1.37            | ns    |

| 4 mA              | Std.           | 0.66              | 11.00           | 0.04             | 1.29            | 0.43              | 10.37           | 11.00           | 2.03            | 1.83            | ns    |

|                   | <b>–</b> 1     | 0.56              | 9.35            | 0.04             | 1.10            | 0.36              | 8.83            | 9.35            | 1.73            | 1.56            | ns    |

|                   | -2             | 0.49              | 8.21            | 0.03             | 0.96            | 0.32              | 7.75            | 8.21            | 1.52            | 1.37            | ns    |

| 6 mA              | Std.           | 0.66              | 7.50            | 0.04             | 1.29            | 0.43              | 7.36            | 7.50            | 2.39            | 2.46            | ns    |

|                   | <b>–</b> 1     | 0.56              | 6.38            | 0.04             | 1.10            | 0.36              | 6.26            | 6.38            | 2.03            | 2.10            | ns    |

|                   | -2             | 0.49              | 5.60            | 0.03             | 0.96            | 0.32              | 5.49            | 5.60            | 1.78            | 1.84            | ns    |

| 8 mA              | Std.           | 0.66              | 7.50            | 0.04             | 1.29            | 0.43              | 7.36            | 7.50            | 2.39            | 2.46            | ns    |

|                   | -1             | 0.56              | 6.38            | 0.04             | 1.10            | 0.36              | 6.26            | 6.38            | 2.03            | 2.10            | ns    |

|                   | -2             | 0.49              | 5.60            | 0.03             | 0.96            | 0.32              | 5.49            | 5.60            | 1.78            | 1.84            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-93 • Minimum and Maximum DC Input and Output Levels

| DC Parameter | Description                    | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

|--------------|--------------------------------|-------|------|-------|------|-------|------|-------|

| VCCI         | Supply Voltage                 | 3.    | 0    | 3     | .3   | 3     | .6   | V     |

| VOL          | Output Low Voltage             | 0.96  | 1.27 | 1.06  | 1.43 | 1.30  | 1.57 | V     |

| VOH          | Output High Voltage            | 1.8   | 2.11 | 1.92  | 2.28 | 2.13  | 2.41 | V     |

| VIL, VIH     | Input Low, Input High Voltages | 0     | 3.6  | 0     | 3.6  | 0     | 3.6  | V     |

| VODIFF       | Differential Output Voltage    | 0.625 | 0.97 | 0.625 | 0.97 | 0.625 | 0.97 | V     |

| VOCM         | Output Common-Mode Voltage     | 1.762 | 1.98 | 1.762 | 1.98 | 1.762 | 1.98 | V     |

| VICM         | Input Common-Mode Voltage      | 1.01  | 2.57 | 1.01  | 2.57 | 1.01  | 2.57 | V     |

| VIDIFF       | Input Differential Voltage     | 300   |      | 300   |      | 300   |      | mV    |

#### Table 2-94 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) |

|---------------|----------------|----------------------|

| 1.64          | 1.94           | Cross point          |

Note: \*Measuring point =  $V_{trip.}$  See Table 2-22 on page 2-22 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-95 • LVPECL

Commercial-Case Conditions:  $T_J = 70$ °C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.66              | 1.80            | 0.04             | 1.40            | ns    |

| <b>-1</b>   | 0.56              | 1.53            | 0.04             | 1.19            | ns    |

| -2          | 0.49              | 1.34            | 0.03             | 1.05            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## **Clock Conditioning Circuits**

### **CCC Electrical Specifications**

#### **Timing Characteristics**

#### Table 2-115 • ProASIC3 CCC/PLL Specification

| Parameter                                                          | Minimum                     | Typical          | Maximum                      | Units |

|--------------------------------------------------------------------|-----------------------------|------------------|------------------------------|-------|

| Clock Conditioning Circuitry Input Frequency f <sub>IN CCC</sub>   | 1.5                         |                  | 350                          | MHz   |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT CCC</sub> | 0.75                        |                  | 350                          | MHz   |

| Serial Clock (SCLK) for Dynamic PLL <sup>1</sup>                   |                             |                  | 125                          | MHz   |

| Delay Increments in Programmable Delay Blocks <sup>2, 3</sup>      |                             | 200 <sup>4</sup> |                              | ps    |

| Number of Programmable Values in Each Programmabl Delay Block      | е                           |                  | 32                           |       |

| Input Period Jitter                                                |                             |                  | 1.5                          | ns    |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub>         | IV                          | lax Peak-to-l    | Peak Period Jitte            | er    |

|                                                                    | 1 Global<br>Network<br>Used |                  | 3 Global<br>Networks<br>Used |       |

| 0.75 MHz to 24 MHz                                                 | 0.50%                       |                  | 0.70%                        |       |

| 24 MHz to 100 MHz                                                  | 1.00%                       |                  | 1.20%                        |       |

| 100 MHz to 250 MHz                                                 | 1.75%                       |                  | 2.00%                        |       |

| 250 MHz to 350 MHz                                                 | 2.50%                       |                  | 5.60%                        |       |

| Acquisition Time                                                   |                             |                  |                              |       |

| (A3P250 and A3P1000 only) LockControl = 0                          |                             |                  | 300                          | μs    |

| LockControl = 1                                                    |                             |                  | 300                          | μs    |

| (all other dies) LockControl = 0                                   |                             |                  | 300                          | μs    |

| LockControl = 1                                                    |                             |                  | 6.0                          | ms    |

| Tracking Jitter <sup>5</sup>                                       |                             |                  |                              |       |

| (A3P250 and A3P1000 only) LockControl = 0                          |                             |                  | 1.6                          | ns    |

| LockControl = 1                                                    |                             |                  | 1.6                          | ns    |

| (all other dies) LockControl = 0                                   |                             |                  | 1.6                          | ns    |

| LockControl = 1                                                    |                             |                  | 0.8                          | ns    |

| Output Duty Cycle                                                  | 48.5                        |                  | 51.5                         | %     |

| Delay Range in Block: Programmable Delay 1 <sup>2, 3</sup>         | 0.6                         |                  | 5.56                         | ns    |

| Delay Range in Block: Programmable Delay 2 <sup>2, 3</sup>         | 0.225                       |                  | 5.56                         | ns    |

| Delay Range in Block: Fixed Delay <sup>2, 3</sup>                  |                             | 2.2              |                              | ns    |

#### Notes:

- 1. Maximum value obtained for a -2 speed-grade device in worst-case commercial conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

- 2. This delay is a function of voltage and temperature. See Table 2-6 on page 2-6 for deratings.

- 3.  $T_J = 25^{\circ}C$ , VCC = 1.5 V

- 4. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help for more information.

- Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to the PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by the period jitter parameter.

- 6. The A3P030 device does not contain a PLL.

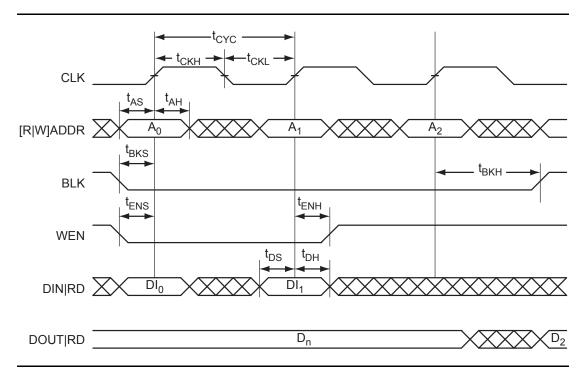

Figure 2-33 • RAM Write, Output Retained. Applicable to Both RAM4K9 and RAM512x18.

Figure 2-34 • RAM Write, Output as Write Data (WMODE = 1). Applicable to RAM4K9 Only.

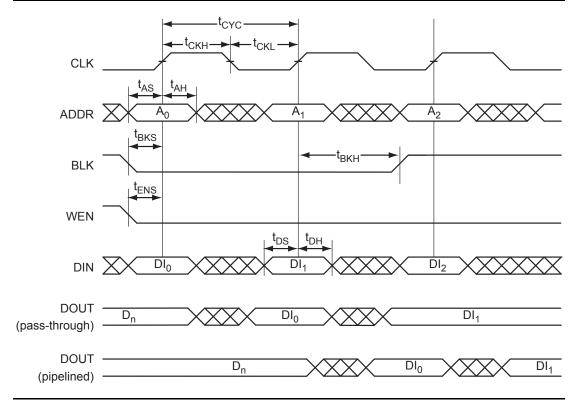

#### **FIFO**

Figure 2-36 • FIFO Model

## Package Pin Assignments

| 01140      |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| QN48       |                 |  |  |  |  |

| Pin Number | A3P030 Function |  |  |  |  |

| 1          | IO82RSB1        |  |  |  |  |

| 2          | GEC0/IO73RSB1   |  |  |  |  |

| 3          | GEA0/IO72RSB1   |  |  |  |  |

| 4          | GEB0/IO71RSB1   |  |  |  |  |

| 5          | GND             |  |  |  |  |

| 6          | VCCIB1          |  |  |  |  |

| 7          | IO68RSB1        |  |  |  |  |

| 8          | IO67RSB1        |  |  |  |  |

| 9          | IO66RSB1        |  |  |  |  |

| 10         | IO65RSB1        |  |  |  |  |

| 11         | IO64RSB1        |  |  |  |  |

| 12         | IO62RSB1        |  |  |  |  |

| 13         | IO61RSB1        |  |  |  |  |

| 14         | IO60RSB1        |  |  |  |  |

| 15         | IO57RSB1        |  |  |  |  |

| 16         | IO55RSB1        |  |  |  |  |

| 17         | IO53RSB1        |  |  |  |  |

| 18         | VCC             |  |  |  |  |

| 19         | VCCIB1          |  |  |  |  |

| 20         | IO46RSB1        |  |  |  |  |

| 21         | IO42RSB1        |  |  |  |  |

| 22         | TCK             |  |  |  |  |

| 23         | TDI             |  |  |  |  |

| 24         | TMS             |  |  |  |  |

| 25         | VPUMP           |  |  |  |  |

| 26         | TDO             |  |  |  |  |

| 27         | TRST            |  |  |  |  |

| 28         | VJTAG           |  |  |  |  |

| 29         | IO38RSB0        |  |  |  |  |

| 30         | GDB0/IO34RSB0   |  |  |  |  |

| 31         | GDA0/IO33RSB0   |  |  |  |  |

| 32         | GDC0/IO32RSB0   |  |  |  |  |

| 33         | VCCIB0          |  |  |  |  |

| 34         | GND             |  |  |  |  |

| 35         | VCC             |  |  |  |  |

| 36         | IO25RSB0        |  |  |  |  |

| QN48       |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| Pin Number | A3P030 Function |  |  |  |  |

| 37         | IO24RSB0        |  |  |  |  |

| 38         | IO22RSB0        |  |  |  |  |

| 39         | IO20RSB0        |  |  |  |  |

| 40         | IO18RSB0        |  |  |  |  |

| 41         | IO16RSB0        |  |  |  |  |

| 42         | IO14RSB0        |  |  |  |  |

| 43         | IO10RSB0        |  |  |  |  |

| 44         | IO08RSB0        |  |  |  |  |

| 45         | IO06RSB0        |  |  |  |  |

| 46         | IO04RSB0        |  |  |  |  |

| 47         | IO02RSB0        |  |  |  |  |

| 48         | IO00RSB0        |  |  |  |  |

4-2 Revision 18

| FG144      |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| Pin Number | A3P125 Function |  |  |  |  |

| K1         | GEB0/IO109RSB1  |  |  |  |  |

| K2         | GEA1/IO108RSB1  |  |  |  |  |

|            |                 |  |  |  |  |

| K3         | GEA0/IO107RSB1  |  |  |  |  |

| K4         | GEA2/IO106RSB1  |  |  |  |  |

| K5         | IO100RSB1       |  |  |  |  |

| K6         | IO98RSB1        |  |  |  |  |

| K7         | GND             |  |  |  |  |

| K8         | IO73RSB1        |  |  |  |  |

| K9         | GDC2/IO72RSB1   |  |  |  |  |

| K10        | GND             |  |  |  |  |

| K11        | GDA0/IO66RSB0   |  |  |  |  |

| K12        | GDB0/IO64RSB0   |  |  |  |  |

| L1         | GND             |  |  |  |  |

| L2         | VMV1            |  |  |  |  |

| L3         | GEB2/IO105RSB1  |  |  |  |  |

| L4         | IO102RSB1       |  |  |  |  |

| L5         | VCCIB1          |  |  |  |  |

| L6         | IO95RSB1        |  |  |  |  |

| L7         | IO85RSB1        |  |  |  |  |

| L8         | IO74RSB1        |  |  |  |  |

| L9         | TMS             |  |  |  |  |

| L10        | VJTAG           |  |  |  |  |

| L11        | VMV1            |  |  |  |  |

| L12        | TRST            |  |  |  |  |

| M1         | GNDQ            |  |  |  |  |

| M2         | GEC2/IO104RSB1  |  |  |  |  |

| M3         | IO103RSB1       |  |  |  |  |

| M4         | IO101RSB1       |  |  |  |  |

| M5         | IO97RSB1        |  |  |  |  |

| M6         | IO94RSB1        |  |  |  |  |

| M7         | IO86RSB1        |  |  |  |  |

| M8         | IO75RSB1        |  |  |  |  |

| M9         | TDI             |  |  |  |  |

| M10        | VCCIB1          |  |  |  |  |

| M11        | VPUMP           |  |  |  |  |

| M12        | GNDQ            |  |  |  |  |

| 2          | 55 %            |  |  |  |  |

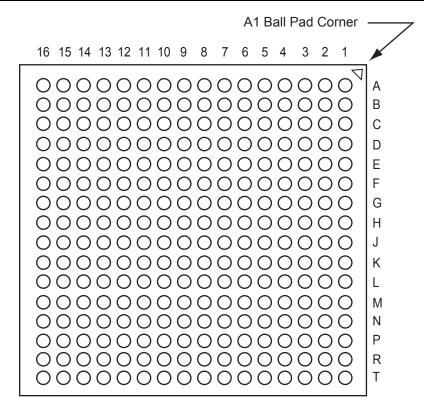

### FG256 - Bottom View

#### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

4-52 Revision 18

| FG256      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | A3P1000 Function |  |  |  |

| H3         | GFB1/IO208PPB3   |  |  |  |

| H4         | VCOMPLF          |  |  |  |

| H5         | GFC0/IO209NPB3   |  |  |  |

| H6         | VCC              |  |  |  |

| H7         | GND              |  |  |  |

| H8         | GND              |  |  |  |

| H9         | GND              |  |  |  |

| H10        | GND              |  |  |  |

| H11        | VCC              |  |  |  |

| H12        | GCC0/IO91NPB1    |  |  |  |

| H13        | GCB1/IO92PPB1    |  |  |  |

| H14        | GCA0/IO93NPB1    |  |  |  |

| H15        | IO96NPB1         |  |  |  |

| H16        | GCB0/IO92NPB1    |  |  |  |

| J1         | GFA2/IO206PSB3   |  |  |  |

| J2         | GFA1/IO207PDB3   |  |  |  |

| J3         | VCCPLF           |  |  |  |

| J4         | IO205NDB3        |  |  |  |

| J5         | GFB2/IO205PDB3   |  |  |  |

| J6         | VCC              |  |  |  |

| J7         | GND              |  |  |  |

| J8         | GND              |  |  |  |

| J9         | GND              |  |  |  |

| J10        | GND              |  |  |  |

| J11        | VCC              |  |  |  |

| J12        | GCB2/IO95PPB1    |  |  |  |

| J13        | GCA1/IO93PPB1    |  |  |  |

| J14        | GCC2/IO96PPB1    |  |  |  |

| J15        | IO100PPB1        |  |  |  |

| J16        | GCA2/IO94PSB1    |  |  |  |

| K1         | GFC2/IO204PDB3   |  |  |  |

| K2         | IO204NDB3        |  |  |  |

| K3         | IO203NDB3        |  |  |  |

| K4         | IO203PDB3        |  |  |  |

| K5         | VCCIB3           |  |  |  |

| K6         | VCC              |  |  |  |

| K7         | GND              |  |  |  |

| K8         | GND              |  |  |  |

|            |                  |  |  |  |

| FG256      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | A3P1000 Function |  |  |  |

| K9         | GND              |  |  |  |

| K10        | GND              |  |  |  |

| K11        | VCC              |  |  |  |

| K12        | VCCIB1           |  |  |  |

| K12        | IO95NPB1         |  |  |  |

| K14        | IO100NPB1        |  |  |  |

| K15        | IO102NDB1        |  |  |  |

| K16        | IO102PDB1        |  |  |  |

| L1         | IO202NDB3        |  |  |  |

| L2         | IO202PDB3        |  |  |  |

| L2<br>L3   |                  |  |  |  |

|            | IO196PPB3        |  |  |  |

| L4         | IO193PPB3        |  |  |  |

| L5         | VCCIB3           |  |  |  |

| L6         | GND              |  |  |  |

| L7         | VCC              |  |  |  |

| L8         | VCC              |  |  |  |

| L9         | VCC              |  |  |  |

| L10        | VCC              |  |  |  |

| L11        | GND              |  |  |  |

| L12        | VCCIB1           |  |  |  |

| L13        | GDB0/IO112NPB1   |  |  |  |

| L14        | IO106NDB1        |  |  |  |

| L15        | IO106PDB1        |  |  |  |

| L16        | IO107PDB1        |  |  |  |

| M1         | IO197NSB3        |  |  |  |

| M2         | IO196NPB3        |  |  |  |

| M3         | IO193NPB3        |  |  |  |

| M4         | GEC0/IO190NPB3   |  |  |  |

| M5         | VMV3             |  |  |  |

| M6         | VCCIB2           |  |  |  |

| M7         | VCCIB2           |  |  |  |

| M8         | IO147RSB2        |  |  |  |

| M9         | IO136RSB2        |  |  |  |

| M10        | VCCIB2           |  |  |  |

| M11        | VCCIB2           |  |  |  |

| M12        | VMV2             |  |  |  |

| M13        | IO110NDB1        |  |  |  |

| M14        | GDB1/IO112PPB1   |  |  |  |

|            |                  |  |  |  |

| FG256      |                   |  |  |  |

|------------|-------------------|--|--|--|

| Pin Number | A3P1000 Function  |  |  |  |

| M15        | GDC1/IO111PDB1    |  |  |  |

| M16        | IO107NDB1         |  |  |  |

| N1         | IO194PSB3         |  |  |  |

| N2         | IO192PPB3         |  |  |  |

| N3         | GEC1/IO190PPB3    |  |  |  |

| N4         | IO192NPB3         |  |  |  |

| N5         | GNDQ              |  |  |  |

| N6         | GEA2/IO187RSB2    |  |  |  |

| N7         | IO161RSB2         |  |  |  |

| N8         | IO155RSB2         |  |  |  |

| N9         | IO141RSB2         |  |  |  |

| N10        | IO141RSB2         |  |  |  |

| N10        | IO129RSB2         |  |  |  |

|            |                   |  |  |  |

| N12        | GNDQ<br>IO110PDP1 |  |  |  |

| N13        | IO110PDB1         |  |  |  |

| N14        | VJTAG             |  |  |  |

| N15        | GDC0/IO111NDB1    |  |  |  |

| N16        | GDA1/IO113PDB1    |  |  |  |

| P1         | GEB1/IO189PDB3    |  |  |  |

| P2         | GEB0/IO189NDB3    |  |  |  |

| P3         | VMV2              |  |  |  |

| P4         | IO179RSB2         |  |  |  |

| P5         | IO171RSB2         |  |  |  |

| P6         | IO165RSB2         |  |  |  |

| P7         | IO159RSB2         |  |  |  |

| P8         | IO151RSB2         |  |  |  |

| P9         | IO137RSB2         |  |  |  |

| P10        | IO134RSB2         |  |  |  |

| P11        | IO128RSB2         |  |  |  |

| P12        | VMV1              |  |  |  |

| P13        | TCK               |  |  |  |

| P14        | VPUMP             |  |  |  |

| P15        | TRST              |  |  |  |

| P16        | GDA0/IO113NDB1    |  |  |  |

| R1         | GEA1/IO188PDB3    |  |  |  |

| R2         | GEA0/IO188NDB3    |  |  |  |

| R3         | IO184RSB2         |  |  |  |

| R4         | GEC2/IO185RSB2    |  |  |  |

# 5 - Datasheet Information

## **List of Changes**

The following table lists critical changes that were made in each version of the ProASIC3 datasheet.

| Revision                       | Changes                                                                                                                                                                                                                                                           | Page                      |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Revision 18<br>(March 2016)    | Updated 3.3 V DC supply voltage's maximum Commercial and Industrial values from 3.3 V to 3.6 V in Table 2-2 (SAR 72693).                                                                                                                                          | 2-2                       |

|                                | Added reference of Package Mechanical Drawings document in all package pin assignment notes (76833).                                                                                                                                                              | NA                        |

| Revision 17                    | Removed PQFP embedded heat spreader info. from Table 2-5 (SAR 52320).                                                                                                                                                                                             | 2-6                       |

| (June 2015)                    | Updated "VCCIBx I/O Supply Voltage" (SAR 43323).                                                                                                                                                                                                                  | 3-1                       |

| Revision 16<br>(December 2014) | Updated "ProASIC3 Ordering Information". Interchanged the positions of Y- Security Feature and I- Application (Temperature Range) (SAR 61079). Added Note "Only devices with package size greater than or equal to 5x5 are supported".                            | 1-IV                      |

|                                | Updated Table Note (2) in Table 2-3 • Flash Programming Limits – Retention, Storage and Operating Temperature so that the Table Note is not applicable for Maximum Storage Temperature T <sub>STG</sub> (SAR 54297).                                              | 2-3                       |

|                                | Added values for Drive strength 2 mA in Table 2-41 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew, Table 2-42 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew, Table 2-43 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew, and Table 2-44 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew (SAR 57184). | 2-34, 2-35,<br>2-36, 2-37 |

|                                | Added Figure 2-1 • High-Temperature Data Retention (HTR) (SAR 45466).                                                                                                                                                                                             | 2-3                       |

|                                | Updates made to maintain the style and consistency of the document.                                                                                                                                                                                               | NA                        |

| Revision 15<br>(July 2014)     | Added corner pad table note (3) to "QN132 – Bottom View" (SAR 47442).                                                                                                                                                                                             | 4-6                       |

|                                | Ambient temperature removed in Table 2-2, table notes and "ProASIC3 Ordering Information" figure were modified (SAR 48343).                                                                                                                                       | 2-2<br>1-IV               |

|                                | Other updates were made to maintain the style and consistency of the datasheet.                                                                                                                                                                                   | NA                        |

| Revision 14<br>(April 2014)    | Note added for the discontinuance of QN132 package to the following tables and section: "ProASIC3 Devices", "I/Os Per Package 1", "ProASIC3 FPGAs Package Sizes Dimensions" and "QN132 – Bottom View" section (SAR 55118).                                        | I, III, 4-6               |

| Revision                       | Changes                                                                                                                                                                                                | Page            |