# E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                                  |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 147456                                                                    |

| Number of I/O                  | 154                                                                       |

| Number of Gates                | 1000000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                        |

| Package / Case                 | 208-BFQFP                                                                 |

| Supplier Device Package        | 208-PQFP (28x28)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p1000-1pq208i |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ProASIC3 Devices               | A3P015 <sup>1</sup> | A3P030                            | A3P060                  | A3P125             | A3P250                          | A3P400                     | A3P600                     | A3P1000                    |

|--------------------------------|---------------------|-----------------------------------|-------------------------|--------------------|---------------------------------|----------------------------|----------------------------|----------------------------|

| Cortex-M1 Devices <sup>2</sup> |                     |                                   |                         |                    | M1A3P250                        | M1A3P400                   | M1A3P600                   | M1A3P1000                  |

| Package Pins<br>QFN            | QN68                | QN48, QN68,<br>QN132 <sup>7</sup> | QN132 <sup>7</sup>      | QN132 <sup>7</sup> | QN132 <sup>7</sup>              |                            |                            |                            |

| CS<br>VQFP<br>TQFP             |                     | VQ100                             | CS121<br>VQ100<br>TQ144 | VQ100<br>TQ144     | VQ100                           |                            |                            |                            |

| PQFP<br>FBGA                   |                     |                                   | FG144                   | PQ208<br>FG144     | PQ208<br>FG144/256 <sup>5</sup> | PQ208<br>FG144/256/<br>484 | PQ208<br>FG144/256/<br>484 | PQ208<br>FG144/256/<br>484 |

Notes:

- A3P015 is not recommended for new designs.

Refer to the Cortex-M1 product brief for more information.

AES is not available for Cortex-M1 ProASIC3 devices.

Six chip (main) and three quadrant global networks are available for A3P060 and above.

The M1A3P250 device does not support this package.

For higher densities and support of additional features, refer to the ProASIC3E Flash Family FPGAs datasheet.

Package not available.

Your valuable IP is protected with industry-standard security, making remote ISP possible. A ProASIC3 device provides the best available security for programmable logic designs.

### Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system powerup (unlike SRAM-based FPGAs). Therefore, flash-based ProASIC3 FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

#### Instant On

Flash-based ProASIC3 devices support Level 0 of the Instant On classification standard. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. The Instant On feature of flash-based ProASIC3 devices greatly simplifies total system design and reduces total system cost, often eliminating the need for CPLDs and clock generation PLLs that are used for these purposes in a system. In addition, glitches and brownouts in system power will not corrupt the ProASIC3 device's flash configuration, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based ProASIC3 devices simplify total system design and reduce cost and design risk while increasing system reliability and improving system initialization time.

#### Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of ProASIC3 flash-based FPGAs. Once it is programmed, the flash cell configuration element of ProASIC3 FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

#### Low Power

Flash-based ProASIC3 devices exhibit power characteristics similar to an ASIC, making them an ideal choice for power-sensitive applications. ProASIC3 devices have only a very limited power-on current surge and no high-current transition period, both of which occur on many FPGAs.

ProASIC3 devices also have low dynamic power consumption to further maximize power savings.

## **Calculating Power Dissipation**

### **Quiescent Supply Current**

#### Table 2-7 • Quiescent Supply Current Characteristics

|                   | A3P015 | A3P030 | A3P060 | A3P125 | A3P250 | A3P400 | A3P600 | A3P1000 |

|-------------------|--------|--------|--------|--------|--------|--------|--------|---------|

| Typical (25°C)    | 2 mA   | 2 mA   | 2 mA   | 2 mA   | 3 mA   | 3 mA   | 5 mA   | 8 mA    |

| Max. (Commercial) | 10 mA  | 10 mA  | 10 mA  | 10 mA  | 20 mA  | 20 mA  | 30 mA  | 50 mA   |

| Max. (Industrial) | 15 mA  | 15 mA  | 15 mA  | 15 mA  | 30 mA  | 30 mA  | 45 mA  | 75 mA   |

Note: IDD Includes VCC, VPUMP, VCCI, and VMV currents. Values do not include I/O static contribution, which is shown in Table 2-11 and Table 2-12 on page 2-9.

### Power per I/O Pin

## Table 2-8 • Summary of I/O Input Buffer Power (Per Pin) – Default I/O Software Settings Applicable to Advanced I/O Banks

|                                      | VMV (V) | Static Power<br>P <sub>DC2</sub> (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (μW/MHz) <sup>2</sup> |

|--------------------------------------|---------|----------------------------------------------------|---------------------------------------------|

| Single-Ended                         |         | 1                                                  |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 3.3     | -                                                  | 16.22                                       |

| 3.3 V LVCMOS Wide Range <sup>3</sup> | 3.3     | -                                                  | 16.22                                       |

| 2.5 V LVCMOS                         | 2.5     | -                                                  | 5.12                                        |

| 1.8 V LVCMOS                         | 1.8     | -                                                  | 2.13                                        |

| 1.5 V LVCMOS (JESD8-11)              | 1.5     | -                                                  | 1.45                                        |

| 3.3 V PCI                            | 3.3     | -                                                  | 18.11                                       |

| 3.3 V PCI-X                          | 3.3     | -                                                  | 18.11                                       |

| Differential                         |         |                                                    |                                             |

| LVDS                                 | 2.5     | 2.26                                               | 1.20                                        |

| LVPECL                               | 3.3     | 5.72                                               | 1.87                                        |

Notes:

- 1. PDC2 is the static power (where applicable) measured on VMV.

- 2. PAC9 is the total dynamic power measured on VCC and VMV.

- 3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

## Table 2-9 • Summary of I/O Input Buffer Power (Per Pin) – Default I/O Software Settings Applicable to Standard Plus I/O Banks

|                                      | VMV (V) | Static Power<br>PDC2 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (µW/MHz) <sup>2</sup> |

|--------------------------------------|---------|----------------------------------------|---------------------------------------------|

| Single-Ended                         |         |                                        |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 3.3     | -                                      | 16.23                                       |

| 3.3 V LVCMOS Wide Range <sup>3</sup> | 3.3     | -                                      | 16.23                                       |

#### Notes:

- 1. PDC2 is the static power (where applicable) measured on VMV.

- 2. PAC9 is the total dynamic power measured on VCC and VMV.

- 3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

#### Table 2-13 • Summary of I/O Output Buffer Power (Per Pin) – Default I/O Software Settings <sup>1</sup> Applicable to Standard I/O Banks

|                                      | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC3 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (µW/MHz) <sup>3</sup> |

|--------------------------------------|------------------------|----------|----------------------------------------|----------------------------------------------|

| Single-Ended                         |                        |          |                                        |                                              |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 35                     | 3.3      | -                                      | 431.08                                       |

| 3.3 V LVCMOS Wide Range <sup>4</sup> | 35                     | 3.3      | -                                      | 431.08                                       |

| 2.5 V LVCMOS                         | 35                     | 2.5      | -                                      | 247.36                                       |

| 1.8 V LVCMOS                         | 35                     | 1.8      | -                                      | 128.46                                       |

| 1.5 V LVCMOS (JESD8-11)              | 35                     | 1.5      | -                                      | 89.46                                        |

Notes:

1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

2. P<sub>DC3</sub> is the static power (where applicable) measured on VCCI.

3. P<sub>AC10</sub> is the total dynamic power measured on VCC and VCCI.

4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

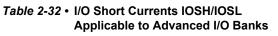

|                                      | Drive Strength                 | IOSL (mA) <sup>1</sup>          | IOSH (mA) <sup>1</sup>          |  |

|--------------------------------------|--------------------------------|---------------------------------|---------------------------------|--|

| 3.3 V LVTTL / 3.3 V LVCMOS           | 2 mA                           | 27                              | 25                              |  |

|                                      | 4 mA                           | 27                              | 25                              |  |

|                                      | 6 mA                           | 54                              | 51                              |  |

|                                      | 8 mA                           | 54                              | 51                              |  |

|                                      | 12 mA                          | 109                             | 103                             |  |

|                                      | 16 mA                          | 127                             | 132                             |  |

|                                      | 24 mA                          | 181                             | 268                             |  |

| 3.3 V LVCMOS Wide Range <sup>2</sup> | 100 µA                         | Same as regular 3.3 V<br>LVCMOS | Same as regular 3.3 V<br>LVCMOS |  |

| 2.5 V LVCMOS                         | 2 mA                           | 18                              | 16                              |  |

|                                      | 4 mA                           | 18                              | 16                              |  |

|                                      | 6 mA                           | 37                              | 32                              |  |

|                                      | 8 mA                           | 37                              | 32                              |  |

|                                      | 12 mA                          | 74                              | 65                              |  |

|                                      | 16 mA                          | 87                              | 83                              |  |

|                                      | 24 mA                          | 124                             | 169                             |  |

| 1.8 V LVCMOS                         | 2 mA                           | 11                              | 9                               |  |

|                                      | 4 mA                           | 22                              | 17                              |  |

|                                      | 6 mA                           | 44                              | 35                              |  |

|                                      | 8 mA                           | 51                              | 45                              |  |

|                                      | 12 mA                          | 74                              | 91                              |  |

|                                      | 16 mA                          | 74                              | 91                              |  |

| 1.5 V LVCMOS                         | 2 mA                           | 16                              | 13                              |  |

|                                      | 4 mA                           | 33                              | 25                              |  |

|                                      | 6 mA                           | 39                              | 32                              |  |

|                                      | 8 mA                           | 55                              | 66                              |  |

|                                      | 12 mA                          | 55                              | 66                              |  |

| 3.3 V PCI/PCI-X                      | Per PCI/PCI-X<br>specification | 109                             | 103                             |  |

) Microsemi.

Power Matters."

Notes:

1.  $T_J = 100^{\circ}C$

Applicable to 3.3 V LVCMOS Wide Range. I<sub>OSL</sub>/I<sub>OSH</sub> dependent on the I/O buffer drive strength selected for wide range applications. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

#### Table 2-51 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew

Commercial-Case Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Advanced I/O Banks

| Applicable to Advanced I/O Banks |                                                                           |                |                   |                 |                  |                 |                   |                 |                 |                 |                 |                  |                  |       |

|----------------------------------|---------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength                | Equiv.<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>dout</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>zL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

| 100 µA                           | 2 mA                                                                      | Std.           | 0.60              | 15.86           | 0.04             | 1.54            | 0.43              | 15.86           | 13.51           | 4.09            | 3.80            | 19.25            | 16.90            | ns    |

|                                  |                                                                           | -1             | 0.51              | 13.49           | 0.04             | 1.31            | 0.36              | 13.49           | 11.49           | 3.48            | 3.23            | 16.38            | 14.38            | ns    |

|                                  |                                                                           | -2             | 0.45              | 11.84           | 0.03             | 1.15            | 0.32              | 11.84           | 10.09           | 3.05            | 2.84            | 14.38            | 12.62            | ns    |

| 100 µA                           | 4 mA                                                                      | Std.           | 0.60              | 11.25           | 0.04             | 1.54            | 0.43              | 11.25           | 9.54            | 4.61            | 4.70            | 14.64            | 12.93            | ns    |

|                                  |                                                                           | -1             | 0.51              | 9.57            | 0.04             | 1.31            | 0.36              | 9.57            | 8.11            | 3.92            | 4.00            | 12.46            | 11.00            | ns    |

|                                  |                                                                           | -2             | 0.45              | 8.40            | 0.03             | 1.15            | 0.32              | 8.40            | 7.12            | 3.44            | 3.51            | 10.93            | 9.66             | ns    |

| 100 µA                           | 6 mA                                                                      | Std.           | 0.60              | 11.25           | 0.04             | 1.54            | 0.43              | 11.25           | 9.54            | 4.61            | 4.70            | 14.64            | 12.93            | ns    |

|                                  |                                                                           | -1             | 0.51              | 9.57            | 0.04             | 1.31            | 0.36              | 9.57            | 8.11            | 3.92            | 4.00            | 12.46            | 11.00            | ns    |

|                                  |                                                                           | -2             | 0.45              | 8.40            | 0.03             | 1.15            | 0.32              | 8.40            | 7.12            | 3.44            | 3.51            | 10.93            | 9.66             | ns    |

| 100 µA                           | 8 mA                                                                      | Std.           | 0.60              | 8.63            | 0.04             | 1.54            | 0.43              | 8.63            | 7.39            | 4.96            | 5.28            | 12.02            | 10.79            | ns    |

|                                  |                                                                           | -1             | 0.51              | 7.34            | 0.04             | 1.31            | 0.36              | 7.34            | 6.29            | 4.22            | 4.49            | 10.23            | 9.18             | ns    |

|                                  |                                                                           | -2             | 0.45              | 6.44            | 0.03             | 1.15            | 0.32              | 6.44            | 5.52            | 3.70            | 3.94            | 8.98             | 8.06             | ns    |

| 100 µA                           | 16 mA                                                                     | Std.           | 0.60              | 8.05            | 0.04             | 1.54            | 0.43              | 8.05            | 6.93            | 5.03            | 5.43            | 11.44            | 10.32            | ns    |

|                                  |                                                                           | -1             | 0.51              | 6.85            | 0.04             | 1.31            | 0.36              | 6.85            | 5.90            | 4.28            | 4.62            | 9.74             | 8.78             | ns    |

|                                  |                                                                           | -2             | 0.45              | 6.01            | 0.03             | 1.15            | 0.32              | 6.01            | 5.18            | 3.76            | 4.06            | 8.55             | 7.71             | ns    |

| 100 µA                           | 24 mA                                                                     | Std.           | 0.60              | 7.50            | 0.04             | 1.54            | 0.43              | 7.50            | 6.90            | 5.13            | 6.00            | 10.89            | 10.29            | ns    |

|                                  |                                                                           | -1             | 0.51              | 6.38            | 0.04             | 1.31            | 0.36              | 6.38            | 5.87            | 4.36            | 5.11            | 9.27             | 8.76             | ns    |

|                                  |                                                                           | -2             | 0.45              | 5.60            | 0.03             | 1.15            | 0.32              | 5.60            | 5.15            | 3.83            | 4.48            | 8.13             | 7.69             | ns    |

Notes:

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

| Table 2-62 •      | 2.5 V LV<br>Commer<br>Applicat | cial-Cas          | e Cond          | itions:          |                 |                   | st-Case         | • VCC =         | = 1.425         | V, Wor          | st-Case          | VCCI = 2         | 2.3 V |

|-------------------|--------------------------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade                 | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 4 mA              | Std.                           | 0.66              | 8.28            | 0.04             | 1.30            | 0.43              | 7.41            | 8.28            | 2.25            | 2.07            | 9.64             | 10.51            | ns    |

|                   | -1                             | 0.56              | 7.04            | 0.04             | 1.10            | 0.36              | 6.30            | 7.04            | 1.92            | 1.76            | 8.20             | 8.94             | ns    |

|                   | -2                             | 0.49              | 6.18            | 0.03             | 0.97            | 0.32              | 5.53            | 6.18            | 1.68            | 1.55            | 7.20             | 7.85             | ns    |

| 6 mA              | Std.                           | 0.66              | 4.85            | 0.04             | 1.30            | 0.43              | 4.65            | 4.85            | 2.59            | 2.71            | 6.88             | 7.09             | ns    |

|                   | -1                             | 0.56              | 4.13            | 0.04             | 1.10            | 0.36              | 3.95            | 4.13            | 2.20            | 2.31            | 5.85             | 6.03             | ns    |

|                   | -2                             | 0.49              | 3.62            | 0.03             | 0.97            | 0.32              | 3.47            | 3.62            | 1.93            | 2.02            | 5.14             | 5.29             | ns    |

| 8 mA              | Std.                           | 0.66              | 4.85            | 0.04             | 1.30            | 0.43              | 4.65            | 4.85            | 2.59            | 2.71            | 6.88             | 7.09             | ns    |

|                   | -1                             | 0.56              | 4.13            | 0.04             | 1.10            | 0.36              | 3.95            | 4.13            | 2.20            | 2.31            | 5.85             | 6.03             | ns    |

|                   | -2                             | 0.49              | 3.62            | 0.03             | 0.97            | 0.32              | 3.47            | 3.62            | 1.93            | 2.02            | 5.14             | 5.29             | ns    |

| 12 mA             | Std.                           | 0.66              | 3.21            | 0.04             | 1.30            | 0.43              | 3.27            | 3.14            | 2.82            | 3.11            | 5.50             | 5.38             | ns    |

|                   | -1                             | 0.56              | 2.73            | 0.04             | 1.10            | 0.36              | 2.78            | 2.67            | 2.40            | 2.65            | 4.68             | 4.57             | ns    |

|                   | -2                             | 0.49              | 2.39            | 0.03             | 0.97            | 0.32              | 2.44            | 2.35            | 2.11            | 2.32            | 4.11             | 4.02             | ns    |

Microsomi

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-63 • 2.5 V LVCMOS Low Slew Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Standard Plus I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 10.84           | 0.04             | 1.30            | 0.43              | 10.64           | 10.84           | 2.26            | 1.99            | 12.87            | 13.08            | ns    |

|                   | –1             | 0.56              | 9.22            | 0.04             | 1.10            | 0.36              | 9.05            | 9.22            | 1.92            | 1.69            | 10.95            | 11.12            | ns    |

|                   | -2             | 0.49              | 8.10            | 0.03             | 0.97            | 0.32              | 7.94            | 8.10            | 1.68            | 1.49            | 9.61             | 9.77             | ns    |

| 6 mA              | Std.           | 0.66              | 7.37            | 0.04             | 1.30            | 0.43              | 7.50            | 7.36            | 2.59            | 2.61            | 9.74             | 9.60             | ns    |

|                   | –1             | 0.56              | 6.27            | 0.04             | 1.10            | 0.36              | 6.38            | 6.26            | 2.20            | 2.22            | 8.29             | 8.16             | ns    |

|                   | -2             | 0.49              | 5.50            | 0.03             | 0.97            | 0.32              | 5.60            | 5.50            | 1.93            | 1.95            | 7.27             | 7.17             | ns    |

| 8 mA              | Std.           | 0.66              | 7.37            | 0.04             | 1.30            | 0.43              | 7.50            | 7.36            | 2.59            | 2.61            | 9.74             | 9.60             | ns    |

|                   | -1             | 0.56              | 6.27            | 0.04             | 1.10            | 0.36              | 6.38            | 6.26            | 2.20            | 2.22            | 8.29             | 8.16             | ns    |

|                   | -2             | 0.49              | 5.50            | 0.03             | 0.97            | 0.32              | 5.60            | 5.50            | 1.93            | 1.95            | 7.27             | 7.17             | ns    |

| 12 mA             | Std.           | 0.66              | 5.63            | 0.04             | 1.30            | 0.43              | 5.73            | 5.51            | 2.83            | 3.01            | 7.97             | 7.74             | ns    |

|                   | –1             | 0.56              | 4.79            | 0.04             | 1.10            | 0.36              | 4.88            | 4.68            | 2.41            | 2.56            | 6.78             | 6.59             | ns    |

|                   | -2             | 0.49              | 4.20            | 0.03             | 0.97            | 0.32              | 4.28            | 4.11            | 2.11            | 2.25            | 5.95             | 5.78             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## B-LVDS/M-LVDS

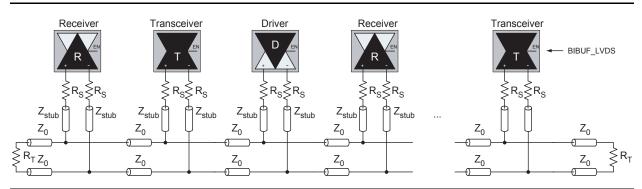

Bus LVDS (B-LVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to highperformance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The drivers require series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus since the driver can be located anywhere on the bus. These configurations can be implemented using the TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-13. The input and output buffer delays are available in the LVDS section in Table 2-92.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case Industrial operating conditions, at the farthest receiver:  $R_S = 60 \Omega$  and  $R_T = 70 \Omega$ , given  $Z_0 = 50 \Omega$  (2") and  $Z_{stub} = 50 \Omega$  (~1.5").

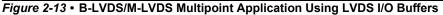

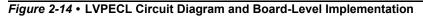

### LVPECL

Low-Voltage Positive Emitter-Coupled Logic (LVPECL) is another differential I/O standard. It requires that one data bit be carried through two signal lines. Like LVDS, two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-14. The building blocks of the LVPECL transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVDS implementation because the output standard specifications are different.

## **Timing Characteristics**

| Combinatorial Cell | Equation                  | Parameter       | -2   | -1   | Std. | Units |

|--------------------|---------------------------|-----------------|------|------|------|-------|

| INV                | Y = !A                    | t <sub>PD</sub> | 0.40 | 0.46 | 0.54 | ns    |

| AND2               | $Y = A \cdot B$           | t <sub>PD</sub> | 0.47 | 0.54 | 0.63 | ns    |

| NAND2              | Y = !(A · B)              | t <sub>PD</sub> | 0.47 | 0.54 | 0.63 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 0.49 | 0.55 | 0.65 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 0.49 | 0.55 | 0.65 | ns    |

| XOR2               | Y = A ⊕ B                 | t <sub>PD</sub> | 0.74 | 0.84 | 0.99 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 0.70 | 0.79 | 0.93 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 0.87 | 1.00 | 1.17 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 0.51 | 0.58 | 0.68 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 0.56 | 0.64 | 0.75 | ns    |

#### Table 2-105 • Combinatorial Cell Propagation Delays

Commercial-Case Conditions: T<sub>1</sub> = 70°C, Worst-Case VCC = 1.425 V

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## VersaTile Specifications as a Sequential Module

The ProASIC3 library offers a wide variety of sequential cells, including flip-flops and latches. Each has a data input and optional enable, clear, or preset. In this section, timing characteristics are presented for a representative sample from the library. For more details, refer to the *Fusion, IGLOO/e, and ProASIC3/E Macro Library Guide*.

Figure 2-26 • Sample of Sequential Cells

Package Pin Assignments

|            | QN132           |

|------------|-----------------|

| Pin Number | A3P125 Function |

| C17        | IO83RSB1        |

| C18        | VCCIB1          |

| C19        | ТСК             |

| C20        | VMV1            |

| C21        | VPUMP           |

| C22        | VJTAG           |

| C23        | VCCIB0          |

| C24        | NC              |

| C25        | NC              |

| C26        | GCA1/IO55RSB0   |

| C27        | GCC0/IO52RSB0   |

| C28        | VCCIB0          |

| C29        | IO42RSB0        |

| C30        | GNDQ            |

| C31        | GBA1/IO40RSB0   |

| C32        | GBB0/IO37RSB0   |

| C33        | VCC             |

| C34        | IO24RSB0        |

| C35        | IO19RSB0        |

| C36        | IO16RSB0        |

| C37        | IO10RSB0        |

| C38        | VCCIB0          |

| C39        | GAB1/IO03RSB0   |

| C40        | VMV0            |

| D1         | GND             |

| D2         | GND             |

| D3         | GND             |

| D4         | GND             |

| QN132      |                 | QN132      |                 | QN132      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number | A3P250 Function |

| A1         | GAB2/IO117UPB3  | A37        | GBB1/IO38RSB0   | B25        | GND             |

| A2         | IO117VPB3       | A38        | GBC0/IO35RSB0   | B26        | IO54PDB1        |

| A3         | VCCIB3          | A39        | VCCIB0          | B27        | GCB2/IO52PDB1   |

| A4         | GFC1/IO110PDB3  | A40        | IO28RSB0        | B28        | GND             |

| A5         | GFB0/IO109NPB3  | A41        | IO22RSB0        | B29        | GCB0/IO49NDB1   |

| A6         | VCCPLF          | A42        | IO18RSB0        | B30        | GCC1/IO48PDB1   |

| A7         | GFA1/IO108PPB3  | A43        | IO14RSB0        | B31        | GND             |

| A8         | GFC2/IO105PPB3  | A44        | IO11RSB0        | B32        | GBB2/IO42PDB1   |

| A9         | IO103NDB3       | A45        | IO07RSB0        | B33        | VMV1            |

| A10        | VCC             | A46        | VCC             | B34        | GBA0/IO39RSB0   |

| A11        | GEA1/IO98PPB3   | A47        | GAC1/IO05RSB0   | B35        | GBC1/IO36RSB0   |

| A12        | GEA0/IO98NPB3   | A48        | GAB0/IO02RSB0   | B36        | GND             |

| A13        | GEC2/IO95RSB2   | B1         | IO118VDB3       | B37        | IO26RSB0        |

| A14        | IO91RSB2        | B2         | GAC2/IO116UDB3  | B38        | IO21RSB0        |

| A15        | VCC             | B3         | GND             | B39        | GND             |

| A16        | IO90RSB2        | B4         | GFC0/IO110NDB3  | B40        | IO13RSB0        |

| A17        | IO87RSB2        | B5         | VCOMPLF         | B41        | IO08RSB0        |

| A18        | IO85RSB2        | B6         | GND             | B42        | GND             |

| A19        | IO82RSB2        | B7         | GFB2/IO106PSB3  | B43        | GAC0/IO04RSB0   |

| A20        | IO76RSB2        | B8         | IO103PDB3       | B44        | GNDQ            |

| A21        | IO70RSB2        | B9         | GND             | C1         | GAA2/IO118UDB3  |

| A22        | VCC             | B10        | GEB0/IO99NDB3   | C2         | IO116VDB3       |

| A23        | GDB2/IO62RSB2   | B11        | VMV3            | C3         | VCC             |

| A24        | TDI             | B12        | GEB2/IO96RSB2   | C4         | GFB1/IO109PPB3  |

| A25        | TRST            | B13        | IO92RSB2        | C5         | GFA0/IO108NPB3  |

| A26        | GDC1/IO58UDB1   | B14        | GND             | C6         | GFA2/IO107PSB3  |

| A27        | VCC             | B15        | IO89RSB2        | C7         | IO105NPB3       |

| A28        | IO54NDB1        | B16        | IO86RSB2        | C8         | VCCIB3          |

| A29        | IO52NDB1        | B17        | GND             | C9         | GEB1/IO99PDB3   |

| A30        | GCA2/IO51PPB1   | B18        | IO78RSB2        | C10        | GNDQ            |

| A31        | GCA0/IO50NPB1   | B19        | IO72RSB2        | C11        | GEA2/IO97RSB2   |

| A32        | GCB1/IO49PDB1   | B20        | GND             | C12        | IO94RSB2        |

| A33        | IO47NSB1        | B21        | GNDQ            | C13        | VCCIB2          |

| A34        | VCC             | B22        | TMS             | C14        | IO88RSB2        |

| A35        | IO41NPB1        | B23        | TDO             | C15        | IO84RSB2        |

| A36        | GBA2/IO41PPB1   | B24        | GDC0/IO58VDB1   | C16        | IO80RSB2        |

🌜 Microsemi.

Package Pin Assignments

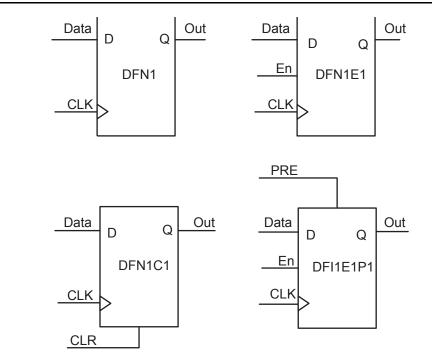

## VQ100 – Top View

## Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

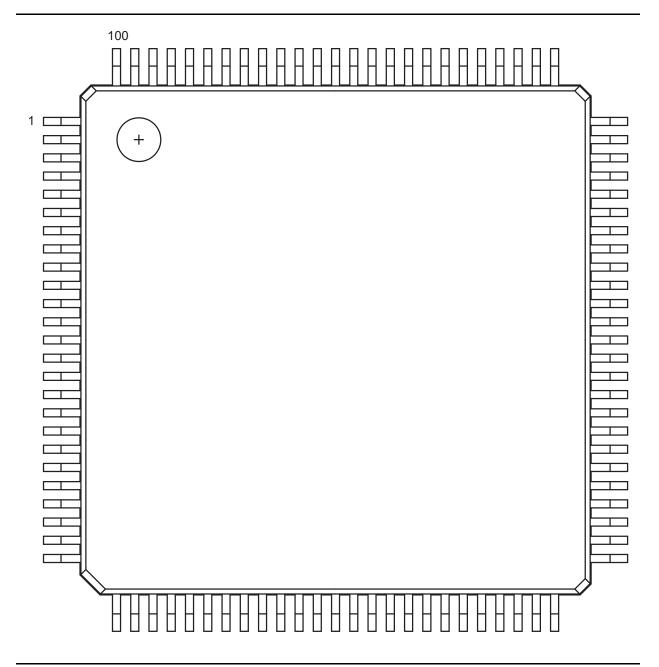

## TQ144 – Top View

### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

## 🌜 Microsemi.

Package Pin Assignments

| PQ208      |                 | PQ208      |                 | PQ208      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P400 Function | Pin Number | A3P400 Function | Pin Number | A3P400 Function |

| 109        | TRST            | 145        | IO64PDB1        | 181        | IO27RSB0        |

| 110        | VJTAG           | 146        | IO63NDB1        | 182        | IO26RSB0        |

| 111        | GDA0/IO79VDB1   | 147        | IO63PDB1        | 183        | IO25RSB0        |

| 112        | GDA1/IO79UDB1   | 148        | IO62NDB1        | 184        | IO24RSB0        |

| 113        | GDB0/IO78VDB1   | 149        | GBC2/IO62PDB1   | 185        | IO23RSB0        |

| 114        | GDB1/IO78UDB1   | 150        | IO61NDB1        | 186        | VCCIB0          |

| 115        | GDC0/IO77VDB1   | 151        | GBB2/IO61PDB1   | 187        | VCC             |

| 116        | GDC1/IO77UDB1   | 152        | IO60NDB1        | 188        | IO21RSB0        |

| 117        | IO76VDB1        | 153        | GBA2/IO60PDB1   | 189        | IO20RSB0        |

| 118        | IO76UDB1        | 154        | VMV1            | 190        | IO19RSB0        |

| 119        | IO75NDB1        | 155        | GNDQ            | 191        | IO18RSB0        |

| 120        | IO75PDB1        | 156        | GND             | 192        | IO17RSB0        |

| 121        | IO74RSB1        | 157        | VMV0            | 193        | IO16RSB0        |

| 122        | GND             | 158        | GBA1/IO59RSB0   | 194        | IO15RSB0        |

| 123        | VCCIB1          | 159        | GBA0/IO58RSB0   | 195        | GND             |

| 124        | NC              | 160        | GBB1/IO57RSB0   | 196        | IO13RSB0        |

| 125        | NC              | 161        | GBB0/IO56RSB0   | 197        | IO11RSB0        |

| 126        | VCC             | 162        | GND             | 198        | IO09RSB0        |

| 127        | IO72NDB1        | 163        | GBC1/IO55RSB0   | 199        | IO07RSB0        |

| 128        | GCC2/IO72PDB1   | 164        | GBC0/IO54RSB0   | 200        | VCCIB0          |

| 129        | GCB2/IO71PSB1   | 165        | IO52RSB0        | 201        | GAC1/IO05RSB0   |

| 130        | GND             | 166        | IO49RSB0        | 202        | GAC0/IO04RSB0   |

| 131        | GCA2/IO70PSB1   | 167        | IO46RSB0        | 203        | GAB1/IO03RSB0   |

| 132        | GCA1/IO69PDB1   | 168        | IO43RSB0        | 204        | GAB0/IO02RSB0   |

| 133        | GCA0/IO69NDB1   | 169        | IO40RSB0        | 205        | GAA1/IO01RSB0   |

| 134        | GCB0/IO68NDB1   | 170        | VCCIB0          | 206        | GAA0/IO00RSB0   |

| 135        | GCB1/IO68PDB1   | 171        | VCC             | 207        | GNDQ            |

| 136        | GCC0/IO67NDB1   | 172        | IO36RSB0        | 208        | VMV0            |

| 137        | GCC1/IO67PDB1   | 173        | IO35RSB0        |            |                 |

| 138        | IO66NDB1        | 174        | IO34RSB0        |            |                 |

| 139        | IO66PDB1        | 175        | IO33RSB0        |            |                 |

| 140        | VCCIB1          | 176        | IO32RSB0        |            |                 |

| 141        | GND             | 177        | IO31RSB0        |            |                 |

| 142        | VCC             | 178        | GND             |            |                 |

| 143        | IO65RSB1        | 179        | IO29RSB0        |            |                 |

| 144        | IO64NDB1        | 180        | IO28RSB0        |            |                 |

## 🌜 Microsemi.

Package Pin Assignments

|            | FG484           | FG484      |                 | FG484      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P400 Function | Pin Number | A3P400 Function | Pin Number | A3P400 Function |

| K19        | IO73NDB1        | M11        | GND             | P3         | NC              |

| K20        | NC              | M12        | GND             | P4         | IO142NDB3       |

| K21        | NC              | M13        | GND             | P5         | IO141NPB3       |

| K22        | NC              | M14        | VCC             | P6         | IO125RSB2       |

| L1         | NC              | M15        | GCB2/IO71PPB1   | P7         | IO139RSB3       |

| L2         | NC              | M16        | GCA1/IO69PPB1   | P8         | VCCIB3          |

| L3         | NC              | M17        | GCC2/IO72PPB1   | P9         | GND             |

| L4         | GFB0/IO146NPB3  | M18        | NC              | P10        | VCC             |

| L5         | GFA0/IO145NDB3  | M19        | GCA2/IO70PDB1   | P11        | VCC             |

| L6         | GFB1/IO146PPB3  | M20        | NC              | P12        | VCC             |

| L7         | VCOMPLF         | M21        | NC              | P13        | VCC             |

| L8         | GFC0/IO147NPB3  | M22        | NC              | P14        | GND             |

| L9         | VCC             | N1         | NC              | P15        | VCCIB1          |

| L10        | GND             | N2         | NC              | P16        | GDB0/IO78VPB1   |

| L11        | GND             | N3         | NC              | P17        | IO76VDB1        |

| L12        | GND             | N4         | GFC2/IO142PDB3  | P18        | IO76UDB1        |

| L13        | GND             | N5         | IO144NPB3       | P19        | IO75PDB1        |

| L14        | VCC             | N6         | IO141PPB3       | P20        | NC              |

| L15        | GCC0/IO67NPB1   | N7         | IO120RSB2       | P21        | NC              |

| L16        | GCB1/IO68PPB1   | N8         | VCCIB3          | P22        | NC              |

| L17        | GCA0/IO69NPB1   | N9         | VCC             | R1         | NC              |

| L18        | NC              | N10        | GND             | R2         | NC              |

| L19        | GCB0/IO68NPB1   | N11        | GND             | R3         | VCC             |

| L20        | NC              | N12        | GND             | R4         | IO140PDB3       |

| L21        | NC              | N13        | GND             | R5         | IO130RSB2       |

| L22        | NC              | N14        | VCC             | R6         | IO138NPB3       |

| M1         | NC              | N15        | VCCIB1          | R7         | GEC0/IO137NPB3  |

| M2         | NC              | N16        | IO71NPB1        | R8         | VMV3            |

| M3         | NC              | N17        | IO74RSB1        | R9         | VCCIB2          |

| M4         | GFA2/IO144PPB3  | N18        | IO72NPB1        | R10        | VCCIB2          |

| M5         | GFA1/IO145PDB3  | N19        | IO70NDB1        | R11        | IO108RSB2       |

| M6         | VCCPLF          | N20        | NC              | R12        | IO101RSB2       |

| M7         | IO143NDB3       | N21        | NC              | R13        | VCCIB2          |

| M8         | GFB2/IO143PDB3  | N22        | NC              | R14        | VCCIB2          |

| M9         | VCC             | P1         | NC              | R15        | VMV2            |

| M10        | GND             | P2         | NC              | R16        | IO83RSB2        |

|            | FG484           |            | FG484           |            | FG484           |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P600 Function | Pin Number | A3P600 Function | Pin Number | A3P600 Function |

| K19        | IO75NDB1        | M11        | GND             | P3         | IO153NDB3       |

| K20        | NC              | M12        | GND             | P4         | IO159NDB3       |

| K21        | IO76NDB1        | M13        | GND             | P5         | IO156NPB3       |

| K22        | IO76PDB1        | M14        | VCC             | P6         | IO151PPB3       |

| L1         | NC              | M15        | GCB2/IO73PPB1   | P7         | IO158PPB3       |

| L2         | IO155PDB3       | M16        | GCA1/IO71PPB1   | P8         | VCCIB3          |

| L3         | NC              | M17        | GCC2/IO74PPB1   | P9         | GND             |

| L4         | GFB0/IO163NPB3  | M18        | IO80PPB1        | P10        | VCC             |

| L5         | GFA0/IO162NDB3  | M19        | GCA2/IO72PDB1   | P11        | VCC             |

| L6         | GFB1/IO163PPB3  | M20        | IO79PPB1        | P12        | VCC             |

| L7         | VCOMPLF         | M21        | IO78PPB1        | P13        | VCC             |

| L8         | GFC0/IO164NPB3  | M22        | NC              | P14        | GND             |

| L9         | VCC             | N1         | IO154NDB3       | P15        | VCCIB1          |

| L10        | GND             | N2         | IO154PDB3       | P16        | GDB0/IO87NPB1   |

| L11        | GND             | N3         | NC              | P17        | IO85NDB1        |

| L12        | GND             | N4         | GFC2/IO159PDB3  | P18        | IO85PDB1        |

| L13        | GND             | N5         | IO161NPB3       | P19        | IO84PDB1        |

| L14        | VCC             | N6         | IO156PPB3       | P20        | NC              |

| L15        | GCC0/IO69NPB1   | N7         | IO129RSB2       | P21        | IO81PDB1        |

| L16        | GCB1/IO70PPB1   | N8         | VCCIB3          | P22        | NC              |

| L17        | GCA0/IO71NPB1   | N9         | VCC             | R1         | NC              |

| L18        | IO67NPB1        | N10        | GND             | R2         | NC              |

| L19        | GCB0/IO70NPB1   | N11        | GND             | R3         | VCC             |

| L20        | IO77PDB1        | N12        | GND             | R4         | IO150PDB3       |

| L21        | IO77NDB1        | N13        | GND             | R5         | IO151NPB3       |

| L22        | IO78NPB1        | N14        | VCC             | R6         | IO147NPB3       |

| M1         | NC              | N15        | VCCIB1          | R7         | GEC0/IO146NPB3  |

| M2         | IO155NDB3       | N16        | IO73NPB1        | R8         | VMV3            |

| M3         | IO158NPB3       | N17        | IO80NPB1        | R9         | VCCIB2          |

| M4         | GFA2/IO161PPB3  | N18        | IO74NPB1        | R10        | VCCIB2          |

| M5         | GFA1/IO162PDB3  | N19        | IO72NDB1        | R11        | IO117RSB2       |

| M6         | VCCPLF          | N20        | NC              | R12        | IO110RSB2       |

| M7         | IO160NDB3       | N21        | IO79NPB1        | R13        | VCCIB2          |

| M8         | GFB2/IO160PDB3  | N22        | NC              | R14        | VCCIB2          |

| M9         | VCC             | P1         | NC              | R15        | VMV2            |

| M10        | GND             | P2         | IO153PDB3       | R16        | IO94RSB2        |

| FG484      |                  | FG484      |                  |            | FG484            |  |

|------------|------------------|------------|------------------|------------|------------------|--|

| Pin Number | A3P1000 Function | Pin Number | A3P1000 Function | Pin Number | A3P1000 Function |  |

| E21        | NC               | G13        | IO52RSB0         | J5         | IO218NDB3        |  |

| E22        | IO84PDB1         | G14        | IO60RSB0         | J6         | IO216PDB3        |  |

| F1         | NC               | G15        | GNDQ             | J7         | IO216NDB3        |  |

| F2         | IO215PDB3        | G16        | IO80NDB1         | J8         | VCCIB3           |  |

| F3         | IO215NDB3        | G17        | GBB2/IO79PDB1    | J9         | GND              |  |

| F4         | IO224NDB3        | G18        | IO79NDB1         | J10        | VCC              |  |

| F5         | IO225NDB3        | G19        | IO82NPB1         | J11        | VCC              |  |

| F6         | VMV3             | G20        | IO85PDB1         | J12        | VCC              |  |

| F7         | IO11RSB0         | G21        | IO85NDB1         | J13        | VCC              |  |

| F8         | GAC0/IO04RSB0    | G22        | NC               | J14        | GND              |  |

| F9         | GAC1/IO05RSB0    | H1         | NC               | J15        | VCCIB1           |  |

| F10        | IO25RSB0         | H2         | NC               | J16        | IO83NPB1         |  |

| F11        | IO36RSB0         | H3         | VCC              | J17        | IO86NPB1         |  |

| F12        | IO42RSB0         | H4         | IO217PDB3        | J18        | IO90PPB1         |  |

| F13        | IO49RSB0         | H5         | IO218PDB3        | J19        | IO87NDB1         |  |

| F14        | IO56RSB0         | H6         | IO221NDB3        | J20        | NC               |  |

| F15        | GBC0/IO72RSB0    | H7         | IO221PDB3        | J21        | IO89PDB1         |  |

| F16        | IO62RSB0         | H8         | VMV0             | J22        | IO89NDB1         |  |

| F17        | VMV0             | H9         | VCCIB0           | K1         | IO211PDB3        |  |

| F18        | IO78NDB1         | H10        | VCCIB0           | K2         | IO211NDB3        |  |

| F19        | IO81NDB1         | H11        | IO38RSB0         | K3         | NC               |  |

| F20        | IO82PPB1         | H12        | IO47RSB0         | K4         | IO210PPB3        |  |

| F21        | NC               | H13        | VCCIB0           | K5         | IO213NDB3        |  |

| F22        | IO84NDB1         | H14        | VCCIB0           | K6         | IO213PDB3        |  |

| G1         | IO214NDB3        | H15        | VMV1             | K7         | GFC1/IO209PPB3   |  |

| G2         | IO214PDB3        | H16        | GBC2/IO80PDB1    | K8         | VCCIB3           |  |

| G3         | NC               | H17        | IO83PPB1         | K9         | VCC              |  |

| G4         | IO222NDB3        | H18        | IO86PPB1         | K10        | GND              |  |

| G5         | IO222PDB3        | H19        | IO87PDB1         | K11        | GND              |  |

| G6         | GAC2/IO223PDB3   | H20        | VCC              | K12        | GND              |  |

| G7         | IO223NDB3        | H21        | NC               | K13        | GND              |  |

| G8         | GNDQ             | H22        | NC               | K14        | VCC              |  |

| G9         | IO23RSB0         | J1         | IO212NDB3        | K15        | VCCIB1           |  |

| G10        | IO29RSB0         | J2         | IO212PDB3        | K16        | GCC1/IO91PPB1    |  |

| G11        | IO33RSB0         | J3         | NC               | K17        | IO90NPB1         |  |

| G12        | IO46RSB0         | J4         | IO217NDB3        | K18        | IO88PDB1         |  |

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page       |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Revision 13<br>(January 2013)   | The "ProASIC3 Ordering Information" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43104).                                                                                                                                                                                                                                                                      | 1-IV       |

|                                 | Added a note to Table 2-2 • Recommended Operating Conditions 1 (SAR 43644): The programming temperature range supported is $T_{ambient} = 0^{\circ}C$ to 85°C.                                                                                                                                                                                                                                                                                                                                        | 2-2        |

|                                 | The note in Table 2-115 • ProASIC3 CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 42569).                                                                                                                                                                                                                                                                                                                       | 2-90       |

|                                 | Libero Integrated Design Environment (IDE) was changed to Libero System-on-<br>Chip (SoC) throughout the document (SAR 40284).<br>Live at Power-Up (LAPU) has been replaced with 'Instant On'.                                                                                                                                                                                                                                                                                                        | NA         |

| Revision 12<br>(September 2012) | The Security section was modified to clarify that Microsemi does not support read-back of programmed data.                                                                                                                                                                                                                                                                                                                                                                                            | 1-1        |

|                                 | Added a Note stating "VMV pins must be connected to the corresponding VCCI pins. See the "VMVx I/O Supply Voltage (quiet)" section on page 3-1 for further information" to Table 2-1 • Absolute Maximum Ratings and Table 2-2 • Recommended Operating Conditions 1 (SAR 38321).                                                                                                                                                                                                                       | 2-1<br>2-2 |

|                                 | Table 2-35 • Duration of Short Circuit Event Before Failure was revised to change the maximum temperature from 110°C to 100°C, with an example of six months instead of three months (SAR 37933).                                                                                                                                                                                                                                                                                                     | 2-31       |

|                                 | In Table 2-93 • Minimum and Maximum DC Input and Output Levels, VIL and VIH were revised so that the maximum is 3.6 V for all listed values of VCCI (SAR 28549).                                                                                                                                                                                                                                                                                                                                      | 2-68       |

|                                 | Figure 2-37 • FIFO Read and Figure 2-38 • FIFO Write are new (SAR 28371).                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-99       |

|                                 | The following sentence was removed from the "VMVx I/O Supply Voltage (quiet)" section in the "Pin Descriptions" chapter: "Within the package, the VMV plane is decoupled from the simultaneous switching noise originating from the output buffer VCCI domain" and replaced with "Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks" (SAR 38321). The datasheet mentions that "VMV pins must be connected to the corresponding VCCI pins" for an ESD enhancement. | 3-1        |

Datasheet Information

| Revision                    | Changes                                                                                                                                                                                                                                                                   | Page    |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Revision 11<br>(March 2012) | Note indicating that A3P015 is not recommended for new designs has been added. The "Devices Not Recommended For New Designs" section is new (SAR 36760).                                                                                                                  | I to IV |

|                             | The following sentence was removed from the Advanced Architecture section:<br>"In addition, extensive on-chip programming circuitry allows for rapid, single-<br>voltage (3.3 V) programming of IGLOO devices via an IEEE 1532 JTAG<br>interface" (SAR 34687).            | NA      |

|                             | The reference to guidelines for global spines and VersaTile rows, given in the "Global Clock Contribution—PCLOCK" section, was corrected to the "Spine Architecture" section of the Global Resources chapter in the <i>ProASIC3 FPGA Fabric User's Guide</i> (SAR 34734). | 2-12    |

|                             | Figure 2-4 • Input Buffer Timing Model and Delays (Example) has been modified for the DIN waveform; the Rise and Fall time label has been changed to tDIN (35430).                                                                                                        | 2-16    |

|                             | The AC Loading figures in the "Single-Ended I/O Characteristics" section were updated to match tables in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section (SAR 34883).                                                                 | 2-32    |

|                             | Added values for minimum pulse width and removed the FRMAX row from Table 2-107 through Table 2-114 in the "Global Tree Timing Characteristics" section. Use the software to determine the FRMAX for the device you are using (SARs 37279, 29269).                        | 2-85    |

Datasheet Information

| Revision             | Changes                                                                                                                                                                                                                                                                                                                     | Page             |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|

| v2.0<br>(April 2007) | In the "Packaging Tables", Ambient was deleted.                                                                                                                                                                                                                                                                             | ii               |  |  |

|                      | The timing characteristics tables were updated.                                                                                                                                                                                                                                                                             | N/A              |  |  |

|                      | The "PLL Macro" section was updated to add information on the VCO and PLL outputs during power-up.                                                                                                                                                                                                                          | 2-15             |  |  |

|                      | The "PLL Macro" section was updated to include power-up information.                                                                                                                                                                                                                                                        |                  |  |  |

|                      | Table 2-11 • ProASIC3 CCC/PLL Specification was updated.                                                                                                                                                                                                                                                                    | 2-29             |  |  |

|                      | Figure 2-19 • Peak-to-Peak Jitter Definition is new.                                                                                                                                                                                                                                                                        | 2-18             |  |  |

|                      | The "SRAM and FIFO" section was updated with operation and timing requirement information.                                                                                                                                                                                                                                  | 2-21             |  |  |

|                      | The "RESET" section was updated with read and write information.                                                                                                                                                                                                                                                            | 2-25             |  |  |

|                      | The "RESET" section was updated with read and write information.                                                                                                                                                                                                                                                            | 2-25             |  |  |

|                      | The "Introduction" in the "Advanced I/Os" section was updated to include information on input and output buffers being disabled.                                                                                                                                                                                            | 2-28             |  |  |

|                      | PCI-X 3.3 V was added to Table 2-11 • VCCI Voltages and Compatible Standards.                                                                                                                                                                                                                                               | 2-29             |  |  |

|                      | In the Table 2-15 • Levels of Hot-Swap Support, the ProASIC3 compliance descriptions were updated for levels 3 and 4.                                                                                                                                                                                                       | 2-34             |  |  |

|                      | Table 2-43 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3 Devices was updated.                                                                                                                                                                                                                             | 2-64             |  |  |

|                      | Notes 3, 4, and 5 were added to Table 2-17 $\cdot$ Comparison Table for 5 V–Compliant Receiver Scheme. 5 x 52.72 was changed to 52.7 and the Maximum current was updated from 4 x 52.7 to 5 x 52.7.                                                                                                                         | 2-40             |  |  |

|                      | The "VCCPLF PLL Supply Voltage" section was updated.                                                                                                                                                                                                                                                                        | 2-50             |  |  |

|                      | The "VPUMP Programming Supply Voltage" section was updated.                                                                                                                                                                                                                                                                 | 2-50             |  |  |

|                      | The "GL Globals" section was updated to include information about direct input into quadrant clocks.                                                                                                                                                                                                                        | 2-51             |  |  |

|                      | V <sub>JTAG</sub> was deleted from the "TCK Test Clock" section.                                                                                                                                                                                                                                                            | 2-51             |  |  |

|                      | In Table 2-22 • Recommended Tie-Off Values for the TCK and TRST Pins, TSK was changed to TCK in note 2. Note 3 was also updated.                                                                                                                                                                                            | 2-51             |  |  |

|                      | Ambient was deleted from Table 3-2 • Recommended Operating Conditions. VPUMP programming mode was changed from "3.0 to 3.6" to "3.15 to 3.45".                                                                                                                                                                              | 3-2              |  |  |

|                      | Note 3 is new in Table 3-4 • Overshoot and Undershoot Limits (as measured on quiet I/Os)1.                                                                                                                                                                                                                                  | 3-2              |  |  |

|                      | In EQ 3-2, 150 was changed to 110 and the result changed from 3.9 to 1.951.                                                                                                                                                                                                                                                 | 3-5              |  |  |

|                      | Table 3-6 • Temperature and Voltage Derating Factors for Timing Delays was updated.                                                                                                                                                                                                                                         | 3-6              |  |  |

|                      | Table 3-5       •       Package Thermal Resistivities was updated.                                                                                                                                                                                                                                                          | 3-5              |  |  |

|                      | Table 3-14 • Summary of Maximum and Minimum DC Input and Output Levels<br>Applicable to Commercial and Industrial Conditions—Software Default Settings<br>(Advanced) and Table 3-17 • Summary of Maximum and Minimum DC Input<br>Levels Applicable to Commercial and Industrial Conditions (Standard Plus) were<br>updated. | 3-17 to 3-<br>17 |  |  |