Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                   |

|--------------------------------|--------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 147456                                                                   |

| Number of I/O                  | 97                                                                       |

| Number of Gates                | 1000000                                                                  |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 144-LBGA                                                                 |

| Supplier Device Package        | 144-FPBGA (13x13)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p1000-2fg144 |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 2-43 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 7.20            | 0.04             | 1.00            | 0.43              | 7.34            | 6.29            | 2.27            | 2.34            | 9.57             | 8.52             | ns    |

|                   | -1             | 0.56              | 6.13            | 0.04             | 0.85            | 0.36              | 6.24            | 5.35            | 1.93            | 1.99            | 8.14             | 7.25             | ns    |

|                   | -2             | 0.49              | 5.38            | 0.03             | 0.75            | 0.32              | 5.48            | 4.69            | 1.70            | 1.75            | 7.15             | 6.36             | ns    |

| 4 mA              | Std.           | 0.66              | 7.20            | 0.04             | 1.00            | 0.43              | 7.34            | 6.29            | 2.27            | 2.34            | 9.57             | 8.52             | ns    |

|                   | -1             | 0.56              | 6.13            | 0.04             | 0.85            | 0.36              | 6.24            | 5.35            | 1.93            | 1.99            | 8.14             | 7.25             | ns    |

|                   | -2             | 0.49              | 5.38            | 0.03             | 0.75            | 0.32              | 5.48            | 4.69            | 1.70            | 1.75            | 7.15             | 6.36             | ns    |

| 6 mA              | Std.           | 0.66              | 4.50            | 0.04             | 1.00            | 0.43              | 4.58            | 3.82            | 2.58            | 2.88            | 6.82             | 6.05             | ns    |

|                   | -1             | 0.56              | 3.83            | 0.04             | 0.85            | 0.36              | 3.90            | 3.25            | 2.19            | 2.45            | 5.80             | 5.15             | ns    |

|                   | -2             | 0.49              | 3.36            | 0.03             | 0.75            | 0.32              | 3.42            | 2.85            | 1.92            | 2.15            | 5.09             | 4.52             | ns    |

| 8 mA              | Std.           | 0.66              | 4.50            | 0.04             | 1.00            | 0.43              | 4.58            | 3.82            | 2.58            | 2.88            | 6.82             | 6.05             | ns    |

|                   | -1             | 0.56              | 3.83            | 0.04             | 0.85            | 0.36              | 3.90            | 3.25            | 2.19            | 2.45            | 5.80             | 5.15             | ns    |

|                   | -2             | 0.49              | 3.36            | 0.03             | 0.75            | 0.32              | 3.42            | 2.85            | 1.92            | 2.15            | 5.09             | 4.52             | ns    |

| 12 mA             | Std.           | 0.66              | 3.16            | 0.04             | 1.00            | 0.43              | 3.22            | 2.58            | 2.79            | 3.22            | 5.45             | 4.82             | ns    |

|                   | -1             | 0.56              | 2.69            | 0.04             | 0.85            | 0.36              | 2.74            | 2.20            | 2.37            | 2.74            | 4.64             | 4.10             | ns    |

|                   | -2             | 0.49              | 2.36            | 0.03             | 0.75            | 0.32              | 2.40            | 1.93            | 2.08            | 2.41            | 4.07             | 3.60             | ns    |

| 16 mA             | Std.           | 0.66              | 3.16            | 0.04             | 1.00            | 0.43              | 3.22            | 2.58            | 2.79            | 3.22            | 5.45             | 4.82             | ns    |

|                   | -1             | 0.56              | 2.69            | 0.04             | 0.85            | 0.36              | 2.74            | 2.20            | 2.37            | 2.74            | 4.64             | 4.10             | ns    |

|                   | -2             | 0.49              | 2.36            | 0.03             | 0.75            | 0.32              | 2.40            | 1.93            | 2.08            | 2.41            | 4.07             | 3.60             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-58 • Minimum and Maximum DC Input and Output Levels Applicable to Standard I/O Banks

| 2.5 V LVCMOS   | v         | ΊL         | v         | IH        | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|----------------|-----------|------------|-----------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive Strength | Min.<br>V | Max.,<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA           | -0.3      | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 2   | 2   | 16                      | 18                      | 10               | 10               |

| 4 mA           | -0.3      | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 4   | 4   | 16                      | 18                      | 10               | 10               |

| 6 mA           | -0.3      | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 6   | 6   | 32                      | 37                      | 10               | 10               |

| 8 mA           | -0.3      | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 8   | 8   | 32                      | 37                      | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

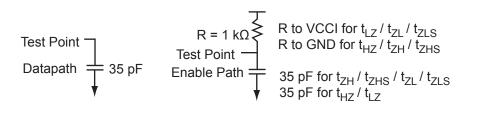

# Figure 2-8 • AC Loading

## Table 2-59 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 2.5            | 1.2                  | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-22 on page 2-22 for a complete table of trip points.

| Table 2-62 •      | 2.5 V LV<br>Commer<br>Applicat | cial-Cas          | e Cond          | itions:          |                 |                   | st-Case         | • VCC =         | = 1.425         | V, Wor          | st-Case          | VCCI = 2         | 2.3 V |

|-------------------|--------------------------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade                 | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 4 mA              | Std.                           | 0.66              | 8.28            | 0.04             | 1.30            | 0.43              | 7.41            | 8.28            | 2.25            | 2.07            | 9.64             | 10.51            | ns    |

|                   | -1                             | 0.56              | 7.04            | 0.04             | 1.10            | 0.36              | 6.30            | 7.04            | 1.92            | 1.76            | 8.20             | 8.94             | ns    |

|                   | -2                             | 0.49              | 6.18            | 0.03             | 0.97            | 0.32              | 5.53            | 6.18            | 1.68            | 1.55            | 7.20             | 7.85             | ns    |

| 6 mA              | Std.                           | 0.66              | 4.85            | 0.04             | 1.30            | 0.43              | 4.65            | 4.85            | 2.59            | 2.71            | 6.88             | 7.09             | ns    |

|                   | -1                             | 0.56              | 4.13            | 0.04             | 1.10            | 0.36              | 3.95            | 4.13            | 2.20            | 2.31            | 5.85             | 6.03             | ns    |

|                   | -2                             | 0.49              | 3.62            | 0.03             | 0.97            | 0.32              | 3.47            | 3.62            | 1.93            | 2.02            | 5.14             | 5.29             | ns    |

| 8 mA              | Std.                           | 0.66              | 4.85            | 0.04             | 1.30            | 0.43              | 4.65            | 4.85            | 2.59            | 2.71            | 6.88             | 7.09             | ns    |

|                   | -1                             | 0.56              | 4.13            | 0.04             | 1.10            | 0.36              | 3.95            | 4.13            | 2.20            | 2.31            | 5.85             | 6.03             | ns    |

|                   | -2                             | 0.49              | 3.62            | 0.03             | 0.97            | 0.32              | 3.47            | 3.62            | 1.93            | 2.02            | 5.14             | 5.29             | ns    |

| 12 mA             | Std.                           | 0.66              | 3.21            | 0.04             | 1.30            | 0.43              | 3.27            | 3.14            | 2.82            | 3.11            | 5.50             | 5.38             | ns    |

| F                 | -1                             | 0.56              | 2.73            | 0.04             | 1.10            | 0.36              | 2.78            | 2.67            | 2.40            | 2.65            | 4.68             | 4.57             | ns    |

|                   | -2                             | 0.49              | 2.39            | 0.03             | 0.97            | 0.32              | 2.44            | 2.35            | 2.11            | 2.32            | 4.11             | 4.02             | ns    |

Microsomi

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## Table 2-63 • 2.5 V LVCMOS Low Slew Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Standard Plus I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 10.84           | 0.04             | 1.30            | 0.43              | 10.64           | 10.84           | 2.26            | 1.99            | 12.87            | 13.08            | ns    |

|                   | –1             | 0.56              | 9.22            | 0.04             | 1.10            | 0.36              | 9.05            | 9.22            | 1.92            | 1.69            | 10.95            | 11.12            | ns    |

|                   | -2             | 0.49              | 8.10            | 0.03             | 0.97            | 0.32              | 7.94            | 8.10            | 1.68            | 1.49            | 9.61             | 9.77             | ns    |

| 6 mA              | Std.           | 0.66              | 7.37            | 0.04             | 1.30            | 0.43              | 7.50            | 7.36            | 2.59            | 2.61            | 9.74             | 9.60             | ns    |

|                   | –1             | 0.56              | 6.27            | 0.04             | 1.10            | 0.36              | 6.38            | 6.26            | 2.20            | 2.22            | 8.29             | 8.16             | ns    |

|                   | -2             | 0.49              | 5.50            | 0.03             | 0.97            | 0.32              | 5.60            | 5.50            | 1.93            | 1.95            | 7.27             | 7.17             | ns    |

| 8 mA              | Std.           | 0.66              | 7.37            | 0.04             | 1.30            | 0.43              | 7.50            | 7.36            | 2.59            | 2.61            | 9.74             | 9.60             | ns    |

|                   | -1             | 0.56              | 6.27            | 0.04             | 1.10            | 0.36              | 6.38            | 6.26            | 2.20            | 2.22            | 8.29             | 8.16             | ns    |

|                   | -2             | 0.49              | 5.50            | 0.03             | 0.97            | 0.32              | 5.60            | 5.50            | 1.93            | 1.95            | 7.27             | 7.17             | ns    |

| 12 mA             | Std.           | 0.66              | 5.63            | 0.04             | 1.30            | 0.43              | 5.73            | 5.51            | 2.83            | 3.01            | 7.97             | 7.74             | ns    |

|                   | –1             | 0.56              | 4.79            | 0.04             | 1.10            | 0.36              | 4.88            | 4.68            | 2.41            | 2.56            | 6.78             | 6.59             | ns    |

|                   | -2             | 0.49              | 4.20            | 0.03             | 0.97            | 0.32              | 4.28            | 4.11            | 2.11            | 2.25            | 5.95             | 5.78             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

|                   | Ah        |             | anuaru Fius I |           | .5          |             |     |    |                         |                         |                 |                  |

|-------------------|-----------|-------------|---------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| 1.5 V<br>LVCMOS   |           | VIL         | VIH           |           | VOL         | VOH         | IOL | юн | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V     | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI   | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 16                      | 13                      | 10              | 10               |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI   | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 4   | 4  | 33                      | 25                      | 10              | 10               |

| Mataai            |           |             |               |           |             |             |     |    |                         |                         |                 |                  |

### Table 2-77 • Minimum and Maximum DC Input and Output Levels Applicable to Standard Plus I/O Banks

Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

#### Table 2-78 • Minimum and Maximum DC Input and Output Levels Applicable to Standard I/O Banks

| 1.5 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | юн | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 13                      | 16                      | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

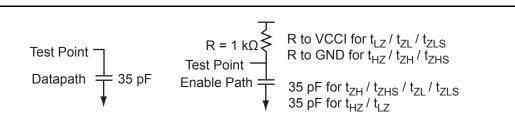

#### Figure 2-10 • AC Loading

### Table 2-79 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.5            | 0.75                 | 35                     |

Note: \*Measuring point =  $V_{trip}$ . See Table 2-22 on page 2-22 for a complete table of trip points.

# 3.3 V PCI, 3.3 V PCI-X

Peripheral Component Interface for 3.3 V standard specifies support for 33 MHz and 66 MHz PCI Bus applications.

| 3.3 V PCI/PCI-X       | V              | ΊL        | V         | IH        | VOL        | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL | IIH |

|-----------------------|----------------|-----------|-----------|-----------|------------|-----------|-----|----|-------------------------|-------------------------|-----|-----|

| Drive Strength        | Min.<br>V      | Max.<br>V | Min.<br>V | Max.<br>V | Max,.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| Per PCI specification | Per PCI curves |           |           |           |            |           |     | 10 | 10                      |                         |     |     |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

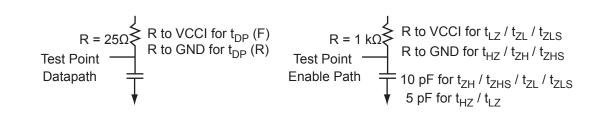

AC loadings are defined per the PCI/PCI-X specifications for the datapath; Microsemi loadings for enable path characterization are described in Figure 2-11.

# Figure 2-11 • AC Loading

AC loadings are defined per PCI/PCI-X specifications for the datapath; Microsemi loading for tristate is described in Table 2-87.

## Table 2-87 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V)                | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------------------|------------------------|

| 0             | 3.3            | 0.285 * VCCI for t <sub>DP(R)</sub> | 10                     |

|               |                | 0.615 * VCCI for t <sub>DP(F)</sub> |                        |

Note: \*Measuring point = V<sub>trip.</sub> See Table 2-22 on page 2-22 for a complete table of trip points.

# B-LVDS/M-LVDS

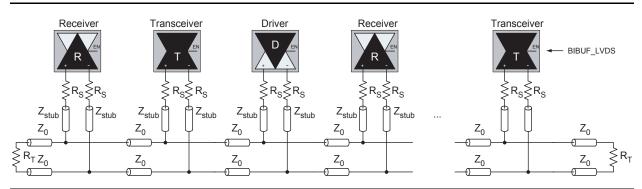

Bus LVDS (B-LVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to highperformance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The drivers require series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus since the driver can be located anywhere on the bus. These configurations can be implemented using the TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-13. The input and output buffer delays are available in the LVDS section in Table 2-92.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case Industrial operating conditions, at the farthest receiver:  $R_S = 60 \Omega$  and  $R_T = 70 \Omega$ , given  $Z_0 = 50 \Omega$  (2") and  $Z_{stub} = 50 \Omega$  (~1.5").

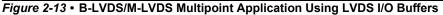

# LVPECL

Low-Voltage Positive Emitter-Coupled Logic (LVPECL) is another differential I/O standard. It requires that one data bit be carried through two signal lines. Like LVDS, two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-14. The building blocks of the LVPECL transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVDS implementation because the output standard specifications are different.

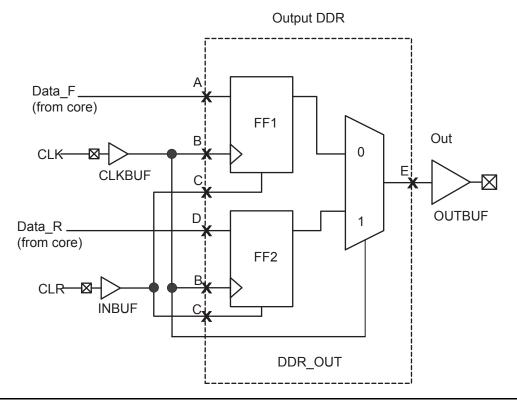

# **Output DDR Module**

# Figure 2-22 • Output DDR Timing Model

# Table 2-103 • Parameter Definitions

| Parameter Name          | Parameter Definition      | Measuring Nodes (from, to) |

|-------------------------|---------------------------|----------------------------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out              | B, E                       |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out | C, E                       |

| t <sub>DDROREMCLR</sub> | Clear Removal             | С, В                       |

| t <sub>DDRORECCLR</sub> | Clear Recovery            | С, В                       |

| t <sub>DDROSUD1</sub>   | Data Setup Data_F         | А, В                       |

| t <sub>DDROSUD2</sub>   | Data Setup Data_R         | D, B                       |

| t <sub>DDROHD1</sub>    | Data Hold Data_F          | А, В                       |

| t <sub>DDROHD2</sub>    | Data Hold Data_R          | D, B                       |

# Table 2-109 • A3P060 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -                 | -2 -1             |                   | Std.              |                   |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.71              | 0.93              | 0.81              | 1.05              | 0.95              | 1.24              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.70              | 0.96              | 0.80              | 1.09              | 0.94              | 1.28              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Microse

Power Matters.

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# Table 2-110 • A3P125 Global Resource

```

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

```

|                      |                                           | -                 | -2 -1             |                   | Std.              |                   |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.77              | 0.99              | 0.87              | 1.12              | 1.03              | 1.32              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.76              | 1.02              | 0.87              | 1.16              | 1.02              | 1.37              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-111 • A3P250 Global Resource

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -                 | -2 -1             |                   | Std.              |                   |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.80              | 1.01              | 0.91              | 1.15              | 1.07              | 1.36              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.78              | 1.04              | 0.89              | 1.18              | 1.04              | 1.39              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## Table 2-112 • A3P400 Global Resource

```

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

```

|                      |                                           | -                 | -2 -1             |                   | Std.              |                   |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.87              | 1.09              | 0.99              | 1.24              | 1.17              | 1.46              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.86              | 1.11              | 0.98              | 1.27              | 1.15              | 1.49              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

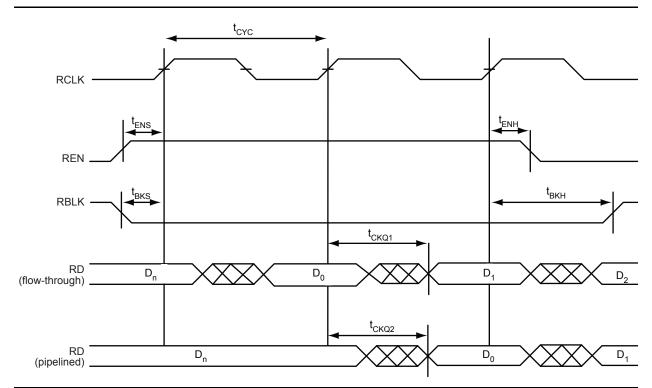

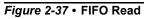

# Timing Waveforms

# Table 2-121 • A3P250 FIFO 1k×4 Worst Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

| Parameter            | Description                                       | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 4.05 | 4.61 | 5.42 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.22 | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.36 | 2.68 | 3.15 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.89 | 1.02 | 1.20 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96 | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86 | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05 | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93 | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.13 | 6.98 | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.92 | 1.05 | 1.23 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272  | 231  | MHz   |

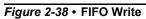

# **QN68 – Bottom View**

# Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

Package Pin Assignments

| QN132      |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | A3P060 Function |  |  |  |

| C17        | IO57RSB1        |  |  |  |

| C18        | NC              |  |  |  |

| C19        | тск             |  |  |  |

| C20        | VMV1            |  |  |  |

| C21        | VPUMP           |  |  |  |

| C22        | VJTAG           |  |  |  |

| C23        | VCCIB0          |  |  |  |

| C24        | NC              |  |  |  |

| C25        | NC              |  |  |  |

| C26        | GCA1/IO42RSB0   |  |  |  |

| C27        | GCC0/IO39RSB0   |  |  |  |

| C28        | VCCIB0          |  |  |  |

| C29        | IO29RSB0        |  |  |  |

| C30        | GNDQ            |  |  |  |

| C31        | GBA1/IO27RSB0   |  |  |  |

| C32        | GBB0/IO24RSB0   |  |  |  |

| C33        | VCC             |  |  |  |

| C34        | IO19RSB0        |  |  |  |

| C35        | IO16RSB0        |  |  |  |

| C36        | IO13RSB0        |  |  |  |

| C37        | GAC1/IO10RSB0   |  |  |  |

| C38        | NC              |  |  |  |

| C39        | GAA0/IO05RSB0   |  |  |  |

| C40        | VMV0            |  |  |  |

| D1         | GND             |  |  |  |

| D2         | GND             |  |  |  |

| D3         | GND             |  |  |  |

| D4         | GND             |  |  |  |

Package Pin Assignments

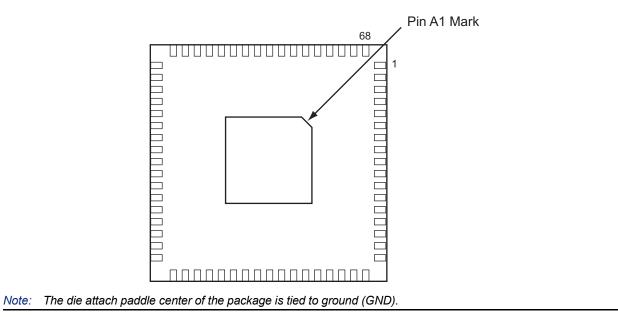

# PQ208 – Top View

# Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

| · · · · ·  | PQ208           |            | PQ208           | PQ208      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number | A3P250 Function |

| 1          | GND             | 37         | IO104PDB3       | 73         | IO83RSB2        |

| 2          | GAA2/IO118UDB3  | 38         | IO104NDB3       | 74         | IO82RSB2        |

| 3          | IO118VDB3       | 39         | IO103PSB3       | 75         | IO81RSB2        |

| 4          | GAB2/IO117UDB3  | 40         | VCCIB3          | 76         | IO80RSB2        |

| 5          | IO117VDB3       | 41         | GND             | 77         | IO79RSB2        |

| 6          | GAC2/IO116UDB3  | 42         | IO101PDB3       | 78         | IO78RSB2        |

| 7          | IO116VDB3       | 43         | IO101NDB3       | 79         | IO77RSB2        |

| 8          | IO115UDB3       | 44         | GEC1/IO100PDB3  | 80         | IO76RSB2        |

| 9          | IO115VDB3       | 45         | GEC0/IO100NDB3  | 81         | GND             |

| 10         | IO114UDB3       | 46         | GEB1/IO99PDB3   | 82         | IO75RSB2        |

| 11         | IO114VDB3       | 47         | GEB0/IO99NDB3   | 83         | IO74RSB2        |

| 12         | IO113PDB3       | 48         | GEA1/IO98PDB3   | 84         | IO73RSB2        |

| 13         | IO113NDB3       | 49         | GEA0/IO98NDB3   | 85         | IO72RSB2        |

| 14         | IO112PDB3       | 50         | VMV3            | 86         | IO71RSB2        |

| 15         | IO112NDB3       | 51         | GNDQ            | 87         | IO70RSB2        |

| 16         | VCC             | 52         | GND             | 88         | VCC             |

| 17         | GND             | 53         | NC              | 89         | VCCIB2          |

| 18         | VCCIB3          | 54         | NC              | 90         | IO69RSB2        |

| 19         | IO111PDB3       | 55         | GEA2/IO97RSB2   | 91         | IO68RSB2        |

| 20         | IO111NDB3       | 56         | GEB2/IO96RSB2   | 92         | IO67RSB2        |

| 21         | GFC1/IO110PDB3  | 57         | GEC2/IO95RSB2   | 93         | IO66RSB2        |

| 22         | GFC0/IO110NDB3  | 58         | IO94RSB2        | 94         | IO65RSB2        |

| 23         | GFB1/IO109PDB3  | 59         | IO93RSB2        | 95         | IO64RSB2        |

| 24         | GFB0/IO109NDB3  | 60         | IO92RSB2        | 96         | GDC2/IO63RSB2   |

| 25         | VCOMPLF         | 61         | IO91RSB2        | 97         | GND             |

| 26         | GFA0/IO108NPB3  | 62         | VCCIB2          | 98         | GDB2/IO62RSB2   |

| 27         | VCCPLF          | 63         | IO90RSB2        | 99         | GDA2/IO61RSB2   |

| 28         | GFA1/IO108PPB3  | 64         | IO89RSB2        | 100        | GNDQ            |

| 29         | GND             | 65         | GND             | 101        | ТСК             |

| 30         | GFA2/IO107PDB3  | 66         | IO88RSB2        | 102        | TDI             |

| 31         | IO107NDB3       | 67         | IO87RSB2        | 103        | TMS             |

| 32         | GFB2/IO106PDB3  | 68         | IO86RSB2        | 104        | VMV2            |

| 33         | IO106NDB3       | 69         | IO85RSB2        | 105        | GND             |

| 34         | GFC2/IO105PDB3  | 70         | IO84RSB2        | 106        | VPUMP           |

| 35         | IO105NDB3       | 71         | VCC             | 107        | NC              |

| 36         | NC              | 72         | VCCIB2          | 108        | TDO             |

| F          | G144            |

|------------|-----------------|

| Pin Number | A3P250 Function |

| K1         | GEB0/IO99NDB3   |

| K2         | GEA1/IO98PDB3   |

| K3         | GEA0/IO98NDB3   |

| K4         | GEA2/IO97RSB2   |

| K5         | IO90RSB2        |

| K6         | IO84RSB2        |

| K7         | GND             |

| K8         | IO66RSB2        |

| K9         | GDC2/IO63RSB2   |

| K10        | GND             |

| K11        | GDA0/IO60VDB1   |

| K12        | GDB0/IO59VDB1   |

| L1         | GND             |

| L2         | VMV3            |

| L3         | GEB2/IO96RSB2   |

| L4         | IO91RSB2        |

| L5         | VCCIB2          |

| L6         | IO82RSB2        |

| L7         | IO80RSB2        |

| L8         | IO72RSB2        |

| L9         | TMS             |

| L10        | VJTAG           |

| L11        | VMV2            |

| L12        | TRST            |

| M1         | GNDQ            |

| M2         | GEC2/IO95RSB2   |

| M3         | IO92RSB2        |

| M4         | IO89RSB2        |

| M5         | IO87RSB2        |

| M6         | IO85RSB2        |

| M7         | IO78RSB2        |

| M8         | IO76RSB2        |

| M9         | TDI             |

| M10        | VCCIB2          |

| M11        | VPUMP           |

| M12        | GNDQ            |

Datasheet Information

| Revision                   | Changes                                                                                                                                                                                                                                                       | Page                |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Revision 10<br>(continued) | "TBD" for 3.3 V LVCMOS Wide Range in Table 2-28 • I/O Output Buffer Maximum Resistances1 through Table 2-30 • I/O Output Buffer Maximum Resistances1 was replaced by "Same as regular 3.3 V" (SAR 33852).                                                     | 2-26 to 2-28        |

|                            | The equations in the notes for Table 2-31 • I/O Weak Pull-Up/Pull-Down Resistances were corrected (SAR 32470).                                                                                                                                                | 2-28                |

|                            | "TBD" for 3.3 V LVCMOS Wide Range in Table 2-32 • I/O Short Currents IOSH/IOSL through Table 2-34 • I/O Short Currents IOSH/IOSL was replaced by "Same as regular 3.3 V LVCMOS" (SAR 33852).                                                                  | 2-29 to 2-31        |

|                            | In the "3.3 V LVCMOS Wide Range" section, values were added to Table 2-47 through Table 2-49 for IOSL and IOSH, replacing "TBD" (SAR 33852).                                                                                                                  | 2-39 to 2-40        |

|                            | The following sentence was deleted from the "2.5 V LVCMOS" section (SAR 24916): "It uses a 5 V-tolerant input buffer and push-pull output buffer."                                                                                                            | 2-47                |

|                            | The table notes were revised for Table 2-90 • LVDS Minimum and Maximum DC Input and Output Levels (SAR 33859).                                                                                                                                                | 2-66                |

|                            | Values were added for $F_{DDRIMAX}$ and $F_{DDOMAX}$ in Table 2-102 • Input DDR Propagation Delays and Table 2-104 • Output DDR Propagation Delays (SAR 23919).                                                                                               | 2-78, 2-80          |

|                            | Table 2-115 • ProASIC3 CCC/PLL Specification was updated. A note was added to indicate that when the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available (SAR 25705).        | 2-90                |

|                            | The following figures were deleted (SAR 29991). Reference was made to a new application note, <i>Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs</i> , which covers these cases in detail (SAR 21770).                   | 2-92,               |

|                            | Figure 2-34 • Write Access after Write onto Same Address<br>Figure 2-35 • Read Access after Write onto Same Address<br>Figure 2-35 • Read Access after Write onto Same Address                                                                                | 2-94,<br>2-99 2-102 |

|                            | The port names in the SRAM "Timing Waveforms", SRAM "Timing Characteristics" tables, Figure 2-39 • FIFO Reset, and the FIFO "Timing Characteristics" tables were revised to ensure consistency with the software names (SARs 29991, 30510).                   |                     |

|                            | The "Pin Descriptions" chapter has been added (SAR 21642).                                                                                                                                                                                                    | 3-1                 |

|                            | Package names used in the "Package Pin Assignments" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                                                                                                          | 4-1                 |

| July 2010                  | The versioning system for datasheets has been changed. Datasheets are assigned a revision number that increments each time the datasheet is revised. The "ProASIC3 Device Status" table on page IV indicates the status for each device in the device family. | N/A                 |

| Revision                                    | Changes                                                                                                                                                                                                                                      | Page   |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Revision 9 (Oct 2009)<br>Product Brief v1.3 | The CS121 package was added to table under "Features and Benefits" section, the "I/Os Per Package 1" table, Table 1 • ProASIC3 FPGAs Package Sizes Dimensions, "ProASIC3 Ordering Information", and the "Temperature Grade Offerings" table. | I – IV |

|                                             | "ProASIC3 Ordering Information" was revised to include the fact that some RoHS compliant packages are halogen-free.                                                                                                                          | IV     |

| Packaging v1.5                              | The "CS121 – Bottom View" figure and pin table for A3P060 are new.                                                                                                                                                                           | 4-15   |

| Revision 8 (Aug 2009)<br>Product Brief v1.2 | All references to M7 devices (CoreMP7) and speed grade –F were removed from this document.                                                                                                                                                   | N/A    |

|                                             | Table 1-1 I/O Standards supported is new.                                                                                                                                                                                                    | 1-7    |

|                                             | The I/Os with Advanced I/O Standards section was revised to add definitions of hot-swap and cold-sparing.                                                                                                                                    | 1-7    |

| DC and Switching<br>Characteristics v1.4    | $3.3~\rm V$ LVCMOS and $1.2~\rm V$ LVCMOS Wide Range support was added to the datasheet. This affects all tables that contained $3.3~\rm V$ LVCMOS and $1.2~\rm V$ LVCMOS data.                                                              | N/A    |

|                                             | $\rm I_{\rm IL}$ and $\rm I_{\rm IH}$ input leakage current information was added to all "Minimum and Maximum DC Input and Output Levels" tables.                                                                                            | N/A    |

|                                             | -F was removed from the datasheet. The speed grade is no longer supported.                                                                                                                                                                   | N/A    |

|                                             | The notes in Table 2-2 • Recommended Operating Conditions 1 were updated.                                                                                                                                                                    | 2-2    |

|                                             | Table 2-4 • Overshoot and Undershoot Limits 1 was updated.                                                                                                                                                                                   | 2-3    |

|                                             | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays was updated.                                                                                                                                                          | 2-6    |

|                                             | In Table 2-116 • RAM4K9, the following specifications were removed:<br>t <sub>WRO</sub><br>t <sub>CCKH</sub>                                                                                                                                 | 2-96   |

|                                             | In Table 2-117 • RAM512X18, the following specifications were removed:<br>t <sub>WRO</sub><br>t <sub>CCKH</sub>                                                                                                                              | 2-97   |

|                                             | In the title of Table 2-74 • 1.8 V LVCMOS High Slew, VCCI had a typo. It was changed from 3.0 V to 1.7 V.                                                                                                                                    | 2-58   |

| Revision 7 (Feb 2009)<br>Product Brief v1.1 | The "Advanced I/O" section was revised to add a bullet regarding wide range power supply voltage support.                                                                                                                                    | I      |

|                                             | The table under "Features and Benefits" section, was updated to include a value for typical equivalent macrocells for A3P250.                                                                                                                | I      |

|                                             | The QN48 package was added to the following tables: the table under "Features<br>and Benefits" section, "I/Os Per Package 1" "ProASIC3 FPGAs Package Sizes<br>Dimensions", and "Temperature Grade Offerings".                                | N/A    |

|                                             | The number of singled-ended I/Os for QN68 was added to the "I/Os Per Package 1" table.                                                                                                                                                       |        |

|                                             | The Wide Range I/O Support section is new.                                                                                                                                                                                                   | 1-7    |

| Revision 6 (Dec 2008)                       | The "QN48 – Bottom View" section is new.                                                                                                                                                                                                     | 4-1    |

| Packaging v1.4                              | The "QN68" pin table for A3P030 is new.                                                                                                                                                                                                      | 4-5    |

Datasheet Information

| Revision     | Changes                                                                                                                                                                                              | Page |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Advance v0.6 | The "RESET" section was updated.                                                                                                                                                                     | 2-25 |

| (continued)  | The "WCLK and RCLK" section was updated.                                                                                                                                                             | 2-25 |

|              | The "RESET" section was updated.                                                                                                                                                                     | 2-25 |

|              | The "RESET" section was updated.                                                                                                                                                                     | 2-27 |

|              | The "Introduction" of the "Advanced I/Os" section was updated.                                                                                                                                       | 2-28 |

|              | The "I/O Banks" section is new. This section explains the following types of I/Os:<br>Advanced<br>Standard+<br>Standard<br>Table 2-12 • Automotive ProASIC3 Bank Types Definition and Differences is | 2-29 |

|              | new. This table describes the standards listed above.                                                                                                                                                | 0.00 |

|              | PCI-X 3.3 V was added to the Compatible Standards for 3.3 V in Table 2-<br>11 • VCCI Voltages and Compatible Standards                                                                               | 2-29 |

|              | Table 2-13 • ProASIC3 I/O Features was updated.                                                                                                                                                      | 2-30 |

|              | The "Double Data Rate (DDR) Support" section was updated to include information concerning implementation of the feature.                                                                            | 2-32 |

|              | The "Electrostatic Discharge (ESD) Protection" section was updated to include testing information.                                                                                                   | 2-35 |

|              | Level 3 and 4 descriptions were updated in Table 2-43 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3 Devices.                                                                       | 2-64 |

|              | The notes in Table 2-43 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3 Devices were updated.                                                                                        | 2-64 |

|              | The "Simultaneous Switching Outputs (SSOs) and Printed Circuit Board Layout" section is new.                                                                                                         | 2-41 |

|              | A footnote was added to Table 2-14 • Maximum I/O Frequency for Single-Ended<br>and Differential I/Os in All Banks in Automotive ProASIC3 Devices (maximum<br>drive strength and high slew selected). | 2-30 |

|              | Table 2-18 • Automotive ProASIC3 I/O Attributes vs. I/O Standard Applications                                                                                                                        | 2-45 |

|              | Table 2-50 • ProASIC3 Output Drive (OUT_DRIVE) for Standard I/O Bank Type (A3P030 device)                                                                                                            | 2-83 |

|              | Table 2-51 • ProASIC3 Output Drive for Standard+ I/O Bank Type was updated.                                                                                                                          | 2-84 |

|              | Table 2-54 • ProASIC3 Output Drive for Advanced I/O Bank Type was updated.                                                                                                                           | 2-84 |

|              | The "x" was updated in the "User I/O Naming Convention" section.                                                                                                                                     | 2-48 |

|              | The "VCC Core Supply Voltage" pin description was updated.                                                                                                                                           | 2-50 |

|              | The "VMVx I/O Supply Voltage (quiet)" pin description was updated to include information concerning leaving the pin unconnected.                                                                     | 2-50 |

|              | The "VJTAG JTAG Supply Voltage" pin description was updated.                                                                                                                                         | 2-50 |

|              | The "VPUMP Programming Supply Voltage" pin description was updated to include information on what happens when the pin is tied to ground.                                                            | 2-50 |

|              | The "I/O User Input/Output" pin description was updated to include information on what happens when the pin is unused.                                                                               | 2-50 |

|              | The "JTAG Pins" section was updated to include information on what happens when the pin is unused.                                                                                                   | 2-51 |

Datasheet Information

| Revision     | Changes                                                                                                                       | Page             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|

| Advance v0.3 | The "PLL Macro" section was updated. EXTFB information was removed from this section.                                         | 2-15             |

|              | The CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub> was updated in Table 2-<br>11 • ProASIC3 CCC/PLL Specification | 2-29             |

|              | EXTFB was removed from Figure 2-27 • CCC/PLL Macro.                                                                           | 2-28             |

|              | Table 2-13 • ProASIC3 I/O Features was updated.                                                                               | 2-30             |

|              | The "Hot-Swap Support" section was updated.                                                                                   | 2-33             |

|              | The "Cold-Sparing Support" section was updated.                                                                               | 2-34             |

|              | "Electrostatic Discharge (ESD) Protection" section was updated.                                                               | 2-35             |

|              | The LVPECL specification in Table 2-43 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3 Devices was updated.   | 2-64             |

|              | In the Bank 1 area of Figure 2-72, VMV2 was changed to VMV1 and VCCIB2 was changed to VCC_IB1.                                | 2-97             |

|              | The VJTAG and I/O pin descriptions were updated in the "Pin Descriptions" section.                                            | 2-50             |

|              | The "JTAG Pins" section was updated.                                                                                          | 2-51             |

|              | "128-Bit AES Decryption" section was updated to include M7 device information.                                                | 2-53             |

|              | Table 3-6 was updated.                                                                                                        | 3-6              |

|              | Table 3-7 was updated.                                                                                                        | 3-6              |

|              | In Table 3-11, PAC4 was updated.                                                                                              | 3-93-8           |

|              | Table 3-20 was updated.                                                                                                       | 3-20             |

|              | The note in Table 3-32 was updated.                                                                                           | 3-27             |

|              | All Timing Characteristics tables were updated from LVTTL to Register Delays                                                  | 3-31 to 3-<br>73 |

|              | The Timing Characteristics for RAM4K9, RAM512X18, and FIFO were updated.                                                      | 3-85 to<br>3-90  |

|              | F <sub>TCKMAX</sub> was updated in Table 3-110.                                                                               | 3-97             |

| Advance v0.2 | Figure 2-11 was updated.                                                                                                      | 2-9              |

|              | The "Clock Resources (VersaNets)" section was updated.                                                                        | 2-9              |

|              | The "VersaNet Global Networks and Spine Access" section was updated.                                                          | 2-9              |

|              | The "PLL Macro" section was updated.                                                                                          | 2-15             |

|              | Figure 2-27 was updated.                                                                                                      | 2-28             |

|              | Figure 2-20 was updated.                                                                                                      | 2-19             |

|              | Table 2-5 was updated.                                                                                                        | 2-25             |

|              | Table 2-6 was updated.                                                                                                        | 2-25             |

|              | The "FIFO Flag Usage Considerations" section was updated.                                                                     | 2-27             |

|              | Table 2-13 was updated.                                                                                                       | 2-30             |

|              | Figure 2-24 was updated.                                                                                                      | 2-31             |

|              | The "Cold-Sparing Support" section is new.                                                                                    | 2-34             |