# E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                                 |

|--------------------------------|--------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | ·                                                                        |

| Total RAM Bits                 | 147456                                                                   |

| Number of I/O                  | 154                                                                      |

| Number of Gates                | 100000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 208-BFQFP                                                                |

| Supplier Device Package        | 208-PQFP (28x28)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p1000-2pq208 |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ProASIC3 Devices               | A3P015 <sup>1</sup> | A3P030                            | A3P060                  | A3P125             | A3P250                          | A3P400                     | A3P600                     | A3P1000                    |

|--------------------------------|---------------------|-----------------------------------|-------------------------|--------------------|---------------------------------|----------------------------|----------------------------|----------------------------|

| Cortex-M1 Devices <sup>2</sup> |                     |                                   |                         |                    | M1A3P250                        | M1A3P400                   | M1A3P600                   | M1A3P1000                  |

| Package Pins<br>QFN            | QN68                | QN48, QN68,<br>QN132 <sup>7</sup> | QN132 <sup>7</sup>      | QN132 <sup>7</sup> | QN132 <sup>7</sup>              |                            |                            |                            |

| CS<br>VQFP<br>TQFP             |                     | VQ100                             | CS121<br>VQ100<br>TQ144 | VQ100<br>TQ144     | VQ100                           |                            |                            |                            |

| PQFP<br>FBGA                   |                     |                                   | FG144                   | PQ208<br>FG144     | PQ208<br>FG144/256 <sup>5</sup> | PQ208<br>FG144/256/<br>484 | PQ208<br>FG144/256/<br>484 | PQ208<br>FG144/256/<br>484 |

Notes:

- A3P015 is not recommended for new designs.

Refer to the Cortex-M1 product brief for more information.

AES is not available for Cortex-M1 ProASIC3 devices.

Six chip (main) and three quadrant global networks are available for A3P060 and above.

The M1A3P250 device does not support this package.

For higher densities and support of additional features, refer to the ProASIC3E Flash Family FPGAs datasheet.

Package not available.

Your valuable IP is protected with industry-standard security, making remote ISP possible. A ProASIC3 device provides the best available security for programmable logic designs.

### Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system powerup (unlike SRAM-based FPGAs). Therefore, flash-based ProASIC3 FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

#### Instant On

Flash-based ProASIC3 devices support Level 0 of the Instant On classification standard. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. The Instant On feature of flash-based ProASIC3 devices greatly simplifies total system design and reduces total system cost, often eliminating the need for CPLDs and clock generation PLLs that are used for these purposes in a system. In addition, glitches and brownouts in system power will not corrupt the ProASIC3 device's flash configuration, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based ProASIC3 devices simplify total system design and reduce cost and design risk while increasing system reliability and improving system initialization time.

#### Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of ProASIC3 flash-based FPGAs. Once it is programmed, the flash cell configuration element of ProASIC3 FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

#### Low Power

Flash-based ProASIC3 devices exhibit power characteristics similar to an ASIC, making them an ideal choice for power-sensitive applications. ProASIC3 devices have only a very limited power-on current surge and no high-current transition period, both of which occur on many FPGAs.

ProASIC3 devices also have low dynamic power consumption to further maximize power savings.

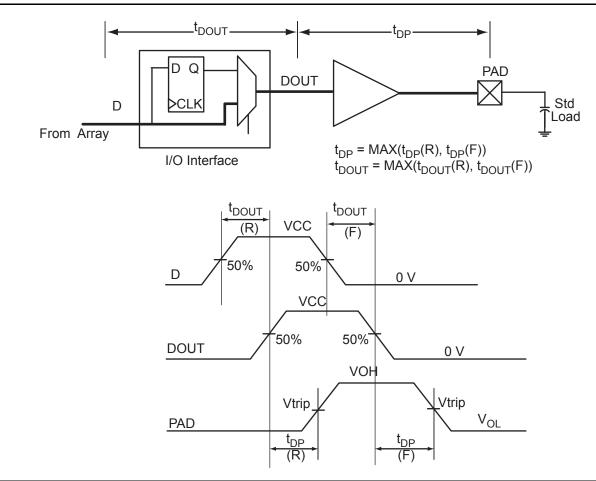

Figure 2-5 • Output Buffer Model and Delays (Example)

#### Table 2-20 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings Applicable to Standard I/O Banks

|                                            |                   | Equiv.                                                          |      |          | VIL         | VIH         |          | VOL         | VOH         |                        |                        |

|--------------------------------------------|-------------------|-----------------------------------------------------------------|------|----------|-------------|-------------|----------|-------------|-------------|------------------------|------------------------|

| I/O Standard                               | Drive<br>Strength | Software<br>Default<br>Drive<br>Strength<br>Option <sup>2</sup> | Slew | Min<br>V | Max<br>V    | Min<br>V    | Max<br>V | Max<br>V    | Min<br>V    | IOL <sup>1</sup><br>mA | IOH <sup>1</sup><br>mA |

| 3.3 V LVTTL /<br>3.3 V<br>LVCMOS           | 8 mA              | 8 mA                                                            | High | -0.3     | 0.8         | 2           | 3.6      | 0.4         | 2.4         | 8                      | 8                      |

| 3.3 V<br>LVCMOS<br>Wide Range <sup>3</sup> | 100 µA            | 8 mA                                                            | High | -0.3     | 0.8         | 2           | 3.6      | 0.2         | VCCI – 0.2  | 0.1                    | 0.1                    |

| 2.5 V<br>LVCMOS                            | 8 mA              | 8 mA                                                            | High | -0.3     | 0.7         | 1.7         | 2.7      | 0.7         | 1.7         | 8                      | 8                      |

| 1.8 V<br>LVCMOS                            | 4 mA              | 4 mA                                                            | High | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45        | VCCI – 0.45 | 4                      | 4                      |

| 1.5 V<br>LVCMOS                            | 2 mA              | 2 mA                                                            | High | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.25 * VCCI | 0.75 * VCCI | 2                      | 2                      |

Notes:

1. Currents are measured at 85°C junction temperature.

2. 3.3 V LVCMOS wide range is applicable to 100 μA drive strength only. The configuration will NOT operate at the equivalent software default drive strength. These values are for Normal Ranges ONLY.

3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

## Table 2-21 • Summary of Maximum and Minimum DC Input Levels Applicable to Commercial and Industrial Conditions

|                            | Comr             | nercial <sup>1</sup> | Industrial <sup>2</sup> |                  |  |

|----------------------------|------------------|----------------------|-------------------------|------------------|--|

|                            | IIL <sup>3</sup> | IIH <sup>4</sup>     | IIL <sup>3</sup>        | IIH <sup>4</sup> |  |

| DC I/O Standards           | μA               | μA                   | μA                      | μA               |  |

| 3.3 V LVTTL / 3.3 V LVCMOS | 10               | 10                   | 15                      | 15               |  |

| 3.3 V LVCMOS Wide Range    | 10               | 10                   | 15                      | 15               |  |

| 2.5 V LVCMOS               | 10               | 10                   | 15                      | 15               |  |

| 1.8 V LVCMOS               | 10               | 10                   | 15                      | 15               |  |

| 1.5 V LVCMOS               | 10               | 10                   | 15                      | 15               |  |

| 3.3 V PCI                  | 10               | 10                   | 15                      | 15               |  |

| 3.3 V PCI-X                | 10               | 10                   | 15                      | 15               |  |

Notes:

1. Commercial range ( $0^{\circ}C < T_A < 70^{\circ}C$ )

2. Industrial range  $(-40^{\circ}C < T_A < 85^{\circ}C)$

- 3. IIL is the input leakage current per I/O pin over recommended operation conditions where  $-0.3V < V_{IN} < V_{IL}$ .

- 4. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

|                   | Applica        | ble to St         | andard          | Plus I/          | J Bank          | S                 |                 |                 |                 |                 |                  |                  |       |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 2 mA              | Std.           | 0.66              | 9.68            | 0.04             | 1.00            | 0.43              | 9.86            | 8.42            | 2.28            | 2.21            | 12.09            | 10.66            | ns    |

|                   | -1             | 0.56              | 8.23            | 0.04             | 0.85            | 0.36              | 8.39            | 7.17            | 1.94            | 1.88            | 10.29            | 9.07             | ns    |

|                   | -2             | 0.49              | 7.23            | 0.03             | 0.75            | 0.32              | 7.36            | 6.29            | 1.70            | 1.65            | 9.03             | 7.96             | ns    |

| 4 mA              | Std.           | 0.66              | 9.68            | 0.04             | 1.00            | 0.43              | 9.86            | 8.42            | 2.28            | 2.21            | 12.09            | 10.66            | ns    |

|                   | -1             | 0.56              | 8.23            | 0.04             | 0.85            | 0.36              | 8.39            | 7.17            | 1.94            | 1.88            | 10.29            | 9.07             | ns    |

|                   | -2             | 0.49              | 7.23            | 0.03             | 0.75            | 0.32              | 7.36            | 6.29            | 1.70            | 1.65            | 9.03             | 7.96             | ns    |

| 6 mA              | Std.           | 0.66              | 6.70            | 0.04             | 1.00            | 0.43              | 6.82            | 5.89            | 2.58            | 2.74            | 9.06             | 8.12             | ns    |

|                   | -1             | 0.56              | 5.70            | 0.04             | 0.85            | 0.36              | 5.80            | 5.01            | 2.20            | 2.33            | 7.71             | 6.91             | ns    |

|                   | -2             | 0.49              | 5.00            | 0.03             | 0.75            | 0.32              | 5.10            | 4.40            | 1.93            | 2.05            | 6.76             | 6.06             | ns    |

| 8 mA              | Std.           | 0.66              | 6.70            | 0.04             | 1.00            | 0.43              | 6.82            | 5.89            | 2.58            | 2.74            | 9.06             | 8.12             | ns    |

|                   | -1             | 0.56              | 5.70            | 0.04             | 0.85            | 0.36              | 5.80            | 5.01            | 2.20            | 2.33            | 7.71             | 6.91             | ns    |

|                   | -2             | 0.49              | 5.00            | 0.03             | 0.75            | 0.32              | 5.10            | 4.40            | 1.93            | 2.05            | 6.76             | 6.06             | ns    |

| 12 mA             | Std.           | 0.66              | 5.05            | 0.04             | 1.00            | 0.43              | 5.14            | 4.51            | 2.79            | 3.08            | 7.38             | 6.75             | ns    |

|                   | -1             | 0.56              | 4.29            | 0.04             | 0.85            | 0.36              | 4.37            | 3.84            | 2.38            | 2.62            | 6.28             | 5.74             | ns    |

|                   | -2             | 0.49              | 3.77            | 0.03             | 0.75            | 0.32              | 3.84            | 3.37            | 2.09            | 2.30            | 5.51             | 5.04             | ns    |

| 16 mA             | Std.           | 0.66              | 5.05            | 0.04             | 1.00            | 0.43              | 5.14            | 4.51            | 2.79            | 3.08            | 7.38             | 6.75             | ns    |

|                   | -1             | 0.56              | 4.29            | 0.04             | 0.85            | 0.36              | 4.37            | 3.84            | 2.38            | 2.62            | 6.28             | 5.74             | ns    |

|                   | -2             | 0.49              | 3.77            | 0.03             | 0.75            | 0.32              | 3.84            | 3.37            | 2.09            | 2.30            | 5.51             | 5.04             | ns    |

Table 2-44 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus I/O Banks

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-45 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | -1             | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2             | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 4 mA              | Std.           | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | –1             | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2             | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 6 mA              | Std.           | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | –1             | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

|                   | -2             | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns    |

| 8 mA              | Std.           | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | -1             | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

| Table 2-52 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew |                                                   |

|---------------------------------------------------|---------------------------------------------------|

| Commercial-Case Conditions: $T_J = 70^{\circ}C$ , | Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V |

| Applicable to Standard Plus I/O Banks             |                                                   |

| -                 | Applicable                                                                |                |                   |                 |                  |                 |                   |                 |                 |                 |                 |                  |                  | -     |

|-------------------|---------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Equiv.<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>dout</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>eout</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zнs</sub> | Units |

| 100 µA            | 2 mA                                                                      | Std.           | 0.60              | 11.14           | 0.04             | 1.52            | 0.43              | 11.14           | 9.54            | 3.51            | 3.61            | 14.53            | 12.94            | ns    |

|                   |                                                                           | -1             | 0.51              | 9.48            | 0.04             | 1.29            | 0.36              | 9.48            | 8.12            | 2.99            | 3.07            | 12.36            | 11.00            | ns    |

|                   |                                                                           | -2             | 0.45              | 8.32            | 0.03             | 1.14            | 0.32              | 8.32            | 7.13            | 2.62            | 2.70            | 10.85            | 9.66             | ns    |

| 100 µA            | 4 mA                                                                      | Std.           | 0.60              | 6.96            | 0.04             | 1.52            | 0.43              | 6.96            | 5.79            | 3.99            | 4.45            | 10.35            | 9.19             | ns    |

|                   |                                                                           | -1             | 0.51              | 5.92            | 0.04             | 1.29            | 0.36              | 5.92            | 4.93            | 3.39            | 3.78            | 8.81             | 7.82             | ns    |

|                   |                                                                           | -2             | 0.45              | 5.20            | 0.03             | 1.14            | 0.32              | 5.20            | 4.33            | 2.98            | 3.32            | 7.73             | 6.86             | ns    |

| 100 µA            | 6 mA                                                                      | Std.           | 0.60              | 6.96            | 0.04             | 1.52            | 0.43              | 6.96            | 5.79            | 3.99            | 4.45            | 10.35            | 9.19             | ns    |

|                   |                                                                           | -1             | 0.51              | 5.92            | 0.04             | 1.29            | 0.36              | 5.92            | 4.93            | 3.39            | 3.78            | 8.81             | 7.82             | ns    |

|                   |                                                                           | -2             | 0.45              | 5.20            | 0.03             | 1.14            | 0.32              | 5.20            | 4.33            | 2.98            | 3.32            | 7.73             | 6.86             | ns    |

| 100 µA            | 8 mA                                                                      | Std.           | 0.60              | 4.89            | 0.04             | 1.52            | 0.43              | 4.89            | 3.92            | 4.31            | 4.98            | 8.28             | 7.32             | ns    |

|                   |                                                                           | -1             | 0.51              | 4.16            | 0.04             | 1.29            | 0.36              | 4.16            | 3.34            | 3.67            | 4.24            | 7.04             | 6.22             | ns    |

|                   |                                                                           | -2             | 0.45              | 3.65            | 0.03             | 1.14            | 0.32              | 3.65            | 2.93            | 3.22            | 3.72            | 6.18             | 5.46             | ns    |

| 100 µA            | 16 mA                                                                     | Std.           | 0.60              | 4.89            | 0.04             | 1.52            | 0.43              | 4.89            | 3.92            | 4.31            | 4.98            | 8.28             | 7.32             | ns    |

|                   |                                                                           | -1             | 0.51              | 4.16            | 0.04             | 1.29            | 0.36              | 4.16            | 3.34            | 3.67            | 4.24            | 7.04             | 6.22             | ns    |

|                   |                                                                           | -2             | 0.45              | 3.65            | 0.03             | 1.14            | 0.32              | 3.65            | 2.93            | 3.22            | 3.72            | 6.18             | 5.46             | ns    |

Notes:

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

Software default selection bioblighted in group.

2. Software default selection highlighted in gray.

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### 1.8 V LVCMOS

Low-voltage CMOS for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.8 V applications. It uses a 1.8 V input buffer and a push-pull output buffer.

| 1.8 V<br>LVCMOS   |          | VIL         | VIH         |          | VOL      | VOH         | IOL | юн | IOSL                   | IOSH                   | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|----------|-------------|-------------|----------|----------|-------------|-----|----|------------------------|------------------------|------------------|------------------|

| Drive<br>Strength | Min<br>V | Max<br>V    | Min<br>V    | Max<br>V | Max<br>V | Min<br>V    | mA  | mA | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI-0.45   | 2   | 2  | 11                     | 9                      | 10               | 10               |

| 4 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI-0.45   | 4   | 4  | 22                     | 17                     | 10               | 10               |

| 6 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI - 0.45 | 6   | 6  | 44                     | 35                     | 10               | 10               |

| 8 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI-0.45   | 8   | 8  | 51                     | 45                     | 10               | 10               |

| 12 mA             | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI-0.45   | 12  | 12 | 74                     | 91                     | 10               | 10               |

| 16 mA             | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI-0.45   | 16  | 16 | 74                     | 91                     | 10               | 10               |

#### Table 2-66 • Minimum and Maximum DC Input and Output Levels Applicable to Advanced I/O Banks

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

## Table 2-67 • Minimum and Maximum DC Input and Output Levels Applicable to Standard Plus I/O I/O Banks

| 1.8 V<br>LVCMOS   | VIL      |             | VIH         |          | VIL VIH  |             | VOL | VOH | IOL                    | ЮН                     | IOSL            | IOSH            | IIL¹ | IIH <sup>2</sup> |

|-------------------|----------|-------------|-------------|----------|----------|-------------|-----|-----|------------------------|------------------------|-----------------|-----------------|------|------------------|

| Drive<br>Strength | Min<br>V | Max<br>V    | Min<br>V    | Max<br>V | Max<br>V | Min<br>V    | mA  | mA  | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup> |      |                  |

| 2 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI – 0.45 | 2   | 2   | 11                     | 9                      | 10              | 10              |      |                  |

| 4 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI – 0.45 | 4   | 4   | 22                     | 17                     | 10              | 10              |      |                  |

| 6 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI – 0.45 | 6   | 6   | 44                     | 35                     | 10              | 10              |      |                  |

| 8 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI - 0.45 | 8   | 8   | 44                     | 35                     | 10              | 10              |      |                  |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN <V CCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

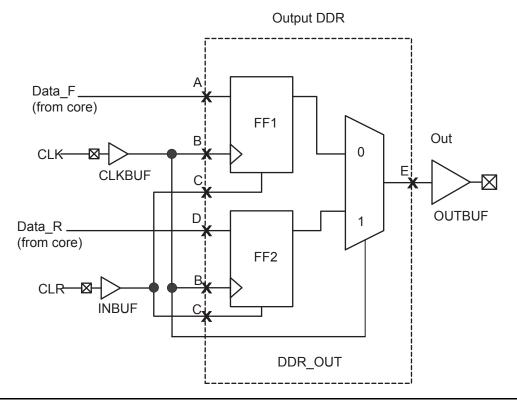

## **Output DDR Module**

### Figure 2-22 • Output DDR Timing Model

#### Table 2-103 • Parameter Definitions

| Parameter Name          | Parameter Definition      | Measuring Nodes (from, to) |

|-------------------------|---------------------------|----------------------------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out              | B, E                       |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out | C, E                       |

| t <sub>DDROREMCLR</sub> | Clear Removal             | С, В                       |

| t <sub>DDRORECCLR</sub> | Clear Recovery            | С, В                       |

| t <sub>DDROSUD1</sub>   | Data Setup Data_F         | А, В                       |

| t <sub>DDROSUD2</sub>   | Data Setup Data_R         | D, B                       |

| t <sub>DDROHD1</sub>    | Data Hold Data_F          | А, В                       |

| t <sub>DDROHD2</sub>    | Data Hold Data_R          | D, B                       |

| Parameter             | Description                                                                                                        | -2   | -1   | Std. | Units |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                 | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                  | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                | 0.13 | 0.15 | 0.17 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                 | 0.10 | 0.11 | 0.13 | ns    |

| t <sub>DS</sub>       | Input data (WD) setup time                                                                                         | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>       | Input data (WD) hold time                                                                                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on RD (output retained)                                                               | 2.16 | 2.46 | 2.89 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on RD (pipelined)                                                                     | 0.90 | 1.02 | 1.20 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge | 0.50 | 0.43 | 0.38 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address—Applicable to Opening Edge | 0.59 | 0.50 | 0.44 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on RD (flow-through)                                                                     | 0.92 | 1.05 | 1.23 | ns    |

|                       | RESET Low to data out Low on RD (pipelined)                                                                        | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                      | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                     | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                          | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                   | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                  | 310  | 272  | 231  | MHz   |

#### Table 2-117 • RAM512X18

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-120 • A3P250 FIFO 512×8

### Worst Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

| Parameter            | Description                                       | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 3.75 | 4.27 | 5.02 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.22 | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.17 | 2.47 | 2.90 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.94 | 1.07 | 1.26 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96 | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86 | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05 | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93 | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.13 | 6.98 | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.92 | 1.05 | 1.23 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272  | 231  | MHz   |

In critical applications, an upset in the JTAG circuit could allow entrance to an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

## **Special Function Pins**

#### NC

#### No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

DC Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

## **Related Documents**

### **User's Guides**

ProASIC FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/PA3\_UG.pdf

## Packaging

The following documents provide packaging information and device selection for low power flash devices.

#### **Product Catalog**

http://www.microsemi.com/soc/documents/ProdCat\_PIB.pdf

Lists devices currently recommended for new designs and the packages available for each member of the family. Use this document or the datasheet tables to determine the best package for your design, and which package drawing to use.

#### Package Mechanical Drawings

http://www.microsemi.com/soc/documents/PckgMechDrwngs.pdf

This document contains the package mechanical drawings for all packages currently or previously supplied by Actel. Use the bookmarks to navigate to the package mechanical drawings.

Additional packaging materials are at http://www.microsemi.com/products/solutions/package/docs.aspx.

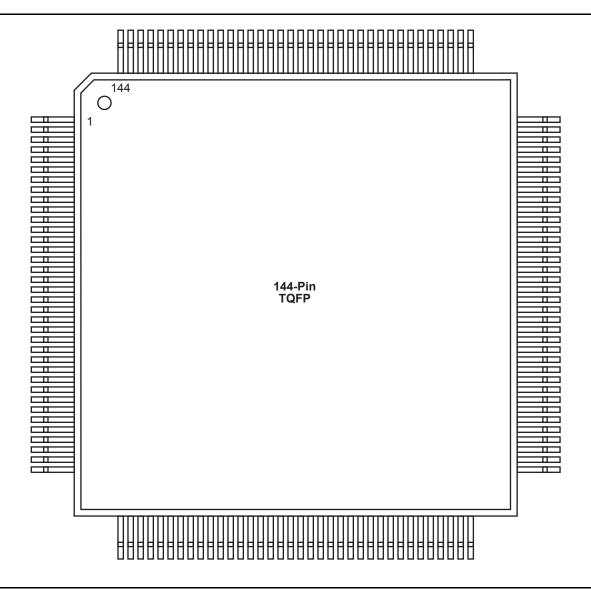

## TQ144 – Top View

### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

## **Microsemi**

Package Pin Assignments

| PQ208      |                 | PQ208      |                 | PQ208      |                 |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|

| Pin Number | A3P125 Function | Pin Number | A3P125 Function | Pin Number | A3P125 Function |  |

| 109        | TRST            | 145        | IO46RSB0        | 181        | IO21RSB0        |  |

| 110        | VJTAG           | 146        | NC              | 182        | IO20RSB0        |  |

| 111        | GDA0/IO66RSB0   | 147        | NC              | 183        | IO19RSB0        |  |

| 112        | GDA1/IO65RSB0   | 148        | NC              | 184        | IO18RSB0        |  |

| 113        | GDB0/IO64RSB0   | 149        | GBC2/IO45RSB0   | 185        | IO17RSB0        |  |

| 114        | GDB1/IO63RSB0   | 150        | IO44RSB0        | 186        | VCCIB0          |  |

| 115        | GDC0/IO62RSB0   | 151        | GBB2/IO43RSB0   | 187        | VCC             |  |

| 116        | GDC1/IO61RSB0   | 152        | IO42RSB0        | 188        | IO16RSB0        |  |

| 117        | NC              | 153        | GBA2/IO41RSB0   | 189        | IO15RSB0        |  |

| 118        | NC              | 154        | VMV0            | 190        | IO14RSB0        |  |

| 119        | NC              | 155        | GNDQ            | 191        | IO13RSB0        |  |

| 120        | NC              | 156        | GND             | 192        | IO12RSB0        |  |

| 121        | NC              | 157        | NC              | 193        | IO11RSB0        |  |

| 122        | GND             | 158        | GBA1/IO40RSB0   | 194        | IO10RSB0        |  |

| 123        | VCCIB0          | 159        | GBA0/IO39RSB0   | 195        | GND             |  |

| 124        | NC              | 160        | GBB1/IO38RSB0   | 196        | IO09RSB0        |  |

| 125        | NC              | 161        | GBB0/IO37RSB0   | 197        | IO08RSB0        |  |

| 126        | VCC             | 162        | GND             | 198        | IO07RSB0        |  |

| 127        | IO60RSB0        | 163        | GBC1/IO36RSB0   | 199        | IO06RSB0        |  |

| 128        | GCC2/IO59RSB0   | 164        | GBC0/IO35RSB0   | 200        | VCCIB0          |  |

| 129        | GCB2/IO58RSB0   | 165        | IO34RSB0        | 201        | GAC1/IO05RSB0   |  |

| 130        | GND             | 166        | IO33RSB0        | 202        | GAC0/IO04RSB0   |  |

| 131        | GCA2/IO57RSB0   | 167        | IO32RSB0        | 203        | GAB1/IO03RSB0   |  |

| 132        | GCA0/IO56RSB0   | 168        | IO31RSB0        | 204        | GAB0/IO02RSB0   |  |

| 133        | GCA1/IO55RSB0   | 169        | IO30RSB0        | 205        | GAA1/IO01RSB0   |  |

| 134        | GCB0/IO54RSB0   | 170        | VCCIB0          | 206        | GAA0/IO00RSB0   |  |

| 135        | GCB1/IO53RSB0   | 171        | VCC             | 207        | GNDQ            |  |

| 136        | GCC0/IO52RSB0   | 172        | IO29RSB0        | 208        | VMV0            |  |

| 137        | GCC1/IO51RSB0   | 173        | IO28RSB0        |            |                 |  |

| 138        | IO50RSB0        | 174        | IO27RSB0        |            |                 |  |

| 139        | IO49RSB0        | 175        | IO26RSB0        |            |                 |  |

| 140        | VCCIB0          | 176        | IO25RSB0        |            |                 |  |

| 141        | GND             | 177        | IO24RSB0        |            |                 |  |

| 142        | VCC             | 178        | GND             |            |                 |  |

| 143        | IO48RSB0        | 179        | IO23RSB0        |            |                 |  |

| 144        | IO47RSB0        | 180        | IO22RSB0        |            |                 |  |

| PQ208      |                 | PQ208      |                 | PQ208      |                 |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|

| Pin Number | A3P600 Function | Pin Number | A3P600 Function | Pin Number | A3P600 Function |  |

| 1          | GND             | 37         | IO152PDB3       | 73         | IO120RSB2       |  |

| 2          | GAA2/IO174PDB3  | 38         | IO152NDB3       | 74         | IO119RSB2       |  |

| 3          | IO174NDB3       | 39         | IO150PSB3       | 75         | IO118RSB2       |  |

| 4          | GAB2/IO173PDB3  | 40         | VCCIB3          | 76         | IO117RSB2       |  |

| 5          | IO173NDB3       | 41         | GND             | 77         | IO116RSB2       |  |

| 6          | GAC2/IO172PDB3  | 42         | IO147PDB3       | 78         | IO115RSB2       |  |

| 7          | IO172NDB3       | 43         | IO147NDB3       | 79         | IO114RSB2       |  |

| 8          | IO171PDB3       | 44         | GEC1/IO146PDB3  | 80         | IO112RSB2       |  |

| 9          | IO171NDB3       | 45         | GEC0/IO146NDB3  | 81         | GND             |  |

| 10         | IO170PDB3       | 46         | GEB1/IO145PDB3  | 82         | IO111RSB2       |  |

| 11         | IO170NDB3       | 47         | GEB0/IO145NDB3  | 83         | IO110RSB2       |  |

| 12         | IO169PDB3       | 48         | GEA1/IO144PDB3  | 84         | IO109RSB2       |  |

| 13         | IO169NDB3       | 49         | GEA0/IO144NDB3  | 85         | IO108RSB2       |  |

| 14         | IO168PDB3       | 50         | VMV3            | 86         | IO107RSB2       |  |

| 15         | IO168NDB3       | 51         | GNDQ            | 87         | IO106RSB2       |  |

| 16         | VCC             | 52         | GND             | 88         | VCC             |  |

| 17         | GND             | 53         | VMV2            | 89         | VCCIB2          |  |

| 18         | VCCIB3          | 54         | GEA2/IO143RSB2  | 90         | IO104RSB2       |  |

| 19         | IO166PDB3       | 55         | GEB2/IO142RSB2  | 91         | IO102RSB2       |  |

| 20         | IO166NDB3       | 56         | GEC2/IO141RSB2  | 92         | IO100RSB2       |  |

| 21         | GFC1/IO164PDB3  | 57         | IO140RSB2       | 93         | IO98RSB2        |  |

| 22         | GFC0/IO164NDB3  | 58         | IO139RSB2       | 94         | IO96RSB2        |  |

| 23         | GFB1/IO163PDB3  | 59         | IO138RSB2       | 95         | IO92RSB2        |  |

| 24         | GFB0/IO163NDB3  | 60         | IO137RSB2       | 96         | GDC2/IO91RSB2   |  |

| 25         | VCOMPLF         | 61         | IO136RSB2       | 97         | GND             |  |

| 26         | GFA0/IO162NPB3  | 62         | VCCIB2          | 98         | GDB2/IO90RSB2   |  |

| 27         | VCCPLF          | 63         | IO135RSB2       | 99         | GDA2/IO89RSB2   |  |

| 28         | GFA1/IO162PPB3  | 64         | IO133RSB2       | 100        | GNDQ            |  |

| 29         | GND             | 65         | GND             | 101        | ТСК             |  |

| 30         | GFA2/IO161PDB3  | 66         | IO131RSB2       | 102        | TDI             |  |

| 31         | IO161NDB3       | 67         | IO129RSB2       | 103        | TMS             |  |

| 32         | GFB2/IO160PDB3  | 68         | IO127RSB2       | 104        | VMV2            |  |

| 33         | IO160NDB3       | 69         | IO125RSB2       | 105        | GND             |  |

| 34         | GFC2/IO159PDB3  | 70         | IO123RSB2       | 106        | VPUMP           |  |

| 35         | IO159NDB3       | 71         | VCC             | 107        | GNDQ            |  |

| 36         | VCC             | 72         | VCCIB2          | 108        | TDO             |  |

## 🌜 Microsemi.

Package Pin Assignments

| FG144      |                 | FG144      |                 | FG144                     |                |  |

|------------|-----------------|------------|-----------------|---------------------------|----------------|--|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number A3P250 Functio |                |  |

| A1         | GNDQ            | D1         | IO112NDB3       | G1                        | GFA1/IO108PPB3 |  |

| A2         | VMV0            | D2         | IO112PDB3       | G2                        | GND            |  |

| A3         | GAB0/IO02RSB0   | D3         | IO116VDB3       | G3                        | VCCPLF         |  |

| A4         | GAB1/IO03RSB0   | D4         | GAA2/IO118UPB3  | G4                        | GFA0/IO108NPB3 |  |

| A5         | IO16RSB0        | D5         | GAC0/IO04RSB0   | G5                        | GND            |  |

| A6         | GND             | D6         | GAC1/IO05RSB0   | G6                        | GND            |  |

| A7         | IO29RSB0        | D7         | GBC0/IO35RSB0   | G7                        | GND            |  |

| A8         | VCC             | D8         | GBC1/IO36RSB0   | G8                        | GDC1/IO58UPB1  |  |

| A9         | IO33RSB0        | D9         | GBB2/IO42PDB1   | G9                        | IO53NDB1       |  |

| A10        | GBA0/IO39RSB0   | D10        | IO42NDB1        | G10                       | GCC2/IO53PDB1  |  |

| A11        | GBA1/IO40RSB0   | D11        | IO43NPB1        | G11                       | IO52NDB1       |  |

| A12        | GNDQ            | D12        | GCB1/IO49PPB1   | G12                       | GCB2/IO52PDB1  |  |

| B1         | GAB2/IO117UDB3  | E1         | VCC             | H1                        | VCC            |  |

| B2         | GND             | E2         | GFC0/IO110NDB3  | H2                        | GFB2/IO106PDB3 |  |

| B3         | GAA0/IO00RSB0   | E3         | GFC1/IO110PDB3  | H3                        | GFC2/IO105PSB3 |  |

| B4         | GAA1/IO01RSB0   | E4         | VCCIB3          | H4                        | GEC1/IO100PDB3 |  |

| B5         | IO14RSB0        | E5         | IO118VPB3       | H5                        | VCC            |  |

| B6         | IO19RSB0        | E6         | VCCIB0          | H6                        | IO79RSB2       |  |

| B7         | IO22RSB0        | E7         | VCCIB0          | H7                        | IO65RSB2       |  |

| B8         | IO30RSB0        | E8         | GCC1/IO48PDB1   | H8                        | GDB2/IO62RSB2  |  |

| B9         | GBB0/IO37RSB0   | E9         | VCCIB1          | H9                        | GDC0/IO58VPB1  |  |

| B10        | GBB1/IO38RSB0   | E10        | VCC             | H10                       | VCCIB1         |  |

| B11        | GND             | E11        | GCA0/IO50NDB1   | H11                       | IO54PSB1       |  |

| B12        | VMV1            | E12        | IO51NDB1        | H12                       | VCC            |  |

| C1         | IO117VDB3       | F1         | GFB0/IO109NPB3  | J1                        | GEB1/IO99PDB3  |  |

| C2         | GFA2/IO107PPB3  | F2         | VCOMPLF         | J2                        | IO106NDB3      |  |

| C3         | GAC2/IO116UDB3  | F3         | GFB1/IO109PPB3  | J3                        | VCCIB3         |  |

| C4         | VCC             | F4         | IO107NPB3       | J4                        | GEC0/IO100NDB3 |  |

| C5         | IO12RSB0        | F5         | GND             | J5                        | IO88RSB2       |  |

| C6         | IO17RSB0        | F6         | GND             | J6                        | IO81RSB2       |  |

| C7         | IO24RSB0        | F7         | GND             | J7                        | VCC            |  |

| C8         | IO31RSB0        | F8         | GCC0/IO48NDB1   | J8                        | ТСК            |  |

| C9         | IO34RSB0        | F9         | GCB0/IO49NPB1   | J9                        | GDA2/IO61RSB2  |  |

| C10        | GBA2/IO41PDB1   | F10        | GND             | J10                       | TDO            |  |

| C11        | IO41NDB1        | F11        | GCA1/IO50PDB1   | J11                       | GDA1/IO60UDB1  |  |

| C12        | GBC2/IO43PPB1   | F12        | GCA2/IO51PDB1   | J12                       | GDB1/IO59UDB1  |  |

| FG256                      |               |  |  |  |

|----------------------------|---------------|--|--|--|

| Pin Number A3P250 Function |               |  |  |  |

| P9                         | IO76RSB2      |  |  |  |

| P10                        | IO71RSB2      |  |  |  |

| P11                        | IO66RSB2      |  |  |  |

| P12                        | NC            |  |  |  |

| P13                        | ТСК           |  |  |  |

| P14                        | VPUMP         |  |  |  |

| P15                        | TRST          |  |  |  |

| P16                        | GDA0/IO60VDB1 |  |  |  |

| R1                         | GEA1/IO98PDB3 |  |  |  |

| R2                         | GEA0/IO98NDB3 |  |  |  |

| R3                         | NC            |  |  |  |

| R4                         | GEC2/IO95RSB2 |  |  |  |

| R5                         | IO91RSB2      |  |  |  |

| R6                         | IO88RSB2      |  |  |  |

| R7                         | IO84RSB2      |  |  |  |

| R8                         | IO80RSB2      |  |  |  |

| R9                         | IO77RSB2      |  |  |  |

| R10                        | IO72RSB2      |  |  |  |

| R11                        | IO68RSB2      |  |  |  |

| R12                        | IO65RSB2      |  |  |  |

| R13                        | GDB2/IO62RSB2 |  |  |  |

| R14                        | TDI           |  |  |  |

| R15                        | NC            |  |  |  |

| R16                        | TDO           |  |  |  |

| T1                         | GND           |  |  |  |

| T2                         | IO94RSB2      |  |  |  |

| Т3                         | GEB2/IO96RSB2 |  |  |  |

| T4                         | IO93RSB2      |  |  |  |

| Τ5                         | IO90RSB2      |  |  |  |

| Т6                         | IO87RSB2      |  |  |  |

| Τ7                         | IO83RSB2      |  |  |  |

| Т8                         | IO79RSB2      |  |  |  |

| Т9                         | IO78RSB2      |  |  |  |

| T10                        | IO73RSB2      |  |  |  |

| T11                        | IO70RSB2      |  |  |  |

| T12                        | GDC2/IO63RSB2 |  |  |  |

| FG256      |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | A3P250 Function |  |  |  |

| T13        | IO67RSB2        |  |  |  |

| T14        | GDA2/IO61RSB2   |  |  |  |

| T15        | TMS             |  |  |  |

| T16        | GND             |  |  |  |

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page       |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Revision 10<br>(September 2011) | The "In-System Programming (ISP) and Security" section and Security section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 32865).                                                                                                                                                                                                                    | I          |

|                                 | The value of 34 I/Os for the QN48 package in A3P030 was added to the "I/Os Per Package 1" section (SAR 33907).                                                                                                                                                                                                                                                                                                                                                                        |            |

|                                 | The Y security option and Licensed DPA Logo were added to the "ProASIC3<br>Ordering Information" section. The trademarked Licensed DPA Logo identifies<br>that a product is covered by a DPA counter-measures license from<br>Cryptography Research (SAR 32151).                                                                                                                                                                                                                      | IV         |

|                                 | The "Specifying I/O States During Programming" section is new (SAR 21281).                                                                                                                                                                                                                                                                                                                                                                                                            | 1-7        |

|                                 | In Table 2-2 • Recommended Operating Conditions 1, VPUMP programming voltage in programming mode was changed from "3.0 to 3.6" to "3.15 to 3.45" (SAR 30666). It was corrected in v2.0 of this datasheet in April 2007 but inadvertently changed back to "3.0 to 3.6 V" in v1.4 in August 2009. The following changes were made to Table 2-2 • Recommended Operating Conditions 1: VCCPLL analog power supply (PLL) was changed from "1.4 to 1.6" to "1.425 to 1.575" (SAR 33850).    | 2-2        |

|                                 | For VCCI and VMV, values for 3.3 V DC and 3.3 V DC Wide Range were corrected. The correct value for 3.3 V DC is "3.0 to 3.6 V" and the correct value for 3.3 V Wide Range is "2.7 to 3.6" (SAR 33848).                                                                                                                                                                                                                                                                                |            |

|                                 | Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings was update to restore values to the correct columns. Previously the Slew Rate column was missing and data were aligned incorrectly (SAR 34034).                                                                                                                                                                                                                                                          | 2-24       |

|                                 | The notes regarding drive strength in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section and "3.3 V LVCMOS Wide Range" section tables were revised for clarification. They now state that the minimum drive strength for the default software configuration when run in wide range is $\pm 100 \ \mu$ A. The drive strength displayed in software is supported in normal range only. For a detailed I/V curve, refer to the IBIS models (SAR 25700). | 2-22, 2-39 |

Datasheet Information

| Revision     | Changes                                                                                                                       | Page             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|

| Advance v0.3 | The "PLL Macro" section was updated. EXTFB information was removed from this section.                                         | 2-15             |

|              | The CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub> was updated in Table 2-<br>11 • ProASIC3 CCC/PLL Specification | 2-29             |

|              | EXTFB was removed from Figure 2-27 • CCC/PLL Macro.                                                                           | 2-28             |

|              | Table 2-13 • ProASIC3 I/O Features was updated.                                                                               | 2-30             |

|              | The "Hot-Swap Support" section was updated.                                                                                   | 2-33             |

|              | The "Cold-Sparing Support" section was updated.                                                                               | 2-34             |

|              | "Electrostatic Discharge (ESD) Protection" section was updated.                                                               | 2-35             |

|              | The LVPECL specification in Table 2-43 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3 Devices was updated.   | 2-64             |

|              | In the Bank 1 area of Figure 2-72, VMV2 was changed to VMV1 and VCCIB2 was changed to VCC_IB1.                                | 2-97             |

|              | The VJTAG and I/O pin descriptions were updated in the "Pin Descriptions" section.                                            | 2-50             |

|              | The "JTAG Pins" section was updated.                                                                                          | 2-51             |

|              | "128-Bit AES Decryption" section was updated to include M7 device information.                                                | 2-53             |

|              | Table 3-6 was updated.                                                                                                        | 3-6              |

|              | Table 3-7 was updated.                                                                                                        | 3-6              |

|              | In Table 3-11, PAC4 was updated.                                                                                              | 3-93-8           |

|              | Table 3-20 was updated.                                                                                                       | 3-20             |

|              | The note in Table 3-32 was updated.                                                                                           | 3-27             |

|              | All Timing Characteristics tables were updated from LVTTL to Register Delays                                                  | 3-31 to 3-<br>73 |

|              | The Timing Characteristics for RAM4K9, RAM512X18, and FIFO were updated.                                                      | 3-85 to<br>3-90  |

|              | F <sub>TCKMAX</sub> was updated in Table 3-110.                                                                               | 3-97             |

| Advance v0.2 | Figure 2-11 was updated.                                                                                                      | 2-9              |

|              | The "Clock Resources (VersaNets)" section was updated.                                                                        | 2-9              |

|              | The "VersaNet Global Networks and Spine Access" section was updated.                                                          | 2-9              |

|              | The "PLL Macro" section was updated.                                                                                          | 2-15             |

|              | Figure 2-27 was updated.                                                                                                      | 2-28             |

|              | Figure 2-20 was updated.                                                                                                      | 2-19             |

|              | Table 2-5 was updated.                                                                                                        | 2-25             |

|              | Table 2-6 was updated.                                                                                                        | 2-25             |

|              | The "FIFO Flag Usage Considerations" section was updated.                                                                     | 2-27             |

|              | Table 2-13 was updated.                                                                                                       | 2-30             |

|              | Figure 2-24 was updated.                                                                                                      | 2-31             |

|              | The "Cold-Sparing Support" section is new.                                                                                    | 2-34             |

| Revision      | Changes                                                   | Page      |

|---------------|-----------------------------------------------------------|-----------|

| Advance v0.2, | Table 2-43 was updated.                                   | 2-64      |

| (continued)   | Table 2-18 was updated.                                   | 2-45      |

|               | Pin descriptions in the "JTAG Pins" section were updated. | 2-51      |

|               | The "User I/O Naming Convention" section was updated.     | 2-48      |

|               | Table 3-7 was updated.                                    | 3-6       |

|               | The "Methodology" section was updated.                    | 3-10      |

|               | Table 3-40 and Table 3-39 were updated.                   | 3-33,3-32 |

|               | The A3P250 "100-Pin VQFP*" pin table was updated.         | 4-14      |

|               | The A3P250 "208-Pin PQFP*" pin table was updated.         | 4-23      |

|               | The A3P1000 "208-Pin PQFP*" pin table was updated.        | 4-29      |

|               | The A3P250 "144-Pin FBGA*" pin table was updated.         | 4-36      |

|               | The A3P1000 "144-Pin FBGA*" pin table was updated.        | 4-32      |

|               | The A3P250 "256-Pin FBGA*" pin table was updated.         | 4-45      |

|               | The A3P1000 "256-Pin FBGA*" pin table was updated.        | 4-54      |

|               | The A3P1000 "484-Pin FBGA*" pin table was updated.        | 4-68      |

## **Datasheet Categories**

#### Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "ProASIC3 Device Status" table on page IV, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

#### **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

#### Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

#### Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

#### Unmarked (production)

This version contains information that is considered to be final.

## **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

## Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.