# E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| 2014.10                        |                                                                         |

|--------------------------------|-------------------------------------------------------------------------|

| Product Status                 | Active                                                                  |

| Number of LABs/CLBs            | -                                                                       |

| Number of Logic Elements/Cells | ·                                                                       |

| Total RAM Bits                 | 147456                                                                  |

| Number of I/O                  | 97                                                                      |

| Number of Gates                | 1000000                                                                 |

| Voltage - Supply               | 1.425V ~ 1.575V                                                         |

| Mounting Type                  | Surface Mount                                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                         |

| Package / Case                 | 144-LBGA                                                                |

| Supplier Device Package        | 144-FPBGA (13x13)                                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p1000-fg144 |

|                                |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

0-I/O is set to drive out logic Low

Last Known State – I/O is set to the last value that was driven out prior to entering the programming mode, and then held at that value during programming

Z -Tristate: I/O is tristated

| om file Save to file |                       |            | Show BSR De             |

|----------------------|-----------------------|------------|-------------------------|

| Port Name            | Macro Cell            | Pin Number | 1/O State (Output Only) |

| BIST                 | ADLIB:INBUF           | T2         | 1                       |

| BYPASS_IO            | ADLIB:INBUF           | K1         | 1                       |

| CLK                  | ADLIB:INBUF           | B1         | 1                       |

| ENOUT                | ADLIB:INBUF           | J16        | 1                       |

| LED                  | ADLIB:OUTBUF          | M3         | 0                       |

| MONITOR[0]           | ADLIB:OUTBUF          | B5         | 0                       |

| MONITOR[1]           | ADLIB:OUTBUF          | C7         | Z                       |

| MONITOR[2]           | ADLIB:OUTBUF          | D9         | Z                       |

| MONITOR[3]           | ADLIB:OUTBUF          | D7         | Z                       |

| MONITOR[4]           | ADLIB:OUTBUF          | A11        | Z                       |

| OEa                  | ADLIB:INBUF           | E4         | Z                       |

| ОЕЬ                  | ADLIB:INBUF           | F1         | Z                       |

| OSC_EN               | ADLIB:INBUF           | К3         | Z                       |

| PAD(10)              | ADLIB:BIBUF_LVCMOS33U | M8         | Z                       |

| PAD[11]              | ADLIB:BIBUF_LVCMOS33D | R7         | Z                       |

| PAD[12]              | ADLIB:BIBUF_LVCMOS33U | D11        | Z                       |

| PAD[13]              | ADLIB:BIBUF_LVCMOS33D | C12        | Z                       |

| PAD[14]              | ADLIB:BIBUF_LVCMOS33U | R6         | Z                       |

|                      |                       |            |                         |

#### Figure 1-4 • I/O States During Programming Window

- 6. Click OK to return to the FlashPoint Programming File Generator window.

- Note: I/O States During programming are saved to the ADB and resulting programming files after completing programming file generation.

## **User I/O Characteristics**

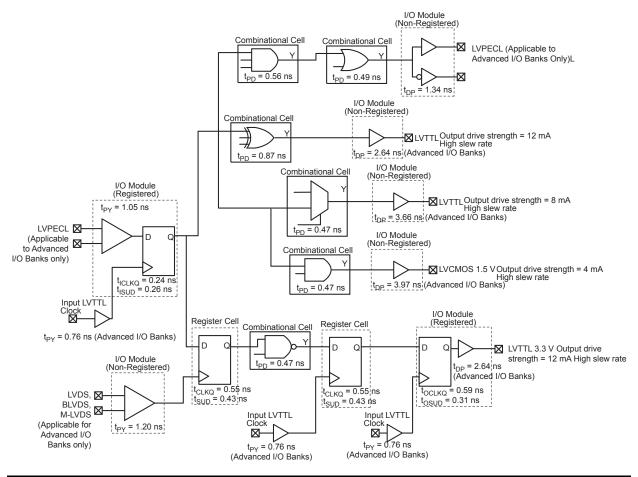

### **Timing Model**

### **Overview of I/O Performance**

### Summary of I/O DC Input and Output Levels – Default I/O Software Settings

#### Table 2-18 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings Applicable to Advanced I/O Banks

|                                            |                   | Equiv.                                                          |      |          | VIL         | VIH            |          | VOL         | VOH         |                        |                        |

|--------------------------------------------|-------------------|-----------------------------------------------------------------|------|----------|-------------|----------------|----------|-------------|-------------|------------------------|------------------------|

| I/O Standard                               | Drive<br>Strength | Software<br>Default<br>Drive<br>Strength<br>Option <sup>2</sup> |      | Min<br>V | Max<br>V    | Min<br>V       | Max<br>V | Max<br>V    | Min<br>V    | IOL <sup>1</sup><br>mA | IOH <sup>1</sup><br>mA |

| 3.3 V LVTTL /<br>3.3 V<br>LVCMOS           | 12 mA             | 12 mA                                                           | High | -0.3     | 0.8         | 2              | 3.6      | 0.4         | 2.4         | 12                     | 12                     |

| 3.3 V<br>LVCMOS<br>Wide Range <sup>3</sup> | 100 µA            | 12 mA                                                           | High | -0.3     | 0.8         | 2              | 3.6      | 0.2         | VCCI – 0.2  | 0.1                    | 0.1                    |

| 2.5 V<br>LVCMOS                            | 12 mA             | 12 mA                                                           | High | -0.3     | 0.7         | 1.7            | 2.7      | 0.7         | 1.7         | 12                     | 12                     |

| 1.8 V<br>LVCMOS                            | 12 mA             | 12 mA                                                           | High | -0.3     | 0.35 * VCCI | 0.65 * VCCI    | 1.9      | 0.45        | VCCI – 0.45 | 12                     | 12                     |

| 1.5 V<br>LVCMOS                            | 12 mA             | 12 mA                                                           | High | -0.3     | 0.35 * VCCI | 0.65 * VCCI    | 1.6      | 0.25 * VCCI | 0.75 * VCCI | 12                     | 12                     |

| 3.3 V PCI                                  |                   |                                                                 |      |          | Per F       | PCI specificat | ions     |             |             |                        |                        |

| 3.3 V PCI-X                                |                   | Per PCI-X specifications                                        |      |          |             |                |          |             |             |                        |                        |

Notes:

1. Currents are measured at 85°C junction temperature.

2. 3.3 V LVCMOS wide range is applicable to 100 μA drive strength only. The configuration will NOT operate at the equivalent software default drive strength. These values are for Normal Ranges ONLY.

3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

#### Table 2-20 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings Applicable to Standard I/O Banks

|                                            |                   | Equiv.                                                          |      |          | VIL         | VIH         |          | VOL         | VOH         |                        |                        |

|--------------------------------------------|-------------------|-----------------------------------------------------------------|------|----------|-------------|-------------|----------|-------------|-------------|------------------------|------------------------|

| I/O Standard                               | Drive<br>Strength | Software<br>Default<br>Drive<br>Strength<br>Option <sup>2</sup> | Slew | Min<br>V | Max<br>V    | Min<br>V    | Max<br>V | Max<br>V    | Min<br>V    | IOL <sup>1</sup><br>mA | IOH <sup>1</sup><br>mA |

| 3.3 V LVTTL /<br>3.3 V<br>LVCMOS           | 8 mA              | 8 mA                                                            | High | -0.3     | 0.8         | 2           | 3.6      | 0.4         | 2.4         | 8                      | 8                      |

| 3.3 V<br>LVCMOS<br>Wide Range <sup>3</sup> | 100 µA            | 8 mA                                                            | High | -0.3     | 0.8         | 2           | 3.6      | 0.2         | VCCI – 0.2  | 0.1                    | 0.1                    |

| 2.5 V<br>LVCMOS                            | 8 mA              | 8 mA                                                            | High | -0.3     | 0.7         | 1.7         | 2.7      | 0.7         | 1.7         | 8                      | 8                      |

| 1.8 V<br>LVCMOS                            | 4 mA              | 4 mA                                                            | High | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45        | VCCI – 0.45 | 4                      | 4                      |

| 1.5 V<br>LVCMOS                            | 2 mA              | 2 mA                                                            | High | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.25 * VCCI | 0.75 * VCCI | 2                      | 2                      |

Notes:

1. Currents are measured at 85°C junction temperature.

2. 3.3 V LVCMOS wide range is applicable to 100 μA drive strength only. The configuration will NOT operate at the equivalent software default drive strength. These values are for Normal Ranges ONLY.

3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

## Table 2-21 • Summary of Maximum and Minimum DC Input Levels Applicable to Commercial and Industrial Conditions

|                            | Comr             | nercial <sup>1</sup> | Indus            | strial <sup>2</sup> |

|----------------------------|------------------|----------------------|------------------|---------------------|

|                            | IIL <sup>3</sup> | IIH <sup>4</sup>     | IIL <sup>3</sup> | IIH <sup>4</sup>    |

| DC I/O Standards           | μΑ               | μA                   | μA               | μA                  |

| 3.3 V LVTTL / 3.3 V LVCMOS | 10               | 10                   | 15               | 15                  |

| 3.3 V LVCMOS Wide Range    | 10               | 10                   | 15               | 15                  |

| 2.5 V LVCMOS               | 10               | 10                   | 15               | 15                  |

| 1.8 V LVCMOS               | 10               | 10                   | 15               | 15                  |

| 1.5 V LVCMOS               | 10               | 10                   | 15               | 15                  |

| 3.3 V PCI                  | 10               | 10                   | 15               | 15                  |

| 3.3 V PCI-X                | 10               | 10                   | 15               | 15                  |

Notes:

1. Commercial range ( $0^{\circ}C < T_A < 70^{\circ}C$ )

2. Industrial range  $(-40^{\circ}C < T_A < 85^{\circ}C)$

- 3. IIL is the input leakage current per I/O pin over recommended operation conditions where  $-0.3V < V_{IN} < V_{IL}$ .

- 4. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

| Table 2-39 • Min                     | imum an  | nd Maxim | um DC I  | nput and   | Output L | evels    |     |    |                        |                        |                  |                 |

|--------------------------------------|----------|----------|----------|------------|----------|----------|-----|----|------------------------|------------------------|------------------|-----------------|

| App<br>3.3 V LVTTL /<br>3.3 V LVCMOS |          | o Standa |          | anks<br>IH | VOL      | VOH      | IOL | ЮН | IOSL                   | IOSH                   | IIL <sup>1</sup> |                 |

| Drive Strength                       | Min<br>V | Max<br>V | Min<br>V | Max<br>V   | Max<br>V | Min<br>V | mA  | mA | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup> |

| 2 mA                                 | -0.3     | 0.8      | 2        | 3.6        | 0.4      | 2.4      | 2   | 2  | 25                     | 27                     | 10               | 10              |

| 4 mA                                 | -0.3     | 0.8      | 2        | 3.6        | 0.4      | 2.4      | 4   | 4  | 25                     | 27                     | 10               | 10              |

| 6 mA                                 | -0.3     | 0.8      | 2        | 3.6        | 0.4      | 2.4      | 6   | 6  | 51                     | 54                     | 10               | 10              |

| 8 mA                                 | -0.3     | 0.8      | 2        | 3.6        | 0.4      | 2.4      | 8   | 8  | 51                     | 54                     | 10               | 10              |

Vlicrose

Power Matters.

## T

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. I<sub>IH</sub> is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at 100°C junction temperature and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

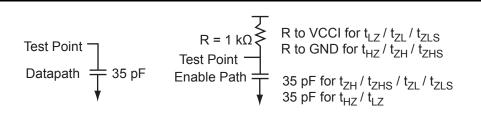

#### Figure 2-7 • AC Loading

#### Table 2-40 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 3.3            | 1.4                  | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-22 on page 2-22 for a complete table of trip points.

#### **Timing Characteristics**

#### Table 2-70 • 1.8 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/O Banks

| Drive    | Speed |                   |                 |                  |                 |                   |                 |                 |                 |                 |                  |                  |       |

|----------|-------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Strength | Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 2 mA     | Std.  | 0.66              | 11.86           | 0.04             | 1.22            | 0.43              | 9.14            | 11.86           | 2.77            | 1.66            | 11.37            | 14.10            | ns    |

|          | -1    | 0.56              | 10.09           | 0.04             | 1.04            | 0.36              | 7.77            | 10.09           | 2.36            | 1.41            | 9.67             | 11.99            | ns    |

|          | -2    | 0.49              | 8.86            | 0.03             | 0.91            | 0.32              | 6.82            | 8.86            | 2.07            | 1.24            | 8.49             | 10.53            | ns    |

| 4 mA     | Std.  | 0.66              | 6.91            | 0.04             | 1.22            | 0.43              | 5.86            | 6.91            | 3.22            | 2.84            | 8.10             | 9.15             | ns    |

|          | -1    | 0.56              | 5.88            | 0.04             | 1.04            | 0.36              | 4.99            | 5.88            | 2.74            | 2.41            | 6.89             | 7.78             | ns    |

|          | -2    | 0.49              | 5.16            | 0.03             | 0.91            | 0.32              | 4.38            | 5.16            | 2.41            | 2.12            | 6.05             | 6.83             | ns    |

| 6 mA     | Std.  | 0.66              | 4.45            | 0.04             | 1.22            | 0.43              | 4.18            | 4.45            | 3.53            | 3.38            | 6.42             | 6.68             | ns    |

|          | -1    | 0.56              | 3.78            | 0.04             | 1.04            | 0.36              | 3.56            | 3.78            | 3.00            | 2.88            | 5.46             | 5.69             | ns    |

|          | -2    | 0.49              | 3.32            | 0.03             | 0.91            | 0.32              | 3.12            | 3.32            | 2.64            | 2.53            | 4.79             | 4.99             | ns    |

| 8 mA     | Std.  | 0.66              | 3.92            | 0.04             | 1.22            | 0.43              | 3.93            | 3.92            | 3.60            | 3.52            | 6.16             | 6.16             | ns    |

|          | -1    | 0.56              | 3.34            | 0.04             | 1.04            | 0.36              | 3.34            | 3.34            | 3.06            | 3.00            | 5.24             | 5.24             | ns    |

|          | -2    | 0.49              | 2.93            | 0.03             | 0.91            | 0.32              | 2.93            | 2.93            | 2.69            | 2.63            | 4.60             | 4.60             | ns    |

| 12 mA    | Std.  | 0.66              | 3.53            | 0.04             | 1.22            | 0.43              | 3.60            | 3.04            | 3.70            | 4.08            | 5.84             | 5.28             | ns    |

|          | -1    | 0.56              | 3.01            | 0.04             | 1.04            | 0.36              | 3.06            | 2.59            | 3.15            | 3.47            | 4.96             | 4.49             | ns    |

|          | -2    | 0.49              | 2.64            | 0.03             | 0.91            | 0.32              | 2.69            | 2.27            | 2.76            | 3.05            | 4.36             | 3.94             | ns    |

| 16 mA    | Std.  | 0.66              | 3.53            | 0.04             | 1.22            | 0.43              | 3.60            | 3.04            | 3.70            | 4.08            | 5.84             | 5.28             | ns    |

|          | -1    | 0.56              | 3.01            | 0.04             | 1.04            | 0.36              | 3.06            | 2.59            | 3.15            | 3.47            | 4.96             | 4.49             | ns    |

|          | -2    | 0.49              | 2.64            | 0.03             | 0.91            | 0.32              | 2.69            | 2.27            | 2.76            | 3.05            | 4.36             | 3.94             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-81 • 1.5 V LVCMOS Low Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Advanced I/O Banks

|                   | ••             |                   |                 |                  |                 |                   |                 |                 |                 |                 |                  |                  |       |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 2 mA              | Std.           | 0.66              | 12.78           | 0.04             | 1.44            | 0.43              | 12.81           | 12.78           | 3.40            | 2.64            | 15.05            | 15.02            | ns    |

|                   | -1             | 0.56              | 10.87           | 0.04             | 1.22            | 0.36              | 10.90           | 10.87           | 2.89            | 2.25            | 12.80            | 12.78            | ns    |

|                   | -2             | 0.49              | 9.55            | 0.03             | 1.07            | 0.32              | 9.57            | 9.55            | 2.54            | 1.97            | 11.24            | 11.22            | ns    |

| 4 mA              | Std.           | 0.66              | 10.01           | 0.04             | 1.44            | 0.43              | 10.19           | 9.55            | 3.75            | 3.27            | 12.43            | 11.78            | ns    |

|                   | -1             | 0.56              | 8.51            | 0.04             | 1.22            | 0.36              | 8.67            | 8.12            | 3.19            | 2.78            | 10.57            | 10.02            | ns    |

|                   | -2             | 0.49              | 7.47            | 0.03             | 1.07            | 0.32              | 7.61            | 7.13            | 2.80            | 2.44            | 9.28             | 8.80             | ns    |

| 6 mA              | Std.           | 0.66              | 9.33            | 0.04             | 1.44            | 0.43              | 9.51            | 8.89            | 3.83            | 3.43            | 11.74            | 11.13            | ns    |

|                   | -1             | 0.56              | 7.94            | 0.04             | 1.22            | 0.36              | 8.09            | 7.56            | 3.26            | 2.92            | 9.99             | 9.47             | ns    |

|                   | -2             | 0.49              | 6.97            | 0.03             | 1.07            | 0.32              | 7.10            | 6.64            | 2.86            | 2.56            | 8.77             | 8.31             | ns    |

| 8 mA              | Std.           | 0.66              | 8.91            | 0.04             | 1.44            | 0.43              | 9.07            | 8.89            | 3.95            | 4.05            | 11.31            | 11.13            | ns    |

|                   | -1             | 0.56              | 7.58            | 0.04             | 1.22            | 0.36              | 7.72            | 7.57            | 3.36            | 3.44            | 9.62             | 9.47             | ns    |

|                   | -2             | 0.49              | 6.65            | 0.03             | 1.07            | 0.32              | 6.78            | 6.64            | 2.95            | 3.02            | 8.45             | 8.31             | ns    |

| 12 mA             | Std.           | 0.66              | 8.91            | 0.04             | 1.44            | 0.43              | 9.07            | 8.89            | 3.95            | 4.05            | 11.31            | 11.13            | ns    |

|                   | -1             | 0.56              | 7.58            | 0.04             | 1.22            | 0.36              | 7.72            | 7.57            | 3.36            | 3.44            | 9.62             | 9.47             | ns    |

|                   | -2             | 0.49              | 6.65            | 0.03             | 1.07            | 0.32              | 6.78            | 6.64            | 2.95            | 3.02            | 8.45             | 8.31             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-82 • 1.5 V LVCMOS High Slew

| Commercial-Case Conditions: T   | J = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V |

|---------------------------------|-------------------------------------------------------------|

| Applicable to Standard Plus I/O | Banks                                                       |

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 7.83            | 0.04             | 1.42            | 0.43              | 6.42            | 7.83            | 2.71            | 2.55            | 8.65             | 10.07            | ns    |

|                   | -1             | 0.56              | 6.66            | 0.04             | 1.21            | 0.36              | 5.46            | 6.66            | 2.31            | 2.17            | 7.36             | 8.56             | ns    |

|                   | -2             | 0.49              | 5.85            | 0.03             | 1.06            | 0.32              | 4.79            | 5.85            | 2.02            | 1.90            | 6.46             | 7.52             | ns    |

| 4 mA              | Std.           | 0.66              | 4.84            | 0.04             | 1.42            | 0.43              | 4.49            | 4.84            | 3.03            | 3.13            | 6.72             | 7.08             | ns    |

|                   | -1             | 0.56              | 4.12            | 0.04             | 1.21            | 0.36              | 3.82            | 4.12            | 2.58            | 2.66            | 5.72             | 6.02             | ns    |

|                   | -2             | 0.49              | 3.61            | 0.03             | 1.06            | 0.32              | 3.35            | 3.61            | 2.26            | 2.34            | 5.02             | 5.28             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

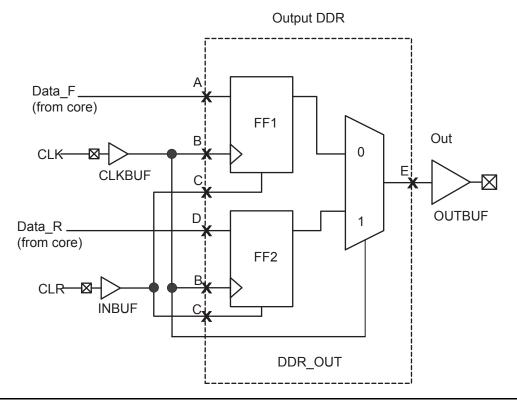

### **Output DDR Module**

### Figure 2-22 • Output DDR Timing Model

#### Table 2-103 • Parameter Definitions

| Parameter Name          | Parameter Definition      | Measuring Nodes (from, to) |

|-------------------------|---------------------------|----------------------------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out              | B, E                       |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out | C, E                       |

| t <sub>DDROREMCLR</sub> | Clear Removal             | С, В                       |

| t <sub>DDRORECCLR</sub> | Clear Recovery            | С, В                       |

| t <sub>DDROSUD1</sub>   | Data Setup Data_F         | А, В                       |

| t <sub>DDROSUD2</sub>   | Data Setup Data_R         | D, B                       |

| t <sub>DDROHD1</sub>    | Data Hold Data_F          | А, В                       |

| t <sub>DDROHD2</sub>    | Data Hold Data_R          | D, B                       |

## **Clock Conditioning Circuits**

### **CCC Electrical Specifications**

#### **Timing Characteristics**

#### Table 2-115 • ProASIC3 CCC/PLL Specification

| Parameter                                                          | Minimum                     | Typical          | Maximum                      | Units |

|--------------------------------------------------------------------|-----------------------------|------------------|------------------------------|-------|

| Clock Conditioning Circuitry Input Frequency fIN_CCC               | 1.5                         |                  | 350                          | MHz   |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT CCC</sub> | 0.75                        |                  | 350                          | MHz   |

| Serial Clock (SCLK) for Dynamic PLL <sup>1</sup>                   |                             |                  | 125                          | MHz   |

| Delay Increments in Programmable Delay Blocks <sup>2, 3</sup>      |                             | 200 <sup>4</sup> |                              | ps    |

| Number of Programmable Values in Each Programmable<br>Delay Block  |                             |                  | 32                           |       |

| Input Period Jitter                                                |                             |                  | 1.5                          | ns    |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub>         | N                           | lax Peak-to-F    | Peak Period Jitt             | er    |

|                                                                    | 1 Global<br>Network<br>Used |                  | 3 Global<br>Networks<br>Used |       |

| 0.75 MHz to 24 MHz                                                 | 0.50%                       |                  | 0.70%                        |       |

| 24 MHz to 100 MHz                                                  | 1.00%                       |                  | 1.20%                        |       |

| 100 MHz to 250 MHz                                                 | 1.75%                       |                  | 2.00%                        |       |

| 250 MHz to 350 MHz                                                 | 2.50%                       |                  | 5.60%                        |       |

| Acquisition Time                                                   |                             |                  |                              |       |

| (A3P250 and A3P1000 only) LockControl = 0                          |                             |                  | 300                          | μs    |

| LockControl = 1                                                    |                             |                  | 300                          | μs    |

| (all other dies) LockControl = 0                                   |                             |                  | 300                          | μs    |

| LockControl = 1                                                    |                             |                  | 6.0                          | ms    |

| Tracking Jitter <sup>5</sup>                                       |                             |                  |                              |       |

| (A3P250 and A3P1000 only) LockControl = 0                          |                             |                  | 1.6                          | ns    |

| LockControl = 1                                                    |                             |                  | 1.6                          | ns    |

| (all other dies) LockControl = 0                                   |                             |                  | 1.6                          | ns    |

| LockControl = 1                                                    |                             |                  | 0.8                          | ns    |

| Output Duty Cycle                                                  | 48.5                        |                  | 51.5                         | %     |

| Delay Range in Block: Programmable Delay 1 <sup>2, 3</sup>         | 0.6                         |                  | 5.56                         | ns    |

| Delay Range in Block: Programmable Delay 2 <sup>2, 3</sup>         | 0.225                       |                  | 5.56                         | ns    |

| Delay Range in Block: Fixed Delay <sup>2, 3</sup>                  |                             | 2.2              |                              | ns    |

Notes:

1. Maximum value obtained for a -2 speed-grade device in worst-case commercial conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2. This delay is a function of voltage and temperature. See Table 2-6 on page 2-6 for deratings.

3.  $T_J = 25^{\circ}C$ , VCC = 1.5 V

- 4. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help for more information.

- 5. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to the PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by the period jitter parameter.

6. The A3P030 device does not contain a PLL.

#### Table 2-120 • A3P250 FIFO 512×8

### Worst Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

| Parameter            | Description                                       | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 3.75 | 4.27 | 5.02 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.22 | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.17 | 2.47 | 2.90 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.94 | 1.07 | 1.26 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96 | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86 | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05 | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93 | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.13 | 6.98 | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.92 | 1.05 | 1.23 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272  | 231  | MHz   |

#### Table 2-121 • A3P250 FIFO 1k×4 Worst Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

| Parameter            | Description                                       | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 4.05 | 4.61 | 5.42 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.22 | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.36 | 2.68 | 3.15 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.89 | 1.02 | 1.20 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96 | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86 | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05 | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93 | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.13 | 6.98 | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.92 | 1.05 | 1.23 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272  | 231  | MHz   |

## 3 – Pin Descriptions

## **Supply Pins**

#### Ground

Ground supply voltage to the core, I/O outputs, and I/O logic.

#### GNDQ Ground (quiet)

Quiet ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ must always be connected to GND on the board.

#### VCC

GND

#### Core Supply Voltage

Supply voltage to the FPGA core, nominally 1.5 V. VCC is required for powering the JTAG state machine in addition to VJTAG. Even when a device is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the device.

#### VCCIBx I/O Supply Voltage

Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number. There are up to eight I/O banks on low power flash devices plus a dedicated VJTAG bank. Each bank can have a separate VCCI connection. All I/Os in a bank will run off the same VCCIBx supply. VCCI can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. In general, unused I/O banks should have their corresponding VCCIX pins tied to GND. If an output pad is terminated to ground through any resistor and if the corresponding VCCIX is left floating, then the leakage current to ground is ~ 0uA. However, if an output pad is terminated to ground is ~ 3 uA. For unused banks the aforementioned behavior is to be taken into account while deciding if it's better to float VCCIX of unused bank or tie it to GND.

#### VMVx I/O Supply Voltage (quiet)

Quiet supply voltage to the input buffers of each I/O bank. *x* is the bank number. Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks. This minimizes the noise transfer within the package and improves input signal integrity. Each bank must have at least one VMV connection, and no VMV should be left unconnected. All I/Os in a bank run off the same VMVx supply. VMV is used to provide a quiet supply voltage to the input buffers of each I/O bank. VMVx can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VMV pins tied to GND. VMV and VCCI should be at the same voltage within a given I/O bank. Used VMV pins must be connected to the corresponding VCCI pins of the same bank (i.e., VMV0 to VCCIB0, VMV1 to VCCIB1, etc.).

#### VCCPLA/B/C/D/E/F PLL Supply Voltage

Supply voltage to analog PLL, nominally 1.5 V.

When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground. Microsemi recommends tying VCCPLx to VCC and using proper filtering circuits to decouple VCC noise from the PLLs. Refer to the PLL Power Supply Decoupling section of the "Clock Conditioning Circuits in IGLOO and ProASIC3 Devices" chapter of the *ProASIC3 FPGA Fabric User's Guide* for a complete board solution for the PLL analog power supply and ground.

There is one VCCPLF pin on ProASIC3 devices.

#### VCOMPLA/B/C/D/E/F PLL Ground

Ground to analog PLL power supplies. When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground.

There is one VCOMPLF pin on ProASIC3 devices.

mode is not used in the design, the FF pin is available as a regular I/O. For IGLOOe, ProASIC3EL, and RT ProASIC3 only, the FF pin can be configured as a Schmitt trigger input.

When Flash\*Freeze mode is used, the FF pin must not be left floating to avoid accidentally entering Flash\*Freeze mode. While in Flash\*Freeze mode, the Flash\*Freeze pin should be constantly asserted.

The Flash\*Freeze pin can be used with any single-ended I/O standard supported by the I/O bank in which the pin is located, and input signal levels compatible with the I/O standard selected. The FF pin should be treated as a sensitive asynchronous signal. When defining pin placement and board layout, simultaneously switching outputs (SSOs) and their effects on sensitive asynchronous pins must be considered.

Unused FF or I/O pins are tristated with weak pull-up. This default configuration applies to both Flash\*Freeze mode and normal operation mode. No user intervention is required.

## JTAG Pins

Low power flash devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). VCC must also be powered for the JTAG state machine to operate, even if the device is in bypass mode; VJTAG alone is insufficient. Both VJTAG and VCC to the part must be supplied to allow JTAG signals to transition the device. Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned for use, the VJTAG pin together with the TRST pin could be tied to GND.

#### TCK Test Clock

Test clock input for JTAG boundary scan, ISP, and UJTAG. The TCK pin does not have an internal pull-up/-down resistor. If JTAG is not used, Microsemi recommends tying off TCK to GND through a resistor placed close to the FPGA pin. This prevents JTAG operation in case TMS enters an undesired state.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements. Refer to Table 1 for more information.

| VJTAG | Tie-Off Resistance |

|-------|--------------------|

| 3.3 V | 200 Ω –1 kΩ        |

| 2.5 V | 200 Ω –1 kΩ        |

| 1.8 V | 500 Ω –1 kΩ        |

| 1.5 V | 500 Ω –1 kΩ        |

#### Table 1 • Recommended Tie-Off Values for the TCK and TRST Pins

#### Notes:

- 1. Equivalent parallel resistance if more than one device is on the JTAG chain

- 2. The TCK pin can be pulled up/down.

- 3. The TRST pin is pulled down.

#### TDI Test Data Input

Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.

#### TDO Test Data Output

Serial output for JTAG boundary scan, ISP, and UJTAG usage.

#### TMS Test Mode Select

The TMS pin controls the use of the IEEE 1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

#### TRST Boundary Scan Reset Pin

The TRST pin functions as an active low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the test access port (TAP) is held in reset mode. The resistor values must be chosen from Table 1 and must satisfy the parallel resistance value requirement. The values in Table 1 correspond to the resistor recommended when a single device is used, and the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

| <u>۱</u>   | VQ100           |            | /Q100           | VQ100      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P030 Function | Pin Number | A3P030 Function | Pin Number | A3P030 Function |

| 1          | GND             | 37         | VCC             | 73         | IO27RSB0        |

| 2          | IO82RSB1        | 38         | GND             | 74         | IO26RSB0        |

| 3          | IO81RSB1        | 39         | VCCIB1          | 75         | IO25RSB0        |

| 4          | IO80RSB1        | 40         | IO49RSB1        | 76         | IO24RSB0        |

| 5          | IO79RSB1        | 41         | IO47RSB1        | 77         | IO23RSB0        |

| 6          | IO78RSB1        | 42         | IO46RSB1        | 78         | IO22RSB0        |

| 7          | IO77RSB1        | 43         | IO45RSB1        | 79         | IO21RSB0        |

| 8          | IO76RSB1        | 44         | IO44RSB1        | 80         | IO20RSB0        |

| 9          | GND             | 45         | IO43RSB1        | 81         | IO19RSB0        |

| 10         | IO75RSB1        | 46         | IO42RSB1        | 82         | IO18RSB0        |

| 11         | IO74RSB1        | 47         | ТСК             | 83         | IO17RSB0        |

| 12         | GEC0/IO73RSB1   | 48         | TDI             | 84         | IO16RSB0        |

| 13         | GEA0/IO72RSB1   | 49         | TMS             | 85         | IO15RSB0        |

| 14         | GEB0/IO71RSB1   | 50         | NC              | 86         | IO14RSB0        |

| 15         | IO70RSB1        | 51         | GND             | 87         | VCCIB0          |

| 16         | IO69RSB1        | 52         | VPUMP           | 88         | GND             |

| 17         | VCC             | 53         | NC              | 89         | VCC             |

| 18         | VCCIB1          | 54         | TDO             | 90         | IO12RSB0        |

| 19         | IO68RSB1        | 55         | TRST            | 91         | IO10RSB0        |

| 20         | IO67RSB1        | 56         | VJTAG           | 92         | IO08RSB0        |

| 21         | IO66RSB1        | 57         | IO41RSB0        | 93         | IO07RSB0        |

| 22         | IO65RSB1        | 58         | IO40RSB0        | 94         | IO06RSB0        |

| 23         | IO64RSB1        | 59         | IO39RSB0        | 95         | IO05RSB0        |

| 24         | IO63RSB1        | 60         | IO38RSB0        | 96         | IO04RSB0        |

| 25         | IO62RSB1        | 61         | IO37RSB0        | 97         | IO03RSB0        |

| 26         | IO61RSB1        | 62         | IO36RSB0        | 98         | IO02RSB0        |

| 27         | IO60RSB1        | 63         | GDB0/IO34RSB0   | 99         | IO01RSB0        |

| 28         | IO59RSB1        | 64         | GDA0/IO33RSB0   | 100        | IO00RSB0        |

| 29         | IO58RSB1        | 65         | GDC0/IO32RSB0   |            |                 |

| 30         | IO57RSB1        | 66         | VCCIB0          |            |                 |

| 31         | IO56RSB1        | 67         | GND             |            |                 |

| 32         | IO55RSB1        | 68         | VCC             |            |                 |

| 33         | IO54RSB1        | 69         | IO31RSB0        |            |                 |

| 34         | IO53RSB1        | 70         | IO30RSB0        |            |                 |

| 35         | IO52RSB1        | 71         | IO29RSB0        |            |                 |

| 36         | IO51RSB1        | 72         | IO28RSB0        |            |                 |

Package Pin Assignments

|            | VQ100           |            | VQ100           |            | VQ100           |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number | A3P250 Function |

| 1          | GND             | 37         | VCC             | 73         | GBA2/IO41PDB1   |

| 2          | GAA2/IO118UDB3  | 38         | GND             | 74         | VMV1            |

| 3          | IO118VDB3       | 39         | VCCIB2          | 75         | GNDQ            |

| 4          | GAB2/IO117UDB3  | 40         | IO77RSB2        | 76         | GBA1/IO40RSB0   |

| 5          | IO117VDB3       | 41         | IO74RSB2        | 77         | GBA0/IO39RSB0   |

| 6          | GAC2/IO116UDB3  | 42         | IO71RSB2        | 78         | GBB1/IO38RSB0   |

| 7          | IO116VDB3       | 43         | GDC2/IO63RSB2   | 79         | GBB0/IO37RSB0   |

| 8          | IO112PSB3       | 44         | GDB2/IO62RSB2   | 80         | GBC1/IO36RSB0   |

| 9          | GND             | 45         | GDA2/IO61RSB2   | 81         | GBC0/IO35RSB0   |

| 10         | GFB1/IO109PDB3  | 46         | GNDQ            | 82         | IO29RSB0        |

| 11         | GFB0/IO109NDB3  | 47         | ТСК             | 83         | IO27RSB0        |

| 12         | VCOMPLF         | 48         | TDI             | 84         | IO25RSB0        |

| 13         | GFA0/IO108NPB3  | 49         | TMS             | 85         | IO23RSB0        |

| 14         | VCCPLF          | 50         | VMV2            | 86         | IO21RSB0        |

| 15         | GFA1/IO108PPB3  | 51         | GND             | 87         | VCCIB0          |

| 16         | GFA2/IO107PSB3  | 52         | VPUMP           | 88         | GND             |

| 17         | VCC             | 53         | NC              | 89         | VCC             |

| 18         | VCCIB3          | 54         | TDO             | 90         | IO15RSB0        |

| 19         | GFC2/IO105PSB3  | 55         | TRST            | 91         | IO13RSB0        |

| 20         | GEC1/IO100PDB3  | 56         | VJTAG           | 92         | IO11RSB0        |

| 21         | GEC0/IO100NDB3  | 57         | GDA1/IO60USB1   | 93         | GAC1/IO05RSB0   |

| 22         | GEA1/IO98PDB3   | 58         | GDC0/IO58VDB1   | 94         | GAC0/IO04RSB0   |

| 23         | GEA0/IO98NDB3   | 59         | GDC1/IO58UDB1   | 95         | GAB1/IO03RSB0   |

| 24         | VMV3            | 60         | IO52NDB1        | 96         | GAB0/IO02RSB0   |

| 25         | GNDQ            | 61         | GCB2/IO52PDB1   | 97         | GAA1/IO01RSB0   |

| 26         | GEA2/IO97RSB2   | 62         | GCA1/IO50PDB1   | 98         | GAA0/IO00RSB0   |

| 27         | GEB2/IO96RSB2   | 63         | GCA0/IO50NDB1   | 99         | GNDQ            |

| 28         | GEC2/IO95RSB2   | 64         | GCC0/IO48NDB1   | 100        | VMV0            |

| 29         | IO93RSB2        | 65         | GCC1/IO48PDB1   |            |                 |

| 30         | IO92RSB2        | 66         | VCCIB1          |            |                 |

| 31         | IO91RSB2        | 67         | GND             |            |                 |

| 32         | IO90RSB2        | 68         | VCC             |            |                 |

| 33         | IO88RSB2        | 69         | IO43NDB1        |            |                 |

| 34         | IO86RSB2        | 70         | GBC2/IO43PDB1   |            |                 |

| 35         | IO85RSB2        | 71         | GBB2/IO42PSB1   |            |                 |

| 36         | IO84RSB2        | 72         | IO41NDB1        |            |                 |

## 🌜 Microsemi.

Package Pin Assignments

|            | FG256           |            | FG256           |            | FG256           |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number | A3P250 Function |

| G13        | GCC1/IO48PPB1   | K1         | GFC2/IO105PDB3  | M5         | VMV3            |

| G14        | IO47NPB1        | K2         | IO107NPB3       | M6         | VCCIB2          |

| G15        | IO54PDB1        | K3         | IO104PPB3       | M7         | VCCIB2          |

| G16        | IO54NDB1        | K4         | NC              | M8         | NC              |

| H1         | GFB0/IO109NPB3  | K5         | VCCIB3          | M9         | IO74RSB2        |

| H2         | GFA0/IO108NDB3  | K6         | VCC             | M10        | VCCIB2          |

| H3         | GFB1/IO109PPB3  | K7         | GND             | M11        | VCCIB2          |

| H4         | VCOMPLF         | K8         | GND             | M12        | VMV2            |

| H5         | GFC0/IO110NPB3  | K9         | GND             | M13        | NC              |

| H6         | VCC             | K10        | GND             | M14        | GDB1/IO59UPB1   |

| H7         | GND             | K11        | VCC             | M15        | GDC1/IO58UDB1   |

| H8         | GND             | K12        | VCCIB1          | M16        | IO56NDB1        |

| H9         | GND             | K13        | IO52NPB1        | N1         | IO103NDB3       |

| H10        | GND             | K14        | IO55RSB1        | N2         | IO101PPB3       |

| H11        | VCC             | K15        | IO53NPB1        | N3         | GEC1/IO100PPB3  |

| H12        | GCC0/IO48NPB1   | K16        | IO51NDB1        | N4         | NC              |

| H13        | GCB1/IO49PPB1   | L1         | IO105NDB3       | N5         | GNDQ            |

| H14        | GCA0/IO50NPB1   | L2         | IO104NPB3       | N6         | GEA2/IO97RSB2   |

| H15        | NC              | L3         | NC              | N7         | IO86RSB2        |

| H16        | GCB0/IO49NPB1   | L4         | IO102RSB3       | N8         | IO82RSB2        |

| J1         | GFA2/IO107PPB3  | L5         | VCCIB3          | N9         | IO75RSB2        |

| J2         | GFA1/IO108PDB3  | L6         | GND             | N10        | IO69RSB2        |

| J3         | VCCPLF          | L7         | VCC             | N11        | IO64RSB2        |

| J4         | IO106NDB3       | L8         | VCC             | N12        | GNDQ            |

| J5         | GFB2/IO106PDB3  | L9         | VCC             | N13        | NC              |

| J6         | VCC             | L10        | VCC             | N14        | VJTAG           |

| J7         | GND             | L11        | GND             | N15        | GDC0/IO58VDB1   |

| J8         | GND             | L12        | VCCIB1          | N16        | GDA1/IO60UDB1   |

| J9         | GND             | L13        | GDB0/IO59VPB1   | P1         | GEB1/IO99PDB3   |

| J10        | GND             | L14        | IO57VDB1        | P2         | GEB0/IO99NDB3   |

| J11        | VCC             | L15        | IO57UDB1        | P3         | NC              |

| J12        | GCB2/IO52PPB1   | L16        | IO56PDB1        | P4         | NC              |

| J13        | GCA1/IO50PPB1   | M1         | IO103PDB3       | P5         | IO92RSB2        |

| J14        | GCC2/IO53PPB1   | M2         | NC              | P6         | IO89RSB2        |

| J15        | NC              | M3         | IO101NPB3       | P7         | IO85RSB2        |

| J16        | GCA2/IO51PDB1   | M4         | GEC0/IO100NPB3  | P8         | IO81RSB2        |

|            | FG256           |            | FG256           |            | FG256           |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P600 Function | Pin Number | A3P600 Function | Pin Number | A3P600 Function |

| A1         | GND             | C5         | GAC0/IO04RSB0   | E9         | IO31RSB0        |

| A2         | GAA0/IO00RSB0   | C6         | GAC1/IO05RSB0   | E10        | VCCIB0          |

| A3         | GAA1/IO01RSB0   | C7         | IO20RSB0        | E11        | VCCIB0          |

| A4         | GAB0/IO02RSB0   | C8         | IO24RSB0        | E12        | VMV1            |

| A5         | IO11RSB0        | C9         | IO33RSB0        | E13        | GBC2/IO62PDB1   |

| A6         | IO16RSB0        | C10        | IO39RSB0        | E14        | IO67PPB1        |

| A7         | IO18RSB0        | C11        | IO44RSB0        | E15        | IO64PPB1        |

| A8         | IO28RSB0        | C12        | GBC0/IO54RSB0   | E16        | IO66PDB1        |

| A9         | IO34RSB0        | C13        | IO51RSB0        | F1         | IO166NDB3       |

| A10        | IO37RSB0        | C14        | VMV0            | F2         | IO168NPB3       |

| A11        | IO41RSB0        | C15        | IO61NPB1        | F3         | IO167PPB3       |

| A12        | IO43RSB0        | C16        | IO63PDB1        | F4         | IO169PDB3       |

| A13        | GBB1/IO57RSB0   | D1         | IO171NDB3       | F5         | VCCIB3          |

| A14        | GBA0/IO58RSB0   | D2         | IO171PDB3       | F6         | GND             |

| A15        | GBA1/IO59RSB0   | D3         | GAC2/IO172PDB3  | F7         | VCC             |

| A16        | GND             | D4         | IO06RSB0        | F8         | VCC             |

| B1         | GAB2/IO173PDB3  | D5         | GNDQ            | F9         | VCC             |

| B2         | GAA2/IO174PDB3  | D6         | IO10RSB0        | F10        | VCC             |

| B3         | GNDQ            | D7         | IO19RSB0        | F11        | GND             |

| B4         | GAB1/IO03RSB0   | D8         | IO26RSB0        | F12        | VCCIB1          |

| B5         | IO13RSB0        | D9         | IO30RSB0        | F13        | IO62NDB1        |

| B6         | IO14RSB0        | D10        | IO40RSB0        | F14        | IO64NPB1        |

| B7         | IO21RSB0        | D11        | IO45RSB0        | F15        | IO65PPB1        |

| B8         | IO27RSB0        | D12        | GNDQ            | F16        | IO66NDB1        |

| B9         | IO32RSB0        | D13        | IO50RSB0        | G1         | IO165NDB3       |

| B10        | IO38RSB0        | D14        | GBB2/IO61PPB1   | G2         | IO165PDB3       |

| B11        | IO42RSB0        | D15        | IO53RSB0        | G3         | IO168PPB3       |

| B12        | GBC1/IO55RSB0   | D16        | IO63NDB1        | G4         | GFC1/IO164PPB3  |

| B13        | GBB0/IO56RSB0   | E1         | IO166PDB3       | G5         | VCCIB3          |

| B14        | IO52RSB0        | E2         | IO167NPB3       | G6         | VCC             |

| B15        | GBA2/IO60PDB1   | E3         | IO172NDB3       | G7         | GND             |

| B16        | IO60NDB1        | E4         | IO169NDB3       | G8         | GND             |

| C1         | IO173NDB3       | E5         | VMV0            | G9         | GND             |

| C2         | IO174NDB3       | E6         | VCCIB0          | G10        | GND             |

| C3         | VMV3            | E7         | VCCIB0          | G11        | VCC             |

| C4         | IO07RSB0        | E8         | IO25RSB0        | G12        | VCCIB1          |

## 🌜 Microsemi.

Package Pin Assignments

|            | FG484           |            | FG484           |            | FG484           |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P400 Function | Pin Number | A3P400 Function | Pin Number | A3P400 Function |

| A1         | GND             | B15        | NC              | D7         | GAB0/IO02RSB0   |

| A2         | GND             | B16        | NC              | D8         | IO16RSB0        |

| A3         | VCCIB0          | B17        | NC              | D9         | IO17RSB0        |

| A4         | NC              | B18        | NC              | D10        | IO22RSB0        |

| A5         | NC              | B19        | NC              | D11        | IO28RSB0        |

| A6         | IO15RSB0        | B20        | NC              | D12        | IO34RSB0        |

| A7         | IO18RSB0        | B21        | VCCIB1          | D13        | IO37RSB0        |

| A8         | NC              | B22        | GND             | D14        | IO41RSB0        |

| A9         | NC              | C1         | VCCIB3          | D15        | IO43RSB0        |

| A10        | IO23RSB0        | C2         | NC              | D16        | GBB1/IO57RSB0   |

| A11        | IO29RSB0        | C3         | NC              | D17        | GBA0/IO58RSB0   |

| A12        | IO35RSB0        | C4         | NC              | D18        | GBA1/IO59RSB0   |

| A13        | IO36RSB0        | C5         | GND             | D19        | GND             |

| A14        | NC              | C6         | NC              | D20        | NC              |

| A15        | NC              | C7         | NC              | D21        | NC              |

| A16        | IO50RSB0        | C8         | VCC             | D22        | NC              |

| A17        | IO51RSB0        | C9         | VCC             | E1         | NC              |

| A18        | NC              | C10        | NC              | E2         | NC              |

| A19        | NC              | C11        | NC              | E3         | GND             |

| A20        | VCCIB0          | C12        | NC              | E4         | GAB2/IO154UDB3  |

| A21        | GND             | C13        | NC              | E5         | GAA2/IO155UDB3  |

| A22        | GND             | C14        | VCC             | E6         | IO12RSB0        |

| B1         | GND             | C15        | VCC             | E7         | GAB1/IO03RSB0   |

| B2         | VCCIB3          | C16        | NC              | E8         | IO13RSB0        |

| B3         | NC              | C17        | NC              | E9         | IO14RSB0        |

| B4         | NC              | C18        | GND             | E10        | IO21RSB0        |

| B5         | NC              | C19        | NC              | E11        | IO27RSB0        |

| B6         | NC              | C20        | NC              | E12        | IO32RSB0        |

| B7         | NC              | C21        | NC              | E13        | IO38RSB0        |

| B8         | NC              | C22        | VCCIB1          | E14        | IO42RSB0        |

| B9         | NC              | D1         | NC              | E15        | GBC1/IO55RSB0   |

| B10        | NC              | D2         | NC              | E16        | GBB0/IO56RSB0   |

| B11        | NC              | D3         | NC              | E17        | IO44RSB0        |

| B12        | NC              | D4         | GND             | E18        | GBA2/IO60PDB1   |

| B13        | NC              | D5         | GAA0/IO00RSB0   | E19        | IO60NDB1        |

| B14        | NC              | D6         | GAA1/IO01RSB0   | E20        | GND             |

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page       |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Revision 10<br>(September 2011) | The "In-System Programming (ISP) and Security" section and Security section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 32865).                                                                                                                                                                                                                    | I          |

|                                 | The value of 34 I/Os for the QN48 package in A3P030 was added to the "I/Os Per Package 1" section (SAR 33907).                                                                                                                                                                                                                                                                                                                                                                        |            |

|                                 | The Y security option and Licensed DPA Logo were added to the "ProASIC3<br>Ordering Information" section. The trademarked Licensed DPA Logo identifies<br>that a product is covered by a DPA counter-measures license from<br>Cryptography Research (SAR 32151).                                                                                                                                                                                                                      | IV         |

|                                 | The "Specifying I/O States During Programming" section is new (SAR 21281).                                                                                                                                                                                                                                                                                                                                                                                                            | 1-7        |

|                                 | In Table 2-2 • Recommended Operating Conditions 1, VPUMP programming voltage in programming mode was changed from "3.0 to 3.6" to "3.15 to 3.45" (SAR 30666). It was corrected in v2.0 of this datasheet in April 2007 but inadvertently changed back to "3.0 to 3.6 V" in v1.4 in August 2009. The following changes were made to Table 2-2 • Recommended Operating Conditions 1: VCCPLL analog power supply (PLL) was changed from "1.4 to 1.6" to "1.425 to 1.575" (SAR 33850).    | 2-2        |

|                                 | For VCCI and VMV, values for 3.3 V DC and 3.3 V DC Wide Range were corrected. The correct value for 3.3 V DC is "3.0 to 3.6 V" and the correct value for 3.3 V Wide Range is "2.7 to 3.6" (SAR 33848).                                                                                                                                                                                                                                                                                |            |

|                                 | Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings was update to restore values to the correct columns. Previously the Slew Rate column was missing and data were aligned incorrectly (SAR 34034).                                                                                                                                                                                                                                                          | 2-24       |

|                                 | The notes regarding drive strength in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section and "3.3 V LVCMOS Wide Range" section tables were revised for clarification. They now state that the minimum drive strength for the default software configuration when run in wide range is $\pm 100 \ \mu$ A. The drive strength displayed in software is supported in normal range only. For a detailed I/V curve, refer to the IBIS models (SAR 25700). | 2-22, 2-39 |

Datasheet Information

| Revision                   | Changes                                                                                                                                                                                                                                                       | Page                |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Revision 10<br>(continued) | "TBD" for 3.3 V LVCMOS Wide Range in Table 2-28 • I/O Output Buffer Maximum Resistances1 through Table 2-30 • I/O Output Buffer Maximum Resistances1 was replaced by "Same as regular 3.3 V" (SAR 33852).                                                     | 2-26 to 2-28        |

|                            | The equations in the notes for Table 2-31 • I/O Weak Pull-Up/Pull-Down Resistances were corrected (SAR 32470).                                                                                                                                                | 2-28                |

|                            | "TBD" for 3.3 V LVCMOS Wide Range in Table 2-32 • I/O Short Currents IOSH/IOSL through Table 2-34 • I/O Short Currents IOSH/IOSL was replaced by "Same as regular 3.3 V LVCMOS" (SAR 33852).                                                                  | 2-29 to 2-31        |

|                            | In the "3.3 V LVCMOS Wide Range" section, values were added to Table 2-47 through Table 2-49 for IOSL and IOSH, replacing "TBD" (SAR 33852).                                                                                                                  | 2-39 to 2-40        |

|                            | The following sentence was deleted from the "2.5 V LVCMOS" section (SAR 24916): "It uses a 5 V-tolerant input buffer and push-pull output buffer."                                                                                                            | 2-47                |

|                            | The table notes were revised for Table 2-90 • LVDS Minimum and Maximum DC Input and Output Levels (SAR 33859).                                                                                                                                                | 2-66                |

|                            | Values were added for $F_{DDRIMAX}$ and $F_{DDOMAX}$ in Table 2-102 • Input DDR Propagation Delays and Table 2-104 • Output DDR Propagation Delays (SAR 23919).                                                                                               | 2-78, 2-80          |

|                            | Table 2-115 • ProASIC3 CCC/PLL Specification was updated. A note was added to indicate that when the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available (SAR 25705).        | 2-90                |

|                            | The following figures were deleted (SAR 29991). Reference was made to a new application note, <i>Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs</i> , which covers these cases in detail (SAR 21770).                   | 2-92,               |

|                            | Figure 2-34 • Write Access after Write onto Same Address<br>Figure 2-35 • Read Access after Write onto Same Address<br>Figure 2-35 • Read Access after Write onto Same Address                                                                                | 2-94,<br>2-99 2-102 |

|                            | The port names in the SRAM "Timing Waveforms", SRAM "Timing Characteristics" tables, Figure 2-39 • FIFO Reset, and the FIFO "Timing Characteristics" tables were revised to ensure consistency with the software names (SARs 29991, 30510).                   |                     |

|                            | The "Pin Descriptions" chapter has been added (SAR 21642).                                                                                                                                                                                                    | 3-1                 |

|                            | Package names used in the "Package Pin Assignments" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                                                                                                          | 4-1                 |

| July 2010                  | The versioning system for datasheets has been changed. Datasheets are assigned a revision number that increments each time the datasheet is revised. The "ProASIC3 Device Status" table on page IV indicates the status for each device in the device family. | N/A                 |